(→Overview) |

|||

| (45 intermediate revisions by 21 users not shown) | |||

| Line 1: | Line 1: | ||

{{lithography processes}} | {{lithography processes}} | ||

| − | The '''5 nanometer (5 nm | + | The '''5 nanometer (5 nm) lithography process''' is a [[technology node]] semiconductor manufacturing process following the [[7 nm lithography process|7 nm process]] node. Commercial [[integrated circuit]] manufacturing using 5 nm process is set to begin sometime around 2020. |

The term "5 nm" is simply a commercial name for a generation of a certain size and its technology, and '''does not''' represent any geometry of the transistor. | The term "5 nm" is simply a commercial name for a generation of a certain size and its technology, and '''does not''' represent any geometry of the transistor. | ||

| Line 7: | Line 7: | ||

First introduced by the major foundries around the [[2020]] timeframe, the 5-nanometer [[process technology]] is characterized by its use of [[FinFET]] transistors with fin pitches in the 20s of nanometer and densest metal pitches in the 30s of nanometers. Due to the small feature sizes, these processes make extensive use of EUV for the critical dimensions, along with quad patterning for the fins and double patterning for the rest of the metal stack. Note that Intel [[7 nm process]] is comparable to the foundry 5-nanometer node. | First introduced by the major foundries around the [[2020]] timeframe, the 5-nanometer [[process technology]] is characterized by its use of [[FinFET]] transistors with fin pitches in the 20s of nanometer and densest metal pitches in the 30s of nanometers. Due to the small feature sizes, these processes make extensive use of EUV for the critical dimensions, along with quad patterning for the fins and double patterning for the rest of the metal stack. Note that Intel [[7 nm process]] is comparable to the foundry 5-nanometer node. | ||

| − | === | + | === Density === |

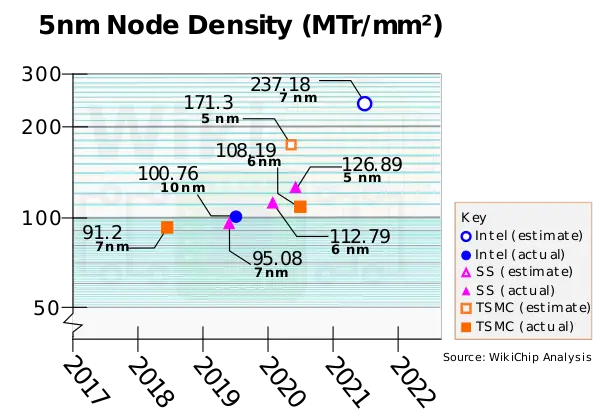

In terms of raw cell-level density, the 5-nanometer node features silicon densities between 130-230 million [[transistors per square millimeter]] based on WikiChip's own analysis. | In terms of raw cell-level density, the 5-nanometer node features silicon densities between 130-230 million [[transistors per square millimeter]] based on WikiChip's own analysis. | ||

| − | :[[File:5nm densities.svg| | + | :[[File:5nm densities.svg|600px]] |

== Industry == | == Industry == | ||

| Line 17: | Line 17: | ||

{{node comp|node=5 nm}} | {{node comp|node=5 nm}} | ||

| − | === | + | === 5 nm process nodes === |

| − | + | {| class="wikitable" style="text-align:center" | |

| + | ! | ||

| + | ! colspan=2| IRDS <info>International Roadmap for Devices and Systems</info> Roadmap 2017 | ||

| + | ! colspan=2| [[Samsung]] <ref name="Samsung 5 nm and 4 nm Update">{{cite book |title=Samsung 5 nm and 4 nm Update |url=https://fuse.wikichip.org/news/2823/samsung-5-nm-and-4-nm-update/ |website=WikiChip |date=19 October 2019}}</ref> | ||

| + | ! colspan="3" |[[TSMC]] <ref>{{cite book |url=https://fuse.wikichip.org/news/7048/n3e-replaces-n3-comes-in-many-flavors/ |title=N3E Replaces N3; Comes in Many Flavors |date=4 September 2022}}</ref> | ||

| + | |- | ||

| + | ! Process name | ||

| + | | [[7 nm]] | ||

| + | | [[5 nm]] | ||

| + | | 5LPE | ||

| + | | 5LPP | ||

| + | | N5 | ||

| + | | N5P | ||

| + | | 4N | ||

| + | |- | ||

| + | ! Transistor <br>density (MTr/mm<sup>2</sup>) | ||

| + | | - | ||

| + | | - | ||

| + | | 126.9 <ref name=Samsung>{{cite book |url=https://fuse.wikichip.org/news/6932/samsung-3nm-gaafet-enters-risk-production-discusses-next-gen-improvements/ |title=Samsung 3nm GAAFET Enters Risk Production; Discusses Next-Gen Improvements |date=5 July 2022}}</ref> | ||

| + | | - | ||

| + | | colspan=2 | 138.2 | ||

| + | | - | ||

| + | |- | ||

| + | ! SRAM bit-cell <br>size (μm<sup>2</sup>) | ||

| + | | 0.027 | ||

| + | | 0.020 | ||

| + | | colspan=2 | 0.0262 <ref>{{cite book |url=https://fuse.wikichip.org/news/7343/iedm-2022-did-we-just-witness-the-death-of-sram/ |title=Did We Just Witness The Death Of SRAM? |date=4 December 2022}}</ref> | ||

| + | | colspan=2 | 0.021 | ||

| + | | - | ||

| + | |- | ||

| + | ! Transistor <br>gate pitch (nm) | ||

| + | | 48 | ||

| + | | 42 | ||

| + | | colspan= 2| 57 | ||

| + | | colspan=2 | 51 | ||

| + | | - | ||

| + | |- | ||

| + | ! Interconnect <br>pitch (nm) | ||

| + | | 28 | ||

| + | | 24 | ||

| + | | 36 | ||

| + | | - | ||

| + | | colspan=2 | 28 | ||

| + | | - | ||

| + | |- | ||

| + | ! Release <br>status | ||

| + | | 2019 | ||

| + | | 2021 | ||

| + | | 2018 risk production<br>2020 production | ||

| + | | 2022 production | ||

| + | | 2019 risk production<br>2020 production | ||

| + | | 2020 risk production<br>2021 production | ||

| + | | 2022 production | ||

| + | |- | ||

| + | |} | ||

| − | === TSMC === | + | === 4 nm process nodes === |

| − | ==== | + | {| class="wikitable" style="text-align:center" |

| − | + | ! | |

| + | ! colspan="5" | [[Samsung]] <ref>https://sammyguru.com/samsung-starts-mass-producing-fourth-gen-4nm-chips-as-demand-skyrockets/</ref> | ||

| + | ! colspan="4" | [[TSMC]] <ref>{{cite book |url=https://fuse.wikichip.org/news/7375/tsmc-n3-and-challenges-ahead/ |title=TSMC N3, and Challenges Ahead |date=27 May 2023}}</ref> | ||

| + | ! [[Intel]] <ref>{{cite book |first=David |last=Schor |url=https://fuse.wikichip.org/news/6720/a-look-at-intel-4-process-technology/ |title=A Look At Intel 4 Process Technology |website=WikiChip Fuse |date=19 June 2022}}</ref> | ||

| + | |- | ||

| + | ! Process name | ||

| + | | 4LPE<br>SF4E || 4LPP<br>SF4 || 4LPP+<br>SF4P || 4HPC<br>SF4X || 4LPA<br>SF4U | ||

| + | | N4 || N4P || N4X || N4C | ||

| + | | Intel 4 | ||

| + | |- | ||

| + | ! Transistor <br>density (MTr/mm<sup>2</sup>) | ||

| + | | colspan="2" | 137 || - || - || - | ||

| + | | colspan="2" | 143.7 || - || - | ||

| + | | 123.4 | ||

| + | |- | ||

| + | ! SRAM bit-cell <br>size (μm<sup>2</sup>) | ||

| + | | colspan="2" | 0.0262 || - || - || - | ||

| + | | colspan="2" | - || - || - | ||

| + | | 0.024 | ||

| + | |- | ||

| + | ! Transistor <br>gate pitch (nm) | ||

| + | | colspan="2" | 57 || - || - || - | ||

| + | | colspan="2" | 51 || - || - | ||

| + | | 50 | ||

| + | |- | ||

| + | ! Interconnect <br>pitch (nm) | ||

| + | | colspan="2" | 32 || - || - || - | ||

| + | | colspan="2" | 28 || - || - | ||

| + | | 30 | ||

| + | |- | ||

| + | ! Release <br>status | ||

| + | | 2020 risk <br>production<br>2021 production || 2022 production || 2023 production || 2025 Q1 <br>production || 2025 production | ||

| + | | 2021 risk <br>production<br>2022 production || 2022 risk <br>production<br>2022 production || 2023 risk <br>production<br>2024 production || 2025 production | ||

| + | | 2022 risk <br>production<br>2023 production | ||

| + | |- | ||

| + | |} | ||

| + | • Transistor gate pitch is also referred to as CPP (contacted poly pitch) and interconnect pitch is also referred to as MMP (minimum metal pitch). | ||

| + | |||

| + | == Intel == | ||

| + | === Intel 4 === | ||

| + | [[Intel 4]] process, codenamed '''P1276''', formerly [[Intel]] 7-nanometer process, will enter risk production at the end of [[2022]] and ramp in [[2023]]. On February 8 [[2017]], [[Intel]] announced a $7B investment in Arizona's Fab 42 which will eventually produce chips on a [[7 nm]] process. On March 23 [[2021]], Intel announced a $20B investment for two fabs in Arizona, which will produce chips on a [[7 nm]] process. | ||

| + | |||

| + | == TSMC == | ||

| + | [[TSMC]] started mass production of its '''5-nanometer N5 node''' in April [[2020]]. [[TSMC]] considers its 5-nanometer node a full node shrink over its [[N7|7-nanometer process]]. In early [[2021]] [[TSMC]] plans on introducing a second version of its N5 process called '''N5P''' which provides additional performance enhancements. | ||

| − | N5 is | + | === N5 === |

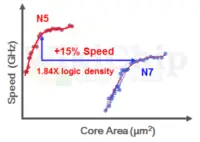

| + | [[TSMC]] started its [[risk production]] of the 5-nanometer, '''N5''', node in March [[2019]]. The process ramped in April [[2020]]. The N5 process is a [[full node]] successor to the company's [[N7 node]], featuring 1.84x improvement in logic density. | ||

| + | |||

| + | The N5 node continues to use [[bulk silicon]] [[FinFET transistors]]. Leveraging their experience from 7+, [[5 nm]] makes extensive use of [[EUV]] for more critical layers in order to reduce the [[multi-patterning]] complexity. It is believed that [[TSMC]] N5 process uses 11-13 EUV masks in order to replace about 35 immersion layers that would otherwise be required to produce the same pattern without EUV. In other words for TSMC to go from its [[N7]] node to its [[N5]] node would entail going from roughly 87 [[masks]] to 115 masks. The introduction of EUV reduced this number back down to around 81 masks. | ||

| + | |||

| + | [[File:n5-ppa.png|200px|thumb|right|N5 PPA]] | ||

| + | |||

| + | At a high level, TSMC N5 is a high-density high-performance [[FinFET]] process designed for mobile SoCs and HPC applications. Fabrication makes extensive use of EUV at Fab 18, the company’s new 12-inch GigaFab located at the Southern Taiwan Science Park. TSMC says that its 5-nanometer process is 1.84x denser than its [[N7|7-nanometer node]]. TSMC also optimized analog devices where roughly 1.2x scaling has been achieved. TSMC reported the density for a typical mobile SoC which consists of 60% logic, 30% SRAM, and 10% analog/IO, their 5 nm technology scaling was projected to reduce chip size by 35%-40%. | ||

{| class="wikitable" style="text-align: center;" | {| class="wikitable" style="text-align: center;" | ||

|- | |- | ||

| − | ! colspan="3" | N5 PPA vs. [[N7]] | + | ! colspan="3" | N5 [[PPA]] vs. [[N7]] |

|- | |- | ||

| − | ! Speed @ iso-power !! Power @ iso-speed !! Max speed improvement<br>@ Vdd (eLVT) | + | ! Speed @ [[iso-power]] !! Power @ [[iso-speed]] !! Max speed improvement<br>@ Vdd (eLVT) |

|- | |- | ||

| ~15% || ~30% || ~25% | | ~15% || ~30% || ~25% | ||

|} | |} | ||

| + | [[File:n5-hmc-fin.jpg|190px|right|thumb|N5 HMC FinFet Device (IEDM 2019)]] | ||

| + | [[File:n5-channel-stress.png|200px|right|thumb|Diffraction pattern for the fully-strained HMC lattice (IEDM 2019)]] | ||

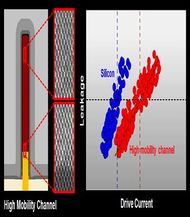

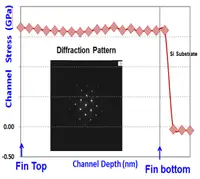

| + | In order to improve the drive current, TSMC introduced a [[high-mobility channel]] (HMC) for its 5-nanometer [[FinFET devices]]. We believe TSMC is employing a SiGe channel for the pMOS devices. It has been suggested that the channel has 37% Ge composition. TSMC says that the HMC delivers 18% performance gain versus equivalent Si finFETs. | ||

| + | |||

| + | [[File:N5 mx rc and vx rc.png|right|thumb|200px|Tightest pitch Mx RC and Vx RC on 5nm was kept at similar levels to N7.]] | ||

| + | Despite aggressively tighter pitches, TSMC says metal lines RC and via resistance have been kept relatively similar to N7. TSMC says this was achieved by "using EUV patterning, innovative scaled barrier/liner, ESL/ELK dielectrics, and Cu reflow." The improvements meant the interconnect RC did not worsen relative to N7 as N7 did relative to N16. | ||

| + | |||

| + | The 5 nm node is expected to deliver a 15% improvement in performance at [[iso-power|constant power]] or a 20% reduction in power at [[iso-performance|constant performance]]. In addition to the ultra-LVT (uLVT) that was offered with [[N7]], there is a new extreme-LVT (eLVT) which can push that 15% up to 25% higher speed at Vdd. Additionally, compared to the standard N5 cells, the HP cell variants can push that performance by another 10% at the cost of density. | ||

| + | |||

| + | The N5 node makes use of a number of [[density boosters]] under a marketing term called "smart hyper-scaling features" (similar to Intel). N5 introduces [[single diffusion breaks]] in order to reduce cell spacing. Additionally, TSMC added the ability to drop the gate contact over the active region (COAG). Although originally experimented with at the N7 node, [[via pillars]] are also used extensively in the N5 node. TSMC makes extensive use of [[via pillars]] in N5 due to the three-fold increase of Mx resistance. | ||

| + | |||

| + | ==== SRAM ==== | ||

| + | Two [[6T]] [[SRAM]] [[bitcells]] were disclosed by TSMC. The high-performance cell is 0.025 µm² while the high-density cell is 0.021 µm². Assuming a ballpark assist circuit overhead of around 30%, the high-density cells yields an estimate of ~32 Mib/mm² of cache. This an increase of 30% from [[N7]] which is around 24.7 Mib/mm². At ISSCC 2020, TSMC presented a test shuttle with 135 Mib of HD SRAM and additional IPs. Their reported density for the HD cells is similar to our estimates. | ||

| + | |||

| + | {| class="wikitable collapsible collapsed tc1" | ||

| + | |- | ||

| + | ! colspan="2" | N5 Shuttle Test Chip | ||

| + | |- | ||

| + | | colspan="2" | [[File:n5 shuttle.jpg|300px]] | ||

| + | |- | ||

| + | | Technology || 5nm HK-MG FinFET | ||

| + | |- | ||

| + | | Supply voltage || Core: 0.75V<br>IO: 1.2V | ||

| + | |- | ||

| + | | Bit cell size || 0.021 μm² | ||

| + | |- | ||

| + | | SRAM macro configuration || 1024x144 MUX4<br>256 bits/BL,<br>288 bits/WL | ||

| + | |- | ||

| + | | SRAM capacity || 135Mb | ||

| + | |- | ||

| + | | Test Features || Column Redundancy<br>Programmable E-fuse | ||

| + | |- | ||

| + | | [[Die size]] || 10mm x 7.98mm = 79.8mm2 | ||

| + | |} | ||

| + | |||

| + | === N5P === | ||

| + | As with their 7-nanometer process, TSMC offer an optimized version of their N5 process called '''N5 Performance-enhanced version''' ('''N5P'''). This process uses the same design rules and is fully IP-compatible with N5. Through FEOL and MOL optimizations, N5P will offer 7% higher performance over N5 at [[iso-power]] or 15% lower power at [[iso-performance]]. Risk production for N5P is expected to start around the fourth quarter of 2020 with volume production starting sometimes in 2021. | ||

| − | + | {| class="wikitable" style="text-align: center;" | |

| + | |- | ||

| + | ! colspan="3" | N5P [[PPA]] vs. N5 | ||

| + | |- | ||

| + | ! Speed @ [[iso-power]] !! Power @ [[iso-speed]] | ||

| + | |- | ||

| + | | ~7% || ~15 | ||

| + | |} | ||

| − | ==== | + | == Samsung == |

| − | + | === 5LPE === | |

| + | Samsung '''5-Nanometer Low-Power Early''' ('''5LPE''') design development completed in early 2019. Unlike TSMC's 5-nanometer node, 5LPE is considered to be only a [[quarter node]] successor to the company's [[7-nanometer 7LPP]] process, delivering 1.3x density improvement through a new [[standard cell library]] as well as new [[scaling boosters]]. Samsung 5LPE process provides different benefits depending on the migration path selected from 7LPP. Moving to a similar [[7.5T library]] will provide 11% performance improvement through various transistor optimizations ([[Low-k spacer]], DC enhancement, etc.). Alternatively, moving to the new [[6T library]] provides around 33% higher density. | ||

| − | == | + | {| class="wikitable" style="text-align: center;" |

| − | = | + | |- |

| − | + | ! colspan="3" | 5LPE [[PPA]] vs. [[7LPP]] | |

| + | |- | ||

| + | ! Speed @ iso-power !! Power @ iso-speed | ||

| + | |- | ||

| + | | ~11% || ~20% | ||

| + | |} | ||

| − | + | The area benefits come from a single [[track reduction]] in the [[cell height]], [[coag|contact over the active region edge]], and the use of a [[single diffusion break]]. | |

{| class="wikitable collapsible collapsed" | {| class="wikitable collapsible collapsed" | ||

| Line 94: | Line 248: | ||

With the new 6T library, Samsung is also providing single-fin devices for ultra-low power and always-on circuits. | With the new 6T library, Samsung is also providing single-fin devices for ultra-low power and always-on circuits. | ||

| − | ==== | + | === 4LPE === |

| − | + | The '''4-nanometer Low-Power Early''' ('''4LPE''') process is a continuation of Samsung's 7LPP and 5LPE, inheriting the transistor and most of the ground rules from 7LPP. This is Samsung's last [[FinFET]]-based process. 4LPE features similar pitches to 5LPE but introduces slightly tighter metal pitches. | |

| + | |||

| + | {| class="wikitable collapsible collapsed" | ||

| + | |- | ||

| + | ! colspan="3" | Samsung 4-nanometer 4LPE Design Rules | ||

| + | |- | ||

| + | ! Layer !! Pitch !! Scale Factor | ||

| + | |- | ||

| + | | Fin || 27'''(?)''' nm || 1.0x'''(?)''' | ||

| + | |- | ||

| + | | Gate Pitch || 54/60 nm || 1.0x | ||

| + | |- | ||

| + | | Metal 1 || 28 nm || 0.70x | ||

| + | |- | ||

| + | | Metal 2 || 36 nm || 1.0x | ||

| + | |- | ||

| + | | Metal 3 || 32 nm || 0.89x | ||

| + | |- | ||

| + | | Metal 4 || 44 nm || 1.0x | ||

| + | |- | ||

| + | |} | ||

== 5 nm Microprocessors== | == 5 nm Microprocessors== | ||

| − | * PEZY | + | |

| + | {| border="0" cellpadding="5" width="100%" | ||

| + | |- | ||

| + | |width="25%" valign="top" align="left"| | ||

| + | * '''[[Apple]]''' | ||

| + | **[[apple/ax/a14|A14 Bionic]] | ||

| + | **[[apple/ax/a15|A15 Bionic]] | ||

| + | **[[apple/mx/m1|M1]] | ||

| + | **M1 Pro | ||

| + | **M1 Max | ||

| + | **M1 Ultra | ||

| + | **M2 | ||

| + | |||

| + | * '''[[MediaTek]]''' • {{mediatek|Dimensity}} | ||

| + | ** Dimensity 8000 | ||

| + | ** Dimensity 8100 | ||

| + | ** Dimensity 9000 | ||

| + | |||

| + | *'''[[Samsung]]''' • [[Exynos]] | ||

| + | **Exynos 1080 | ||

| + | **Exynos 1280 | ||

| + | **Exynos 2100 | ||

| + | **Exynos W920 | ||

| + | |||

| + | *'''[[Annapurna Labs]]''' | ||

| + | **[[AWS Graviton3]] (Amazon) | ||

| + | |||

| + | |width="25%" valign="top" align="left"| | ||

| + | *'''[[Qualcomm]]''' | ||

| + | **Snapdragon 780 5G | ||

| + | **Snapdragon 888 | ||

| + | **Snapdragon 888+ | ||

| + | **[[Snapdragon 4]] Gen 2 | ||

| + | **[[Snapdragon 6]] Gen 1 | ||

| + | **[[Snapdragon 6]] Gen 3 | ||

| + | **[[Snapdragon 7]] Gen 1 | ||

| + | **[[Snapdragon 7]]s Gen 2 | ||

| + | **[[Snapdragon 8]] Gen 1 | ||

| + | **[[Snapdragon 8]] Plus Gen 1 | ||

| + | **[[Snapdragon 8cx]] Gen 3 | ||

| + | **[[Snapdragon 7]]c+ Gen 3 | ||

| + | |||

| + | *'''[[HiSilicon]]''' • [[Kirin]] | ||

| + | **{{hisilicon|Kirin 9000}} | ||

| + | **{{hisilicon|Kirin 9000E}} | ||

| + | |||

| + | * [[PEZY]] | ||

** {{pezy|PEZY-SC4}} | ** {{pezy|PEZY-SC4}} | ||

| + | ** {{pezy|PEZY-SCx}} | ||

| + | |width="25%" valign="top" align="left"| | ||

| + | :;'''[[AMD]]''' • [[EPYC]] | ||

| + | *[[amd/epyc/9124|EPYC 9124]] | ||

| + | *[[amd/epyc/9174f|EPYC 9174F]] | ||

| + | *[[amd/epyc/9224|EPYC 9224]] | ||

| + | *[[amd/epyc/9254|EPYC 9254]] | ||

| + | *[[amd/epyc/9274f|EPYC 9274F]] | ||

| + | *[[amd/epyc/9334|EPYC 9334]] | ||

| + | *[[amd/epyc/9354|EPYC 9354]] | ||

| + | *[[amd/epyc/9354p|EPYC 9354P]] | ||

| + | *[[amd/epyc/9374f|EPYC 9374F]] | ||

| + | *[[amd/epyc/9454|EPYC 9454]] | ||

| + | *[[amd/epyc/9454p|EPYC 9454P]] | ||

| + | *[[amd/epyc/9474f|EPYC 9474F]] | ||

| + | *[[amd/epyc/9534|EPYC 9534]] | ||

| + | *[[amd/epyc/9554|EPYC 9554]] | ||

| + | *[[amd/epyc/9554p|EPYC 9554P]] | ||

| + | *[[amd/epyc/9634|EPYC 9634]] | ||

| + | *[[amd/epyc/9654|EPYC 9654]] | ||

| + | *[[amd/epyc/9654p|EPYC 9654P]] | ||

| + | |width="25%" valign="top" align="left"| | ||

| + | *'''[[Ryzen]]''' | ||

| + | *{{amd|ryzen 5/7600x|Ryzen 5 7600X}} | ||

| + | *{{amd|ryzen 7/7700|Ryzen 7 7700}} | ||

| + | *{{amd|ryzen 7/7700x|Ryzen 7 7700X}} | ||

| + | *{{amd|ryzen 7/7800x3d|Ryzen 7 7800X3D}} | ||

| + | *{{amd|ryzen 9/7900x3d|Ryzen 9 7900X3D}} | ||

| + | *{{amd|ryzen 9/7950x3d|Ryzen 9 7950X3D}} | ||

| + | |} | ||

| + | |||

{{expand list}} | {{expand list}} | ||

| − | == 5 nm Microarchitectures== | + | == 5 nm Microarchitectures == |

| + | |||

| + | {| border="0" cellpadding="5" width="75%" | ||

| + | |- | ||

| + | |width="25%" valign="top" align="left"| | ||

| + | :;[[ARM]] • [[Cortex]] | ||

| + | *{{armh|Cortex-X1|l=arch}} | ||

| + | *{{armh|Cortex-M55|l=arch}} | ||

| + | *{{armh|Cortex-A76|l=arch}} | ||

| + | *{{armh|Cortex-A77|l=arch}} | ||

| + | *{{armh|Cortex-A78|l=arch}} | ||

| + | *{{armh|Cortex-A510|l=arch}} | ||

| + | *{{armh|Cortex-A710|l=arch}} | ||

| + | *{{armh|Cortex-A715|l=arch}} | ||

| + | |width="25%" valign="top" align="left"| | ||

| + | :;[[AMD]] | ||

| + | *{{amd|Zen 4|l=arch}} | ||

| + | :Genoa - Cores | ||

| + | *Navi 3 (GPU) | ||

| + | :;[[Neoverse]] | ||

| + | *Chaberton | ||

| + | *Hunter | ||

| + | *Poseidon | ||

| + | |width="25%" valign="top" align="left"| | ||

| + | :;Nvidia | ||

| + | * Grace Hopper | ||

| + | |} | ||

| + | |||

{{expand list}} | {{expand list}} | ||

| Line 113: | Line 391: | ||

* Samsung, Arm TechCon, 2019 | * Samsung, Arm TechCon, 2019 | ||

* TSMC, Arm TechCon, 2019 | * TSMC, Arm TechCon, 2019 | ||

| + | * {{bib|iedm|2019|TSMC}} | ||

[[category:lithography]] | [[category:lithography]] | ||

Latest revision as of 18:00, 21 March 2025

The 5 nanometer (5 nm) lithography process is a technology node semiconductor manufacturing process following the 7 nm process node. Commercial integrated circuit manufacturing using 5 nm process is set to begin sometime around 2020.

The term "5 nm" is simply a commercial name for a generation of a certain size and its technology, and does not represent any geometry of the transistor.

Contents

Overview[edit]

First introduced by the major foundries around the 2020 timeframe, the 5-nanometer process technology is characterized by its use of FinFET transistors with fin pitches in the 20s of nanometer and densest metal pitches in the 30s of nanometers. Due to the small feature sizes, these processes make extensive use of EUV for the critical dimensions, along with quad patterning for the fins and double patterning for the rest of the metal stack. Note that Intel 7 nm process is comparable to the foundry 5-nanometer node.

Density[edit]

In terms of raw cell-level density, the 5-nanometer node features silicon densities between 130-230 million transistors per square millimeter based on WikiChip's own analysis.

Industry[edit]

Only three companies are currently planning or developing a 5-nanometer node: Intel, TSMC, and Samsung.

| Intel | TSMC | Samsung | |||||

|---|---|---|---|---|---|---|---|

| Process | P1278 (CPU), P1279 (SoC) | N5, N5P | 5LPP | ||||

| Production | 2023 | Q1'2020 | 2020 | ||||

| Litho | Lithography | EUV | |||||

| Immersion Exposure | SE (EUV) DP (193i) | SE (EUV) DP (193i) | |||||

| Wafer | Type | Bulk | |||||

| Size | 300 mm | ||||||

| xTor | Type | FinFET | FinFET | ||||

| Voltage | |||||||

| Value | 7 nm Δ | Value | 7 nm Δ | Value | 7 nm Δ | ||

| Fin | Pitch | 27 nm | 1.0x | ||||

| Width | |||||||

| Height | |||||||

| Gate Length (Lg) | 8/10 nm | 1.0x | |||||

| Contacted Gate Pitch (CPP) | 60 nm (HP) 54 nm (HD) | 1.0x 1.0x | |||||

| Minimum Metal Pitch (MMP) | 36 nm | 1.0x | |||||

| SRAM | High-Perf (HP) | 0.032 µm² | 1.0x | ||||

| High-Density (HD) | 0.021 µm² | 0.78x | 0.026 µm² | 1.0x | |||

| Low-Voltage (LV) | |||||||

5 nm process nodes[edit]

| IRDS International Roadmap for Devices and Systems Roadmap 2017

|

Samsung [1] | TSMC [2] | |||||

|---|---|---|---|---|---|---|---|

| Process name | 7 nm | 5 nm | 5LPE | 5LPP | N5 | N5P | 4N |

| Transistor density (MTr/mm2) |

- | - | 126.9 [3] | - | 138.2 | - | |

| SRAM bit-cell size (μm2) |

0.027 | 0.020 | 0.0262 [4] | 0.021 | - | ||

| Transistor gate pitch (nm) |

48 | 42 | 57 | 51 | - | ||

| Interconnect pitch (nm) |

28 | 24 | 36 | - | 28 | - | |

| Release status |

2019 | 2021 | 2018 risk production 2020 production |

2022 production | 2019 risk production 2020 production |

2020 risk production 2021 production |

2022 production |

4 nm process nodes[edit]

| Samsung [5] | TSMC [6] | Intel [7] | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| Process name | 4LPE SF4E |

4LPP SF4 |

4LPP+ SF4P |

4HPC SF4X |

4LPA SF4U |

N4 | N4P | N4X | N4C | Intel 4 |

| Transistor density (MTr/mm2) |

137 | - | - | - | 143.7 | - | - | 123.4 | ||

| SRAM bit-cell size (μm2) |

0.0262 | - | - | - | - | - | - | 0.024 | ||

| Transistor gate pitch (nm) |

57 | - | - | - | 51 | - | - | 50 | ||

| Interconnect pitch (nm) |

32 | - | - | - | 28 | - | - | 30 | ||

| Release status |

2020 risk production 2021 production |

2022 production | 2023 production | 2025 Q1 production |

2025 production | 2021 risk production 2022 production |

2022 risk production 2022 production |

2023 risk production 2024 production |

2025 production | 2022 risk production 2023 production |

• Transistor gate pitch is also referred to as CPP (contacted poly pitch) and interconnect pitch is also referred to as MMP (minimum metal pitch).

Intel[edit]

Intel 4[edit]

Intel 4 process, codenamed P1276, formerly Intel 7-nanometer process, will enter risk production at the end of 2022 and ramp in 2023. On February 8 2017, Intel announced a $7B investment in Arizona's Fab 42 which will eventually produce chips on a 7 nm process. On March 23 2021, Intel announced a $20B investment for two fabs in Arizona, which will produce chips on a 7 nm process.

TSMC[edit]

TSMC started mass production of its 5-nanometer N5 node in April 2020. TSMC considers its 5-nanometer node a full node shrink over its 7-nanometer process. In early 2021 TSMC plans on introducing a second version of its N5 process called N5P which provides additional performance enhancements.

N5[edit]

TSMC started its risk production of the 5-nanometer, N5, node in March 2019. The process ramped in April 2020. The N5 process is a full node successor to the company's N7 node, featuring 1.84x improvement in logic density.

The N5 node continues to use bulk silicon FinFET transistors. Leveraging their experience from 7+, 5 nm makes extensive use of EUV for more critical layers in order to reduce the multi-patterning complexity. It is believed that TSMC N5 process uses 11-13 EUV masks in order to replace about 35 immersion layers that would otherwise be required to produce the same pattern without EUV. In other words for TSMC to go from its N7 node to its N5 node would entail going from roughly 87 masks to 115 masks. The introduction of EUV reduced this number back down to around 81 masks.

At a high level, TSMC N5 is a high-density high-performance FinFET process designed for mobile SoCs and HPC applications. Fabrication makes extensive use of EUV at Fab 18, the company’s new 12-inch GigaFab located at the Southern Taiwan Science Park. TSMC says that its 5-nanometer process is 1.84x denser than its 7-nanometer node. TSMC also optimized analog devices where roughly 1.2x scaling has been achieved. TSMC reported the density for a typical mobile SoC which consists of 60% logic, 30% SRAM, and 10% analog/IO, their 5 nm technology scaling was projected to reduce chip size by 35%-40%.

| N5 PPA vs. N7 | ||

|---|---|---|

| Speed @ iso-power | Power @ iso-speed | Max speed improvement @ Vdd (eLVT) |

| ~15% | ~30% | ~25% |

In order to improve the drive current, TSMC introduced a high-mobility channel (HMC) for its 5-nanometer FinFET devices. We believe TSMC is employing a SiGe channel for the pMOS devices. It has been suggested that the channel has 37% Ge composition. TSMC says that the HMC delivers 18% performance gain versus equivalent Si finFETs.

Despite aggressively tighter pitches, TSMC says metal lines RC and via resistance have been kept relatively similar to N7. TSMC says this was achieved by "using EUV patterning, innovative scaled barrier/liner, ESL/ELK dielectrics, and Cu reflow." The improvements meant the interconnect RC did not worsen relative to N7 as N7 did relative to N16.

The 5 nm node is expected to deliver a 15% improvement in performance at constant power or a 20% reduction in power at constant performance. In addition to the ultra-LVT (uLVT) that was offered with N7, there is a new extreme-LVT (eLVT) which can push that 15% up to 25% higher speed at Vdd. Additionally, compared to the standard N5 cells, the HP cell variants can push that performance by another 10% at the cost of density.

The N5 node makes use of a number of density boosters under a marketing term called "smart hyper-scaling features" (similar to Intel). N5 introduces single diffusion breaks in order to reduce cell spacing. Additionally, TSMC added the ability to drop the gate contact over the active region (COAG). Although originally experimented with at the N7 node, via pillars are also used extensively in the N5 node. TSMC makes extensive use of via pillars in N5 due to the three-fold increase of Mx resistance.

SRAM[edit]

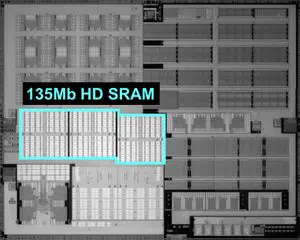

Two 6T SRAM bitcells were disclosed by TSMC. The high-performance cell is 0.025 µm² while the high-density cell is 0.021 µm². Assuming a ballpark assist circuit overhead of around 30%, the high-density cells yields an estimate of ~32 Mib/mm² of cache. This an increase of 30% from N7 which is around 24.7 Mib/mm². At ISSCC 2020, TSMC presented a test shuttle with 135 Mib of HD SRAM and additional IPs. Their reported density for the HD cells is similar to our estimates.

| N5 Shuttle Test Chip | |

|---|---|

| |

| Technology | 5nm HK-MG FinFET |

| Supply voltage | Core: 0.75V IO: 1.2V |

| Bit cell size | 0.021 μm² |

| SRAM macro configuration | 1024x144 MUX4 256 bits/BL, 288 bits/WL |

| SRAM capacity | 135Mb |

| Test Features | Column Redundancy Programmable E-fuse |

| Die size | 10mm x 7.98mm = 79.8mm2 |

N5P[edit]

As with their 7-nanometer process, TSMC offer an optimized version of their N5 process called N5 Performance-enhanced version (N5P). This process uses the same design rules and is fully IP-compatible with N5. Through FEOL and MOL optimizations, N5P will offer 7% higher performance over N5 at iso-power or 15% lower power at iso-performance. Risk production for N5P is expected to start around the fourth quarter of 2020 with volume production starting sometimes in 2021.

| N5P PPA vs. N5 | ||

|---|---|---|

| Speed @ iso-power | Power @ iso-speed | |

| ~7% | ~15 | |

Samsung[edit]

5LPE[edit]

Samsung 5-Nanometer Low-Power Early (5LPE) design development completed in early 2019. Unlike TSMC's 5-nanometer node, 5LPE is considered to be only a quarter node successor to the company's 7-nanometer 7LPP process, delivering 1.3x density improvement through a new standard cell library as well as new scaling boosters. Samsung 5LPE process provides different benefits depending on the migration path selected from 7LPP. Moving to a similar 7.5T library will provide 11% performance improvement through various transistor optimizations (Low-k spacer, DC enhancement, etc.). Alternatively, moving to the new 6T library provides around 33% higher density.

| 5LPE PPA vs. 7LPP | ||

|---|---|---|

| Speed @ iso-power | Power @ iso-speed | |

| ~11% | ~20% | |

The area benefits come from a single track reduction in the cell height, contact over the active region edge, and the use of a single diffusion break.

| Samsung 5-nanometer 5LPE Design Rules | ||

|---|---|---|

| Layer | Pitch | Scale Factor |

| Fin | 27 nm | 1.0x |

| Gate Pitch | 54/60 nm | 1.0x |

| Metal 1 | 40 nm | 1.0x |

| Metal 2 | 36 nm | 0.75x |

| Metal 3 | 36 nm | 1.0x |

| Metal 4 | 44 nm | 1.0x |

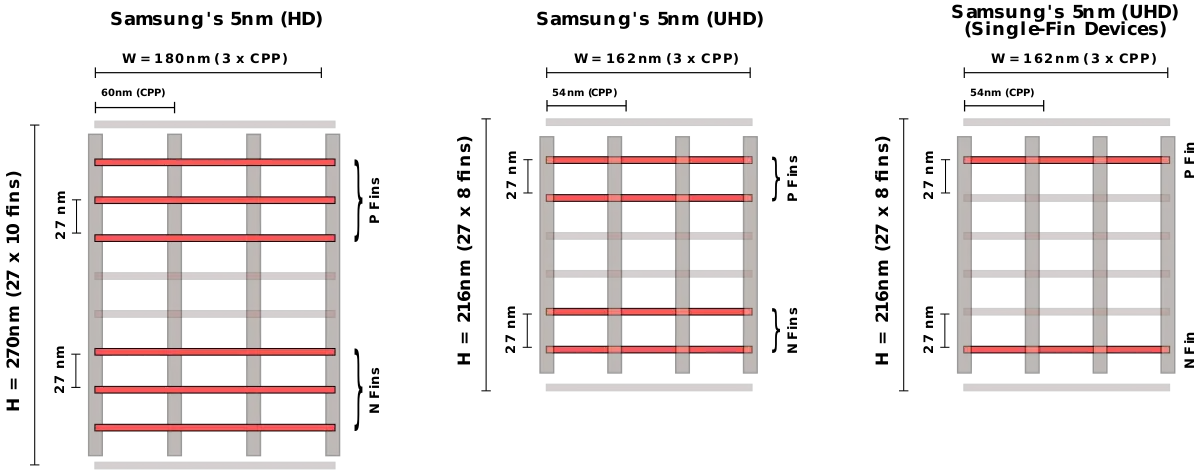

Samsung 5LPE provides two main libraries - 7.5T library (HD) for performance and a 6T library (UHD) for the area and power optimizations. The 7.5T library utilizes a relaxed 60 nm poly pitch with 10 diffusion lines for a cell height of 270 nanometers. This is identical to the 7LPP library. In the 7LPP process, Samsung also offered a high-density 6.75T cell library with a tighter 54 nm CPP that had 9 diffusion lines. In 5LPP, the new 6T library also utilizes the 54 nm CPP but reduces the diffusion lines to 8 for an even shorter cell height of 216 nm.

| Samsung 5-nanometer 5LPE Standard Libraries | ||

|---|---|---|

| Library | 7.5T HD | 6T UHD |

| Cell Height | 270 nm | 216 nm |

| Config | 3p+3n | 2p+2n |

| Signal Tracks | 6 | 5 |

| CPP | 60 nm | 54 nm |

| M1 | 40 (Bi) | 40 (Uni) |

| M2 | 60 nm | 36 nm |

| DB | MDB | SDB |

| CB | CB on STI | CB on RXN/RXP edge |

With the new 6T library, Samsung is also providing single-fin devices for ultra-low power and always-on circuits.

4LPE[edit]

The 4-nanometer Low-Power Early (4LPE) process is a continuation of Samsung's 7LPP and 5LPE, inheriting the transistor and most of the ground rules from 7LPP. This is Samsung's last FinFET-based process. 4LPE features similar pitches to 5LPE but introduces slightly tighter metal pitches.

| Samsung 4-nanometer 4LPE Design Rules | ||

|---|---|---|

| Layer | Pitch | Scale Factor |

| Fin | 27(?) nm | 1.0x(?) |

| Gate Pitch | 54/60 nm | 1.0x |

| Metal 1 | 28 nm | 0.70x |

| Metal 2 | 36 nm | 1.0x |

| Metal 3 | 32 nm | 0.89x |

| Metal 4 | 44 nm | 1.0x |

5 nm Microprocessors[edit]

|

|

This list is incomplete; you can help by expanding it.

5 nm Microarchitectures[edit]

|

|

This list is incomplete; you can help by expanding it.

Bibliography[edit]

- WikiChip Own Research

- TSMC Technology Symposium, 2017

- TSMC Technology Symposium, 2018

- TSMC Technology Symposium, 2019

- Samsung Foundry Forum, 2019

- Samsung, Arm TechCon, 2019

- TSMC, Arm TechCon, 2019

- TSMC, 2019 IEEE 65th International Electron Devices Meeting (IEDM).

Semiconductor lithography processes technology

Semiconductor lithography processes technology