| Line 24: | Line 24: | ||

=== TSMC === | === TSMC === | ||

| + | |||

| + | [[File:7nm tsmc.jpeg|right|200px]] | ||

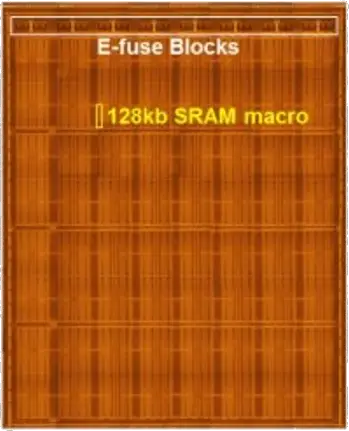

| + | In ISSCC 2017, the memory group at [[TSMC]] detailed their test 256 Mib SRAM chip which featured a 42.64 mm² die. The chip is manufactured on TSMC's 7nm HK-MG FinFET process using SAQP. The over die is 0.34x the size of their [[16 nm process]] version. TSMC's 7nm process density is 1.6X compared to their 10nm process. Minimum metal pitch is 40 nm, as reported at IEDM 2016. TSMC claims their 7nm process will deliver a 20% performance improvement and a 40% reduction in power consumption. | ||

| + | |||

| + | The 7nm node will come in two variants, one optimized for mobile applications and a second one optimized for High Performance applications. | ||

| + | TSMC plans to introduce a second improved process called 7nm+ a year later, which will introduce some layers processed with EUVL. This will improve yields and reduce fab cycle times. The 7nm+ process will deliver improved power consumption and between 15-20% area scaling over their first generation 7nm process. | ||

| + | |||

| + | {| class="collapsible collapsed wikitable" | ||

| + | |- | ||

| + | ! colspan="2" | TSMC 256 Mib SRAM demo 7 nm wafer | ||

| + | |- | ||

| + | | | ||

| + | <table class="wikitable"> | ||

| + | <tr><th>Technology</th><td>7 nm HK-MG FinFET</td></tr> | ||

| + | <tr><th>Metal scheme</th><td>1 Poly / 7 Metal</td></tr> | ||

| + | <tr><th>Supply voltage</th><td>0.75 V (core)<br>1.8 V (i/o)</td></tr> | ||

| + | <tr><th>Bit cell size</th><td>0.027 µm²</td></tr> | ||

| + | <tr><th>macro configs</th><td>4096x32 MUX16<br>258 bits/BL<br>272 bits/WL</td></tr> | ||

| + | <tr><th>Capacity</th><td>256 Mib</td></tr> | ||

| + | <tr><th>Test Features</th><td>Row/Column Redundancy<br>Programmable E-fuse</td></tr> | ||

| + | <tr><th>Die Size</th><td>5903 µm x 7223 µm = 42.64 mm²</td></tr> | ||

| + | </table> | ||

| + | | [[File:tsmc 7nm SRAM block.png]] | ||

| + | |} | ||

==== N7 ==== | ==== N7 ==== | ||

==== N7P ==== | ==== N7P ==== | ||

=== Samsung === | === Samsung === | ||

| + | Samsung will use EUVL for their 7nm node and thus will be the first to introduce this new technology after more than a decade of development. | ||

| + | On May 24 2017, Samsung released a press release of their updated roadmap. Due to delays in the introduction of EUVL, Samsung will introduce a new process called 8nm LPP, to bridge the gap between 10nm and 7nm. The process will be manufactured without the use of EUVL and will feature a slightly relaxed transistor size. | ||

==== 7LPE ==== | ==== 7LPE ==== | ||

==== 7LPP ==== | ==== 7LPP ==== | ||

=== GlobalFoundries === | === GlobalFoundries === | ||

| + | |||

| + | * '''Note:''' As of august 2018 GlobalFoundries has announced they will suspend further development of their 7nm, 5nm and 3nm process. | ||

| + | [[File:globalfoundries interconnect 7nm.jpg|right|350px]] | ||

| + | On May 30 2017, GlobalFoundries Senior Vice President and head of CMOS Business Unit, Gregg Bartlett, announced their updated roadmap. Instead of [[EUV]], the company will use multiple patterning 193i for their 7 nm node. The company is planning on first tape-out in the 2nd half of 2018 with mass production to begin in 2019. Bartlett noted that GF will switch to EUVL when it's ready. | ||

| + | |||

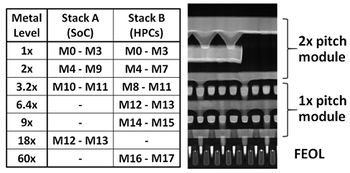

| + | The 7nm process features SAQP for the FEOL, and double patterning for the BEOL. GlobalFoundries claims a 2.8 times density improvement compared to their 14nm process, and a performance improvement of 40% or a 55% reduction in power consumption. Two versions of the process will be developed: a low power version for mobile applications. And a high performance version for desktop and server chips. | ||

==== 7LP ==== | ==== 7LP ==== | ||

==== 7HPC ==== | ==== 7HPC ==== | ||

Revision as of 00:11, 30 December 2019

The 7 nanometer (7 nm) lithography process is a technology node semiconductor manufacturing process following the 10 nm process node. Mass production of integrated circuit fabricated using a 7 nm process begun in 2018. The process technology will be phased out by leading-edge foundries by 2020/21 timeframe where it will be replaced by the 5 nm node.

The term "7 nm" is simply a commercial name for a generation of a certain size and its technology, and does not represent any geometry of the transistor.

Contents

Overview

First introduced by the major foundries around the 2018-19 timeframe, the 7-nanometer process technology is characterized by its use of FinFET transistors with fin pitches in the 30s of nanometer and densest metal pitches in the upper 30s or low 40s of nanometers. Due to the small feature sizes, quad patterning had to be utilized for some layers. This process was introduced just as EUV Lithography became ready for mass production, therefore some foundries utilized EUV while others didn't. Note that Intel 10 nm process is comparable to the foundry 7-nanometer node.

Density

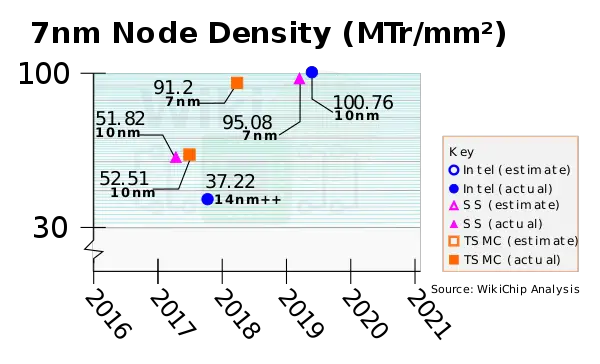

In terms of raw cell-level density, the 7-nanometer node features silicon densities between 90-105 million transistors per square millimeter based on WikiChip's own analysis.

Industry

Only three companies are currently planning or developing a 5-nanometer node: Intel, TSMC, and Samsung.

| Intel | TSMC | Samsung | GlobalFoundries | ||||||

|---|---|---|---|---|---|---|---|---|---|

| Process | P1276 (CPU), P1277 (SoC) | N7, N7P, N7+ | 7LPE, 7LPP | ||||||

| Production | 2021 | April 2018 | April 2019 | Cancelled | |||||

| Litho | Lithography | EUV | DUV ⇒ EUV | EUV | DUV ⇒ EUV | ||||

| Immersion Exposure | SADP ⇒ SE (EUV) DP (193i) | SE (EUV) DP (193i) | SADP ⇒ SE (EUV) DP (193i) | ||||||

| Wafer | Type | Bulk | |||||||

| Size | 300 mm | ||||||||

| xTor | Type | FinFET | |||||||

| Voltage | |||||||||

| Value | 10 nm Δ | Value | 10 nm Δ | Value | 10 nm Δ | Value | 14 nm Δ | ||

| Fin | Pitch | 30 nm | 0.83x | 27 nm | 0.64x | 30 nm | 0.625x | ||

| Width | 6 nm | 1.00x | |||||||

| Height | 52 nm | 1.24x | |||||||

| Gate Length (Lg) | 8/10 nm | ||||||||

| Contacted Gate Pitch (CPP) | 64 nm (HP) 57 nm (HD) | 0.82x | 60 nm (HP) 54 nm (HD) | 0.79x | 56 nm | 0.72x | |||

| Minimum Metal Pitch (MMP) | 40 nm | 0.95x | 36 nm | 0.75x | 40 nm | 0.625x | |||

| SRAM | High-Perf (HP) | 0.032 µm² | 0.65x | 0.0353 µm² | 0.44x | ||||

| High-Density (HD) | 0.027 µm² | 0.64x | 0.026 µm² | 0.65x | 0.0269 µm² | 0.42x | |||

| Low-Voltage (LV) | |||||||||

Intel

P1276

Intel's 7-nanometer process, P1276, will enter risk production at the end of 2020 and ramp in 2021. On February 8 2017 Intel announced a $7B investment in Arizona's Fab 42 which will eventually produce chips on a 7 nm process.

Intel has not disclosed the details of the process but the company's current CEO claims it will feature a density that is 2x that of Intel's 10-nanometer node. Intel's prior CEO, Brian Krzanich, mentioned that 7-nanometer will have "2.4x the compaction ratio" of 10 nm. This puts the 7-nanometer node at around 202-250 transistors per square millimeter.

TSMC

In ISSCC 2017, the memory group at TSMC detailed their test 256 Mib SRAM chip which featured a 42.64 mm² die. The chip is manufactured on TSMC's 7nm HK-MG FinFET process using SAQP. The over die is 0.34x the size of their 16 nm process version. TSMC's 7nm process density is 1.6X compared to their 10nm process. Minimum metal pitch is 40 nm, as reported at IEDM 2016. TSMC claims their 7nm process will deliver a 20% performance improvement and a 40% reduction in power consumption.

The 7nm node will come in two variants, one optimized for mobile applications and a second one optimized for High Performance applications. TSMC plans to introduce a second improved process called 7nm+ a year later, which will introduce some layers processed with EUVL. This will improve yields and reduce fab cycle times. The 7nm+ process will deliver improved power consumption and between 15-20% area scaling over their first generation 7nm process.

N7

N7P

Samsung

Samsung will use EUVL for their 7nm node and thus will be the first to introduce this new technology after more than a decade of development. On May 24 2017, Samsung released a press release of their updated roadmap. Due to delays in the introduction of EUVL, Samsung will introduce a new process called 8nm LPP, to bridge the gap between 10nm and 7nm. The process will be manufactured without the use of EUVL and will feature a slightly relaxed transistor size.

7LPE

7LPP

GlobalFoundries

- Note: As of august 2018 GlobalFoundries has announced they will suspend further development of their 7nm, 5nm and 3nm process.

On May 30 2017, GlobalFoundries Senior Vice President and head of CMOS Business Unit, Gregg Bartlett, announced their updated roadmap. Instead of EUV, the company will use multiple patterning 193i for their 7 nm node. The company is planning on first tape-out in the 2nd half of 2018 with mass production to begin in 2019. Bartlett noted that GF will switch to EUVL when it's ready.

The 7nm process features SAQP for the FEOL, and double patterning for the BEOL. GlobalFoundries claims a 2.8 times density improvement compared to their 14nm process, and a performance improvement of 40% or a 55% reduction in power consumption. Two versions of the process will be developed: a low power version for mobile applications. And a high performance version for desktop and server chips.

7LP

7HPC

7 nm Microprocessors

- PEZY

- MediaTek

- Apple

- HiSilicon (Huawei)

- Snapdragon (Qualcomm)

This list is incomplete; you can help by expanding it.

7 nm Microarchitectures

- AMD

- Ampere

- Esperanto

- Intel

Semiconductor lithography processes technology

Semiconductor lithography processes technology