(→Industry) |

(fixed) |

||

| (37 intermediate revisions by 15 users not shown) | |||

| Line 1: | Line 1: | ||

{{lithography processes}} | {{lithography processes}} | ||

| − | The '''14 nanometer (14 nm) lithography process''' is a semiconductor manufacturing [[process node]] serving as [[process shrink|shrink]] from the [[22 nm process]]. The term "14 nm" is simply a commercial name for a generation of a certain size and its technology, as opposed to gate length or half pitch. The 14 nm node was introduced in 2014/2015 and | + | The '''14 nanometer (14 nm) lithography process''' is a semiconductor manufacturing [[process node]] serving as [[process shrink|shrink]] from the [[22 nm process]]. <br> |

| + | The term "14 nm" is simply a commercial name for a generation of a certain size and its technology, as opposed to gate length or half pitch. | ||

| + | :The 14 nm node was introduced in 2014/2015 and has been replaced by the [[10 nm process]]. | ||

== Industry == | == Industry == | ||

| + | === Composition === | ||

| + | [[File:intel 14nm relative density.png|left|200px]] | ||

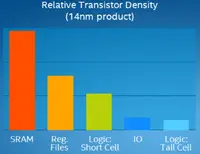

| + | It's important to note that not all processes compete with each other. The process should cater to the products that will make use of the underlying technology. The composition of the actual integrated circuit also varies by manufacturer and by design due to different goals. | ||

| + | |||

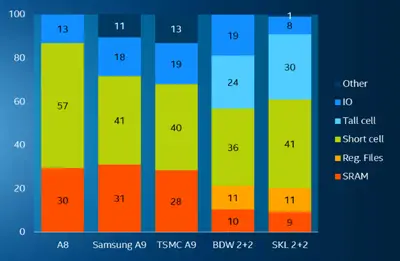

| + | For example, the cache on [[Apple]]'s 14 nm {{apple|A9}} (manufactured by Samsung) accounts almost 1/3 of the entire chip whereas [[Intel]]'s {{intel|Broadwell|l=arch}} cache accounts for only 10% of the entire chip. Likewise, [[Intel]]'s {{intel|Broadwell|l=arch}} and {{intel|Skylake|l=arch}} target high-performance and incorporate a large amount of higher-speed elements which are inherently sparse. | ||

| + | |||

| + | [[File:relative percentage of elements on 14nm chip.png|left|400px]] | ||

| + | Tall cells account for almost 30% Skylake's composition and less than 1% on Apple's {{apple|A8}} or {{apple|A9}}. Those numbers are somewhat expected given tall logic cells are generally optimized for performance and high frequency (e.g., high-switching circuitry in the [[CPU]]) whereas short cells are optimized for density (e.g., GPU shader arrays). | ||

| + | |||

| + | It should be noted that [[SRAM]] is the densest component of the process in a chip, with sometimes up to three or four times the density of logic cells that are used in the same process. It should be noted that in recent years, SRAM hasn't scaled as well as logic and I/O have either. | ||

| + | |||

| + | === Intel === | ||

| + | [[File:intel 14nm gate.png|left|250px]] | ||

| + | {{see also|intel/process|l1=Intel's Process Technology History}} | ||

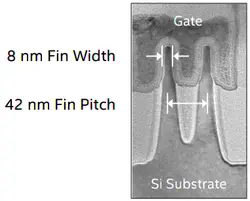

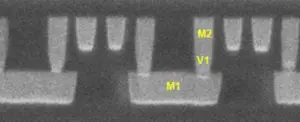

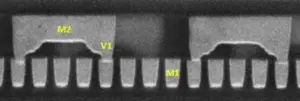

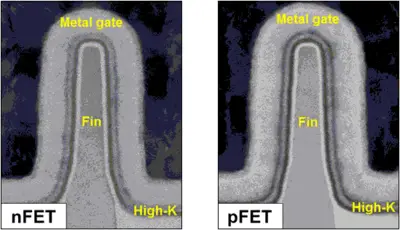

| + | Intel got off to a bumpy start with major yield problems initially, but by {{intel|Skylake|l=arch}} yield has reached very healthy numbers. 14 nm became [[Intel]]'s 2nd generation FinFET transistors. Intel uses TiN pMOS / TiAlN nMOS as work function metals. Intel makes use of 193 nm immersion lithography with [[Self-Aligned Double Patterning]] (SADP) at the critical patterning layers. Compared to all other "14 nm nodes", Intel's process is the densest and considerably so, with >1.5x raw logic density. | ||

| + | Intel's 14 nm process has gone through multiple refinements optimizing higher clock speed, higher drive current, and lower power dissipation. The original "14nm" was used for their {{intel|Broadwell|l=arch}} and mainstream {{intel|Skylake|l=arch}} processors. They improved on their original process with a second process, "14nm+", offering 12% higher drive current at lower power. That process has been used for both {{intel|Kaby Lake|l=arch}} and Server/HEDT {{intel|Skylake SP|l=core}}/{{intel|Skylake X|X|l=core}} processors. | ||

| + | |||

| + | A third improved process, "14nm++", is set to begin in late 2017 and will further allow for +23-24% higher drive current for 52% less power vs the original 14nm process. The 14nm++ process also appear to have slightly relaxed poly pitch of 84 nm (from 70 nm). It's unknown what impact, if any, this will have on the density. | ||

| + | |||

| + | {| class="wikitable collapsible collapsed" | ||

| + | |- | ||

| + | ! colspan="3" | Intel 14nm Design Rules | ||

| + | |- | ||

| + | ! Layer !! Pitch !! Scale Factor | ||

| + | |- | ||

| + | | Fin || 42 nm || 0.70 | ||

| + | |- | ||

| + | | Contacted Gate Pitch || 70 nm || 0.78 | ||

| + | |- | ||

| + | | Metal 0 || 56 || - | ||

| + | |- | ||

| + | | Metal 1 || 70 || 0.78 | ||

| + | |- | ||

| + | | Metal 2 || 52 || 0.65 | ||

| + | |} | ||

| + | |||

| + | === Specifications === | ||

{{finfet nodes comp | {{finfet nodes comp | ||

<!-- Intel --> | <!-- Intel --> | ||

| process 1 fab = [[Intel]] | | process 1 fab = [[Intel]] | ||

| − | | process 1 name = P1272 (CPU) | + | | process 1 name = P1272<!--(CPU)-->, P1273<!--(SoC)--> |

| process 1 date = 2014 | | process 1 date = 2014 | ||

| process 1 lith = 193 nm | | process 1 lith = 193 nm | ||

| Line 38: | Line 77: | ||

| process 1 dram Δ = | | process 1 dram Δ = | ||

<!-- Samsung --> | <!-- Samsung --> | ||

| − | | process 2 fab = [[Samsung]] | + | | process 2 fab = [[Samsung]] <info>'''Samsung''' consists of a process development collaboration between [[Samsung]] and [[GlobalFoundries]]. GlobalFoundries licenses Samsung's 14nm process at Fab8, New York.</info> |

| − | | process 2 name = 14LPE<info>1<sup>st</sup> generation; 14 nm Low Power Early</info> | + | | process 2 name = 14LPE<info>1<sup>st</sup> generation; 14 nm Low Power Early</info>/LPP<info>2<sup>nd</sup> generation; 14 nm Low Power Performance</info>/LPC<info>3<sup>rd</sup> generation; 14 nm Low Power Cost [reduced]</info>/LPU<info>4<sup>th</sup> generation; 14 nm Low Power Ultimate</info> |

| process 2 date = 2015 | | process 2 date = 2015 | ||

| process 2 lith = 193 nm | | process 2 lith = 193 nm | ||

| Line 53: | Line 92: | ||

| process 2 fin width = 8 nm | | process 2 fin width = 8 nm | ||

| process 2 fin width Δ = | | process 2 fin width Δ = | ||

| − | | process 2 fin height = | + | | process 2 fin height = 37 nm |

| process 2 fin height Δ = | | process 2 fin height Δ = | ||

| process 2 gate len = 30 nm | | process 2 gate len = 30 nm | ||

| Line 70: | Line 109: | ||

| process 2 dram Δ = | | process 2 dram Δ = | ||

<!-- IBM --> | <!-- IBM --> | ||

| − | | process 3 fab = [[IBM]] | + | | process 3 fab = [[IBM]] (GF) <info>(Now GlobalFoundries)</info> |

| process 3 name = 14HP<info>14nm High Performance</info> | | process 3 name = 14HP<info>14nm High Performance</info> | ||

| process 3 date = 2017 | | process 3 date = 2017 | ||

| Line 106: | Line 145: | ||

| process 4 date = 2Q 2017 | | process 4 date = 2Q 2017 | ||

| process 4 lith = 193 nm | | process 4 lith = 193 nm | ||

| − | | process 4 immersion = | + | | process 4 immersion = Yes |

| process 4 exposure = | | process 4 exposure = | ||

| − | | process 4 wafer type = | + | | process 4 wafer type = Bulk |

| process 4 wafer size = 300 mm | | process 4 wafer size = 300 mm | ||

| process 4 transistor = FinFET | | process 4 transistor = FinFET | ||

| Line 134: | Line 173: | ||

| process 4 dram Δ = | | process 4 dram Δ = | ||

<!-- UMC --> | <!-- UMC --> | ||

| − | | process 5 fab = [[Common Platform Alliance]] | + | | process 5 fab = [[STMicro]] <info>[[Common Platform Alliance]] - The '''Common Platform Alliance''' is a joint collaboration between [[IBM]], [[STMicroelectronics]]</info> |

| process 5 name = 14FDSOI | | process 5 name = 14FDSOI | ||

| process 5 date = | | process 5 date = | ||

| Line 165: | Line 204: | ||

| process 5 dram = | | process 5 dram = | ||

| process 5 dram Δ = | | process 5 dram Δ = | ||

| + | <!-- SMIC --> | ||

| + | | process 6 fab = [[SMIC]] | ||

| + | | process 6 name = 14FinFET | ||

| + | | process 6 date = | ||

| + | | process 6 lith = 193 nm | ||

| + | | process 6 immersion = Yes | ||

| + | | process 6 exposure = | ||

| + | | process 6 wafer type = | ||

| + | | process 6 wafer size = 300 mm | ||

| + | | process 6 transistor = FinFET | ||

| + | | process 6 volt = | ||

| + | | process 6 delta from = [[ ]] Δ | ||

| + | | process 6 fin pitch = - | ||

| + | | process 6 fin pitch Δ = | ||

| + | | process 6 fin width = | ||

| + | | process 6 fin width Δ = | ||

| + | | process 6 fin height = | ||

| + | | process 6 fin height Δ = | ||

| + | | process 6 gate len = | ||

| + | | process 6 gate len Δ = | ||

| + | | process 6 cpp = | ||

| + | | process 6 cpp Δ = | ||

| + | | process 6 mmp = | ||

| + | | process 6 mmp Δ = | ||

| + | | process 6 sram hp = | ||

| + | | process 6 sram hp Δ = | ||

| + | | process 6 sram hd = | ||

| + | | process 6 sram hd Δ = | ||

| + | | process 6 sram lv = | ||

| + | | process 6 sram lv Δ = | ||

| + | | process 6 dram = | ||

| + | | process 6 dram Δ = <br>. | ||

}} | }} | ||

| − | === | + | === Samsung === |

| − | [[File: | + | [[File:ss 14-10nm.png|right|500px]] |

| − | + | === 14LPE, 14LPP === | |

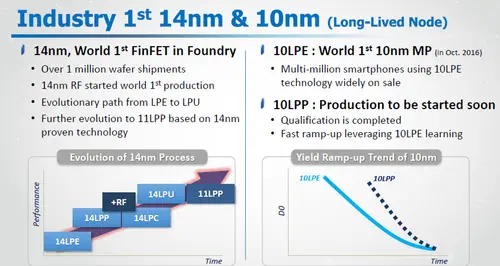

| − | + | This process became Samsung's and GlobalFoundries first generation of FinFET-based transistors. Samsung uses TiN pMOS / TiAIC nMOS as work function metals. Samsung node has gone through a number of refinements from 14LPE (14 Low-Power Early) to 14LPP (14 Low-Power Performance) and further. | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | === 11LPP === | |

| − | + | In late 2017, Samsung announced "11LPP" (11 Low-Power Plus) which is a further enhancement of 14LPP. 11LPP is reported to deliver up to 15% higher performance with enhanced design rules that allow for up to 10% reduction in area. Samsung expects 11LPP to enter mass production in late 2017 or early 2018. | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

=== IBM === | === IBM === | ||

| Line 205: | Line 252: | ||

IBM's HP 14nm CMOS process features a [[FinFET]] architecture on an [[silicon-on-insulator|SOI]] substrate. The use of SOI with [[FinFET]] gives IBM a number of unique advantages such as lower [[parasitic capacitance]] at the base of the fin as well as simplifies patterning of the active fins and minimizes their variability such as height and thickness. The architecture also includes high-density deep-trench [[embedded DRAM]] cells with a reported size of 0.0174 µm². The process features an L<sub>gate</sub> of 20nm and smaller (18nm to 27nm) which IBM reported to result in over 35% performance gain verses their HP 22nm process (for identical V<sub>dd</sub> = 0.80 V). | IBM's HP 14nm CMOS process features a [[FinFET]] architecture on an [[silicon-on-insulator|SOI]] substrate. The use of SOI with [[FinFET]] gives IBM a number of unique advantages such as lower [[parasitic capacitance]] at the base of the fin as well as simplifies patterning of the active fins and minimizes their variability such as height and thickness. The architecture also includes high-density deep-trench [[embedded DRAM]] cells with a reported size of 0.0174 µm². The process features an L<sub>gate</sub> of 20nm and smaller (18nm to 27nm) which IBM reported to result in over 35% performance gain verses their HP 22nm process (for identical V<sub>dd</sub> = 0.80 V). | ||

| − | |||

{| class="wikitable collapsible collapsed" | {| class="wikitable collapsible collapsed" | ||

| Line 230: | Line 276: | ||

|} | |} | ||

| − | === | + | === GlobalFoundries === |

| − | + | Building on top of Samsung's licensed 14nm process, GlobalFoundries announced the "12LP" (12 nm Leading Performance) process in late 2017 which is said to deliver up to 15% increase in density and 10% increase in performance through further cell optimization such as [[track reduction]]. | |

| − | |||

| − | |||

| − | Building on top of Samsung's licensed 14nm process, GlobalFoundries announced "12LP" in late 2017 which | ||

| − | |||

| − | |||

=== UMC === | === UMC === | ||

| + | [[File:UMC_14nm_finfet.png|left|400px]] | ||

UMC announced the start of 14nm process mass production in February 2017. The 14nm process is their first process to use FinFET, and provides up to 55% higher performance and twice the gate density compared to their 28nm process. | UMC announced the start of 14nm process mass production in February 2017. The 14nm process is their first process to use FinFET, and provides up to 55% higher performance and twice the gate density compared to their 28nm process. | ||

| − | |||

{{clear}} | {{clear}} | ||

| Line 262: | Line 303: | ||

== 14 nm Microprocessors== | == 14 nm Microprocessors== | ||

| − | * AMD | + | ::* '''[[AMD]] |

{{collist | {{collist | ||

| count = 4 | | count = 4 | ||

| style = padding-left: 30px | | style = padding-left: 30px | ||

| | | | ||

| − | * {{amd| | + | * '''{{amd|Ryzen}}''' |

* {{amd|Ryzen 3}} | * {{amd|Ryzen 3}} | ||

* {{amd|Ryzen 5}} | * {{amd|Ryzen 5}} | ||

* {{amd|Ryzen 7}} | * {{amd|Ryzen 7}} | ||

| + | |||

| + | * '''{{amd|EPYC}}''' | ||

| + | * {{amd|EPYC Embedded}} | ||

| + | * {{amd|Ryzen Embedded}} | ||

| + | * {{amd|Ryzen Threadripper}} | ||

}} | }} | ||

| − | * | + | ::* '''[[Intel]]''' |

| − | |||

| − | |||

{{collist | {{collist | ||

| − | | count = | + | | count = 4 |

| style = padding-left: 30px | | style = padding-left: 30px | ||

| | | | ||

| + | * '''{{intel|Atom}}''' | ||

* {{intel|Atom x5}} | * {{intel|Atom x5}} | ||

* {{intel|Atom x7}} | * {{intel|Atom x7}} | ||

| + | |||

* {{intel|Core i3}} | * {{intel|Core i3}} | ||

* {{intel|Core i5}} | * {{intel|Core i5}} | ||

| − | * {{intel|Core i7}} | + | * {{intel|Core i7}} ({{intel|Core i7EE|EE}}) |

| − | * {{intel|Core | + | * {{intel|Core i9}} |

| + | |||

* {{intel|pentium (2009)|Pentium}} | * {{intel|pentium (2009)|Pentium}} | ||

| + | * {{intel|Pentium Gold}} | ||

| + | * {{intel|Pentium Silver}} | ||

* {{intel|Celeron}} | * {{intel|Celeron}} | ||

| − | + | ||

| − | * {{intel|Xeon | + | * '''{{intel|Xeon}}''' |

* {{intel|Xeon D}} | * {{intel|Xeon D}} | ||

| − | + | * {{intel|Xeon E5}} (E3) | |

| − | * {{intel|Xeon E5}} | ||

* {{intel|Xeon E7}} | * {{intel|Xeon E7}} | ||

| + | |||

| + | * {{intel|Xeon Bronze}} | ||

| + | * {{intel|Xeon Silver}} | ||

* {{intel|Xeon Gold}} | * {{intel|Xeon Gold}} | ||

* {{intel|Xeon Platinum}} | * {{intel|Xeon Platinum}} | ||

| − | |||

}} | }} | ||

| + | * Apple | ||

| + | ** {{apple|Ax}} | ||

* Samsung | * Samsung | ||

** {{samsung|Exynos}} | ** {{samsung|Exynos}} | ||

| + | * NXP | ||

| + | ** {{nxp|i.MX 8M Mini}} | ||

{{expand list}} | {{expand list}} | ||

== 14 nm Microarchitectures== | == 14 nm Microarchitectures== | ||

| − | * Intel | + | ::* '''[[Intel]]''' |

| − | + | {{collist | |

| − | ** {{intel| | + | | count = 4 |

| − | ** {{intel| | + | | style = padding-left: 30px |

| − | ** {{intel| | + | | |

| − | ** {{intel| | + | * {{intel|Airmont|l=arch}} |

| − | ** {{intel| | + | * {{intel|Goldmont|l=arch}} |

| − | * AMD | + | * {{intel|Broadwell|l=arch}} |

| − | ** {{amd|Zen|l=arch}} | + | * {{intel|Skylake|l=arch}} |

| − | * IBM | + | |

| − | + | * {{intel|Kaby Lake|l=arch}} | |

| − | + | * {{intel|Coffee Lake|l=arch}} | |

| + | * {{intel|Whiskey Lake|l=arch}} | ||

| + | * {{intel|Amber Lake|l=arch}} | ||

| + | |||

| + | * {{intel|Comet Lake|l=arch}} | ||

| + | * {{intel|Cascade Lake|l=arch}} | ||

| + | * {{intel|Cooper Lake|l=arch}} | ||

| + | * {{intel|Rocket Lake|l=arch}} | ||

| + | |||

| + | * '''[[AMD]]''' | ||

| + | |||

| + | * {{amd|Zen|l=arch}} | ||

| + | * {{amd|Zen refresh|l=arch}} | ||

| + | * {{amd|Arctic Islands|l=arch}} | ||

| + | * {{amd|Vega|l=arch}} | ||

| + | |||

| + | * '''[[IBM]]''' | ||

| + | * {{ibm|POWER9|l=arch}} | ||

| + | * {{ibm|z14|l=arch}} | ||

| + | |||

| + | * '''[[Samsung]]''' | ||

| + | * {{samsung|Mongoose 1|l=arch}} | ||

| + | }} | ||

{{expand list}} | {{expand list}} | ||

| Line 321: | Line 397: | ||

* [[:File:14-nm-technology-fact-sheet.pdf|Intel's 14 nm Technology: Delivering Ultrafast, Energy-Sipping Products]] | * [[:File:14-nm-technology-fact-sheet.pdf|Intel's 14 nm Technology: Delivering Ultrafast, Energy-Sipping Products]] | ||

* [[:File:2015 InvestorMeeting Bill Holt WEB2.pdf|Intel's 14nm, Advancing Moore's Law, investor meeting]] | * [[:File:2015 InvestorMeeting Bill Holt WEB2.pdf|Intel's 14nm, Advancing Moore's Law, investor meeting]] | ||

| + | * [[:File:Ruth-Brain-2017-Manufacturing.pdf|Intel's 14 nm technology leadership, Dr. Ruth Brain]] | ||

== References == | == References == | ||

| Line 330: | Line 407: | ||

* Chen, Shyng-Tsong, et al. "64 nm pitch Cu dual-damascene interconnects using pitch split double exposure patterning scheme." Interconnect Technology Conference and 2011 Materials for Advanced Metallization (IITC/MAM), 2011 IEEE International. IEEE, 2011. | * Chen, Shyng-Tsong, et al. "64 nm pitch Cu dual-damascene interconnects using pitch split double exposure patterning scheme." Interconnect Technology Conference and 2011 Materials for Advanced Metallization (IITC/MAM), 2011 IEEE International. IEEE, 2011. | ||

| − | [[ | + | [[category:lithography]] |

Latest revision as of 19:34, 19 March 2025

The 14 nanometer (14 nm) lithography process is a semiconductor manufacturing process node serving as shrink from the 22 nm process.

The term "14 nm" is simply a commercial name for a generation of a certain size and its technology, as opposed to gate length or half pitch.

- The 14 nm node was introduced in 2014/2015 and has been replaced by the 10 nm process.

Contents

Industry[edit]

Composition[edit]

It's important to note that not all processes compete with each other. The process should cater to the products that will make use of the underlying technology. The composition of the actual integrated circuit also varies by manufacturer and by design due to different goals.

For example, the cache on Apple's 14 nm A9 (manufactured by Samsung) accounts almost 1/3 of the entire chip whereas Intel's Broadwell cache accounts for only 10% of the entire chip. Likewise, Intel's Broadwell and Skylake target high-performance and incorporate a large amount of higher-speed elements which are inherently sparse.

Tall cells account for almost 30% Skylake's composition and less than 1% on Apple's A8 or A9. Those numbers are somewhat expected given tall logic cells are generally optimized for performance and high frequency (e.g., high-switching circuitry in the CPU) whereas short cells are optimized for density (e.g., GPU shader arrays).

It should be noted that SRAM is the densest component of the process in a chip, with sometimes up to three or four times the density of logic cells that are used in the same process. It should be noted that in recent years, SRAM hasn't scaled as well as logic and I/O have either.

Intel[edit]

- See also: Intel's Process Technology History

Intel got off to a bumpy start with major yield problems initially, but by Skylake yield has reached very healthy numbers. 14 nm became Intel's 2nd generation FinFET transistors. Intel uses TiN pMOS / TiAlN nMOS as work function metals. Intel makes use of 193 nm immersion lithography with Self-Aligned Double Patterning (SADP) at the critical patterning layers. Compared to all other "14 nm nodes", Intel's process is the densest and considerably so, with >1.5x raw logic density. Intel's 14 nm process has gone through multiple refinements optimizing higher clock speed, higher drive current, and lower power dissipation. The original "14nm" was used for their Broadwell and mainstream Skylake processors. They improved on their original process with a second process, "14nm+", offering 12% higher drive current at lower power. That process has been used for both Kaby Lake and Server/HEDT Skylake SP/X processors.

A third improved process, "14nm++", is set to begin in late 2017 and will further allow for +23-24% higher drive current for 52% less power vs the original 14nm process. The 14nm++ process also appear to have slightly relaxed poly pitch of 84 nm (from 70 nm). It's unknown what impact, if any, this will have on the density.

| Intel 14nm Design Rules | ||

|---|---|---|

| Layer | Pitch | Scale Factor |

| Fin | 42 nm | 0.70 |

| Contacted Gate Pitch | 70 nm | 0.78 |

| Metal 0 | 56 | - |

| Metal 1 | 70 | 0.78 |

| Metal 2 | 52 | 0.65 |

Specifications[edit]

| Process Name | |

|---|---|

| 1st Production | |

| Litho- graphy |

Lithography |

| Immersion | |

| Exposure | |

| Wafer | Type |

| Size | |

| Tran- sistor |

Type |

| Voltage | |

| Fin | Pitch |

| Width | |

| Height | |

| Gate Length (Lg) | |

| Contacted Gate Pitch (CPP) | |

| Minimum Metal Pitch (MMP) | |

| SRAM bitcell |

High-Perf (HP) |

| High-Density (HD) | |

| Low-Voltage (LV) | |

| DRAM bitcell |

eDRAM |

| Intel | Samsung Samsung consists of a process development collaboration between Samsung and GlobalFoundries. GlobalFoundries licenses Samsung's 14nm process at Fab8, New York. |

IBM (GF) (Now GlobalFoundries) |

UMC | STMicro Common Platform Alliance - The Common Platform Alliance is a joint collaboration between IBM, STMicroelectronics |

SMIC | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| P1272, P1273 | 14LPE 1st generation; 14 nm Low Power Early /LPP2nd generation; 14 nm Low Power Performance /LPC3rd generation; 14 nm Low Power Cost [reduced] /LPU4th generation; 14 nm Low Power Ultimate |

14HP 14nm High Performance |

14FDSOI | 14FinFET | |||||||

| 2014 | 2015 | 2017 | 2Q 2017 | ||||||||

| 193 nm | 193 nm | 193 nm | 193 nm | 193 nm | 193 nm | ||||||

| Yes | Yes | Yes | Yes | Yes | Yes | ||||||

| SADP | LELE | SADP | DP | ||||||||

| Bulk | Bulk | SOI | Bulk | SOI | |||||||

| 300 mm | 300 mm | 300 mm | 300 mm | 300 mm | 300 mm | ||||||

| FinFET | FinFET | FinFET | FinFET | Planar | FinFET | ||||||

| 0.70 V | 0.80 V | 0.80 V | 0.80 V | ||||||||

| Value | 22 nm Δ | Value | 20 nm Δ | Value | 22 nm Δ | Value | 28 nm Δ | Value | 28 nm Δ | Value | [[ ]] Δ |

| 42 nm | 0.70x | 48 nm | N/A | 42 nm | N/A | N/A | N/A | ||||

| 8 nm | 1.00x | 8 nm | 10 nm | ||||||||

| 42 nm | 1.24x | 37 nm | 25 nm | ||||||||

| 20 nm | 0.77x | 30 nm | 18-26 nm | 0.72-0.79x | 20 nm | 0.71x | |||||

| 70 nm | 0.78x | 78 nm | 1.22x | 80 nm | 0.80x | 90 nm | 0.79x | ||||

| 52 nm | 0.65x | 64 nm | 1.00x | 64 nm | 0.80x | 64 nm | 0.71x | ||||

| 0.0706 µm² | 0.54x | 0.080 µm² | 0.78x | 0.0900 µm² | 0.63x | 0.090 µm² | 0.59x | ||||

| 0.0499 µm² | 0.54x | 0.064 µm² | 0.79x | 0.0810 µm² | 0.81x | 0.081 µm² | 0.68x | ||||

| 0.0588 µm² | 0.54x | ||||||||||

| 0.0174 µm² | 0.67x | . | |||||||||

Samsung[edit]

14LPE, 14LPP[edit]

This process became Samsung's and GlobalFoundries first generation of FinFET-based transistors. Samsung uses TiN pMOS / TiAIC nMOS as work function metals. Samsung node has gone through a number of refinements from 14LPE (14 Low-Power Early) to 14LPP (14 Low-Power Performance) and further.

11LPP[edit]

In late 2017, Samsung announced "11LPP" (11 Low-Power Plus) which is a further enhancement of 14LPP. 11LPP is reported to deliver up to 15% higher performance with enhanced design rules that allow for up to 10% reduction in area. Samsung expects 11LPP to enter mass production in late 2017 or early 2018.

IBM[edit]

IBM developed their own "14HP" (14nm High-Performance) process at their East Fishkill, NY plant. Note that the plant AND the process, along with numerous semiconductor technology IPs, were sold to GlobalFoundries in late 2014. GF still operates the plant (also by ex-IBM semiconductor engineers) and the process which is used by IBM for their various processors. This process was designed by IBM for their very large chips with effective power supply and clock distribution capable of producing dies as large as 700 mm² and larger with a hierarchical BEOL of 17 levels of copper interconnect for high performance wire-ability. It should be noted that GlobalFoundries had no such capabilities prior to their acquisition of IBM's plant, semiconductor manufacturing group, and IP portfolio.

IBM's HP 14nm CMOS process features a FinFET architecture on an SOI substrate. The use of SOI with FinFET gives IBM a number of unique advantages such as lower parasitic capacitance at the base of the fin as well as simplifies patterning of the active fins and minimizes their variability such as height and thickness. The architecture also includes high-density deep-trench embedded DRAM cells with a reported size of 0.0174 µm². The process features an Lgate of 20nm and smaller (18nm to 27nm) which IBM reported to result in over 35% performance gain verses their HP 22nm process (for identical Vdd = 0.80 V).

| IBM 14nm Design Rules | ||

|---|---|---|

| Layer | Pitch | |

| Fin | 42 nm | |

| Contacted Gate Pitch | 80 nm | |

| Metal 1 | 64 nm | |

| Metal 2 | 80 nm | |

| Metal 3 | 128 nm | |

| Metal 4 | 256 nm | |

| Metal 5 | 512 nm | |

| Metal 6 | 2.56 µm | |

GlobalFoundries[edit]

Building on top of Samsung's licensed 14nm process, GlobalFoundries announced the "12LP" (12 nm Leading Performance) process in late 2017 which is said to deliver up to 15% increase in density and 10% increase in performance through further cell optimization such as track reduction.

UMC[edit]

UMC announced the start of 14nm process mass production in February 2017. The 14nm process is their first process to use FinFET, and provides up to 55% higher performance and twice the gate density compared to their 28nm process.

Find models[edit]

Click to browse all 14 nm MPU models

14 nm Microprocessors[edit]

- Apple

- Samsung

- NXP

This list is incomplete; you can help by expanding it.

14 nm Microarchitectures[edit]

This list is incomplete; you can help by expanding it.

Documents[edit]

- Intel's 14 nm Technology: Delivering Ultrafast, Energy-Sipping Products

- Intel's 14nm, Advancing Moore's Law, investor meeting

- Intel's 14 nm technology leadership, Dr. Ruth Brain

References[edit]

- Natarajan, S., et al. "A 14nm logic technology featuring 2 nd-generation FinFET, air-gapped interconnects, self-aligned double patterning and a 0.0588 µm 2 SRAM cell size." Electron Devices Meeting (IEDM), 2014 IEEE International. IEEE, 2014.

- Lin, C. H., et al. "High performance 14nm SOI FinFET CMOS technology with 0.0174 µm 2 embedded DRAM and 15 levels of Cu metallization." Electron Devices Meeting (IEDM), 2014 IEEE International. IEEE, 2014.

- Jan, C-H., et al. "A 14 nm SoC platform technology featuring 2 nd generation Tri-Gate transistors, 70 nm gate pitch, 52 nm metal pitch, and 0.0499 um 2 SRAM cells, optimized for low power, high performance and high density SoC products." VLSI Technology (VLSI Technology), 2015 Symposium on. IEEE, 2015.

- Song, Taejoong, et al. "A 14 nm FinFET 128 Mb SRAM With VMIN Enhancement Techniques for Low-Power Applications." IEEE Journal of Solid-State Circuits 50.1 (2015): 158-169.

- Weber, Olivier, et al. "14nm FDSOI technology for high speed and energy efficient applications." VLSI Technology (VLSI-Technology): Digest of Technical Papers, 2014 Symposium on. IEEE, 2014.

- Chen, Shyng-Tsong, et al. "64 nm pitch Cu dual-damascene interconnects using pitch split double exposure patterning scheme." Interconnect Technology Conference and 2011 Materials for Advanced Metallization (IITC/MAM), 2011 IEEE International. IEEE, 2011.

Semiconductor lithography processes technology

Semiconductor lithography processes technology