From WikiChip

Difference between revisions of "32 nm lithography process"

(→Industry) |

(→Industry) |

||

| (26 intermediate revisions by 5 users not shown) | |||

| Line 1: | Line 1: | ||

{{lithography processes}} | {{lithography processes}} | ||

| − | The '''32 nm lithography process''' is a [[technology node|full node]] semiconductor manufacturing process following the [[40 nm lithography process|40 nm process]] stopgap. Commercial [[integrated circuit]] manufacturing using 32 nm process began in 2010. This technology was superseded by the [[28 nm lithography process|28 nm process]] (HN) / [[22 nm lithography process|22 nm process]] (FN) in 2012. | + | The '''32 nanometer (32 nm) lithography process''' is a [[technology node|full node]] semiconductor manufacturing process following the [[40 nm lithography process|40 nm process]] stopgap. Commercial [[integrated circuit]] manufacturing using 32 nm process began in 2010. This technology was superseded by the [[28 nm lithography process|28 nm process]] (HN) / [[22 nm lithography process|22 nm process]] (FN) in 2012. |

== Industry == | == Industry == | ||

| − | TSMC cancelled its planned 32nm node process. | + | TSMC cancelled its planned 32nm node process. Intel's 32 nm process became the first process to introduce the [[self-aligned via patterning]]. |

| − | {{ | + | |

| − | | | + | {{nodes comp |

| − | | | + | <!-- Intel --> |

| − | | | + | | process 1 fab = [[Intel]] |

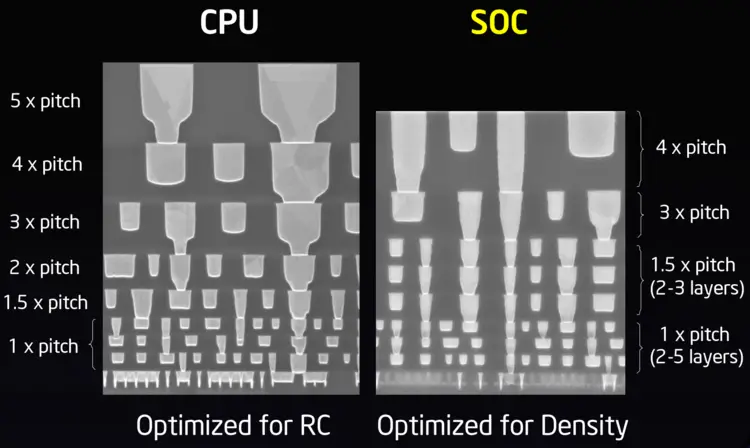

| − | | | + | | process 1 name = P1268 (CPU) / P1269 (SoC) |

| − | | | + | | process 1 date = 2009 |

| − | | | + | | process 1 lith = 193 nm |

| − | | | + | | process 1 immersion = Yes |

| − | | | + | | process 1 exposure = DP |

| − | | | + | | process 1 wafer type = Bulk |

| + | | process 1 wafer size = 300 mm | ||

| + | | process 1 transistor = Planar | ||

| + | | process 1 volt = 1 V, 0.75 V | ||

| + | | process 1 layers = 9 | ||

| + | | process 1 delta from = [[45 nm]] Δ | ||

| + | | process 1 gate len = 30 nm | ||

| + | | process 1 gate len Δ = | ||

| + | | process 1 cpp = 112.5 nm | ||

| + | | process 1 cpp Δ = 0.63x | ||

| + | | process 1 mmp = 112.5 nm | ||

| + | | process 1 mmp Δ = 0.70x | ||

| + | | process 1 sram hp = 0.199 µm² | ||

| + | | process 1 sram hp Δ = | ||

| + | | process 1 sram hd = 0.148 µm² | ||

| + | | process 1 sram hd Δ = | ||

| + | | process 1 sram lv = 0.171 µm² | ||

| + | | process 1 sram lv Δ = | ||

| + | | process 1 dram = | ||

| + | | process 1 dram Δ = | ||

| + | <!-- TSMC --> | ||

| + | | process 2 fab = [[TSMC]] | ||

| + | | process 2 name = | ||

| + | | process 2 date = | ||

| + | | process 2 lith = 193 nm | ||

| + | | process 2 immersion = Yes | ||

| + | | process 2 exposure = DP | ||

| + | | process 2 wafer type = Bulk | ||

| + | | process 2 wafer size = 300 mm | ||

| + | | process 2 transistor = Planar | ||

| + | | process 2 volt = 1.1 V | ||

| + | | process 2 layers = | ||

| + | | process 2 delta from = [[40 nm]] Δ | ||

| + | | process 2 gate len = 30 nm | ||

| + | | process 2 gate len Δ = | ||

| + | | process 2 cpp = 130 nm | ||

| + | | process 2 cpp Δ = | ||

| + | | process 2 mmp = 100 nm | ||

| + | | process 2 mmp Δ = | ||

| + | | process 2 sram hp = | ||

| + | | process 2 sram hp Δ = | ||

| + | | process 2 sram hd = 0.15 µm² | ||

| + | | process 2 sram hd Δ = | ||

| + | | process 2 sram lv = | ||

| + | | process 2 sram lv Δ = | ||

| + | | process 2 dram = | ||

| + | | process 2 dram Δ = | ||

| + | <!-- IBM --> | ||

| + | | process 3 fab = [[Common Platform Alliance]]<info>The Common Platform Alliance 20 nm node was a collaboration between [[IBM]], [[Samsung]], [[Freescale]], [[Toshiba]], [[Chartered Semiconductor Manufacturing]], [[Infineon Technologies ]]</info> | ||

| + | | process 3 name = | ||

| + | | process 3 date = 2011 | ||

| + | | process 3 lith = 193 nm | ||

| + | | process 3 immersion = Yes | ||

| + | | process 3 exposure = DP | ||

| + | | process 3 wafer type = Bulk | ||

| + | | process 3 wafer size = 300 mm | ||

| + | | process 3 transistor = Planar | ||

| + | | process 3 volt = 1 V, 0.8 V | ||

| + | | process 3 layers = 11 | ||

| + | | process 3 delta from = [[45 nm]] Δ | ||

| + | | process 3 gate len = 30 nm | ||

| + | | process 3 gate len Δ = | ||

| + | | process 3 cpp = 126 nm | ||

| + | | process 3 cpp Δ = | ||

| + | | process 3 mmp = 100 nm | ||

| + | | process 3 mmp Δ = | ||

| + | | process 3 sram hp = | ||

| + | | process 3 sram hp Δ = | ||

| + | | process 3 sram hd = 0.157 µm² | ||

| + | | process 3 sram hd Δ = | ||

| + | | process 3 sram lv = | ||

| + | | process 3 sram lv Δ = | ||

| + | | process 3 dram = | ||

| + | | process 3 dram Δ = | ||

| + | <!-- Toshiba --> | ||

| + | | process 4 fab = [[Toshiba]] / [[NEC]] | ||

| + | | process 4 name = | ||

| + | | process 4 date = | ||

| + | | process 4 lith = 193 nm | ||

| + | | process 4 immersion = Yes | ||

| + | | process 4 exposure = DP | ||

| + | | process 4 wafer type = Bulk | ||

| + | | process 4 wafer size = 300 mm | ||

| + | | process 4 transistor = Planar | ||

| + | | process 4 volt = 1 V | ||

| + | | process 4 layers = | ||

| + | | process 4 delta from = [[40 nm]] Δ | ||

| + | | process 4 gate len = | ||

| + | | process 4 gate len Δ = | ||

| + | | process 4 cpp = 120 nm | ||

| + | | process 4 cpp Δ = | ||

| + | | process 4 mmp = 100 nm | ||

| + | | process 4 mmp Δ = | ||

| + | | process 4 sram hp = | ||

| + | | process 4 sram hp Δ = | ||

| + | | process 4 sram hd = 0.124 µm² | ||

| + | | process 4 sram hd Δ = | ||

| + | | process 4 sram lv = | ||

| + | | process 4 sram lv Δ = | ||

| + | | process 4 dram = | ||

| + | | process 4 dram Δ = | ||

| + | <!-- IBM SOI --> | ||

| + | | process 5 fab = [[Common Platform Alliance]] (SOI)<info>[[IBM]], [[Freescale]], [[AMD]]</info> | ||

| + | | process 5 name = | ||

| + | | process 5 date = | ||

| + | | process 5 lith = 193 nm | ||

| + | | process 5 immersion = Yes | ||

| + | | process 5 exposure = DP | ||

| + | | process 5 wafer type = SOI | ||

| + | | process 5 wafer size = 300 mm | ||

| + | | process 5 transistor = Planar | ||

| + | | process 5 volt = 1 V | ||

| + | | process 5 layers = 11 | ||

| + | | process 5 delta from = [[45 nm]] Δ | ||

| + | | process 5 gate len = 25 nm | ||

| + | | process 5 gate len Δ = | ||

| + | | process 5 cpp = 130 nm | ||

| + | | process 5 cpp Δ = | ||

| + | | process 5 mmp = 100 nm | ||

| + | | process 5 mmp Δ = | ||

| + | | process 5 sram hp = | ||

| + | | process 5 sram hp Δ = | ||

| + | | process 5 sram hd = 0.149 µm² | ||

| + | | process 5 sram hd Δ = | ||

| + | | process 5 sram lv = | ||

| + | | process 5 sram lv Δ = | ||

| + | | process 5 dram = 0.039 µm² | ||

| + | | process 5 dram Δ = | ||

}} | }} | ||

| − | + | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

=== Design Rules === | === Design Rules === | ||

{| class="wikitable collapsible collapsed" | {| class="wikitable collapsible collapsed" | ||

|- | |- | ||

| − | ! colspan=" | + | ! colspan="5" | Intel 32nm Design Rules |

|- | |- | ||

| − | ! Layer !! Pitch !! Thick !! Aspect Ratio | + | ! Layer !! Pitch !! Thick !! Aspect Ratio !! Image |

|- | |- | ||

| − | | Isolation || 140 nm || 200 || - | + | | Isolation || 140 nm || 200 || - || rowspan="12" | [[file:intel 32nm design rules.png|750px]] |

|- | |- | ||

| Contacted Gate || 112.5 nm || 35 nm || -- | | Contacted Gate || 112.5 nm || 35 nm || -- | ||

| Line 65: | Line 171: | ||

|- | |- | ||

| Metal 9 || 19.4 µm || 8 µm || 1.5 | | Metal 9 || 19.4 µm || 8 µm || 1.5 | ||

| + | |- | ||

| + | | Bump || 145.9 µm || 25.5 µm || - | ||

|} | |} | ||

| + | |||

| + | == Find models == | ||

| + | {{#ask: | ||

| + | [[instance of::microprocessor]] | ||

| + | [[process::32 nm]] | ||

| + | | ?full page name | ||

| + | | ?name | ||

| + | | ?microprocessor family | ||

| + | | ?microarchitecture | ||

| + | | ?process | ||

| + | | ?designer | ||

| + | | ?manufacturer | ||

| + | | ?first launched | ||

| + | | ?base frequency | ||

| + | | format=template|link=all|sort=name|order=asc|headers=hide|mainlabel=-|intro=<table class="wikitable"><tr><th colspan="8">[[32 nm]] Microprocessors</th></tr><tr><th colspan="3">Model</th><th colspan="5">Specs</th></tr><tr><th>Model</th><th>Family</th><th>µarch</th><th>Process</th><th>Designer</th><th>Manufacturer</th><th>Intro</th><th>Freq</th></tr>|outro=</table>|limit=0|searchlabel=Click to browse all 32 nm MPU models|sep=,|template=proc table 1|userparam=9 | ||

| + | }} | ||

== 32 nm Microprocessors== | == 32 nm Microprocessors== | ||

| Line 72: | Line 196: | ||

** {{amd|A10}} | ** {{amd|A10}} | ||

* Intel | * Intel | ||

| + | ** {{intel|Celeron}} | ||

| + | ** {{intel|Core i3}} | ||

| + | ** {{intel|Core i5}} | ||

| + | ** {{intel|Core i7}} | ||

** {{intel|Core i7EE}} | ** {{intel|Core i7EE}} | ||

| + | ** {{intel|Xeon}} | ||

| + | ** {{intel|Xeon E3}} | ||

| + | ** {{intel|Xeon E5}} | ||

| + | ** {{intel|Xeon E7}} | ||

| + | * UC Davis | ||

| + | ** {{ucdavis|KiloCore}} | ||

| + | * Princeton | ||

| + | ** {{Princeton|Piton}} | ||

{{expand list}} | {{expand list}} | ||

| − | == 32 nm | + | == 32 nm Microarchitectures == |

| + | * AMD | ||

| + | ** {{amd|Bulldozer|l=arch}} | ||

| + | ** {{amd|Piledriver|l=arch}} | ||

| + | * IBM | ||

| + | ** {{ibm|z12|l=arch}} | ||

| + | * Intel | ||

| + | ** {{intel|Saltwell|l=arch}} | ||

| + | ** {{intel|Sandy Bridge|l=arch}} | ||

| + | ** {{intel|Westmere|l=arch}} | ||

| + | |||

{{expand list}} | {{expand list}} | ||

| − | == 32 nm | + | == Documents == |

| − | * | + | * [[:File:samsung foundry solution 28-32nm.pdf|Samsung foundry solution for 32 & 28 nm]] |

| − | ** | + | |

| − | ** | + | == References == |

| − | ** | + | * Greene, B., et al. "High performance 32nm SOI CMOS with high-k/metal gate and 0.149 µm 2 SRAM and ultra low-k back end with eleven levels of copper." VLSI Technology, 2009 Symposium on. IEEE, 2009. |

| + | * Jan, C-H., et al. "A 32nm SoC platform technology with 2 nd generation high-k/metal gate transistors optimized for ultra low power, high performance, and high density product applications." Electron Devices Meeting (IEDM), 2009 IEEE International. IEEE, 2009. | ||

| + | * Wu, Shien-Yang, et al. "A 32nm CMOS low power SoC platform technology for foundry applications with functional high density SRAM." Electron Devices Meeting, 2007. IEDM 2007. IEEE International. IEEE, 2007. | ||

| + | * Chen, X., et al. "A cost effective 32nm high-K/metal gate CMOS technology for low power applications with single-metal/gate-first process." VLSI Technology, 2008 Symposium on. IEEE, 2008. | ||

| + | * Diaz, C. H., et al. "32nm gate-first high-k/metal-gate technology for high performance low power applications." Electron Devices Meeting, 2008. IEDM 2008. IEEE International. IEEE, 2008. | ||

| + | * Natarajan, S., et al. "A 32nm logic technology featuring 2 nd-generation high-k+ metal-gate transistors, enhanced channel strain and 0.171 μm 2 SRAM cell size in a 291Mb array." Electron Devices Meeting, 2008. IEDM 2008. IEEE International. IEEE, 2008. | ||

| + | * Hasegawa, S., et al. "A cost-conscious 32nm CMOS platform technology with advanced single exposure lithography and gate-first metal gate/high-k process." Electron Devices Meeting, 2008. IEDM 2008. IEEE International. IEEE, 2008. | ||

| + | * Arnaud, F., et al. "32nm general purpose bulk CMOS technology for high performance applications at low voltage." Electron Devices Meeting, 2008. IEDM 2008. IEEE International. IEEE, 2008. | ||

| + | * Pilo, Harold, et al. "A 64 Mb SRAM in 32 nm high-k metal-gate SOI technology with 0.7 V operation enabled by stability, write-ability and read-ability enhancements." IEEE Journal of Solid-State Circuits 47.1 (2012): 97-106. | ||

| − | + | [[category:lithography]] | |

Latest revision as of 18:14, 8 July 2021

The 32 nanometer (32 nm) lithography process is a full node semiconductor manufacturing process following the 40 nm process stopgap. Commercial integrated circuit manufacturing using 32 nm process began in 2010. This technology was superseded by the 28 nm process (HN) / 22 nm process (FN) in 2012.

Contents

Industry[edit]

TSMC cancelled its planned 32nm node process. Intel's 32 nm process became the first process to introduce the self-aligned via patterning.

| Process Name | |

|---|---|

| 1st Production | |

| Lithography | Lithography |

| Immersion | |

| Exposure | |

| Wafer | Type |

| Size | |

| Transistor | Type |

| Voltage | |

| Metal Layers | |

| Gate Length (Lg) | |

| Contacted Gate Pitch (CPP) | |

| Minimum Metal Pitch (MMP) | |

| SRAM bitcell | High-Perf (HP) |

| High-Density (HD) | |

| Low-Voltage (LV) | |

| DRAM bitcell | eDRAM |

| Intel | TSMC | Common Platform Alliance The Common Platform Alliance 20 nm node was a collaboration between IBM, Samsung, Freescale, Toshiba, Chartered Semiconductor Manufacturing, Infineon Technologies |

Toshiba / NEC | Common Platform Alliance (SOI) | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| P1268 (CPU) / P1269 (SoC) | ||||||||||||

| 2009 | 2011 | |||||||||||

| 193 nm | 193 nm | 193 nm | 193 nm | 193 nm | ||||||||

| Yes | Yes | Yes | Yes | Yes | ||||||||

| DP | DP | DP | DP | DP | ||||||||

| Bulk | Bulk | Bulk | Bulk | SOI | ||||||||

| 300 mm | 300 mm | 300 mm | 300 mm | 300 mm | ||||||||

| Planar | Planar | Planar | Planar | Planar | ||||||||

| 1 V, 0.75 V | 1.1 V | 1 V, 0.8 V | 1 V | 1 V | ||||||||

| 9 | 11 | 11 | ||||||||||

| Value | 45 nm Δ | Value | 40 nm Δ | Value | 45 nm Δ | Value | 40 nm Δ | Value | 45 nm Δ | |||

| 30 nm | 30 nm | 30 nm | 25 nm | |||||||||

| 112.5 nm | 0.63x | 130 nm | 126 nm | 120 nm | 130 nm | |||||||

| 112.5 nm | 0.70x | 100 nm | 100 nm | 100 nm | 100 nm | |||||||

| 0.199 µm² | ||||||||||||

| 0.148 µm² | 0.15 µm² | 0.157 µm² | 0.124 µm² | 0.149 µm² | ||||||||

| 0.171 µm² | ||||||||||||

| 0.039 µm² | ||||||||||||

Design Rules[edit]

Find models[edit]

Click to browse all 32 nm MPU models

32 nm Microprocessors[edit]

- AMD

- Intel

- UC Davis

- Princeton

This list is incomplete; you can help by expanding it.

32 nm Microarchitectures[edit]

- AMD

- IBM

- Intel

This list is incomplete; you can help by expanding it.

Documents[edit]

References[edit]

- Greene, B., et al. "High performance 32nm SOI CMOS with high-k/metal gate and 0.149 µm 2 SRAM and ultra low-k back end with eleven levels of copper." VLSI Technology, 2009 Symposium on. IEEE, 2009.

- Jan, C-H., et al. "A 32nm SoC platform technology with 2 nd generation high-k/metal gate transistors optimized for ultra low power, high performance, and high density product applications." Electron Devices Meeting (IEDM), 2009 IEEE International. IEEE, 2009.

- Wu, Shien-Yang, et al. "A 32nm CMOS low power SoC platform technology for foundry applications with functional high density SRAM." Electron Devices Meeting, 2007. IEDM 2007. IEEE International. IEEE, 2007.

- Chen, X., et al. "A cost effective 32nm high-K/metal gate CMOS technology for low power applications with single-metal/gate-first process." VLSI Technology, 2008 Symposium on. IEEE, 2008.

- Diaz, C. H., et al. "32nm gate-first high-k/metal-gate technology for high performance low power applications." Electron Devices Meeting, 2008. IEDM 2008. IEEE International. IEEE, 2008.

- Natarajan, S., et al. "A 32nm logic technology featuring 2 nd-generation high-k+ metal-gate transistors, enhanced channel strain and 0.171 μm 2 SRAM cell size in a 291Mb array." Electron Devices Meeting, 2008. IEDM 2008. IEEE International. IEEE, 2008.

- Hasegawa, S., et al. "A cost-conscious 32nm CMOS platform technology with advanced single exposure lithography and gate-first metal gate/high-k process." Electron Devices Meeting, 2008. IEDM 2008. IEEE International. IEEE, 2008.

- Arnaud, F., et al. "32nm general purpose bulk CMOS technology for high performance applications at low voltage." Electron Devices Meeting, 2008. IEDM 2008. IEEE International. IEEE, 2008.

- Pilo, Harold, et al. "A 64 Mb SRAM in 32 nm high-k metal-gate SOI technology with 0.7 V operation enabled by stability, write-ability and read-ability enhancements." IEEE Journal of Solid-State Circuits 47.1 (2012): 97-106.

Semiconductor lithography processes technology

Semiconductor lithography processes technology