(→45 nm Microprocessors) |

|||

| (19 intermediate revisions by 4 users not shown) | |||

| Line 1: | Line 1: | ||

{{Lithography processes}} | {{Lithography processes}} | ||

| − | The '''45 nm lithography process''' is a [[technology node|full node]] semiconductor manufacturing process following the [[55 nm lithography process|55 nm process]] stopgap. Commercial [[integrated circuit]] manufacturing using 45 nm process began in 2007. This technology was superseded by the [[40 nm lithography process|40 nm process]] (HN) / [[32 nm lithography process|32 nm process]] (FN) in 2010. | + | The '''45 nanometer (45 nm) lithography process''' is a [[technology node|full node]] semiconductor manufacturing process following the [[55 nm lithography process|55 nm process]] stopgap. Commercial [[integrated circuit]] manufacturing using 45 nm process began in 2007. This technology was superseded by the [[40 nm lithography process|40 nm process]] (HN) / [[32 nm lithography process|32 nm process]] (FN) in 2010. |

== Industry == | == Industry == | ||

| + | In January of 2006 Intel announced that they've been able to fabricate the first fully functional [[SRAM]] chips on a 45 nm process. As a preview Intel showcased 45nm SRAM chip (shown below) packing more than 1 billion transistors. Intel opened 3 45 nm facilities, their initial {{intel|D1D}} facility in Oregon, {{intel|Fab 32}} in Arizona and {{intel|Fab 28}} in Israel. Intel's 45 nm process is the first time high-k + metal gate transistors was used in high-volume manufacturing process. | ||

{{scrolling table/top|style=text-align: right; | first=Fab | {{scrolling table/top|style=text-align: right; | first=Fab | ||

|Process Name | |Process Name | ||

| Line 17: | Line 18: | ||

{{scrolling table/mid}} | {{scrolling table/mid}} | ||

|- | |- | ||

| − | ! colspan="2" | [[Intel]] !! colspan="2" | [[Fujitsu]] !! colspan="2" | [[TI]] !! colspan="2" | [[Toshiba]] / [[Sony]] / [[NEC]] !! colspan="2" | [[IBM]] / [[Toshiba]] / [[Sony]] / [[AMD]] | + | ! colspan="2" | [[Intel]] !! colspan="2" | [[Fujitsu]] !! colspan="2" | [[TI]] !! colspan="2" | [[Toshiba]] / [[Sony]] / [[NEC]] !! colspan="2" | [[Samsung]] !! colspan="2" | [[IBM]] / [[Toshiba]] / [[Sony]] / [[AMD]] |

|- style="text-align: center;" | |- style="text-align: center;" | ||

| − | | colspan="2" | P1266 || colspan="2" | CS-300 || colspan="2" | || colspan="2" | || colspan="2" | | + | | colspan="2" | P1266 (CPU) / P1266.8 (SoC) / P1269 (SoC) || colspan="2" | CS-300 || colspan="2" | || colspan="2" | || colspan="2" | 11LP || colspan="2" | |

|- style="text-align: center;" | |- style="text-align: center;" | ||

| − | | colspan="2" | | + | | colspan="2" | 2006 || colspan="2" | 2008 || colspan="2" | 2008 || colspan="2" | 2006 || colspan="2" | 2007 || colspan="2" | 2007 |

|- style="text-align: center;" | |- style="text-align: center;" | ||

| − | | colspan=" | + | | colspan="10" | Bulk || colspan="2" | PDSOI |

|- style="text-align: center;" | |- style="text-align: center;" | ||

| − | | colspan=" | + | | colspan="12" | 300mm |

|- | |- | ||

| − | ! Value !! [[65 nm]] Δ !! Value !! [[65 nm]] Δ !! Value !! [[65 nm]] Δ !! Value !! [[65 nm]] Δ !! Value !! [[65 nm]] Δ | + | ! Value !! [[65 nm]] Δ !! Value !! [[65 nm]] Δ !! Value !! [[65 nm]] Δ !! Value !! [[65 nm]] Δ !! Value !! [[65 nm]] Δ !! Value !! [[65 nm]] Δ |

|- | |- | ||

| − | | 180 nm || 0.82x || 190 nm || ?x || ? nm || ?x || 180 nm || ?x || 190 nm || 0.76x | + | | 180 nm || 0.82x || 190 nm || ?x || ? nm || ?x || 180 nm || ?x || ? nm || ?x || 190 nm || 0.76x |

|- | |- | ||

| − | | 160 nm || 0.76x || ? nm || ?x || ? nm || ?x || ? nm || ?x || | + | | 160 nm || 0.76x || ? nm || ?x || ? nm || ?x || ? nm || ?x || ? nm || ?x || ? nm || ?x |

|- | |- | ||

| − | | 0.346 | + | | 0.346 µm² || 0.61x || 0.225 µm² || ?x || 0.255 µm² || ?x || 0.248 µm² || ?x || 0.29 µm² || 0.54x || 0.370 µm² || 0.57x |

|- | |- | ||

| − | | | + | | 0.3816 µm² || 0.56x || || || || || || || 0.359 µm² || 0.53x || || |

|- | |- | ||

| − | | || || || || || || || || 0.067 | + | | || || || || || || || || 0.11 µm² || 0.58x || 0.067 µm² || 0.53x |

{{scrolling table/end}} | {{scrolling table/end}} | ||

| − | === | + | === Intel === |

| + | <gallery widths=200px heights=300px> | ||

| + | File:45nm SRAM Cell.jpg|6T SRAM Bit-Cell | ||

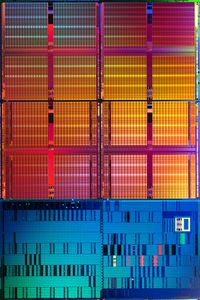

| + | File:45nm SRAM photo.JPG|Die photo of an [[Intel]] [[45 nm]] shuttle test chip including 153 MiB [[SRAM]] and logic test circuits | ||

| + | File:45nm wafer photo 1.jpg|300 mm wafer with 45 nm shuttle test chips | ||

| + | File:45nm wafer photo 2.JPG|Intel engineer holding 300 mm wafer with 45 nm shuttle test chips | ||

| + | File:45nm-wafer-photo-3.jpg|Intel 300 mm wafer with 45 nm shuttle test chips | ||

| + | </gallery> | ||

| + | |||

{| class="wikitable collapsible collapsed" | {| class="wikitable collapsible collapsed" | ||

|- | |- | ||

| − | ! colspan="4" | Design Rules | + | ! colspan="4" | Intel 45nm Design Rules |

|- | |- | ||

! Layer !! Pitch !! Thick !! Aspect Ratio | ! Layer !! Pitch !! Thick !! Aspect Ratio | ||

| Line 74: | Line 83: | ||

** {{amd|Opteron}} | ** {{amd|Opteron}} | ||

** {{amd|Phenom II}} | ** {{amd|Phenom II}} | ||

| + | * Freescale | ||

| + | ** {{freescale|QorIQ}} | ||

* IBM | * IBM | ||

** {{ibm|Power7}} | ** {{ibm|Power7}} | ||

| Line 92: | Line 103: | ||

** {{intel|Xeon}} | ** {{intel|Xeon}} | ||

| + | {{expand list}}n Chips== | ||

{{expand list}} | {{expand list}} | ||

| − | == 45 nm | + | == 45 nm Microarchitectures == |

| + | * AMD | ||

| + | ** {{amd|K10|l=arch}} | ||

| + | * IBM | ||

| + | ** {{ibm|z196|l=arch}} | ||

| + | * Intel | ||

| + | ** {{intel|Bonnell|l=arch}} | ||

| + | ** {{intel|Nehalem|l=arch}} | ||

| + | ** {{intel|Penryn|l=arch}} | ||

| + | * VIA Technologies | ||

| + | ** {{via|Isaiah|l=arch}} | ||

| + | |||

{{expand list}} | {{expand list}} | ||

| − | == 45 nm | + | == Documents == |

| − | * Intel | + | * [[:File:samsung foundry - 45, 65, 90 (August, 2007).pdf|Samsung foundry - 45 nm, 65 nm, 90 nm guide (August, 2007)]] |

| − | ** | + | * Intel |

| − | ** | + | ** [[:File:45nmSummaryFoils.pdf|New Intel 45 nm Processors]] |

| − | ** | + | ** [[:File:Press45nm107 FINAL.pdf|High-k + Metal Gate Transistor Breakthrough on 45 nm Microprocessors]] |

| + | ** [[:File:SandToCircuit FINAL.pdf|From sand to circuits]] | ||

| + | |||

| + | == References == | ||

| + | * Mistry, Kaizad, et al. "A 45nm logic technology with high-k+ metal gate transistors, strained silicon, 9 Cu interconnect layers, 193nm dry patterning, and 100% Pb-free packaging." Electron Devices Meeting, 2007. IEDM 2007. IEEE International. IEEE, 2007. | ||

| − | + | [[category:lithography]] | |

Latest revision as of 04:51, 20 July 2018

The 45 nanometer (45 nm) lithography process is a full node semiconductor manufacturing process following the 55 nm process stopgap. Commercial integrated circuit manufacturing using 45 nm process began in 2007. This technology was superseded by the 40 nm process (HN) / 32 nm process (FN) in 2010.

Contents

Industry[edit]

In January of 2006 Intel announced that they've been able to fabricate the first fully functional SRAM chips on a 45 nm process. As a preview Intel showcased 45nm SRAM chip (shown below) packing more than 1 billion transistors. Intel opened 3 45 nm facilities, their initial D1D facility in Oregon, Fab 32 in Arizona and Fab 28 in Israel. Intel's 45 nm process is the first time high-k + metal gate transistors was used in high-volume manufacturing process.

| Fab |

|---|

| Process Name |

| 1st Production |

| Type |

| Wafer |

| |

| Contacted Gate Pitch |

| Interconnect Pitch (M1P) |

| SRAM bit cell (HD) |

| SRAM bit cell (LP) |

| DRAM bit cell |

| Intel | Fujitsu | TI | Toshiba / Sony / NEC | Samsung | IBM / Toshiba / Sony / AMD | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| P1266 (CPU) / P1266.8 (SoC) / P1269 (SoC) | CS-300 | 11LP | |||||||||

| 2006 | 2008 | 2008 | 2006 | 2007 | 2007 | ||||||

| Bulk | PDSOI | ||||||||||

| 300mm | |||||||||||

| Value | 65 nm Δ | Value | 65 nm Δ | Value | 65 nm Δ | Value | 65 nm Δ | Value | 65 nm Δ | Value | 65 nm Δ |

| 180 nm | 0.82x | 190 nm | ?x | ? nm | ?x | 180 nm | ?x | ? nm | ?x | 190 nm | 0.76x |

| 160 nm | 0.76x | ? nm | ?x | ? nm | ?x | ? nm | ?x | ? nm | ?x | ? nm | ?x |

| 0.346 µm² | 0.61x | 0.225 µm² | ?x | 0.255 µm² | ?x | 0.248 µm² | ?x | 0.29 µm² | 0.54x | 0.370 µm² | 0.57x |

| 0.3816 µm² | 0.56x | 0.359 µm² | 0.53x | ||||||||

| 0.11 µm² | 0.58x | 0.067 µm² | 0.53x | ||||||||

Intel[edit]

| Intel 45nm Design Rules | |||

|---|---|---|---|

| Layer | Pitch | Thick | Aspect Ratio |

| Isolation | 200 nm | 200 nm | - |

| Contacted Gate | 180 nm | 60 nm | -- |

| Metal 1 | 160 nm | 144 nm | 1.8 |

| Metal 2 | 160 nm | 144 nm | 1.8 |

| Metal 3 | 160 nm | 144 nm | 1.8 |

| Metal 4 | 240 nm | 216 nm | 1.8 |

| Metal 5 | 280 nm | 252 nm | 1.8 |

| Metal 6 | 360 nm | 324 nm | 1.8 |

| Metal 7 | 560 nm | 504 nm | 1.7 |

| Metal 8 | 810 nm | 720 nm | 1.8 |

| Metal 9 | 30.5 µm | 7 µm | 0.4 |

45 nm Microprocessors[edit]

- AMD

- Freescale

- IBM

- Intel

This list is incomplete; you can help by expanding it.n Chips== This list is incomplete; you can help by expanding it.

45 nm Microarchitectures[edit]

This list is incomplete; you can help by expanding it.

Documents[edit]

References[edit]

- Mistry, Kaizad, et al. "A 45nm logic technology with high-k+ metal gate transistors, strained silicon, 9 Cu interconnect layers, 193nm dry patterning, and 100% Pb-free packaging." Electron Devices Meeting, 2007. IEDM 2007. IEEE International. IEEE, 2007.

Semiconductor lithography processes technology

Semiconductor lithography processes technology