From WikiChip

32 nm lithography process

The 32 nanometer (32 nm) lithography process is a full node semiconductor

- manufacturing process following the 40 nm process stopgap.

Commercial integrated circuit manufacturing using 32 nm process began in 2010.

- This technology was superseded by the 28 nm process (HN) / 22 nm process (FN) in 2012.

Contents

Industry

Intel's 32 nm process became the first process to introduce the self-aligned via patterning.

Design Rules

| Intel 32 nm Design Rules | ||||

|---|---|---|---|---|

| Layer | Pitch | Thick | Aspect Ratio | Image |

| Isolation | 140 nm | 200 | - |

|

| Contacted Gate | 112.5 nm | 35 nm | -- | |

| Metal 1 | 112.5 nm | 95 nm | 1.7 | |

| Metal 2 | 112.5 nm | 95 nm | 1.7 | |

| Metal 3 | 112.5 nm | 95 nm | 1.7 | |

| Metal 4 | 168.8 nm | 151 nm | 1.8 | |

| Metal 5 | 225.0 nm | 204 nm | 1.8 | |

| Metal 6 | 337.6 nm | 303 nm | 1.8 | |

| Metal 7 | 450.1 nm | 388 nm | 1.7 | |

| Metal 8 | 566.5 nm | 504 nm | 1.8 | |

| Metal 9 | 19.4 µm | 8 µm | 1.5 | |

| Bump | 145.9 µm | 25.5 µm | - | |

Specifications

| Process Name | |

|---|---|

| 1st Production | |

| Litho- graphy |

Lithography |

| Immersion | |

| Exposure | |

| Wafer | Type |

| Size | |

| Tran- sistor |

Type |

| Voltage | |

| Metal Layers | |

| Gate Length (Lg) | |

| Contacted Gate Pitch (CPP) | |

| Minimum Metal Pitch (MMP) | |

| SRAM bitcell |

High-Perf (HP) |

| High-Density (HD) | |

| Low-Voltage (LV) | |

| DRAM bitcell |

eDRAM |

| Intel | TSMC | Samsung Common Platform Alliance - The Common Platform Alliance 20 nm node was a collaboration between IBM, Samsung, Freescale, Toshiba, Chartered Semiconductor Manufacturing, Infineon Technologies |

NEC | AMD | |||||

|---|---|---|---|---|---|---|---|---|---|

| P1268, P1269 | |||||||||

| 2009 | 2011 | ||||||||

| 193 nm | 193 nm | 193 nm | 193 nm | 193 nm | |||||

| Yes | Yes | Yes | Yes | Yes | |||||

| DP | DP | DP | DP | DP | |||||

| Bulk | Bulk | Bulk | Bulk | SOI | |||||

| 300 mm | 300 mm | 300 mm | 300 mm | 300 mm | |||||

| Planar | Planar | Planar | Planar | Planar | |||||

| 1.0 V, 0.75 V | 1.1 V | 1.0 V, 0.8 V | 1 V | 1 V | |||||

| 9 | 11 | 11 | |||||||

| Value | 45 nm Δ | Value | 40 nm Δ | Value | 45 nm Δ | Value | 40 nm Δ | Value | 45 nm Δ |

| 30 nm | 1 | 30 nm | 2 | 30 nm | 25 nm | ||||

| 112.5 nm | 0.63x | 130 nm | 126 nm | 120 nm | 130 nm | ||||

| 112.5 nm | 0.70x | 100 nm | 100 nm | 100 nm | 100 nm | ||||

| 0.199 µm² | |||||||||

| 0.148 µm² | 0.15 µm² | 0.157 µm² | 0.124 µm² | 0.149 µm² | |||||

| 0.171 µm² | |||||||||

| 0.039 µm² | |||||||||

Find models

Click to browse all 32 nm MPU models

32 nm Microprocessors

- AMD

- Intel

- UC Davis

- Princeton

This list is incomplete; you can help by expanding it.

32 nm Microarchitectures

- AMD

- IBM

- Intel

This list is incomplete; you can help by expanding it.

Documents

References

- Greene, B., et al. "High performance 32nm SOI CMOS with high-k/metal gate and 0.149 µm 2 SRAM and ultra low-k back end with eleven levels of copper." VLSI Technology, 2009 Symposium on. IEEE, 2009.

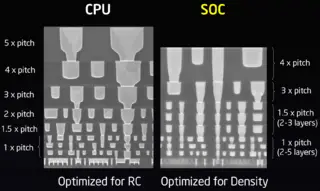

- Jan, C-H., et al. "A 32nm SoC platform technology with 2 nd generation high-k/metal gate transistors optimized for ultra low power, high performance, and high density product applications." Electron Devices Meeting (IEDM), 2009 IEEE International. IEEE, 2009.

- Wu, Shien-Yang, et al. "A 32nm CMOS low power SoC platform technology for foundry applications with functional high density SRAM." Electron Devices Meeting, 2007. IEDM 2007. IEEE International. IEEE, 2007.

- Chen, X., et al. "A cost effective 32nm high-K/metal gate CMOS technology for low power applications with single-metal/gate-first process." VLSI Technology, 2008 Symposium on. IEEE, 2008.

- Diaz, C. H., et al. "32nm gate-first high-k/metal-gate technology for high performance low power applications." Electron Devices Meeting, 2008. IEDM 2008. IEEE International. IEEE, 2008.

- Natarajan, S., et al. "A 32nm logic technology featuring 2 nd-generation high-k+ metal-gate transistors, enhanced channel strain and 0.171 μm 2 SRAM cell size in a 291Mb array." Electron Devices Meeting, 2008. IEDM 2008. IEEE International. IEEE, 2008.

- Hasegawa, S., et al. "A cost-conscious 32nm CMOS platform technology with advanced single exposure lithography and gate-first metal gate/high-k process." Electron Devices Meeting, 2008. IEDM 2008. IEEE International. IEEE, 2008.

- Arnaud, F., et al. "32nm general purpose bulk CMOS technology for high performance applications at low voltage." Electron Devices Meeting, 2008. IEDM 2008. IEEE International. IEEE, 2008.

- Pilo, Harold, et al. "A 64 Mb SRAM in 32 nm high-k metal-gate SOI technology with 0.7 V operation enabled by stability, write-ability and read-ability enhancements." IEEE Journal of Solid-State Circuits 47.1 (2012): 97-106.

Semiconductor lithography processes technology

Semiconductor lithography processes technology