From WikiChip

Difference between revisions of "amd/List of AMD CPU sockets"

(Socket F/C32/G34 update.) |

(→Mobile Sockets (ultrathin, tablet)) |

||

| (23 intermediate revisions by 6 users not shown) | |||

| Line 1: | Line 1: | ||

| − | {{ | + | <!--{{DISPLAYTITLE:List of AMD CPU sockets}}--> |

| − | |||

| − | |||

== Overview == | == Overview == | ||

| − | {| class="wikitable sortable" | + | <!-- {| class="wikitable sortable" --> |

| + | {| class="wikitable mw-datatable" style="margin:0.5em auto; text-align:center; min-width:70em;" | ||

| + | |- | ||

!Year!!Desktop!!Desktop APU!!Server!!Mobile!!Tablet!!Embedded | !Year!!Desktop!!Desktop APU!!Server!!Mobile!!Tablet!!Embedded | ||

|- | |- | ||

| − | |1998||{{amd|Super Socket 7|Super 7|l=package}}||||||{{amd|Super Socket 7|Super 7|l=package}}|||| | + | |1998||{{amd|Super Socket 7|Super 7|l=package}} (321)||||||{{amd|Super Socket 7|Super 7|l=package}} (321)|||| |

| + | |- | ||

| + | |1999||{{amd|Slot A|l=package}} (242)|||||||||| | ||

|- | |- | ||

| − | | | + | |2000||{{amd|Socket A|l=package}} (462)||||||{{amd|Socket A|l=package}} (462)|||| |

|- | |- | ||

| − | | | + | |2002||||||||{{amd|Socket 563|563|l=package}}|||| |

|- | |- | ||

|2003||{{amd|Socket 754|754|l=package}}, {{amd|Socket 940|940|l=package}}||||{{amd|Socket 940|940|l=package}}||{{amd|Socket 754|754|l=package}}|||| | |2003||{{amd|Socket 754|754|l=package}}, {{amd|Socket 940|940|l=package}}||||{{amd|Socket 940|940|l=package}}||{{amd|Socket 754|754|l=package}}|||| | ||

| Line 17: | Line 19: | ||

|2004||{{amd|Socket 939|939|l=package}}|||||||||| | |2004||{{amd|Socket 939|939|l=package}}|||||||||| | ||

|- | |- | ||

| − | |2006||{{amd|Socket AM2|AM2|l=package}}, {{amd|Socket F|Fr3|l=package}}||||{{amd|Socket F|F|l=package}}||{{amd|Socket S1g1|S1g1|l=package}}|||| | + | |2006||{{amd|Socket AM2|AM2|l=package}}, {{amd|Socket F|Fr3|l=package}}||||{{amd|Socket F|F|l=package}}, {{amd|Socket L|L|l=package}} (1207FX)||{{amd|Socket S1g1|S1g1|l=package}}|||| |

|- | |- | ||

|2007||{{amd|Socket AM2+|AM2+|l=package}}||||{{amd|Socket F|Fr2|l=package}}|||||| | |2007||{{amd|Socket AM2+|AM2+|l=package}}||||{{amd|Socket F|Fr2|l=package}}|||||| | ||

| Line 39: | Line 41: | ||

|2016||{{amd|Socket AM4|AM4|l=package}}||{{amd|Socket AM4|AM4|l=package}}||||||{{amd|FT4|l=package}}|| | |2016||{{amd|Socket AM4|AM4|l=package}}||{{amd|Socket AM4|AM4|l=package}}||||||{{amd|FT4|l=package}}|| | ||

|- | |- | ||

| − | |2017||{{amd|Socket TR4|TR4|l=package}}||||{{amd|Socket SP3|SP3|l=package}}|||||| | + | |2017||{{amd|Socket TR4|TR4|l=package}}||||{{amd|Socket SP3|SP3|l=package}} (Zen 2/3)|||||| |

| + | |- | ||

| + | |2018||||||||{{amd|FP5|l=package}} (Zen/Zen+)||||{{amd|FP5|l=package}}, {{amd|SP4|l=package}}, {{amd|SP4r2|l=package}} | ||

| + | |- | ||

| + | |2019||{{amd|Socket sTRX4|sTRX4|l=package}}|||||||||| | ||

| + | |- | ||

| + | |2020||{{amd|Socket sWRX8|sWRX8|l=package}}||||||{{amd|FP6|l=package}} (Zen 2/3)||{{amd|FT5|l=package}}||{{amd|FP6|l=package}} (Zen 2/3) | ||

| + | |- | ||

| + | |2022||{{amd|Socket AM5|AM5|l=package}}||{{amd|Socket AM5|AM5|l=package}}||{{amd|Socket SP5|SP5|l=package}} (Zen 4/5)||{{amd|FP7|l=package}}||{{amd|FT6|l=package}}||{{amd|FP7|l=package}} | ||

|- | |- | ||

| − | | | + | |2023||{{amd|Socket sTR5|sTR5|l=package}}||{{amd|Socket sTR5|sTR5|l=package}}||||{{amd|FP7r2|l=package}}||{{amd|FL1|l=package}}||{{amd|FP7r2|l=package}} |

|- | |- | ||

| − | | | + | |2024||||||{{amd|Socket SP6|SP6|l=package}} (Siena)||{{amd|FP8|l=package}}, {{amd|FP10|l=package}}||||{{amd|FP8|l=package}}, {{amd|FP10|l=package}} |

| + | |- | ||

| + | |2025||||||{{amd|Socket SP7|SP7|l=package}} (Venice)||{{amd|FP11|l=package}}, {{amd|FP12|l=package}}||||{{amd|FP11|l=package}}, {{amd|FP12|l=package}} <!-- BGA 2077 --> | ||

| + | |- | ||

| + | |2026||{{amd|Socket AM6|AM6|l=package}}||{{amd|Socket AM6|AM6|l=package}}||{{amd|Socket SP8|SP8|l=package}} (Venice)|||||| | ||

| + | |- | ||

| + | |2027|||||||||||| | ||

|- | |- | ||

| − | |||

|} | |} | ||

| − | == Desktop | + | == Desktop/{{abbr|HEDT}}/Workstation Sockets == |

| − | {| class="wikitable | + | {| class="wikitable mw-datatable" style="margin:0.5em auto; text-align:center; min-width:70em;" |

| − | !Name (a.k.a.) | + | |- |

| + | ! Name (a.k.a.) | ||

| + | ! Year | ||

| + | ! Type<ref>PGA = Pin Grid Array, BGA = Ball Grid Array (CPU package soldered directly to the motherboard), LGA = Land Grid Array, SEC = Single Edge Cartridge (printed circuit board with an edge connector similar to graphics cards).</ref> | ||

| + | ! Contacts | ||

| + | ! {{amd|CPUID|AMD CPU ID}} | ||

| + | ! MC<ref>If processors for this socket integrate a Memory Controller, the number of independent channels times the maximum channel width in bits, including [[ECC]] lanes. Not all processors for this socket may support ECC.</ref> | ||

| + | ! I/O lanes<ref>FSB = Front Side Bus (memory and I/O interfaces provided by the chipset), HTx = HyperTransport generation x link (I/O interfaces provided by the chipset), PCIex = Peripheral Component Interconnect Express generation x link. Note HT and PCIe links support bifurcation, e.g. 1x16 into 2x8 links. The table lists the maximum number of lanes and interfaces. Some processors may support fewer, and some motherboards may use alternative functions of these pins.</ref> | ||

| + | ! APU<ref>This socket has graphics interfaces (DisplayPort, HDMI, VGA, etc.) to accommodate Accelerated Processing Units i.e. processors with integrated graphics. Not all processors for this socket may integrate a graphics processor.</ref> | ||

| + | ! FCH<ref>The number of dedicated I/O lanes to the Fusion Controller Hub a.k.a. chipset, equivalent to Intel's Platform Controller Hub. The FCH mainly serves as an I/O expander. A controller hub may be integrated on the processor, in this case the CPU package and socket has suitable I/O interfaces (USB, SATA, {{abbr|LPC}}, {{abbr|SMBus}}, etc.), sometimes in addition to the FCH interface.</ref> | ||

| + | ! Notes | ||

| + | ! Package<ref>CPU package bottom view, not to scale.</ref> | ||

|- | |- | ||

| − | |{{amd|Super Socket 7|l=package}}||1998||PGA||321|||| | + | |{{amd|Super Socket 7|l=package}}||1998||PGA||321||5||-||FSB||{{tchk|no}}||-||||[[File:CPGA-321.svg|x50px]] |

|- | |- | ||

| − | |{{amd|Slot A|l=package}}||1999||SEC||242|||| | + | |{{amd|Slot A|l=package}}||1999||SEC||242||6||-||FSB||{{tchk|no}}||-|||| |

|- | |- | ||

| − | |{{amd|Socket A|l=package}}||2000||PGA||462|||| | + | |{{amd|Socket A|l=package}}||2000||PGA||462||6||-||FSB||{{tchk|no}}||-||||[[File:OPGA-453.svg|x50px]] <br>[[File:CPGA-453.svg|x50px]] |

|- | |- | ||

| − | |{{amd|Socket 563|l=package}}||||PGA||563|||| | + | |{{amd|Socket 563|l=package}}||2003||PGA||563||6||-||FSB||{{tchk|no}}||-||||[[File:OPGA-563.svg|x50px]] |

|- | |- | ||

| − | |{{amd|Socket 754|l=package}}||2003||PGA||754||||72 bit DDR||HT1|| | + | |{{amd|Socket 754|l=package}}||2003||PGA||754||0Fh||72 bit DDR||16 HT1||{{tchk|no}}||-||||[[File:OPGA-754.svg|x50px]] |

|- | |- | ||

| − | |{{amd|Socket 940|l=package}}||2003||PGA||940||||144 bit DDR|| | + | |{{amd|Socket 940|l=package}}||2003||PGA||940||0Fh||144 bit DDR||3× 16 HT1||{{tchk|no}}||-||||[[File:OPGA-940 S940.svg|x50px]] <br>[[File:CPGA-940.svg|x50px]] |

|- | |- | ||

| − | |{{amd|Socket 939|l=package}}||2004||PGA||939||||144 bit DDR||HT1|| | + | |{{amd|Socket 939|l=package}}||2004||PGA||939||0Fh||144 bit DDR||16 HT1||{{tchk|no}}||-||||[[File:OPGA-939.svg|x50px]] |

|- | |- | ||

| − | |{{amd|Socket AM2|l=package}}||2006||PGA||940||0Fh||144 bit DDR2||HT1|| | + | |{{amd|Socket AM2|l=package}}||2006||PGA||940||NPT 0Fh||144 bit DDR2||16 HT1||{{tchk|no}}||-||||[[File:OPGA-940 AM2.svg|x50px]] |

|- | |- | ||

| − | |{{amd|Socket F|Socket Fr3|l=package}}||2006||LGA||1207||0Fh|| | + | |{{amd|Socket F|Socket Fr3|l=package}}||2006||LGA||1207||NPT 0Fh||2× 72 bit DDR2||3 × 16 HT1||{{tchk|no}}||-||||[[File:LGA-1207 F.svg|x50px]] |

|- | |- | ||

| − | |{{amd|Socket AM2+|l=package}} (AM2r2)||2007||PGA||940||10h|| | + | |{{amd|Socket AM2+|l=package}} <br>(AM2r2)||2007||PGA||940||10h||2× 72 bit DDR2||16 HT3||{{tchk|no}}||-||||[[File:OPGA-940 AM2.svg|x50px]] |

|- | |- | ||

| − | |{{amd|Socket AM3|l=package}}||2009||PGA||938||10h|| | + | |{{amd|Socket AM3|l=package}}||2009||PGA||938||10h||2× 72 bit DDR2/3||16 HT3||{{tchk|no}}||-||||[[File:OPGA-938.svg|x50px]] <br>[[File:OPGA-940 AM3.svg|x50px]] |

|- | |- | ||

| − | |{{amd|Socket FM1|l=package}}||2011||PGA||905||12h|| | + | |{{amd|Socket FM1|l=package}}||2011||PGA||905||12h||2× 72 bit DDR3||16 + 4 PCIe 2||{{tchk|yes}}||4 PCIe 2||||[[File:OPGA-905.svg|x50px]] |

|- | |- | ||

| − | |{{amd|Socket AM3+|l=package}} (AM3b)||2012||PGA||941||15h|| | + | |{{amd|Socket AM3+|l=package}} <br>(AM3b)||2012||PGA||941||15h||2× 72 bit DDR3||16 HT3||{{tchk|no}}||-||||[[File:OPGA-941.svg|x50px]] |

|- | |- | ||

| − | |{{amd|Socket FM2|l=package}}||2012||PGA||904||15h|| | + | |{{amd|Socket FM2|l=package}}||2012||PGA||904||15h||2× 64 bit DDR3||16 + 4 PCIe 2||{{tchk|yes}}||4 PCIe 2||||[[File:OPGA-904.svg|x50px]] |

|- | |- | ||

| − | |{{amd|Socket AM1|l=package}} (FS1b)||2014||PGA||721||16h||72 bit DDR3||4 + 4 | + | |{{amd|Socket AM1|l=package}} <br>(FS1b)||2014||PGA||721||16h||72 bit DDR3||4 + 4 PCIe 2||{{tchk|yes}}||integrated||||[[File:OPGA-721.svg|x50px]] |

|- | |- | ||

| − | |{{amd|Socket FM2+|l=package}} (FM2b, FM2r2)||2014||PGA||906||15h|| | + | |{{amd|Socket FM2+|l=package}} <br>(FM2b, FM2r2)||2014||PGA||906||15h||2× 64 bit DDR3||16 + 4 PCIe 2/3||{{tchk|yes}}||4 PCIe 2||||[[File:OPGA-906.svg|x50px]] |

|- | |- | ||

| − | |{{amd|Socket AM4|l=package}}||2016||PGA||1331||15h, 17h, 19h|| | + | |{{amd|Socket AM4|l=package}}||2016||PGA||1331||15h, 17h, 19h||2× 72 bit DDR3/4||16 + 4 PCIe 3/4||{{tchk|yes}}||4 PCIe 3/4||||[[File:socket_am4.svg|x50px]] |

|- | |- | ||

| − | |{{amd|Socket TR4|l=package}} (SP3r2)||2017||LGA||4094||17h||4 | + | |{{amd|Socket TR4|l=package}} <br>(SP3r2)||2017||LGA||4094||17h||4× 72 bit DDR4||4× 16 PCIe 3||{{tchk|no}}||||||[[File:FCLGA-4094.svg|x50px]] |

| + | |- | ||

| + | |{{amd|Socket sTRX4|l=package}} <br>(SP3r3)||2019||LGA||4094||17h||4× 72 bit DDR4||4× 16 PCIe 4||{{tchk|no}}||||||[[File:FCLGA-4094.svg|x50px]] | ||

| + | |- <!-- Socket sWRX8 • 2020 • AMD Ryzen Threadripper Pro (5000 series) • Desktop • LGA • 4094 --> | ||

| + | |{{amd|Socket sWRX8|l=package}}<br>(SP3r4)||2020||LGA||4094||17h, 19h||8× 72 bit DDR4||8× 16 PCIe 4||{{tchk|no}}||||||[[File:FCLGA-4094.svg|x50px]] | ||

| + | |- <!-- Socket AM5 • 2022 • AMD Ryzen 7000/8000 (APU)/9000 series/Zen 4 Ryzen CPUs • Desktop • LGA • 1718 --> | ||

| + | |{{amd|Socket AM5|l=package}}||2022||LGA||1718||19h||2× 72 bit DDR5||16 + 4 + 4 PCIe 4/5||{{tchk|yes}}||4 PCIe 4/5||||[[File:LGA-1718.svg|x50px]] | ||

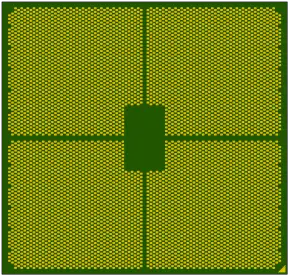

| + | |- <!-- Socket sTR5 • 2023 • AMD Ryzen Threadripper/Pro (7000 series) • Desktop • LGA • 4844 --> | ||

| + | |{{amd|Socket sTR5|l=package}}||2023||LGA||4844||19h||8× 72 bit DDR5<br>(RDIMM w/ ECC)||8× 16 PCIe 5||{{tchk|yes}}||4 PCIe 4/5||TRX50,<br>WRX90||[[File:LGA-4844.svg|x50px]] | ||

|- | |- | ||

| − | |||

|} | |} | ||

| + | <references/> | ||

| + | <!--<pre> | ||

| + | * Socket AM4 • 2016 • Desktop • PGA • 1331 • 1 • AMD Ryzen 9, Ryzen 7, Ryzen 5 & Ryzen 3 Zen CPUs • DDR4 | ||

| + | : AMD Athlon Bristol Ridge/Raven Ridge 14nm/Picasso 12nm, AMD Ryzen 1000/2000/3000/4000/5000 series | ||

| + | * Socket SP3 • 2017 • AMD Epyc Naples/Rome/Milan • Server • LGA • 4094 • DDR4 | ||

| + | * Socket TR4/Socket SP3r2 • 2017 • AMD Ryzen Threadripper (1000/2000 series) • Desktop • LGA • 4094 • DDR4 | ||

| + | * Socket sTRX4/Socket SP3r3 • 2019 • AMD Ryzen Threadripper (3000 series) • Desktop • LGA • 4094 • DDR4 | ||

| − | == Server | + | * Socket sWRX8 • 2022 • AMD Ryzen Threadripper Pro (5000 series) • Desktop • LGA • 4094 |

| − | {| class="wikitable | + | * Socket AM5 • 2022 • AMD Ryzen 7000/8000 (APU)/9000 series/Zen 4 Ryzen CPUs • Desktop • LGA • 1718 |

| − | !Name!!Year!!Type!! | + | * Socket SP5 • 2022 • AMD Epyc Genoa • Server • LGA • 6096 • Used for AMD Epyc Genoa and Milan |

| + | * Socket SP6 • 2023 • AMD Epyc Siena • Server • LGA • 4844 | ||

| + | * Socket sTR5 • 2023 • AMD Ryzen Threadripper/Pro (7000 series) • Desktop • LGA • 4844 | ||

| + | </pre>--> | ||

| + | |||

| + | == Server Sockets == | ||

| + | {| class="wikitable mw-datatable" style="margin:0.5em auto; text-align:center; min-width:70em;" | ||

| + | |- | ||

| + | !Name!!Year!!Type!!Contacts!!{{amd|CPUID|CPU Family}}!!Memory <br>Controller!!I/O lanes!!APU!!{{abbr|SCH|Server Controller Hub}}!!Notes!!Package | ||

|- | |- | ||

| − | |{{amd|Socket 940|l=package}}||2003||PGA||940||||144 bit DDR|| | + | |{{amd|Socket 940|l=package}}||2003||PGA||940||0Fh||144 bit DDR||3× 16 HT1||{{tchk|no}}||-|| [[Athlon]] 64 FX, <br>[[Opteron]] ||[[File:OPGA-940 S940.svg|x50px]] <br>[[File:CPGA-940.svg|x50px]] |

|- | |- | ||

| − | |{{amd|Socket F|l=package}}||2006||LGA||1207||0Fh | + | |{{amd|Socket F|l=package}}||2006||LGA||1207||NPT 0Fh||2 × 72 bit DDR2||3× 16 HT1||{{tchk|no}}||-|| [[Athlon]] 64 FX, <br>[[Opteron]] <br>2xxx/8xxx <br>(multi) ||[[File:LGA-1207 F.svg|x50px]] |

|- | |- | ||

| − | |{{amd|Socket F|Socket Fr2|l=package}}||2007||LGA||1207||0Fh, 10h|| | + | |{{amd|Socket F|Socket Fr2|l=package}}||2007||LGA||1207||NPT 0Fh, 10h||2× 72 bit DDR2||3× 16 HT1||{{tchk|no}}||-||||[[File:LGA-1207 F.svg|x50px]] |

|- | |- | ||

| − | |{{amd|Socket F|Socket Fr5|l=package}}||2008||LGA||1207||0Fh, 10h|| | + | |{{amd|Socket F|Socket Fr5|l=package}}||2008||LGA||1207||NPT 0Fh, 10h||2× 72 bit DDR2||3× 16 HT1/3||{{tchk|no}}||-||||[[File:LGA-1207 F.svg|x50px]] |

|- | |- | ||

| − | |{{amd|Socket F|Socket Fr6|l=package}}||2009||LGA||1207||10h|| | + | |{{amd|Socket F|Socket Fr6|l=package}}||2009||LGA||1207||10h||2× 72 bit DDR2||3× 16 HT3||{{tchk|no}}||-||||[[File:LGA-1207 F.svg|x50px]] |

|- | |- | ||

| − | |{{amd|Socket C32|l=package}}||2010||LGA||1207||10h, 15h|| | + | |{{amd|Socket C32|l=package}}||2010||LGA||1207||10h, 15h||2× 72 bit DDR3||3× 16 HT3||{{tchk|no}}||-|| [[Opteron]] <br>4xxx ||[[File:LGA-1207 C32.svg|x50px]] |

|- | |- | ||

| − | |{{amd|Socket G34|l=package}}||2010||LGA||1944||10h, 15h|| | + | |{{amd|Socket G34|l=package}}||2010||LGA||1944||10h, 15h||4× 72 bit DDR3||3× 16 + 2× 8 HT3||{{tchk|no}}||-|| [[Opteron]] <br>6xxx ||[[File:LGA-1944.svg|x50px]] |

| + | |- <!-- Socket SP3 • 2017 • AMD Epyc Naples/Rome/Milan • Server • LGA • 4094 | 58.5×75.4 mm (SP3) • DDR4 --> | ||

| + | |{{amd|Socket SP3|l=package}}||2017||LGA||4094||17h, 19h||8× 72 bit DDR4||8× 16 PCIe 3/4||{{tchk|no}}||integrated||[[EPYC]] <br>[[Naples]] <br>{{amd|Rome|l=core}} <br>[[Milan]]||[[File:FCLGA-4094.svg|x50px]] | ||

| + | |- <!-- Socket SP5 • 2022 • AMD Epyc Genoa/Turin • Server • LGA • 6096 | 72.0×75.4 mm --> | ||

| + | |{{amd|Socket SP5|l=package}}||2022||LGA||6096||19h, 1Ah||12× 80 bit DDR5||8× 16 PCIe 5||{{tchk|no}}||integrated||[[EPYC]] <br>9004/9005 <br>[[Genoa]] <br>{{amd|Turin|l=core}}||[[File:LGA-6096.svg|x50px]] | ||

| + | |- <!-- Socket SP6 • 2024 • AMD Epyc Siena • Server • LGA • 4844 | 58.5×75.4 mm (SP3) • 48 CXL 1.1 --> | ||

| + | |{{amd|Socket SP6|l=package}}||2024||LGA||4844||19h||6× 80 bit DDR5||6× 16 PCIe 5||{{tchk|no}}||integrated||[[EPYC]] <br>8004 <br>{{amd|Siena|l=core}}||[[File:LGA-4844.svg|x50px]] | ||

| + | |- <!-- Socket SP7 • 2025 • AMD Epyc Venice/Verano • Server • LGA • 4844? | 58.5×75.4 mm (SP3) • 48 CXL 3.1 --> | ||

| + | |{{amd|Socket SP7|l=package}}||2025||LGA||-||1Ah||16× 80 bit DDR5||128× PCIe Gen 6 + <br>16× PCIe Gen 4 (2P) <br>96× PCIe Gen 6 + <br>8× PCIe Gen 4 (1P)||{{tchk|no}}||integrated||[[EPYC]] <br>9006/9007 <br>{{amd|Venice|l=core}} <br>{{amd|Verano|l=core}}||[[File:LGA-4844.svg|x50px]] | ||

| + | |- <!-- Socket SP8 • 2026 • AMD Epyc Venice • Server • LGA • 4844? | 58.5×75.4 mm (SP3) • 48 CXL 3.1 --> | ||

| + | |{{amd|Socket SP8|l=package}}||2026||LGA||-||1Ah||8× 80 bit DDR5||192× PCIe Gen 6 + <br>16× PCIe Gen 4 (2P) <br>128× PCIe Gen 6 + <br>8× PCIe Gen 4 (1P)||{{tchk|no}}||integrated||[[EPYC]] <br>9006 <br>{{amd|Venice|l=core}}||[[File:LGA-4844.svg|x50px]] | ||

|- | |- | ||

| − | |||

|} | |} | ||

| + | <references/> | ||

| + | <!-- | ||

| + | *AMD SP7: | ||

| + | :Up To 16-Channel DDR5 Support | ||

| + | :Up To 8000 MT/s DDR5 ECC Memory | ||

| + | :Up To 12800 MT/s DDR5 RDIMM Memory | ||

| + | :Support for RDIMM, 3DS RDIMM, MRDIMM, Tall DIMM | ||

| + | :Up To 128 PCI Gen 6 + 16 PCIe Gen 4 Lanes on 2P Platform | ||

| + | :Up To 96 PCIe Gen 6 + 8 PCIe Gen 4 Lanes on 1P Platform | ||

| + | *AMD SP8: | ||

| + | :Up To 8-Channel DDR5 Support | ||

| + | :Up To 8000 MT/s DDR5 ECC Memory | ||

| + | :Up To 12800 MT/s DDR5 RDIMM Memory | ||

| + | :Support for RDIMM, 3DS RDIMM, MRDIMM, Tall DIMM | ||

| + | :Up To 192 PCI Gen 6 + 16 PCIe Gen 4 Lanes on 2P Platform | ||

| + | :Up To 128 PCIe Gen 6 + 8 PCIe Gen 4 Lanes on 1P Platform | ||

| + | <pre> | ||

| + | • General line | ||

| + | Socket name • Method (number of pins) • Product Family | ||

| − | == Mobile | + | *Socket 5 • PGA 320 • K5 |

| − | {| class="wikitable | + | *Socket 7 • PGA 321 • K5, K6 (Little Foot) |

| + | *Super Socket 7 • PGA 321 • K6-II, K6-III, Rise mP6 | ||

| + | *Slot A • Slot 242 • K7 Athlon | ||

| + | *Socket A • PGA 462 • Athlon, Athlon XP, Duron, Sempron ("Thoroughbred-B" Core) | ||

| + | *Socket 563 • PGA 563 • Mobile Athlon XP | ||

| + | *Socket 754 • PGA 754 • Athlon 64, Sempron, Turion | ||

| + | *Socket 939 • PGA 939 • Athlon 64 (FX/X2), Opteron 1xx | ||

| + | *Socket 940 • PGA 940 • Athlon 64 FX, Opteron | ||

| + | |||

| + | *Socket S1 • PGA 638 • Athlon Mobile, Turion (X2) | ||

| + | *Socket AM1 • PGA 721 • Athlon, Sempron (Kabini) | ||

| + | *Socket AM2 • PGA 940 • Athlon 64 (FX/X2), Opteron, Sempron | ||

| + | *Socket AM2+ • PGA 940 • Athlon (II/X2 Kuma), Phenom (I/II) | ||

| + | *Socket AM3 • PGA 940/941 • Athlon II, Phenom II, Sempron | ||

| + | *Socket AM3+ • PGA 942 • Athlon II, FX (Zambezi, Vishera), Phenom II | ||

| + | *Socket AM4 • PGA 1331 • A-series (Gen 7) APU (Bristol Ridge) | ||

| + | :Ryzen Desktop (Summit Ridge, Pinnacle Ridge, Matisse, Vermeer) | ||

| + | :Ryzen APU (Raven Ridge, Picasso, Renoir) | ||

| + | *Socket AM5 • LGA 1718 • Desktop Ryzen (Raphael, Granite Ridge), Ryzen APU (Phoenix) | ||

| + | |||

| + | *Socket F • LGA 1207 • Athlon 64 FX, Opteron 2xxx/8xxx (multi) | ||

| + | *Socket F+ • LGA 1207 • Athlon 64 FX, Opteron 2xxx/8xxx (multi) | ||

| + | |||

| + | *Socket FS1 • PGA 722 • Mobile APU (Rano) | ||

| + | *Socket FS1+ • PGA 722 • Mobile APU (Trinity, Richland) | ||

| + | *Socket FM1 • PGA 905 • A-series (Gen 1) APU (Lano) | ||

| + | *Socket FM2 • PGA 904 • A-series (Gen 2) APU (Trinity, Richland) | ||

| + | *Socket FM2+ • PGA 906 • A-series (Gen 2) APU (Trinity, Richland) | ||

| + | :Gen 4 APU (Kaveri), (Gen 6) APU (Carrizo) | ||

| + | |||

| + | *Package FT1 • BGA 413 • Mobile APU (Desna, Ontario, Zacate, Hondo) | ||

| + | *Package FP2 • BGA 827 • Mobile APU (Trinity, Richland) | ||

| + | *Package FP3 • BGA 906 • Mobile APU (Kaveri) | ||

| + | *Package FT3/FT3b • BGA 769 • Mobile APU (Kabini, Temasi, Bima, Mullins) | ||

| + | *Package FP4 • BGA 769 • Mobile APU (Carrizo, Carrizo-L) | ||

| + | *Package FP5 • BGA 1140 • Mobile Ryzen (Raven Ridge, Picasso) | ||

| + | *Package FP6 • BGA 1140 • Mobile Ryzen (Renoir, Cezanne, Barcelo) | ||

| + | *Package FP7 • BGA • Mobile Ryzen (Rembrandt, Phoenix, Hawk Point) | ||

| + | *Package FL1 • BGA • Mobile Ryzen (Dragon Ridge) | ||

| + | *Package FT6 • BGA • Mobile Ryzen (Mendocino) | ||

| + | |||

| + | • Server/Workstation | ||

| + | Socket name • Method (number of pins) • Product Family | ||

| + | |||

| + | *Socket C32 • LGA 1207 • Opteron 4xxx (Multiprocessor support) | ||

| + | *Socket G34 • LGA 1974 • Opteron 6xxx (Multiprocessor support) | ||

| + | *Socket TR4 • LGA 4094 • Ryzen Threadripper (Gen 1/2) | ||

| + | *Socket sTRX4 • LGA 4094 • Ryzen Threadripper (Gen 3) | ||

| + | *Socket sWRX8 • LGA 4094 • Ryzen Threadripper Pro (Gen 3/4) | ||

| + | *Socket sTRX5 • LGA 4844 • Ryzen Threadripper (Gen 5) | ||

| + | *Socket SP3 • LGA 4094 • EPYC 7xxx (Gen 1-3) 700x (Naples, Rome, Milan) | ||

| + | *Socket SP5 • LGA 6096 • EPYC 9xxx (Gen 4) 9004 (Genoa, Bergamo) | ||

| + | *Socket SP6 • LGA 4844 • EPYC 8xxx (Gen 4) 8004 (Siena) | ||

| + | </pre> | ||

| + | --> | ||

| + | |||

| + | == Mobile Sockets (mainstream) == | ||

| + | {| class="wikitable mw-datatable" style="margin:0.5em auto; text-align:center; min-width:70em;" | ||

| + | |- | ||

!Name!!Year!!Type!!Pins!!Fam.!!MC!!I/O lanes!!APU!!FCH!!Notes!!Package | !Name!!Year!!Type!!Pins!!Fam.!!MC!!I/O lanes!!APU!!FCH!!Notes!!Package | ||

|- | |- | ||

| − | |{{amd|Super Socket 7|l=package}}||1998||PGA||321|||| | + | |{{amd|Super Socket 7|l=package}}||1998||PGA||321||5||-||FSB||{{tchk|no}}||-||||[[File:CPGA-321.svg|x50px]] |

| + | |- | ||

| + | |{{amd|Socket A|l=package}}||2000||PGA||462||6||-||FSB||{{tchk|no}}||-||||[[File:OPGA-453.svg|x50px]] <!-- [[File:CPGA-453.svg|x50px]] --> | ||

| + | |- | ||

| + | |{{amd|Socket 563|l=package}}||2003||PGA||563||6||-||FSB||{{tchk|no}}||-||||[[File:OPGA-563.svg|x50px]] | ||

|- | |- | ||

| − | |{{amd|Socket | + | |{{amd|Socket 754|l=package}}||2003||PGA||754||0Fh||72 bit DDR||16 HT1||{{tchk|no}}||-||||[[File:OPGA-754.svg|x50px]] |

|- | |- | ||

| − | |{{amd|Socket | + | |{{amd|Socket S1g1|l=package}}||2006||PGA||638||NPT 0Fh||144 bit DDR2||16 HT1||{{tchk|no}}||-||||[[File:OPGA-638.svg|x50px]] |

|- | |- | ||

| − | |{{amd|Socket | + | |{{amd|Socket S1g2|l=package}}||2008||PGA||638||11h||2× 64 bit DDR2||16 HT3||{{tchk|no}}||-||||[[File:OPGA-638.svg|x50px]] |

|- | |- | ||

| − | |{{amd|Socket | + | |{{amd|Socket S1g3|l=package}}||2009||PGA||638||10h||2× 64 bit DDR2||16 HT3||{{tchk|no}}||-||||[[File:OPGA-638.svg|x50px]] |

|- | |- | ||

| − | |{{amd| | + | |{{amd|ASB1|Package ASB1|l=package}}||2009||BGA||812||NPT 0Fh||144 bit DDR2||16 HT1||{{tchk|no}}||-||||[[File:BGA-812.svg|x50px]] |

|- | |- | ||

| − | |{{amd|Socket | + | |{{amd|Socket S1g4|l=package}}||2010||PGA||638||10h||2× 64 bit DDR3||16 HT3||{{tchk|no}}||-||||[[File:OPGA-638.svg|x50px]] |

|- | |- | ||

| − | |{{amd| | + | |{{amd|ASB2|Package ASB2|l=package}}||2010||BGA||812||10h||2× 72 bit DDR3||16 HT3||{{tchk|no}}||-||||[[File:BGA-812.svg|x50px]] |

|- | |- | ||

| − | |{{amd|Socket | + | |{{amd|Socket FS1|l=package}}||2011||PGA||722||12h||2× 64 bit DDR3||16 + 4 PCIe 2||{{tchk|yes}}||4 PCIe 2||||[[File:OPGA-722.svg|x50px]] |

|- | |- | ||

| − | |{{amd| | + | |{{amd|Socket FS1r2|l=package}}||2012||PGA||722||15h||2× 64 bit DDR3||16 + 4 PCIe 2||{{tchk|yes}}||4 PCIe 2||||[[File:OPGA-722.svg|x50px]] |

|- | |- | ||

| − | |{{amd| | + | |{{amd|FP2|Package FP2|l=package}}||2012||BGA||827||15h||2× 64 bit DDR3||16 + 4 PCIe 2||{{tchk|yes}}||4 PCIe 2||||[[File:BGA-827.svg|x50px]] |

|- | |- | ||

| − | |{{amd| | + | |{{amd|FP3|Package FP3|l=package}}||2014||BGA||854||15h||2× 72 bit DDR3||16 + 8 PCIe 2/3||{{tchk|yes}}||4 PCIe 2||||[[File:BGA-854.svg|x50px]] |

|- | |- | ||

| − | |{{amd| | + | |{{amd|FP4|Package FP4|l=package}}||2015||BGA||968||15h, 16h||2× 72 bit DDR3/4||8 + 4 PCIe 3||{{tchk|yes}}||integrated||||[[File:BGA-968.svg|x50px]] |

|- | |- | ||

| − | |{{amd| | + | |{{amd|FP5|Package FP5|l=package}}||2018||BGA||1140||17h||2× 72 bit DDR4||8 + 8 PCIe 3||{{tchk|yes}}||integrated||Zen, Zen+||[[File:BGA-1140.svg|x50px]] |

|- | |- | ||

| − | |{{amd| | + | |{{amd|FP6|Package FP6|l=package}}||2020||BGA||1140||17h, 19h||2× 72 bit DDR4<br>4× 32 bit LPDDR4x||8 + 12 PCIe 3||{{tchk|yes}}||integrated||Zen 2, Zen 3||[[File:BGA-1140.svg|x50px]] |

|- | |- | ||

| − | |{{amd| | + | |{{amd|FP7|Package FP7|l=package}} <br>{{amd|FP7r2|Package FP7r2|l=package}}||2022||BGA||1140||19h||4× DDR5-4800, <br>4× LPDDR5-6400||8 + 12 PCIe 4||{{tchk|yes}}||integrated||Zen 3+ <br>Rembrandt||[[File:BGA-1140.svg|x50px]] |

|- | |- | ||

| − | |{{amd| | + | |{{amd|FP8|Package FP8|l=package}}||2024||BGA||-||1Ah||4× DDR5-4800, <br>4× LPDDR5-6400||16 PCIe 4||{{tchk|yes}}||integrated||Zen 5 <br>Strix Point||[[File:BGA-2020.svg|x50px]] |

| + | |- | ||

| + | |{{amd|FP10|Package FP10|l=package}}||2024||BGA||1384||1Ah||4× DDR5-4800, <br>4× LPDDR5-6400||16 PCIe 4||{{tchk|yes}}||integrated||Zen 6 <br>Medusa Point||[[File:BGA-1384.svg|x50px]] <!-- 25x42.5 mm AL --> | ||

| + | |- | ||

| + | |{{amd|FP11|Package FP11|l=package}}||2025||BGA||2077||1Ah||4× DDR5-4800, <br>4× LPDDR5-6400||16 PCIe 4||{{tchk|yes}}||integrated||Zen 5 <br>Strix Halo||[[File:BGA-2077.svg|x50px]] | ||

|- | |- | ||

|} | |} | ||

| + | <references/> | ||

| − | == Mobile | + | == Mobile Sockets (ultrathin, tablet) == |

| − | {| class="wikitable | + | {| class="wikitable mw-datatable" style="margin:0.5em auto; text-align:center; min-width:70em;" |

| − | !Name!!Year!!Type!!Pins!! | + | |- |

| + | !Name!!Year!!Type!!Pins!!Famimy!!MC!!I/O lanes!!APU!!FCH!!Notes!!Package | ||

| + | |- | ||

| + | |{{amd|FT1|Package FT1|l=package}}||2011||BGA||413||14h||64 bit DDR3||4 PCIe 2||{{tchk|yes}}||4 PCIe 2||||[[File:BGA-413.svg|x50px]] | ||

| + | |- | ||

| + | |{{amd|FT3|Package FT3|l=package}}||2013||BGA||769||16h||72 bit DDR3||4 PCIe 2||{{tchk|yes}}||4 PCIe 2||||[[File:BGA-769.svg|x50px]] | ||

| + | |- | ||

| + | |{{amd|FT3b|Package FT3b|l=package}}||2014||BGA||769||16h||72 bit DDR3||4 PCIe 2||{{tchk|yes}}||4 PCIe 2||||[[File:BGA-769.svg|x50px]] | ||

|- | |- | ||

| − | |{{amd| | + | |{{amd|FT4|Package FT4|l=package}}||2016||BGA||769||15h||64 bit DDR3/4||8 PCIe 3||{{tchk|yes}}||integrated||||[[File:BGA-769.svg|x50px]] |

|- | |- | ||

| − | |{{amd| | + | |{{amd|FT5|Package FT5|l=package}}||2020||BGA||-||17h||2× DDR4, LPDDR4||8 PCIe 3||{{tchk|yes}}||integrated||Zen|| |

|- | |- | ||

| − | |{{amd| | + | |{{amd|FT6|Package FT6|l=package}}||2022||BGA||-||17h||2× DDR5, LPDDR5||4 PCIe 3||{{tchk|yes}}||integrated||Zen 2|| |

|- | |- | ||

| − | |{{amd| | + | |{{amd|FL1|Package FL1|l=package}}||2023||BGA||1763||19h, 1Ah||2× DDR5, LPDDR5||4 PCIe 4||{{tchk|yes}}||integrated||Zen 4/5|| <!-- Dragon Range/Fire Range • 40 × 40 mm (FL1 BGA-1763/AM5 LGA-1718) --> |

|- | |- | ||

| − | |||

|} | |} | ||

| + | <references/> | ||

| − | == Embedded | + | == Embedded Sockets == |

| − | {| class="wikitable | + | {| class="wikitable mw-datatable" style="margin:0.5em auto; text-align:center; min-width:70em;" |

| + | |- | ||

!Name!!Year!!Type!!Pins!!Fam.!!MC!!I/O lanes!!APU!!FCH!!Notes!!Package | !Name!!Year!!Type!!Pins!!Fam.!!MC!!I/O lanes!!APU!!FCH!!Notes!!Package | ||

|- | |- | ||

| − | |{{amd|ASB1|Package ASB1|l=package}}||2009||BGA||812||0Fh||144 bit DDR2||HT1|| | + | |{{amd|ASB1|Package ASB1|l=package}}||2009||BGA||812||NPT 0Fh||144 bit DDR2||16 HT1||{{tchk|no}}||-||||[[File:BGA-812.svg|x50px]] |

| + | |- | ||

| + | |{{amd|ASB2|Package ASB2|l=package}}||2010||BGA||812||10h||2× 72 bit DDR3||16 HT3||{{tchk|no}}||-||||[[File:BGA-812.svg|x50px]] | ||

| + | |- | ||

| + | |{{amd|FT1|Package FT1|l=package}}||2011||BGA||413||14h||64 bit DDR3||4 PCIe 2||{{tchk|yes}}||4 PCIe2||||[[File:BGA-413.svg|x50px]] | ||

| + | |- | ||

| + | |{{amd|FP2|Package FP2|l=package}}||2012||BGA||827||15h||2× 64 bit DDR3||16 + 4 PCIe 2||{{tchk|yes}}||4 PCIe2||||[[File:BGA-827.svg|x50px]] | ||

| + | |- | ||

| + | |{{amd|FT3|Package FT3|l=package}}||2013||BGA||769||16h||72 bit DDR3||4 PCIe 2||{{tchk|yes}}||4 PCIe2||||[[File:BGA-769.svg|x50px]] | ||

| + | |- | ||

| + | |{{amd|FP3|Package FP3|l=package}}||2014||BGA||854||15h||2× 72 bit DDR3||16 + 8 PCIe 2/3||{{tchk|yes}}||4 PCIe2||||[[File:BGA-854.svg|x50px]] | ||

|- | |- | ||

| − | |{{amd| | + | |{{amd|SP1|Package SP1|l=package}}||2014||BGA||1021||||2× 72 bit DDR3/4||8 PCIe 3||{{tchk|no}}||integrated|||| |

|- | |- | ||

| − | |{{amd| | + | |{{amd|FT3b|Package FT3b|l=package}}||2014||BGA||769||16h||72 bit DDR3||4 PCIe 2||{{tchk|yes}}||4 PCIe2||||[[File:BGA-769.svg|x50px]] |

|- | |- | ||

| − | |{{amd| | + | |{{amd|FP4|Package FP4|l=package}}||2015||BGA||968||15h, 16h||2× 72 bit DDR3/4||8 + 4 PCIe 3||{{tchk|yes}}||integrated||||[[File:BGA-968.svg|x50px]] |

|- | |- | ||

| − | |{{amd| | + | |{{amd|FP5|Package FP5|l=package}}||2018||BGA||1140||17h||2× 72 bit DDR4||8 + 8 PCIe 3||{{tchk|yes}}||integrated||||[[File:BGA-1140.svg|x50px]] |

|- | |- | ||

| − | |{{amd| | + | |{{amd|Socket SP3|l=package}}||2017||LGA||4094||17h||8× 72 bit DDR4||8× 16 PCIe 3||{{tchk|no}}||integrated |

| + | |<ref>Embedded versions of EPYC 7001 & 7002 processors, hence Family 17h only.</ref> | ||

| + | |[[File:FCLGA-4094.svg|x50px]] | ||

|- | |- | ||

| − | |{{amd| | + | |{{amd|SP4|Package SP4|l=package}}||2018||BGA||2028||17h||4× 72 bit DDR4||4× 16 PCIe 3||{{tchk|no}}||integrated||||[[File:BGA-2028.svg|x50px]] |

|- | |- | ||

| − | |{{amd| | + | |{{amd|SP4r2|Package SP4r2|l=package}}||2018||BGA||2028||17h||2× 72 bit DDR4||2× 16 PCIe 3||{{tchk|no}}||integrated||||[[File:BGA-2028.svg|x50px]] |

|- | |- | ||

| − | |{{amd| | + | |{{amd|FP6|Package FP6|l=package}}||2020||BGA||1140||17h||2× 72 bit DDR4<br>4× 32 bit LPDDR4x||8 + 12 PCIe 3||{{tchk|yes}}||integrated||||[[File:BGA-1140.svg|x50px]] |

| + | |} | ||

| + | <references/> | ||

| + | |||

| + | == Game Consoles == | ||

| + | {| class="wikitable mw-datatable" style="margin:0.5em auto; text-align:center; min-width:70em;" | ||

|- | |- | ||

| − | + | !Name!!Year!!Type!!Pins!!Family!!MC!!I/O!!APU!!FCH!!Notes | |

|- | |- | ||

| − | |{{amd| | + | |{{wp|Xbox_One|Xbox One X}} <br>{{amd|BGA-2409|l=pack}}||2017||BGA||2409||16h||12× 32 bit GDDR5||8 PCIe 3||{{tchk|yes}}||||[[File:BGA-2409.svg|x50px]] |

|- | |- | ||

| − | |{{amd| | + | |{{wp|Xbox_Series_X_and_Series_S|Xbox Series X/S}} <br>{{amd|BGA-2963|l=pack}}||2020||BGA||2963||17h||20× 16 bit GDDR6||8 PCIe 4||{{tchk|yes}}||Arden ES||Lidless package with stiffener frame, <br>52.5 × 52.5 mm, 0.8+ mm multi-pitch<ref name="ISSCC2021-XSX"/><ref name="Paternoster2021"/> |

|- | |- | ||

| − | |||

|} | |} | ||

| + | |||

| + | *Microsoft XBOX Series X • ADN-A0 (Arden A0), XBX/BGA-2963, ADN-A0, Arden ES, 8C/16T, 8 MB, 3.60/3.80 GHz • MS XBOX | ||

| + | *Microsoft XBOX Series S • ADN-A0 (Arden A0), XBS/BGA-2963, ADN-A0, Arden ES, 8C/16T, 8 MB, 3.40/3.60 GHz • MS XBOX | ||

| + | *Sony Playstation 5 • ARL-A0 (Ariel A0), PS5/BGA ??, ARL-A0, Ariel ES/Oberon, 8C/16T, 32 MB, 1.60/3.20 GHz • [https://forum.ixbt.com/topic.cgi?id=8:26120-112 Sony PS5] | ||

| + | |||

| + | <references> | ||

| + | <ref name="ISSCC2021-XSX">{{cite presentation|presenters=Paternoster, Paul|authors=Maki, Andy;Hernandez, Andres;Grossman, Mark;Lau, Michael;Sutherland, David;Mathad, Aditya|title=XBOX SERIES X SoC – A Next Generation Gaming Console|slides=File:ISSCC2021 3.1 XSX Paternoster slides.pdf|date=2021-02-15|conference=IEEE ISSCC 2021|session=3.1}}</ref> | ||

| + | <ref name="Paternoster2021">{{cite article|authors=Paternoster, Paul;Maki, Andy;Hernandez, Andres;Grossman, Mark;Lau, Michael;Sutherland, David;Mathad, Aditya|title=XBOX Series X: A Next-Generation Gaming Console SoC|date=2021-02|conference=Proceedings of IEEE ISSCC 2021|pages=46-48|doi=10.1109/ISSCC42613.2021.9366057}}</ref> | ||

| + | </references> | ||

| + | <!-- | ||

| + | 100-000000001 - XBX / BGA 2963 - ADN-A0 - XBOX Series X / Arden ES - 8C / 16T - 8 MB - 3,60 GHz / 3,80 GHz • MS XBOX | ||

| + | 100-000000002 - XBS / BGA ?? - XBOX Series S - 8C / 16T - 8 MB - 3,40 GHz / 3,60 GHz • 299 EUR MS Box | ||

| + | 100-000000004 - PS5 / BGA ?? - ARL-A0 - Ariel ES 13F9 (PS5) - 8C / 16T - 32 MB - 1,60 GHz / 3,20 GHz • Sony PS5 | ||

| + | 100-000000189 - BGA (PS5) - ARL-?? - Ariel / Oberon (PS5) - 8C / 16T - 32 MB - 1,60 GHz / 3,20 GHz • Sony PS5 | ||

| + | 100-000000228 - XBX / BGA 2963 - ADN-B0 - Arden (Xbox) - 8C / 16T - 8 MB - 3,60 GHz / 3,80 GHz • 499 EUR MS XBOX | ||

| + | |||

| + | spez-Variant: | ||

| + | ADN-A0 : Arden A0, Microsoft XBOX Series X | ||

| + | ARL-A0 : Ariel A0, Sony Playstation 5 | ||

| + | |||

| + | Steppings (ZEN2): | ||

| + | SSP-B0 - Starship B0, EPYC 7xx2 CPUs, Threadripper 3xxx CPUs | ||

| + | RN-A1 - Renoir A1, Ryzen 4xxx G, GE, U, H APUs | ||

| + | LCN-A1 - Lucienne A1, Ryzen 5xxx G, GE, U APUs (Update Renoir) | ||

| + | MTS-B0 - Matisse B0, Ryzen 3xxx CPUs (no 3xxx APUs) | ||

| + | |||

| + | Steppings (ZEN3): | ||

| + | GN-B1 - Genesis B1, EPYC 7xx3 CPUs, Threadripper 5xxx CPUs | ||

| + | VMR-B0 - Vermeer B0, Ryzen 5xxx CPUs (no 5xxx APUs) | ||

| + | VMR-B2 - Vermeer B2, Ryzen 5xxx CPUs (no 5xxx APUs) | ||

| + | BRC-A0 - Barcelo, A0, Ryzen 5x25 APU | ||

| + | |||

| + | Eng. Samples: | ||

| + | LCN-A0 - Lucienne A0 ES, Zen2 APU (Update Renoir) | ||

| + | GN-A0 - Genesis A0 ES, Zen3 High End CPU | ||

| + | GN-B0 - Genesis B0 ES, Zen3 Server CPU | ||

| + | GN-B2 - Genesis B2 ES, Zen3 Server CPU Refresh | ||

| + | VMR-A0 - Vermeer A0 ES, Zen3 Desktop CPU | ||

| + | CZN-A0 - Cezanne A0 ES, Zen3 APU | ||

| + | --> | ||

| + | |||

| + | == AMD CPU Packages == | ||

| + | <table class="wikitable sortable"> | ||

| + | <tr><th colspan="8" style="background:#D6D6FF;">AMD CPU Packages</th></tr> | ||

| + | <tr><th colspan="4">General</th><th colspan="4">Details</th></tr> | ||

| + | <tr><th>Name</th><th>Package</th><th>Contacts</th><th>[[TDP]]</th><th>Socket</th><th>[[µarch]]</th><th>Market</th><th>Release</th></tr> | ||

| + | {{#ask: | ||

| + | <!-- [[Category:~*]] --> | ||

| + | [[instance of::package]] | ||

| + | [[designer::AMD]] | ||

| + | |?name | ||

| + | |?name | ||

| + | |?package | ||

| + | |?package contacts | ||

| + | |?tdp | ||

| + | |?socket | ||

| + | |?microarchitecture | ||

| + | |?market segment | ||

| + | |?first_launched | ||

| + | |sort=name | ||

| + | |order=ascending | ||

| + | |format=template | ||

| + | |template=proc table 2 | ||

| + | |userparam=9 | ||

| + | |valuesep=, | ||

| + | |mainlabel=- | ||

| + | }} | ||

| + | </table> | ||

| + | |||

| + | === [[AMD]] CPU sockets === | ||

| + | {| border="0" cellpadding="5" width="90%" | ||

| + | |- | ||

| + | |width="30%" valign="top" align="left"| | ||

| + | :;Desktop sockets | ||

| + | * {{amd|Socket 940|l=package}} (2003) | ||

| + | * {{amd|Socket 939|l=package}} (2004) | ||

| + | * {{amd|Socket AM2|l=package}} (2006) | ||

| + | * {{amd|Socket AM2+|l=package}} (2007) | ||

| + | * {{amd|Socket AM3|l=package}} (2009) | ||

| + | * {{amd|Socket AM3+|l=package}} (2011) | ||

| + | * {{amd|Socket FM1|l=package}} (2011) | ||

| + | * {{amd|Socket FM2|l=package}} (2012) | ||

| + | * {{amd|Socket FM2+|l=package}} (2014) | ||

| + | * {{amd|Socket AM1|l=package}} (2014) | ||

| + | * {{amd|Socket AM4|l=package}} (2016) | ||

| + | * {{amd|Socket TR4|l=package}} (2017) <!-- Whitehaven, Colfax --> | ||

| + | * {{amd|Socket sTRX4|l=package}} (2019) <!-- Castle Peak --> | ||

| + | * {{amd|Socket sWRX8|l=package}} (2020) <!-- Castle Peak, Chagall --> | ||

| + | * {{amd|Socket AM5|l=package}} (2022) | ||

| + | * {{amd|Socket sTR5|l=package}} (2023) <!-- Storm Peak --> | ||

| + | * {{amd|Socket AM6|l=package}} (2026) <!-- Zen 7, DDR6, PCIe 6.0, LGA-2100, 67×106 mm (2028?) --> | ||

| + | |width="30%" valign="top" align="left"| | ||

| + | :;Mobile sockets | ||

| + | * {{amd|Socket 563|l=package}} (2002) | ||

| + | * {{amd|Socket S1|l=package}} (2006) | ||

| + | * {{amd|Socket S1|S1g2, S1g3, S1g4|l=package}} | ||

| + | * {{amd|Socket FS1|l=package}} (2011) | ||

| + | * {{amd|FT1|Package FT1|l=package}} (2011) | ||

| + | * {{amd|FP2|Package FP2|l=package}} (2012) | ||

| + | * {{amd|FT3|Package FT3|l=package}} (2013) | ||

| + | * {{amd|FP3|Package FP3|l=package}} (2014) | ||

| + | * {{amd|FP4|Package FP4|l=package}} (2015) <!-- Carrizo --> | ||

| + | * {{amd|FT4|Package FT4|l=package}} (2016) <!-- Stoney Ridge --> | ||

| + | * {{amd|FP5|Package FP5|l=package}} (2019) <!-- Raven Ridge, Picasso, Dali, Banded Kestrel: f17h m18h rb1 --> | ||

| + | * {{amd|FT5|Package FT5|l=package}} (2020) <!-- Pollock (3015e, 3015Ce) --> | ||

| + | * {{amd|FP6|Package FP6|l=package}} (2020) <!-- Renoir, Lucienne, Cezanne, Grey Hawk, Barcelo --> | ||

| + | * {{amd|FP7|Package FP7|l=package}} (2022) <!-- Rembrandt, Phoenix --> | ||

| + | * {{amd|FL1|Package FL1|l=package}} (2023) <!-- Dragon Range --> | ||

| + | * {{amd|FP8|Package FP8|l=package}} (2024) <!-- Phoenix --> | ||

| + | * {{amd|FP11|Package FP11|l=package}} (2025) | ||

| + | |width="30%" valign="top" align="left"| | ||

| + | :;Combined sockets | ||

| + | * {{amd|Super Socket 7|l=package}} (1998) • [CPGA-321] <!-- CBGA-360 was a package for the Mobile AMD K6. | ||

| + | Other members of the K6 family used the [[amd/packages/super socket 7|CPGA-321]] and {{\\|OBGA-349}} package. --> | ||

| + | * {{amd|Slot A|l=package}} (Desktop) (1999) | ||

| + | * {{amd|Socket A|l=package}} (2000) | ||

| + | * {{amd|Socket 754|l=package}} (2003) | ||

| + | |||

| + | :;Server sockets | ||

| + | * {{amd|Socket 940|l=package}} (2003) | ||

| + | * {{amd|Socket F|l=package}} (2006) | ||

| + | * {{amd|Socket F|Fr2, Fr3, Fr5, Fr6|l=package}} (F+) <!-- | ||

| + | * {{amd|G3|Socket G3|l=package}} (not released) --> | ||

| + | * {{amd|C32|Socket C32|l=package}} (2010) | ||

| + | * {{amd|G34|Socket G34|l=package}} (2010) | ||

| + | * {{amd|SP1|Package SP1|l=package}} (2014) | ||

| + | * {{amd|SP3|Socket SP3|l=package}} (2017) <!-- Naples, Rome, Milan, Milan-X --> | ||

| + | * {{amd|SP4|Package SP4|l=package}} (2018) <!-- Snowy Owl --> | ||

| + | * {{amd|SP5|Socket SP5|l=package}} (2022) <!-- Genoa, Genoa-X, Bergamo --> | ||

| + | * {{amd|SP6|Socket SP6|l=package}} (2023) <!-- Siena --> | ||

| + | * {{amd|SP7|Socket SP7|l=package}} (2025) | ||

| + | * {{amd|SP8|Socket SP8|l=package}} (2026) | ||

| + | |} | ||

| + | |||

| + | == Packages to Scale == | ||

| + | [[File:BGA-413.svg|76px|FT1 19 mm × 19 mm (BGA)]] | ||

| + | [[File:BGA-769.svg|96px|FT3/FT3b/FT4 24.5 mm × 24.5 mm (BGA)]] | ||

| + | [[File:BGA-812.svg|106px|ASB1/ASB2 27 mm × 27 mm (BGA)]] | ||

| + | [[File:BGA-827.svg|121px|FP2 31 mm × 27 mm (BGA)]] | ||

| + | [[File:BGA-854.svg|113px|FP3 29 mm × 32 mm (BGA)]] | ||

| + | [[File:BGA-968.svg|144px|FP4 37 mm × 29 mm (BGA)]] | ||

| + | [[File:BGA-1140.svg|136px|FP5/FP6 35 mm × 25 mm (BGA)]] | ||

| + | |||

| + | [[File:OPGA-563.svg|129px|Socket 563 33 mm × 33 mm]] | ||

| + | [[File:OPGA-638.svg|136px|S1 35 mm × 35 mm]] | ||

| + | [[File:OPGA-722.svg|136px|FS1/FS1r2 35 mm × 35 mm]] | ||

| + | [[File:OPGA-721.svg|136px|AM1 35 mm × 35 mm]] | ||

| + | [[File:OPGA-754.svg|155px|Socket 754 40 mm × 40 mm]] | ||

| + | [[File:OPGA-940 S940.svg|155px|Socket 940 40 mm × 40 mm]] | ||

| + | |||

| + | [[File:OPGA-939.svg|155px|Socket 939 40 mm × 40 mm]] | ||

| + | [[File:LGA-1207 F.svg|155px|Socket F 40 mm × 40 mm]] | ||

| + | [[File:LGA-1207 C32.svg|155px|C32 40 mm × 40 mm]] | ||

| + | [[File:OPGA-940 AM2.svg|155px|AM2/AM2+ 40 mm × 40 mm]] | ||

| + | [[File:OPGA-905.svg|155px|FM1 40 mm × 40 mm]] | ||

| + | |||

| + | [[File:OPGA-938.svg|155px|AM3 40 mm × 40 mm]] | ||

| + | [[File:OPGA-941.svg|155px|AM3+ 40 mm × 40 mm]] | ||

| + | [[File:OPGA-904.svg|155px|FM2 40 mm × 40 mm]] | ||

| + | [[File:OPGA-906.svg|155px|FM2+ 40 mm × 40 mm]] | ||

| + | [[File:socket_am4.svg|151px|AM4 40 mm × 40 mm]] | ||

| + | |||

| + | [[File:LGA-1718.svg|155px|AM5 40 mm × 40 mm]] | ||

| + | [[File:CPGA-321.svg|191px|Socket 7/Super 7 49.5 mm × 49.5 mm]] | ||

| + | [[File:OPGA-453.svg|191px|Socket A 49.5 mm × 49.5 mm]] | ||

| + | [[File:BGA-2409.svg|193px|XBox One X BGA-2409 50 mm × 50 mm]] | ||

| + | |||

| + | [[File:LGA-1944.svg|231px|G34 60 mm × 42.5 mm]] | ||

| + | [[File:FCLGA-4094.svg|289px|SP3/TR4/sTRX4/sWRX8 75.4 mm × 58.5 mm]] | ||

| + | [[File:LGA-6096.svg|289px|SP5 75.4 mm × 72.0 mm]] | ||

| + | |||

| + | <span style="width:170px;height:170px;line-height:170px;border:1px solid #000;display:inline-block;text-align:center" title="SP4/SP4r2 45 mm × 45 mm">SP4/SP4r2</span> | ||

| + | <span style="width:198px;height:198px;line-height:198px;border:1px solid #000;display:inline-block;text-align:center" title="XBox Series X/S 52.5 mm × 52.5 mm">XBox Series X/S</span> | ||

[[Category:amd]] | [[Category:amd]] | ||

Latest revision as of 16:14, 1 October 2025

Contents

Overview[edit]

| Year | Desktop | Desktop APU | Server | Mobile | Tablet | Embedded |

|---|---|---|---|---|---|---|

| 1998 | Super 7 (321) | Super 7 (321) | ||||

| 1999 | Slot A (242) | |||||

| 2000 | Socket A (462) | Socket A (462) | ||||

| 2002 | 563 | |||||

| 2003 | 754, 940 | 940 | 754 | |||

| 2004 | 939 | |||||

| 2006 | AM2, Fr3 | F, L (1207FX) | S1g1 | |||

| 2007 | AM2+ | Fr2 | ||||

| 2008 | Fr5 | S1g2 | ||||

| 2009 | AM3 | Fr6 | S1g3 | ASB1 | ||

| 2010 | C32, G34 | S1g4 | ASB2 | |||

| 2011 | FM1 | FS1 | FT1 | FT1 | ||

| 2012 | AM3+ | FM2 | FS1r2, FP2 | FP2 | ||

| 2013 | FT3 | FT3 | ||||

| 2014 | FM2+, AM1 | FP3 | FT3b | FP3, FT3b, SP1 | ||

| 2015 | FP4 | FP4 | ||||

| 2016 | AM4 | AM4 | FT4 | |||

| 2017 | TR4 | SP3 (Zen 2/3) | ||||

| 2018 | FP5 (Zen/Zen+) | FP5, SP4, SP4r2 | ||||

| 2019 | sTRX4 | |||||

| 2020 | sWRX8 | FP6 (Zen 2/3) | FT5 | FP6 (Zen 2/3) | ||

| 2022 | AM5 | AM5 | SP5 (Zen 4/5) | FP7 | FT6 | FP7 |

| 2023 | sTR5 | sTR5 | FP7r2 | FL1 | FP7r2 | |

| 2024 | SP6 (Siena) | FP8, FP10 | FP8, FP10 | |||

| 2025 | SP7 (Venice) | FP11, FP12 | FP11, FP12 | |||

| 2026 | AM6 | AM6 | SP8 (Venice) | |||

| 2027 |

Desktop/HEDT/Workstation Sockets[edit]

| Name (a.k.a.) | Year | Type[1] | Contacts | AMD CPU ID | MC[2] | I/O lanes[3] | APU[4] | FCH[5] | Notes | Package[6] |

|---|---|---|---|---|---|---|---|---|---|---|

| Super Socket 7 | 1998 | PGA | 321 | 5 | - | FSB | ✘ | - |

| |

| Slot A | 1999 | SEC | 242 | 6 | - | FSB | ✘ | - | ||

| Socket A | 2000 | PGA | 462 | 6 | - | FSB | ✘ | - |  x50px | |

| Socket 563 | 2003 | PGA | 563 | 6 | - | FSB | ✘ | - |

| |

| Socket 754 | 2003 | PGA | 754 | 0Fh | 72 bit DDR | 16 HT1 | ✘ | - |

| |

| Socket 940 | 2003 | PGA | 940 | 0Fh | 144 bit DDR | 3× 16 HT1 | ✘ | - |

| |

| Socket 939 | 2004 | PGA | 939 | 0Fh | 144 bit DDR | 16 HT1 | ✘ | - |

| |

| Socket AM2 | 2006 | PGA | 940 | NPT 0Fh | 144 bit DDR2 | 16 HT1 | ✘ | - |

| |

| Socket Fr3 | 2006 | LGA | 1207 | NPT 0Fh | 2× 72 bit DDR2 | 3 × 16 HT1 | ✘ | - |

| |

| Socket AM2+ (AM2r2) |

2007 | PGA | 940 | 10h | 2× 72 bit DDR2 | 16 HT3 | ✘ | - |

| |

| Socket AM3 | 2009 | PGA | 938 | 10h | 2× 72 bit DDR2/3 | 16 HT3 | ✘ | - |

| |

| Socket FM1 | 2011 | PGA | 905 | 12h | 2× 72 bit DDR3 | 16 + 4 PCIe 2 | ✔ | 4 PCIe 2 |

| |

| Socket AM3+ (AM3b) |

2012 | PGA | 941 | 15h | 2× 72 bit DDR3 | 16 HT3 | ✘ | - |

| |

| Socket FM2 | 2012 | PGA | 904 | 15h | 2× 64 bit DDR3 | 16 + 4 PCIe 2 | ✔ | 4 PCIe 2 |

| |

| Socket AM1 (FS1b) |

2014 | PGA | 721 | 16h | 72 bit DDR3 | 4 + 4 PCIe 2 | ✔ | integrated |

| |

| Socket FM2+ (FM2b, FM2r2) |

2014 | PGA | 906 | 15h | 2× 64 bit DDR3 | 16 + 4 PCIe 2/3 | ✔ | 4 PCIe 2 |

| |

| Socket AM4 | 2016 | PGA | 1331 | 15h, 17h, 19h | 2× 72 bit DDR3/4 | 16 + 4 PCIe 3/4 | ✔ | 4 PCIe 3/4 |

| |

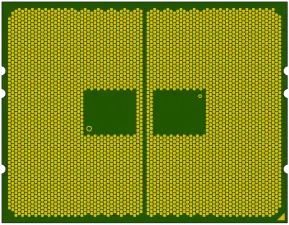

| Socket TR4 (SP3r2) |

2017 | LGA | 4094 | 17h | 4× 72 bit DDR4 | 4× 16 PCIe 3 | ✘ |

| ||

| Socket sTRX4 (SP3r3) |

2019 | LGA | 4094 | 17h | 4× 72 bit DDR4 | 4× 16 PCIe 4 | ✘ |

| ||

| Socket sWRX8 (SP3r4) |

2020 | LGA | 4094 | 17h, 19h | 8× 72 bit DDR4 | 8× 16 PCIe 4 | ✘ |

| ||

| Socket AM5 | 2022 | LGA | 1718 | 19h | 2× 72 bit DDR5 | 16 + 4 + 4 PCIe 4/5 | ✔ | 4 PCIe 4/5 |

| |

| Socket sTR5 | 2023 | LGA | 4844 | 19h | 8× 72 bit DDR5 (RDIMM w/ ECC) |

8× 16 PCIe 5 | ✔ | 4 PCIe 4/5 | TRX50, WRX90 |

x50px |

- ↑ PGA = Pin Grid Array, BGA = Ball Grid Array (CPU package soldered directly to the motherboard), LGA = Land Grid Array, SEC = Single Edge Cartridge (printed circuit board with an edge connector similar to graphics cards).

- ↑ If processors for this socket integrate a Memory Controller, the number of independent channels times the maximum channel width in bits, including ECC lanes. Not all processors for this socket may support ECC.

- ↑ FSB = Front Side Bus (memory and I/O interfaces provided by the chipset), HTx = HyperTransport generation x link (I/O interfaces provided by the chipset), PCIex = Peripheral Component Interconnect Express generation x link. Note HT and PCIe links support bifurcation, e.g. 1x16 into 2x8 links. The table lists the maximum number of lanes and interfaces. Some processors may support fewer, and some motherboards may use alternative functions of these pins.

- ↑ This socket has graphics interfaces (DisplayPort, HDMI, VGA, etc.) to accommodate Accelerated Processing Units i.e. processors with integrated graphics. Not all processors for this socket may integrate a graphics processor.

- ↑ The number of dedicated I/O lanes to the Fusion Controller Hub a.k.a. chipset, equivalent to Intel's Platform Controller Hub. The FCH mainly serves as an I/O expander. A controller hub may be integrated on the processor, in this case the CPU package and socket has suitable I/O interfaces (USB, SATA, LPC, SMBus, etc.), sometimes in addition to the FCH interface.

- ↑ CPU package bottom view, not to scale.

Server Sockets[edit]

| Name | Year | Type | Contacts | CPU Family | Memory Controller |

I/O lanes | APU | SCH | Notes | Package |

|---|---|---|---|---|---|---|---|---|---|---|

| Socket 940 | 2003 | PGA | 940 | 0Fh | 144 bit DDR | 3× 16 HT1 | ✘ | - | Athlon 64 FX, Opteron |

|

| Socket F | 2006 | LGA | 1207 | NPT 0Fh | 2 × 72 bit DDR2 | 3× 16 HT1 | ✘ | - | Athlon 64 FX, Opteron 2xxx/8xxx (multi) |

|

| Socket Fr2 | 2007 | LGA | 1207 | NPT 0Fh, 10h | 2× 72 bit DDR2 | 3× 16 HT1 | ✘ | - |

| |

| Socket Fr5 | 2008 | LGA | 1207 | NPT 0Fh, 10h | 2× 72 bit DDR2 | 3× 16 HT1/3 | ✘ | - |

| |

| Socket Fr6 | 2009 | LGA | 1207 | 10h | 2× 72 bit DDR2 | 3× 16 HT3 | ✘ | - |

| |

| Socket C32 | 2010 | LGA | 1207 | 10h, 15h | 2× 72 bit DDR3 | 3× 16 HT3 | ✘ | - | Opteron 4xxx |

|

| Socket G34 | 2010 | LGA | 1944 | 10h, 15h | 4× 72 bit DDR3 | 3× 16 + 2× 8 HT3 | ✘ | - | Opteron 6xxx |

|

| Socket SP3 | 2017 | LGA | 4094 | 17h, 19h | 8× 72 bit DDR4 | 8× 16 PCIe 3/4 | ✘ | integrated | EPYC Naples Rome Milan |

|

| Socket SP5 | 2022 | LGA | 6096 | 19h, 1Ah | 12× 80 bit DDR5 | 8× 16 PCIe 5 | ✘ | integrated | EPYC 9004/9005 Genoa Turin |

|

| Socket SP6 | 2024 | LGA | 4844 | 19h | 6× 80 bit DDR5 | 6× 16 PCIe 5 | ✘ | integrated | EPYC 8004 Siena |

x50px |

| Socket SP7 | 2025 | LGA | - | 1Ah | 16× 80 bit DDR5 | 128× PCIe Gen 6 + 16× PCIe Gen 4 (2P) 96× PCIe Gen 6 + 8× PCIe Gen 4 (1P) |

✘ | integrated | EPYC 9006/9007 Venice Verano |

x50px |

| Socket SP8 | 2026 | LGA | - | 1Ah | 8× 80 bit DDR5 | 192× PCIe Gen 6 + 16× PCIe Gen 4 (2P) 128× PCIe Gen 6 + 8× PCIe Gen 4 (1P) |

✘ | integrated | EPYC 9006 Venice |

x50px |

Mobile Sockets (mainstream)[edit]

| Name | Year | Type | Pins | Fam. | MC | I/O lanes | APU | FCH | Notes | Package |

|---|---|---|---|---|---|---|---|---|---|---|

| Super Socket 7 | 1998 | PGA | 321 | 5 | - | FSB | ✘ | - |

| |

| Socket A | 2000 | PGA | 462 | 6 | - | FSB | ✘ | - |

| |

| Socket 563 | 2003 | PGA | 563 | 6 | - | FSB | ✘ | - |

| |

| Socket 754 | 2003 | PGA | 754 | 0Fh | 72 bit DDR | 16 HT1 | ✘ | - |

| |

| Socket S1g1 | 2006 | PGA | 638 | NPT 0Fh | 144 bit DDR2 | 16 HT1 | ✘ | - |

| |

| Socket S1g2 | 2008 | PGA | 638 | 11h | 2× 64 bit DDR2 | 16 HT3 | ✘ | - |

| |

| Socket S1g3 | 2009 | PGA | 638 | 10h | 2× 64 bit DDR2 | 16 HT3 | ✘ | - |

| |

| Package ASB1 | 2009 | BGA | 812 | NPT 0Fh | 144 bit DDR2 | 16 HT1 | ✘ | - |

| |

| Socket S1g4 | 2010 | PGA | 638 | 10h | 2× 64 bit DDR3 | 16 HT3 | ✘ | - |

| |

| Package ASB2 | 2010 | BGA | 812 | 10h | 2× 72 bit DDR3 | 16 HT3 | ✘ | - |

| |

| Socket FS1 | 2011 | PGA | 722 | 12h | 2× 64 bit DDR3 | 16 + 4 PCIe 2 | ✔ | 4 PCIe 2 |

| |

| Socket FS1r2 | 2012 | PGA | 722 | 15h | 2× 64 bit DDR3 | 16 + 4 PCIe 2 | ✔ | 4 PCIe 2 |

| |

| Package FP2 | 2012 | BGA | 827 | 15h | 2× 64 bit DDR3 | 16 + 4 PCIe 2 | ✔ | 4 PCIe 2 |

| |

| Package FP3 | 2014 | BGA | 854 | 15h | 2× 72 bit DDR3 | 16 + 8 PCIe 2/3 | ✔ | 4 PCIe 2 | ||

| Package FP4 | 2015 | BGA | 968 | 15h, 16h | 2× 72 bit DDR3/4 | 8 + 4 PCIe 3 | ✔ | integrated |

| |

| Package FP5 | 2018 | BGA | 1140 | 17h | 2× 72 bit DDR4 | 8 + 8 PCIe 3 | ✔ | integrated | Zen, Zen+ |

|

| Package FP6 | 2020 | BGA | 1140 | 17h, 19h | 2× 72 bit DDR4 4× 32 bit LPDDR4x |

8 + 12 PCIe 3 | ✔ | integrated | Zen 2, Zen 3 |

|

| Package FP7 Package FP7r2 |

2022 | BGA | 1140 | 19h | 4× DDR5-4800, 4× LPDDR5-6400 |

8 + 12 PCIe 4 | ✔ | integrated | Zen 3+ Rembrandt |

|

| Package FP8 | 2024 | BGA | - | 1Ah | 4× DDR5-4800, 4× LPDDR5-6400 |

16 PCIe 4 | ✔ | integrated | Zen 5 Strix Point |

x50px |

| Package FP10 | 2024 | BGA | 1384 | 1Ah | 4× DDR5-4800, 4× LPDDR5-6400 |

16 PCIe 4 | ✔ | integrated | Zen 6 Medusa Point |

x50px |

| Package FP11 | 2025 | BGA | 2077 | 1Ah | 4× DDR5-4800, 4× LPDDR5-6400 |

16 PCIe 4 | ✔ | integrated | Zen 5 Strix Halo |

x50px |

Mobile Sockets (ultrathin, tablet)[edit]

| Name | Year | Type | Pins | Famimy | MC | I/O lanes | APU | FCH | Notes | Package |

|---|---|---|---|---|---|---|---|---|---|---|

| Package FT1 | 2011 | BGA | 413 | 14h | 64 bit DDR3 | 4 PCIe 2 | ✔ | 4 PCIe 2 |

| |

| Package FT3 | 2013 | BGA | 769 | 16h | 72 bit DDR3 | 4 PCIe 2 | ✔ | 4 PCIe 2 |

| |

| Package FT3b | 2014 | BGA | 769 | 16h | 72 bit DDR3 | 4 PCIe 2 | ✔ | 4 PCIe 2 |

| |

| Package FT4 | 2016 | BGA | 769 | 15h | 64 bit DDR3/4 | 8 PCIe 3 | ✔ | integrated |

| |

| Package FT5 | 2020 | BGA | - | 17h | 2× DDR4, LPDDR4 | 8 PCIe 3 | ✔ | integrated | Zen | |

| Package FT6 | 2022 | BGA | - | 17h | 2× DDR5, LPDDR5 | 4 PCIe 3 | ✔ | integrated | Zen 2 | |

| Package FL1 | 2023 | BGA | 1763 | 19h, 1Ah | 2× DDR5, LPDDR5 | 4 PCIe 4 | ✔ | integrated | Zen 4/5 |

Embedded Sockets[edit]

| Name | Year | Type | Pins | Fam. | MC | I/O lanes | APU | FCH | Notes | Package |

|---|---|---|---|---|---|---|---|---|---|---|

| Package ASB1 | 2009 | BGA | 812 | NPT 0Fh | 144 bit DDR2 | 16 HT1 | ✘ | - |

| |

| Package ASB2 | 2010 | BGA | 812 | 10h | 2× 72 bit DDR3 | 16 HT3 | ✘ | - |

| |

| Package FT1 | 2011 | BGA | 413 | 14h | 64 bit DDR3 | 4 PCIe 2 | ✔ | 4 PCIe2 |

| |

| Package FP2 | 2012 | BGA | 827 | 15h | 2× 64 bit DDR3 | 16 + 4 PCIe 2 | ✔ | 4 PCIe2 |

| |

| Package FT3 | 2013 | BGA | 769 | 16h | 72 bit DDR3 | 4 PCIe 2 | ✔ | 4 PCIe2 |

| |

| Package FP3 | 2014 | BGA | 854 | 15h | 2× 72 bit DDR3 | 16 + 8 PCIe 2/3 | ✔ | 4 PCIe2 | ||

| Package SP1 | 2014 | BGA | 1021 | 2× 72 bit DDR3/4 | 8 PCIe 3 | ✘ | integrated | |||

| Package FT3b | 2014 | BGA | 769 | 16h | 72 bit DDR3 | 4 PCIe 2 | ✔ | 4 PCIe2 |

| |

| Package FP4 | 2015 | BGA | 968 | 15h, 16h | 2× 72 bit DDR3/4 | 8 + 4 PCIe 3 | ✔ | integrated |

| |

| Package FP5 | 2018 | BGA | 1140 | 17h | 2× 72 bit DDR4 | 8 + 8 PCIe 3 | ✔ | integrated |

| |

| Socket SP3 | 2017 | LGA | 4094 | 17h | 8× 72 bit DDR4 | 8× 16 PCIe 3 | ✘ | integrated | [1] |

|

| Package SP4 | 2018 | BGA | 2028 | 17h | 4× 72 bit DDR4 | 4× 16 PCIe 3 | ✘ | integrated | x50px | |

| Package SP4r2 | 2018 | BGA | 2028 | 17h | 2× 72 bit DDR4 | 2× 16 PCIe 3 | ✘ | integrated | x50px | |

| Package FP6 | 2020 | BGA | 1140 | 17h | 2× 72 bit DDR4 4× 32 bit LPDDR4x |

8 + 12 PCIe 3 | ✔ | integrated |

|

- ↑ Embedded versions of EPYC 7001 & 7002 processors, hence Family 17h only.

Game Consoles[edit]

| Name | Year | Type | Pins | Family | MC | I/O | APU | FCH | Notes |

|---|---|---|---|---|---|---|---|---|---|

| Xbox One X BGA-2409 |

2017 | BGA | 2409 | 16h | 12× 32 bit GDDR5 | 8 PCIe 3 | ✔ |

| |

| Xbox Series X/S BGA-2963 |

2020 | BGA | 2963 | 17h | 20× 16 bit GDDR6 | 8 PCIe 4 | ✔ | Arden ES | Lidless package with stiffener frame, 52.5 × 52.5 mm, 0.8+ mm multi-pitch[1][2] |

- Microsoft XBOX Series X • ADN-A0 (Arden A0), XBX/BGA-2963, ADN-A0, Arden ES, 8C/16T, 8 MB, 3.60/3.80 GHz • MS XBOX

- Microsoft XBOX Series S • ADN-A0 (Arden A0), XBS/BGA-2963, ADN-A0, Arden ES, 8C/16T, 8 MB, 3.40/3.60 GHz • MS XBOX

- Sony Playstation 5 • ARL-A0 (Ariel A0), PS5/BGA ??, ARL-A0, Ariel ES/Oberon, 8C/16T, 32 MB, 1.60/3.20 GHz • Sony PS5

- ↑ Paternoster, Paul et al. XBOX SERIES X SoC – A Next Generation Gaming Console (Presentation, Slides). IEEE ISSCC 2021, 3.1. February 15, 2021

- ↑ Paternoster, Paul et al. (2021). XBOX Series X: A Next-Generation Gaming Console SoC. Proceedings of IEEE ISSCC 2021. pp. 46-48. doi:10.1109/ISSCC42613.2021.9366057

AMD CPU Packages[edit]

| AMD CPU Packages | |||||||

|---|---|---|---|---|---|---|---|

| General | Details | ||||||

| Name | Package | Contacts | TDP | Socket | µarch | Market | Release |

| ASB1 | ASB1 | 812 | 18 W 18,000 mW 0.0241 hp 0.018 kW | K8 | Mobile | 8 January 2009 | |

| ASB2 | ASB2 | 812 | 15 W 15,000 mW 0.0201 hp 0.015 kW | K10 | Mobile | 12 May 2010 | |

| FT1 | FT1, UOB413 | 413 | 18 W 18,000 mW 0.0241 hp 0.018 kW | Bobcat | Mobile, Embedded | 4 January 2011 | |

| FT3 | BGA-769 | 769 | 25 W 25,000 mW 0.0335 hp 0.025 kW | Jaguar | Mobile, Embedded | May 2013 | |

| FT3b | BGA-769 | 769 | 25 W 25,000 mW 0.0335 hp 0.025 kW | Puma | Mobile, Embedded | 4 June 2014 | |

| FT4 | BGA-769 | 769 | 15 W 15,000 mW 0.0201 hp 0.015 kW | Excavator | Mobile | June 2016 | |

| Package CBGA-360 | CBGA-360 | 360 | 11 W 11,000 mW 0.0148 hp 0.011 kW | K6 | Mobile | 5 March 1998 | |

| Package FP2 | BGA-827, FP2 | 827 | 25 W 25,000 mW 0.0335 hp 0.025 kW | Piledriver | Mobile, Embedded | 15 May 2012 | |

| Package FP3 | BGA-854, FP3 | 854 | 35 W 35,000 mW 0.0469 hp 0.035 kW | Steamroller | Mobile, Embedded | June 2014 | |

| Package FP4 | BGA-968, FP4 | 968 | 45 W 45,000 mW 0.0603 hp 0.045 kW | Excavator | Mobile, Embedded | June 2015 | |

| Package FP5 | BGA-1140 | 1,140 | 45 W 45,000 mW 0.0603 hp 0.045 kW | Zen, Zen+ | Mobile, Embedded | 8 January 2018 | |

| Package FP6 | BGA-1140 | 1,140 | 55 W 55,000 mW 0.0738 hp 0.055 kW | Zen 2, Zen 3 | Mobile, Embedded | 16 March 2020 | |

| Package OBGA-349 | OBGA-349 | 349 | 18 W 18,000 mW 0.0241 hp 0.018 kW | K6 | Embedded | 25 September 2000 | |

| Package SP1 | BGA-1021 | 1,021 | 32 W 32,000 mW 0.0429 hp 0.032 kW | Cortex-A57 | Embedded, Server | January 2016 | |

| Package SP4 | BGA-2028 | 2,028 | 100 W 100,000 mW 0.134 hp 0.1 kW | Zen | Embedded | 21 February 2018 | |

| Package SP4r2 | BGA-2028 | 2,028 | 55 W 55,000 mW 0.0738 hp 0.055 kW | Zen | Embedded | 21 February 2018 | |

| Socket 563 | OPGA-563, UOG 563 | 563 | 35 W 35,000 mW 0.0469 hp 0.035 kW | Socket 563 | K7 | Mobile | March 2003 |

| Socket 754 | OPGA-754 | 754 | 89 W 89,000 mW 0.119 hp 0.089 kW | Socket 754 | K8 | Desktop | 23 September 2003 |

| Socket 939 | OPGA-939 | 939 | 110 W 110,000 mW 0.148 hp 0.11 kW | Socket 939 | K8 | Desktop | 1 June 2004 |

| Socket 940 | CPGA-940 | 940 | 110 W 110,000 mW 0.148 hp 0.11 kW | Socket 940 | K8 | Server | 22 April 2003 |

| Socket AM1 | OPGA-721 | 721 | 25 W 25,000 mW 0.0335 hp 0.025 kW | Socket AM1 | Jaguar | Desktop | 9 April 2014 |

| Socket AM2 | OPGA-940 AM2 | 940 | 125 W 125,000 mW 0.168 hp 0.125 kW | Socket AM2 | K8 | Desktop | 23 May 2006 |

| Socket AM2+ | OPGA-940 (AM2) | 940 | 140 W 140,000 mW 0.188 hp 0.14 kW | Socket AM2+ | K10 | Desktop | 19 November 2007 |

| Socket AM3 | OPGA-938 | 938 | 125 W 125,000 mW 0.168 hp 0.125 kW | Socket AM3 | K10 | Desktop | 9 February 2009 |

| Socket AM3+ | OPGA-940 (AM3) | 940 | 220 W 220,000 mW 0.295 hp 0.22 kW | Socket AM3+ | Bulldozer | Desktop | 20 March 2012 |

| Socket AM4 | OPGA-1331 | 1,331 | 105 W 105,000 mW 0.141 hp 0.105 kW | Socket AM4 | Zen | Desktop | September 2016 |

| Socket AM5 | LGA-1718 | 1,718 | 170 W 170,000 mW 0.228 hp 0.17 kW | Socket AM5 | Zen 4 | Desktop | 18 April 2022 |

| Socket C32 | LGA-1207 | 1,207 | 95 W 95,000 mW 0.127 hp 0.095 kW | Socket C32 | K10, Bulldozer, Piledriver | Server | 23 June 2010 |

| Socket F | LGA-1207 | 1,207 | 137 W 137,000 mW 0.184 hp 0.137 kW | Socket F | K8, K10 | Server | 15 August 2006 |

| Socket FM1 | OPGA-905 | 905 | 100 W 100,000 mW 0.134 hp 0.1 kW | Socket FM1 | K10 | Desktop | 30 June 2011 |

| Socket FM2 | OPGA-904 | 904 | 100 W 100,000 mW 0.134 hp 0.1 kW | Socket FM2 | Piledriver | Desktop | 1 October 2012 |

| Socket FM2+ | OPGA-906 | 906 | 95 W 95,000 mW 0.127 hp 0.095 kW | Socket FM2+ | Steamroller, Excavator | Desktop | 31 July 2014 |

| Socket FS1 | OPGA-722 | 722 | 45 W 45,000 mW 0.0603 hp 0.045 kW | Socket FS1 | K10 | Mobile | 14 June 2011 |

| Socket FS1r2 | OPGA-722 | 722 | 35 W 35,000 mW 0.0469 hp 0.035 kW | Socket FS1r2 | Piledriver | Mobile | 15 May 2012 |

| Socket G34 | LGA-1944 | 1,944 | 140 W 140,000 mW 0.188 hp 0.14 kW | Socket G34 | K10, Bulldozer, Piledriver | Server | 29 March 2010 |

| Socket S1g1 | OPGA-638 | 638 | 35 W 35,000 mW 0.0469 hp 0.035 kW | Socket S1g1 | K8 | Mobile | 17 May 2006 |

| Socket S1g2 | OPGA-638 | 638 | 35 W 35,000 mW 0.0469 hp 0.035 kW | Socket S1g2 | Mobile | 4 June 2008 | |

| Socket S1g3 | OPGA-638 | 638 | 35 W 35,000 mW 0.0469 hp 0.035 kW | Socket S1g3 | K10 | Mobile | 10 September 2009 |

| Socket S1g4 | OPGA-638 | 638 | 45 W 45,000 mW 0.0603 hp 0.045 kW | Socket S1g4 | K10 | Mobile | 12 May 2010 |

| Socket SP3 | SP3, FCLGA-4094 | 4,094 | 120 W 120,000 mW , 155 W0.161 hp 0.12 kW 155,000 mW , 180 W0.208 hp 0.155 kW 180,000 mW 0.241 hp 0.18 kW | SP3, LGA-4094 | Zen, Zen 2, Zen 3 | Server | 20 June 2017 |

| Socket SP5 | SP5, FCLGA-6096 | 6,096 | 400 W 400,000 mW 0.536 hp 0.4 kW | Socket SP5 | Zen 4 | Server | 10 November 2022 |

| Socket TR4 | TR4, FCLGA-4094 | 4,094 | 180 W 180,000 mW , 250 W0.241 hp 0.18 kW 250,000 mW 0.335 hp 0.25 kW | TR4, SP3r2, sTR4 | Zen, Zen+ | Desktop, Workstation | 10 August 2017 |

| Socket sTRX4 | sTRX4, FCLGA-4094 | 4,094 | 280 W 280,000 mW 0.375 hp 0.28 kW | sTRX4 | Zen 2 | HEDT | 25 November 2019 |

| Socket sWRX8 | sWRX8, FCLGA-4094 | 4,094 | 280 W 280,000 mW 0.375 hp 0.28 kW | sWRX8 | Zen 2, Zen 3 | Workstation | 14 July 2020 |

| Super Socket 7 | CPGA-321 | 321 | 30 W 30,000 mW 0.0402 hp 0.03 kW | Super Socket 7 | K6 | Desktop | May 1998 |

AMD CPU sockets[edit]

Packages to Scale[edit]

SP4/SP4r2 XBox Series X/S