| Edit Values | |

| Socket S1g4 | |

| General Info | |

| Designer | AMD |

| Introduction | May 12, 2010 (launched) |

| Market | Mobile |

| Microarchitecture | K10 |

| TDP | 45 W 45,000 mW 0.0603 hp 0.045 kW |

| Package | |

| Name | OPGA-638 |

| Type | Organic Micro Pin Grid Array |

| Contacts | 638 |

| Dimension | 35.0 mm 3.5 cm × 35.0 mm1.378 in 3.5 cm 1.378 in |

| Pitch | 1.27 mm 0.05 in |

| Socket | |

| Name | Socket S1g4 |

| Type | PGA |

Socket S1g4 was the fourth and last socket for OPGA-638-packaged AMD mobile microprocessors with an integrated DDR2 and DDR3 memory controller, and the successor to Socket S1g3. Its counterparts for desktop processors are Socket AM3 and Socket AM3+, for servers Socket C32 and Socket G34. For the small form factor desktop, mobile and embedded market AMD developed package ASB2. Socket S1g4 was superseded by Socket FS1 supporting mobile processors with integrated graphics.

The main improvement of Socket S1g4 over S1g3 is support for DDR3 memory. As the number of CPU cores in the package grew to three and four, voltage regulators were integrated on the chip and support for two core power planes was dropped.

Socket S1g4 was used in AMD's "Danube" mobile platform. All processors for Socket S1g4, codename "Champlain", are members of AMD's Family 10h with CPU cores based on the K10 microarchitecture and were fabricated on a 45 nm SOI process.

All revisions of Socket S1 have the same dimensions, however processors for Socket S1g4 appear to be electrically incompatible with Socket S1g1 and vice versa. Processors for Socket S1g2 have a DDR2 memory controller and will not work in Socket S1g4. To which extent Socket S1g4 processors are compatible with Socket S1g2 and S1g3, in DDR2 mode and with a suitable BIOS, is unclear.

Contents

Features[edit]

- 638-pin lidless micro pin grid array package, 1.27 mm pitch, 26 × 26 pins, 35 × 35 mm, organic substrate, C4 (flip chip) die attachment

- 16 bit HyperTransport 3.0 interface up to 1800 MHz, 3600 MT/s, 7.2 GB/s in each direction

- 2 × 64 bit DDR2 SDRAM interface up to 400 MHz, PC2-6400 (DDR2-800), 12.8 GB/s or

- 2 × 64 bit DDR3 SDRAM interface up to 667 MHz, PC3-10600 (DDR3-1333), 21.3 GB/s

- Up to 2 SODIMMs, no ECC support

- DDR2 JEDEC SSTL_1.8, DDR3 JEDEC 1.5V, 1.35V

- Power Management

- AMD PowerNow! technology

- ACPI C1, C1E, C2, C3, C5/Altvid, S1, S3, S4, S5

- Separate core and northbridge power planes

- Two northbrige P-states

- Thermal Controls

- Thermal protection

- Hardware thermal control

- Thermal diode

Chipsets[edit]

- AMD 880M

- AMD SB820 southbridge

Processors using Socket S1g4[edit]

- AMD Phenom II Quad-Core Mobile

- AMD Phenom II Triple-Core Mobile

- AMD Phenom II Dual-Core Mobile

- AMD Turion II Dual-Core Mobile

- AMD Athlon II Dual-Core Mobile

- AMD V-Series

| List of all Socket S1g4-based Processors | |||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Model | Price | Process | Launched | µarch | Family | Core | C | T | Freq | Turbo | TDP | ||||||||

| Count: 0 | |||||||||||||||||||

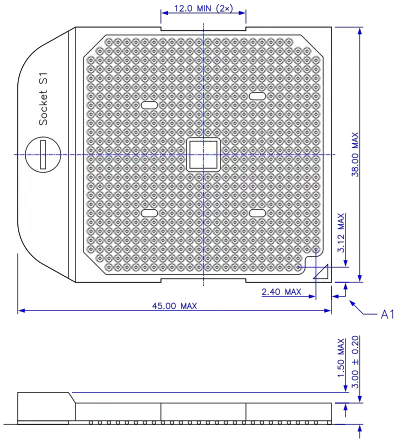

Package Diagram[edit]

No data available. Dimensions should be similar to those of the OPGA-638 package shown on the Socket S1g1 page.

Socket Outline[edit]

Socket S1 limits as specified in AMD Publ. #31839. Depicted is Foxconn Interconnect Technology Part No. PZ6382A-284S-01F. All dimensions in millimeters.

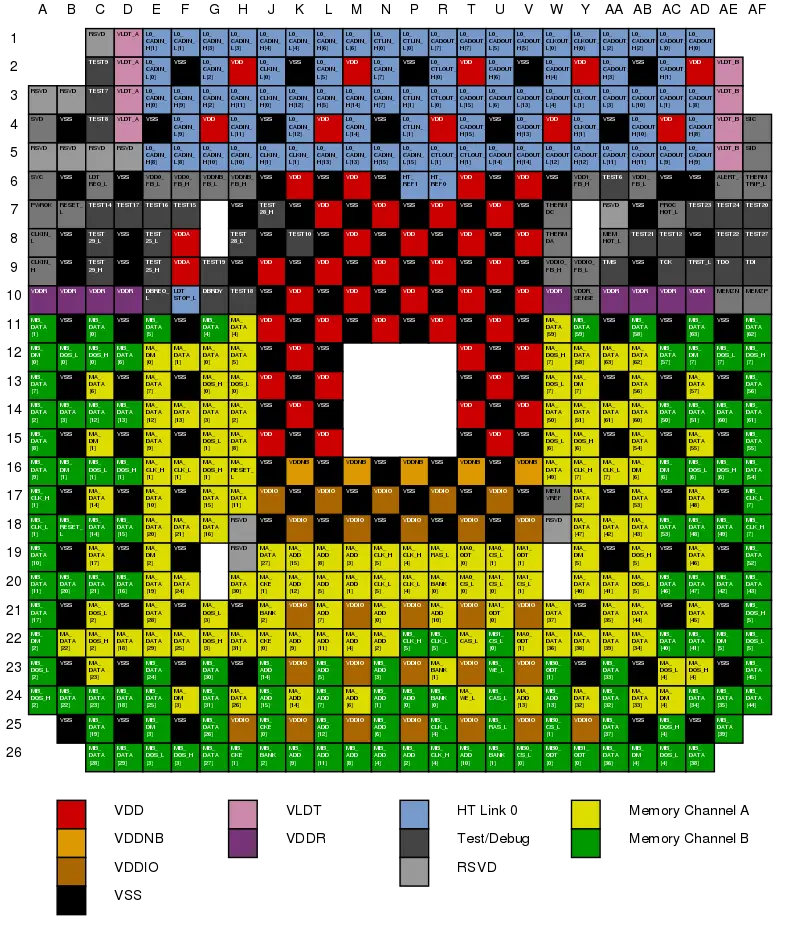

Pin Map[edit]

Differences between Socket S1 revisions[edit]

| Pin | S1g1 | S1g2/S1g3 | S1g4 | Description |

|---|---|---|---|---|

| R21 | MA_ADD[0] | MA_ADD[10] | MA_ADD[10] | DRAM Column/Row Address |

| N21 | MA_ADD[1] | MA_ADD[0] | MA_ADD[0] | |

| M22 | MA_ADD[3] | MA_ADD[4] | MA_ADD[4] | |

| M24 | MA_ADD[4] | MA_ADD[6] | MA_ADD[6] | |

| M20 | MA_ADD[5] | MA_ADD[1] | MA_ADD[1] | |

| M19 | MA_ADD[6] | MA_ADD[3] | MA_ADD[3] | |

| L22 | MA_ADD[8] | MA_ADD[11] | MA_ADD[11] | |

| L19 | MA_ADD[9] | MA_ADD[8] | MA_ADD[8] | |

| R19 | MA_ADD[10] | MA_RAS_L | MA_RAS_L | |

| L20 | MA_ADD[11] | MA_ADD[5] | MA_ADD[5] | |

| K24 | MA_ADD[12] | MA_ADD[14] | MA_ADD[14] | |

| K20 | MA_ADD[14] | MA_ADD[12] | MA_ADD[12] | |

| T22 | MA_BANK[0] | MA_CAS_L | MA_CAS_L | DRAM Bank Address / Column Address Strobe |

| R20 | MA_BANK[1] | MA_BANK[0] | MA_BANK[0] | |

| R23 | RSVD | MA_BANK[1] | MA_BANK[1] | |

| K22 | MA_BANK[2] | MA_ADD[9] | MA_ADD[9] | |

| U20 | MA_CAS_L | MA1_CS_L[0] | MA1_CS_L[0] | DRAM Column Address Strobe / Chip Select |

| J21 | MA_CKE[0] | MA_BANK[2] | MA_BANK[2] | DRAM Clock Enable / Bank Address |

| T20 | MA_RAS_L | MA0_CS_L[0] | MA0_CS_L[0] | DRAM Row Address Strobe / Chip Select |

| U21 | MA_WE_L | MA1_ODT[0] | MA1_ODT[0] | DRAM Write Enable / Enable Pin for On Die Termination |

| E16 | MA0_CLK_H[1] | MA_CLK_H[1] | MA_CLK_H[1] | DRAM Differential Clock |

| F16 | MA0_CLK_L[1] | MA_CLK_L[1] | MA_CLK_L[1] | |

| P19 | RSVD | MA_CLK_H[4] | MA_CLK_H[4] | |

| P20 | RSVD | MA_CLK_L[4] | MA_CLK_L[4] | |

| N19 | RSVD | MA_CLK_H[5] | MA_CLK_H[5] | |

| N20 | RSVD | MA_CLK_L[5] | MA_CLK_L[5] | |

| Y16 | MA0_CLK_H[2] | MA_CLK_H[7] | MA_CLK_H[7] | |

| AA16 | MA0_CLK_L[2] | MA_CLK_L[7] | MA_CLK_L[7] | |

| T19 | MA0_CS_L[0] | MA0_ODT[0] | MA0_ODT[0] | |

| V22 | MA0_CS_L[1] | MA0_ODT[1] | MA0_ODT[1] | |

| J22 | MA0_CS_L[2] | MA_CKE[0] | MA_CKE[0] | |

| V19 | MA0_CS_L[3] | MA1_ODT[1] | MA1_ODT[1] | |

| U19 | MA0_ODT[0] | MA0_CS_L[1] | MA0_CS_L[1] | |

| V20 | MA0_ODT[1] | MA1_CS_L[1] | MA1_CS_L[1] | |

| H16 | RSVD | RSVD_M1 | MA_RESET_L | DRAM Reset Pin for Suspend-to-RAM Power Management Mode |

| T24 | MB_ADD[0] | MA_WE_L | MA_WE_L | |

| P26 | MB_ADD[1] | MB_ADD[2] | MB_ADD[2] | |

| P24 | MB_ADD[2] | MB_ADD[0] | MB_ADD[0] | |

| N26 | MB_ADD[3] | MB_ADD[4] | MB_ADD[4] | |

| N25 | MB_ADD[4] | MB_ADD[6] | MB_ADD[6] | |

| N24 | MB_ADD[5] | MB_ADD[1] | MB_ADD[1] | |

| N23 | MB_ADD[6] | MB_ADD[3] | MB_ADD[3] | |

| L26 | MB_ADD[7] | MB_ADD[11] | MB_ADD[11] | |

| L24 | MB_ADD[9] | MB_ADD[7] | MB_ADD[7] | |

| U25 | MB_ADD[10] | MB_RAS_L | MB_RAS_L | |

| L25 | MB_ADD[11] | MB_ADD[12] | MB_ADD[12] | |

| L23 | MB_ADD[12] | MB_ADD[5] | MB_ADD[5] | |

| W25 | MB_ADD[13] | MB0_CS_L[1] | MB0_CS_L[1] | |

| J26 | MB_ADD[14] | MB_BANK[2] | MB_BANK[2] | |

| J25 | MB_ADD[15] | MB_CKE[0] | MB_CKE[0] | |

| R24 | RSVD | MB_BANK[0] | MB_BANK[0] | |

| U26 | MB_BANK[0] | MB_BANK[1] | MB_BANK[1] | |

| T26 | MB_BANK[1] | MB_ADD[10] | MB_ADD[10] | |

| K26 | MB_BANK[2] | MB_ADD[9] | MB_ADD[9] | |

| V26 | MB_CAS_L | MB0_CS_L[0] | MB0_CS_L[0] | |

| J23 | MB_CKE[0] | MB_ADD[14] | MB_ADD[14] | |

| U24 | MB_RAS_L | MB_CAS_L | MB_CAS_L | |

| U22 | MB_WE_L | MB1_CS_L[0] | MB1_CS_L[0] | |

| A17 | MB0_CLK_H[1] | MB_CLK_H[1] | MB_CLK_H[1] | |

| A18 | MB0_CLK_L[1] | MB_CLK_L[1] | MB_CLK_L[1] | |

| R26 | RSVD | MB_CLK_H[4] | MB_CLK_H[4] | |

| R25 | RSVD | MB_CLK_L[4] | MB_CLK_L[4] | |

| P22 | RSVD | MB_CLK_H[5] | MB_CLK_H[5] | |

| R22 | RSVD | MB_CLK_L[5] | MB_CLK_L[5] | |

| AF18 | MB0_CLK_H[2] | MB_CLK_H[7] | MB_CLK_H[7] | |

| AF17 | MB0_CLK_L[2] | MB_CLK_L[7] | MB_CLK_L[7] | |

| U23 | MB0_CS_L[0] | MB_WE_L | MB_WE_L | |

| W24 | MB0_CS_L[1] | MB_ADD[13] | MB_ADD[13] | |

| J24 | MB0_CS_L[2] | MB_ADD[15] | MB_ADD[15] | |

| Y26 | MB0_CS_L[3] | MB1_ODT[0] | MB1_ODT[0] | |

| B18 | RSVD | RSVD_M2 | MB_RESET_L | |

| AA8 | RSVD | MEMHOT_L | MEMHOT_L | DRAM Thermal Protection input |

| A3 | PSI_L | RSVD | RSVD | Power Status Indicator (low power mode) for VDD regulator |

| W8 | TEST4 | THERMDA | THERMDA | Thermal Diode, Anode |

| W7 | TEST5 | THERMDC | THERMDC | Thermal Diode, Cathode |

| AA7 | TEST13 | RSVD | RSVD | |

| AE6 | TEST26 | ALERT_L | ALERT_L | Programmable pin that can indicate different events, including a SB-TSI interrupt |

| M11 | VSS | KEY1 | VSS | |

| W18 | RSVD | KEY2 | RSVD | |

| misc. | VDD | VDD0 | VDD | Core power supply |

| F6 | VDD_FB_H | VDD0_FB_H | VDD0_FB_H | Differential feedback to VDD0 regulator |

| E6 | VDD_FB_L | VDD0_FB_L | VDD0_FB_L | |

| misc. | VDD | VDD1 | VDD | |

| Y6 | TEST3 | VDD1_FB_H | VDD1_FB_H | Differential feedback to VDD1 regulator |

| AB6 | TEST2 | VDD1_FB_L | VDD1_FB_L | |

| misc. | VDD | VDDNB | VDDNB | Northbridge power supply |

| H6 | RSVD | VDDNB_FB_H | VDDNB_FB_H | Differential feedback to VDDNB regulator |

| G6 | RSVD | VDDNB_FB_L | VDDNB_FB_L | |

| B5 | VID[0] | RSVD | RSVD | Voltage ID for VDD regulator |

| C5 | VID[1] | RSVD | RSVD | |

| A4 | VID[2] | SVD | SVD | Serial Voltage ID Interface, Data |

| A6 | VID[3] | SVC | SVC | Serial Voltage ID Interface, Clock |

| C6 | VID[4] | LDTREQ_L | LDTREQ_L | HT link is active or requested by a device (HT Gen 3.0) |

| A5 | VID[5] | RSVD | RSVD | |

| misc. | VTT | VTT | VDDR | |

| Y10 | VTT_SENSE | VTT_SENSE | VDDR_SENSE | VTT / VDDR monitor pin |

References[edit]

- "Low-Profile Socket S1 Design Specification", AMD Publ. #31839, Rev. 3.01, April 10, 2007

- "BIOS and Kernel Developer’s Guide (BKDG) For AMD Family 10h Processors", AMD Publ. #31116, Rev. 3.62, January 14, 2013

- "Revision Guide for AMD Family 10h Processors", AMD Publ. #41322, Rev. 3.92, March 2012

- "AMD RS880M Databook Device Specification for the RS880M and RS880MC", AMD Publ. #46113, Rev. 1.30, 2010

See also[edit]

| designer | AMD + |

| first launched | May 12, 2010 + |

| instance of | package + |

| market segment | Mobile + |

| microarchitecture | K10 + |

| name | Socket S1g4 + |

| package | OPGA-638 + |

| package contacts | 638 + |

| package length | 35 mm (3.5 cm, 1.378 in) + |

| package pitch | 1.27 mm (0.05 in) + |

| package type | Organic Micro Pin Grid Array + |

| package width | 35 mm (3.5 cm, 1.378 in) + |

| socket | Socket S1g4 + |

| tdp | 45 W (45,000 mW, 0.0603 hp, 0.045 kW) + |