From WikiChip

Difference between revisions of "20 nm lithography process"

(→Industry: typo) |

m (Bot: Automated text replacement (-Category:Lithography +category:lithography)) |

||

| (8 intermediate revisions by 4 users not shown) | |||

| Line 3: | Line 3: | ||

== Industry == | == Industry == | ||

| − | {{ | + | {{nodes comp |

| − | | | + | <!-- TSMC --> |

| − | | | + | | process 1 fab = [[TSMC]] |

| − | | | + | | process 1 name = |

| − | | | + | | process 1 date = 3Q 2014 |

| − | | | + | | process 1 lith = 193 nm |

| − | | | + | | process 1 immersion = Yes |

| − | | | + | | process 1 exposure = |

| + | | process 1 wafer type = Bulk | ||

| + | | process 1 wafer size = 300 mm | ||

| + | | process 1 transistor = Planar | ||

| + | | process 1 volt = 0.95 V | ||

| + | | process 1 layers = 10 | ||

| + | | process 1 delta from = [[28 nm]] Δ | ||

| + | | process 1 gate len = | ||

| + | | process 1 gate len Δ = | ||

| + | | process 1 cpp = 90 nm | ||

| + | | process 1 cpp Δ = 0.77x | ||

| + | | process 1 mmp = 64 nm | ||

| + | | process 1 mmp Δ = 0.67x | ||

| + | | process 1 sram hp = | ||

| + | | process 1 sram hp Δ = | ||

| + | | process 1 sram hd = 0.081 µm² | ||

| + | | process 1 sram hd Δ = 0.64x | ||

| + | | process 1 sram lv = | ||

| + | | process 1 sram lv Δ = | ||

| + | | process 1 dram = | ||

| + | | process 1 dram Δ = | ||

| + | <!-- IBM --> | ||

| + | | process 2 fab = [[Common Platform Alliance]] <info>The '''Common Platform Alliance''' 20 nm node was a collaboration between [[IBM]], [[Samsung]], [[GlobalFoundries]], [[Toshiba]], [[STMicroelectronics]]</info> | ||

| + | | process 2 name = | ||

| + | | process 2 date = 2014 | ||

| + | | process 2 lith = 193 nm | ||

| + | | process 2 immersion = Yes | ||

| + | | process 2 exposure = | ||

| + | | process 2 wafer type = Bulk | ||

| + | | process 2 wafer size = 300 mm | ||

| + | | process 2 transistor = Planar | ||

| + | | process 2 volt = 0.9 V | ||

| + | | process 2 layers = | ||

| + | | process 2 delta from = [[28 nm]] Δ | ||

| + | | process 2 gate len = 20 nm | ||

| + | | process 2 gate len Δ = 0.67x | ||

| + | | process 2 cpp = 86 nm | ||

| + | | process 2 cpp Δ = 0.76 | ||

| + | | process 2 mmp = 64 nm | ||

| + | | process 2 mmp Δ = 0.71x | ||

| + | | process 2 sram hp = 0.102 µm² | ||

| + | | process 2 sram hp Δ = | ||

| + | | process 2 sram hd = 0.081 µm² | ||

| + | | process 2 sram hd Δ = 0.68x | ||

| + | | process 2 sram lv = | ||

| + | | process 2 sram lv Δ = | ||

| + | | process 2 dram = | ||

| + | | process 2 dram Δ = | ||

}} | }} | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

=== TSMC === | === TSMC === | ||

| Line 50: | Line 79: | ||

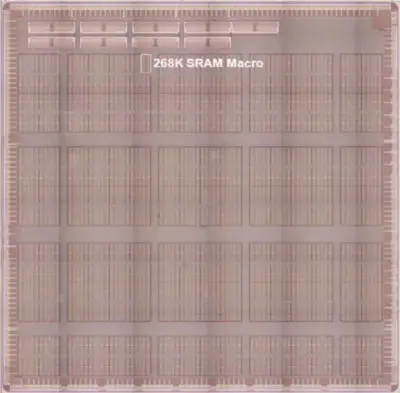

| [[File:tsmc 20nm SRAM block.png|400px]] | | [[File:tsmc 20nm SRAM block.png|400px]] | ||

|} | |} | ||

| − | |||

| − | |||

| − | |||

== 20 nm Microprocessors== | == 20 nm Microprocessors== | ||

* MediaTek | * MediaTek | ||

** {{mediatek|Helio}} | ** {{mediatek|Helio}} | ||

| + | * Fujitsu | ||

| + | ** {{fujitsu|SPARC64}} | ||

| + | * Oracle | ||

| + | ** {{oracle|SPARC M8}} | ||

{{expand list}} | {{expand list}} | ||

| Line 64: | Line 94: | ||

== References == | == References == | ||

* Chang, Jonathan, et al. "A 20nm 112Mb SRAM in High-к metal-gate with assist circuitry for low-leakage and low-V MIN applications." Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2013 IEEE International. IEEE, 2013. | * Chang, Jonathan, et al. "A 20nm 112Mb SRAM in High-к metal-gate with assist circuitry for low-leakage and low-V MIN applications." Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2013 IEEE International. IEEE, 2013. | ||

| + | * Shang, Huiling, et al. "High performance bulk planar 20nm CMOS technology for low power mobile applications." VLSI Technology (VLSIT), 2012 Symposium on. IEEE, 2012. | ||

| − | [[ | + | [[category:lithography]] |

Latest revision as of 22:04, 20 May 2018

The 20 nanometer (20 nm) lithography process is a half-node semiconductor manufacturing process used as a stopgap between the 22 nm and 16 nm processes. The term "20 nm" is simply a commercial name for a generation of a certain size and its technology, as opposed to gate length or half pitch. Commercial integrated circuit manufacturing using 20 nm process began in 2014. This technology superseded by commercial 16 nm process.

Industry[edit]

| Process Name | |

|---|---|

| 1st Production | |

| Litho- graphy |

Lithography |

| Immersion | |

| Exposure | |

| Wafer | Type |

| Size | |

| Tran- sistor |

Type |

| Voltage | |

| Metal Layers | |

| Gate Length (Lg) | |

| Contacted Gate Pitch (CPP) | |

| Minimum Metal Pitch (MMP) | |

| SRAM bitcell |

High-Perf (HP) |

| High-Density (HD) | |

| Low-Voltage (LV) | |

| DRAM bitcell |

eDRAM |

| TSMC | Common Platform Alliance The Common Platform Alliance 20 nm node was a collaboration between IBM, Samsung, GlobalFoundries, Toshiba, STMicroelectronics

| ||

|---|---|---|---|

| 3Q 2014 | 2014 | ||

| 193 nm | 193 nm | ||

| Yes | Yes | ||

| Bulk | Bulk | ||

| 300 mm | 300 mm | ||

| Planar | Planar | ||

| 0.95 V | 0.9 V | ||

| 10 | |||

| Value | 28 nm Δ | Value | 28 nm Δ |

| 20 nm | 0.67x | ||

| 90 nm | 0.77x | 86 nm | 0.76 |

| 64 nm | 0.67x | 64 nm | 0.71x |

| 0.102 µm² | |||

| 0.081 µm² | 0.64x | 0.081 µm² | 0.68x |

TSMC[edit]

TSMC demonstrated their 112 Mebibit SRAM wafer from their 20 nm HKMG process at the 2013 IEEE ISSCC.

20 nm Microprocessors[edit]

This list is incomplete; you can help by expanding it.

20 nm Microarchitectures[edit]

This list is incomplete; you can help by expanding it.

References[edit]

- Chang, Jonathan, et al. "A 20nm 112Mb SRAM in High-к metal-gate with assist circuitry for low-leakage and low-V MIN applications." Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2013 IEEE International. IEEE, 2013.

- Shang, Huiling, et al. "High performance bulk planar 20nm CMOS technology for low power mobile applications." VLSI Technology (VLSIT), 2012 Symposium on. IEEE, 2012.

Semiconductor lithography processes technology

Semiconductor lithography processes technology