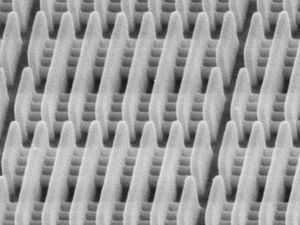

The 16 nanometer (16 nm) lithography process is a full node semiconductor manufacturing process following the 20 nm process stopgap. Commercial integrated circuit manufacturing using 16 nm process began in 2014. The term "16 nm" is simply a commercial name for a generation of a certain size and its technology, as opposed to gate length or half pitch. This technology is set to be replaced with 10 nm process in 2017.

Industry

An enhanced version of TSMC's 16nm process was introduced in late 2016 called "12nm".

| Process Name | |

|---|---|

| 1st Production | |

| Lithography | Lithography |

| Immersion | |

| Exposure | |

| Wafer | Type |

| Size | |

| Transistor | Type |

| Voltage | |

| Fin | Pitch |

| Width | |

| Height | |

| Gate Length (Lg) | |

| Contacted Gate Pitch (CPP) | |

| Minimum Metal Pitch (MMP) | |

| SRAM bitcell | High-Perf (HP) |

| High-Density (HD) | |

| Low-Voltage (LV) | |

| DRAM bitcell | eDRAM |

| TSMC | |

|---|---|

| 16FF 16nm FinFET , 16FF+16nm FinFET Plus , 16FFC, 12FFC12nm FinFET Compact , 12FFN

| |

| 3Q 2015 | |

| 193 nm | |

| Yes | |

| Bulk | |

| 300 mm | |

| FinFET | |

| 0.75 V | |

| Value | 20 nm Δ |

| 48 nm | N/A |

| 37 nm | |

| 34 nm | |

| 90 nm | 1x |

| 64 nm | 1x |

| 0.074 µm² | 0.86x |

TSMC

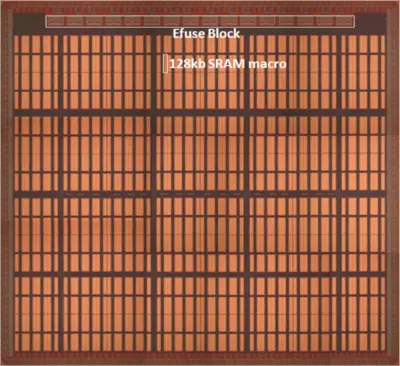

TSMC uses the same BEOL as its 20nm process. They named their process 16 nm which reflects those relaxed pitches. TSMC demonstrated their 128 Mebibit SRAM wafer from their 16 nm HKMG FinFET process at the 2014 IEEE ISSCC. TSMC followed their 16FF process by the 16FF+ which provided roughly 10-15% performance improvement. A final 16FFC (16FF Compact) designed to reduce cost through less masks while using half the power.

In late 2016 TSMC announced a "12nm" process (e.g. 12FFC16 nm Microprocessors

- HiSilicon

- MediaTek

- Microsoft

- Nvidia

- PEZY

- Renesas

This list is incomplete; you can help by expanding it.

16 nm Microarchitectures

- AppliedMicro/Ampere

- ARM

- Zhaoxin

This list is incomplete; you can help by expanding it.

References

- Chen, Yen-Huei, et al. "A 16 nm 128 Mb SRAM in High-κ Metal-Gate FinFET Technology With Write-Assist Circuitry for Low-VMIN Applications." IEEE Journal of Solid-State Circuits 50.1 (2015): 170-177.

- Wu, Shien-Yang, et al. "A 16nm FinFET CMOS technology for mobile SoC and computing applications." Electron Devices Meeting (IEDM), 2013 IEEE International. IEEE, 2013.

- TechInsights/Chipworks, Kevin Gibb, The ConFab 2016

Semiconductor lithography processes technology

Semiconductor lithography processes technology