(→7 nm Microarchitectures) |

(→See also) |

||

| Line 236: | Line 236: | ||

== See also == | == See also == | ||

| − | * {{intel| | + | * {{intel|processs|Intel proces technology history}} |

== References == | == References == | ||

Revision as of 01:33, 8 April 2018

The 7 nanometer (7 nm) lithography process is a technology node semiconductor manufacturing process following the 10 nm process node. The term "7 nm" is simply a commercial name for a generation of a certain size and its technology and does not represent any geometry of a transistor. Commercial mass production of integrated circuit using 7 nm process is set to begin sometimes in 2019 or 2020. This technology will be replaced by 5 nm process around 2022.

Contents

Industry

Only four semiconductor foundries are able to develop the advanced 7nm: Intel, Samsung, TSMC, and GlobalFoundries.

| Process Name | |

|---|---|

| 1st Production | |

| Litho- graphy |

Lithography |

| Immersion | |

| Exposure | |

| Wafer | Type |

| Size | |

| Tran- sistor |

Type |

| Voltage | |

| Fin | Pitch |

| Width | |

| Height | |

| Gate Length (Lg) | |

| Contacted Gate Pitch (CPP) | |

| Minimum Metal Pitch (MMP) | |

| SRAM bitcell |

High-Perf (HP) |

| High-Density (HD) | |

| Low-Voltage (LV) | |

| DRAM bitcell |

eDRAM |

| Intel | TSMC | GlobalFoundries | Samsung | Common Platform Paper | |||||

|---|---|---|---|---|---|---|---|---|---|

| P1276 (CPU), P1277 (SoC) | 7FF, 7FF+ will use EUVL instead of immersion lithography , 7HPC |

7LP 7nm Leading Performance |

7LPE 7 nm Low Power Early |

||||||

| 2019 | 2019 | ||||||||

| EUV | 193 nm | 193 nm | EUV | EUV | |||||

| Yes | Yes | ||||||||

| SAQP | SAQP | SE | SE | ||||||

| Bulk | Bulk | Bulk | Bulk | Bulk | |||||

| 300 mm | 300 mm | 300 mm | 300 mm | 300 nm | |||||

| FinFET | FinFET | FinFET | FinFet | ||||||

| 0.70 V | 0.70 V | ||||||||

| Value | 10 nm Δ | Value | 10 nm Δ | Value | 14 nm Δ | Value | 10 nm Δ | Value | 10 nm Δ |

| 54 nm | 0.84x | 56 nm | 0.72x | 54 nm | 0.79x | 48 nm | 0.75x | ||

| 40 nm | 0.95x | 40 nm | 0.63x | 36 nm | 0.7x | 36 nm | 0.75x | ||

| 0.027 µm² | 0.64x | 0.0269 µm² | 0.34x | 0.0260 µm² | 0.65x | ||||

Intel

- Note: For the most part, foundries' 7nm process is competing against Intel's 10nm process, not their 7nm.

On February 8 2017 Intel announced a $7B investment in Arizona's Fab 42 which will eventually produce chips on a 7 nm process. In May of 2017, Intel's Technology and Manufacturing Group Director, Mark Bohr, confirmed that Intel's 7 nm node has entered development phase and that the company's research focuses on the 5 nm and 3 nm nodes. Details of their 7 nm node have not been disclosed yet. CEO Brian Krzanich mentioned a 2020 timeframe in an investor conference in June.

GlobalFoundries

On May 30 2017, GlobalFoundries Senior Vice President and head of CMOS Business Unit, Gregg Bartlett, announced their updated roadmap. Instead of EUV, the company will use multiple patterning 193i for their 7 nm node. The company is planning on first tape-out in the 2nd half of 2018 with mass production to begin in 2019. Bartlett noted that GF will switch to EUVL when it's ready.

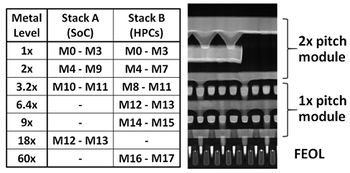

The 7nm proces features SAQP for the FEOL, and double patterning for the BEOL. GlobalFoundries claims a 2.8 times density improvement compared to their 14nm proces, and a performance improvement of 40% or a 55% reduction in power consumption. Two versions of the process will be developed: a low power version for mobile applications. And a high performance version for desktop and server chips.

TSMC

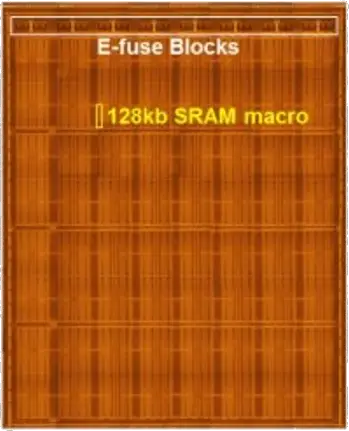

In ISSCC 2017, the memory group at TSMC detailed their test 256 MiB SRAM chip which featured a 42.64 mm² die. The chip is manufactured on TSMC's 7nm HK-MG FinFET process using 4P4E LELELELE patterning technique. The over die is 0.34x smaller than their 16 nm process version. TSMC's 7nm process density is 1.6X compared to their 10nm process. Minimum metal pitch is 40 nm, as reported at IEDM 2016. TSMC claims their 7nm process will deliver a 20% performance improvement and a 40% reduction in power consumption.

The 7nm node will come in two variants, one optimized for mobile applications and a second one optimized for High performance applications. TSMC plans to introduce a second improved process called 7nm+ a year later, which will introduce some layers processed with EUVL. This will improve yields and reduce fab cycle times. The 7nm+ process will deliver improved power consumption and between 15-20% area scaling over their first generation 7nm process.

Samsung

Samsung will use EUVL for their 7nm node and thus will be the first to introduce this new technology after more than a decade of development. On May 24 2017, Samsung released a press release of their updated roadmap. Due to delays in the introduction of EUVL, Samsung will introduce a new process called 8nm LPP, to bridge the gap between 10nm and 7nm. The process will be manufactured without the use of EUVL and will feature a slightly relaxed transistor size.

7 nm Microprocessors

This list is incomplete; you can help by expanding it.

7 nm Microarchitectures

- AMD

- Ampere

- Esperanto

- Intel

See also

References

- Chang, Jonathan, et al. "12.1 A 7nm 256Mb SRAM in high-k metal-gate FinFET technology with write-assist circuitry for low-V MIN applications." Solid-State Circuits Conference (ISSCC), 2017 IEEE International. IEEE, 2017.

- Standaert, T., et al. "BEOL process integration for the 7 nm technology node." Interconnect Technology Conference/Advanced Metallization Conference (IITC/AMC), 2016 IEEE International. IEEE, 2016.

- Samsung/GlobalFoundries, IEEE International Electron Devices Meeting (IEDM) 2016

Semiconductor lithography processes technology

Semiconductor lithography processes technology