From WikiChip

Difference between revisions of "16 nm lithography process"

(→TSMC) |

|||

| Line 38: | Line 38: | ||

{| class="collapsible collapsed wikitable" | {| class="collapsible collapsed wikitable" | ||

|- | |- | ||

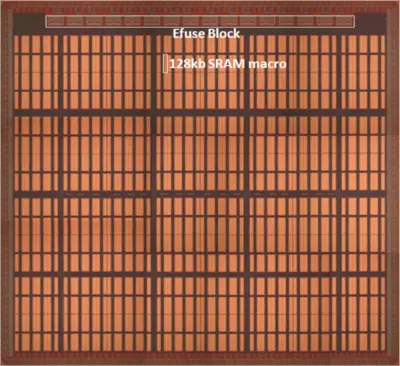

| − | ! colspan="2" | TSMC 128 Mib SRAM demo wafer<ref name="tsmc" /> | + | ! colspan="2" | TSMC 128 Mib SRAM demo 16 nm wafer<ref name="tsmc" /> |

|- | |- | ||

| | | | ||

Revision as of 17:34, 10 March 2017

The 16 nanometer (16 nm) lithography process is a full node semiconductor manufacturing process following the 20 nm process stopgap. Commercial integrated circuit manufacturing using 16 nm process began in 2014. The term "16 nm" is simply a commercial name for a generation of a certain size and its technology, as opposed to gate length or half pitch. This technology is set to be replaced with 10 nm process in 2017.

Industry

| Fab |

|---|

| Wafer |

| |

| Fin Pitch |

| Fin Width |

| Fin Height |

| Contacted Gate Pitch |

| Interconnect Pitch (M1P) |

| SRAM bit cell |

TSMC

TSMC demonstrated their 128 Mebibit SRAM wafer from their 16 nm HKMG FinFET process at the 2014 IEEE ISSCC.

| TSMC 128 Mib SRAM demo 16 nm wafer[2] | |||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

| ||||||||||||||||

16 nm Microprocessors

This list is incomplete; you can help by expanding it.

16 nm Microarchitectures

This list is incomplete; you can help by expanding it.

Semiconductor lithography processes technology

Semiconductor lithography processes technology