From WikiChip

Difference between revisions of "90 nm lithography process"

(→90 nm Microprocessors) |

(fixed) |

||

| (5 intermediate revisions by 4 users not shown) | |||

| Line 1: | Line 1: | ||

{{lithography processes}} | {{lithography processes}} | ||

| − | The '''90 nanometer (90 nm) lithography process''' is a [[technology node|full node]] semiconductor manufacturing process following the [[110 nm lithography process|110 nm process]] stopgap. Commercial [[integrated circuit]] manufacturing using 90 nm process began in 2003. This technology was superseded by the [[80 nm lithography process|80 nm | + | The '''90 nanometer ([[90 nm]]) lithography process''' is a [[technology node|full node]] semiconductor manufacturing process following the [[110 nm lithography process|110 nm process]] stopgap. |

| + | :Commercial [[integrated circuit]] manufacturing using [[90 nm]] process began in [[2003]]. | ||

| + | This technology was superseded by the [[80 nm lithography process|80 nm]] (HN) / [[65 nm lithography process|65 nm process]] (FN) in [[2006]]. | ||

== Industry == | == Industry == | ||

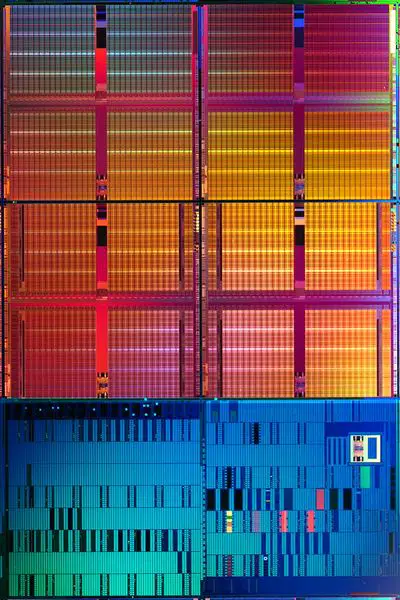

| − | Introduced in late 2002, Intel's 90 nm process became the first volume production to introduce [[strained silicon]] transistors. | + | [[File:45nm SRAM photo.JPG|left|400px]] |

| − | {{scrolling table/top|style=text-align: right; | first=Fab | + | Introduced in late [[2002]], [[Intel]]'s [[90 nm]] process became the first volume production to introduce [[strained silicon]] transistors. |

| + | {{clear}} | ||

| + | |||

| + | === Specifications === | ||

| + | {{scrolling table/top|style=text-align: right; | first=Fab /<br>Manuf | ||

|Process Name | |Process Name | ||

|1st Production | |1st Production | ||

| Line 11: | Line 17: | ||

|Metal Layers | |Metal Layers | ||

| | | | ||

| − | |Contacted Gate Pitch | + | |Contacted <br>Gate Pitch |

| − | |Interconnect Pitch (M1P) | + | |Interconnect <br>Pitch (M1P) |

| − | |SRAM bit cell | + | |SRAM <br>bit cell |

| − | |DRAM bit cell | + | |DRAM <br>bit cell |

}} | }} | ||

{{scrolling table/mid}} | {{scrolling table/mid}} | ||

|- | |- | ||

| − | ! colspan="2" | [[Intel]] !! colspan="2" | [[TSMC]] !! colspan="2" | [[Samsung]] !! colspan="2" | [[Fujitsu]] || colspan="2" | [[IBM]] / [[Toshiba]] / [[Sony]] / [[AMD]] / [[Chartered]] !! colspan="2" | [[Motorola]] !! colspan="2" | [[TI]] | + | ! colspan="2" | [[Intel]] !! colspan="2" | [[TSMC]] !! colspan="2" | [[Samsung]] !! colspan="2" | [[Fujitsu]] || colspan="2" | [[IBM]] / [[Toshiba]] / <br>[[Sony]] / [[AMD]] <!--/ [[Chartered]]--> !! colspan="2" | [[Motorola]] !! colspan="2" | [[TI]] |

|- style="text-align: center;" | |- style="text-align: center;" | ||

| colspan="2" | P1262 || colspan="2" | || colspan="2" | || colspan="2" | CS-100 / CS-101 || colspan="2" | || colspan="2" | HiPerMOS 8 || colspan="2" | | | colspan="2" | P1262 || colspan="2" | || colspan="2" | || colspan="2" | CS-100 / CS-101 || colspan="2" | || colspan="2" | HiPerMOS 8 || colspan="2" | | ||

| Line 32: | Line 38: | ||

! Value !! [[130 nm]] Δ !! Value !! [[130 nm]] Δ !! Value !! [[130 nm]] Δ !! Value !! [[130 nm]] Δ !! Value !! [[130 nm]] Δ !! Value !! [[130 nm]] Δ !! Value !! [[130 nm]] Δ | ! Value !! [[130 nm]] Δ !! Value !! [[130 nm]] Δ !! Value !! [[130 nm]] Δ !! Value !! [[130 nm]] Δ !! Value !! [[130 nm]] Δ !! Value !! [[130 nm]] Δ !! Value !! [[130 nm]] Δ | ||

|- | |- | ||

| − | | 260 nm || 0.82x || 240 nm || 0.77x || 245 nm || 0.70x || ? nm || ?x || ? nm || ?x || ? nm || ?x || ? nm || ?x | + | | 260 nm || 0.82x || 240 nm || 0.77x || 245 nm || 0.70x || ? nm || ?x || ? nm || ?x || ? nm || ?x || ? nm || ?x <br>. |

|- | |- | ||

| − | | 220 nm || 0.63x || 240 nm || 0.71x || 245 nm || 0.70x || ? nm || ?x || ? nm || ?x || ? nm || ?x || ? nm || ?x | + | | 220 nm || 0.63x || 240 nm || 0.71x || 245 nm || 0.70x || ? nm || ?x || ? nm || ?x || ? nm || ?x || ? nm || ?x <br>. |

|- | |- | ||

| − | | 1.0 µm² || 0.50x || 0.999 µm² || 0.47x || 0.999 µm² || ?x || 1.07 µm² || 0.54x || 0.999 µm² || ?x || ? µm² || ?x || ? µm² || ?x | + | | 1.0 µm² || 0.50x || 0.999 <br>µm² || 0.47x || 0.999 <br>µm² || ?x || 1.07 µm² || 0.54x || 0.999 <br>µm² || ?x || ? µm² || ?x || ? µm² || ?x |

|- | |- | ||

| − | | || || || || 0.275 µm² || || || || 0.19 µm² || ?x || || || || | + | | || || || || 0.275 <br>µm² || || || || 0.19 µm² || ?x || || || || |

{{scrolling table/end}} | {{scrolling table/end}} | ||

== 90 nm Microprocessors== | == 90 nm Microprocessors== | ||

| − | * AMD | + | * [[AMD]] |

** {{amd|Athlon 64}} | ** {{amd|Athlon 64}} | ||

** {{amd|Athlon 64 X2}} | ** {{amd|Athlon 64 X2}} | ||

| Line 49: | Line 55: | ||

** {{amd|Turion 64}} | ** {{amd|Turion 64}} | ||

** {{amd|Turion 64 X2}} | ** {{amd|Turion 64 X2}} | ||

| − | * Cavium | + | * [[Cavium]] |

** {{cavium|OCTEON Plus}} | ** {{cavium|OCTEON Plus}} | ||

| − | * HAL (Fujitsu) | + | * HAL ([[Fujitsu]]) |

** {{hal|SPARC64 V}} | ** {{hal|SPARC64 V}} | ||

| − | * IBM | + | * [[IBM]] |

** {{ibm|PowerPC 970}} | ** {{ibm|PowerPC 970}} | ||

* Loongson | * Loongson | ||

** {{loongson|Godson 2}} | ** {{loongson|Godson 2}} | ||

| − | * Qualcomm | + | * [[Qualcomm]] |

** {{qualcomm|MSM6xxx}} | ** {{qualcomm|MSM6xxx}} | ||

* Sun | * Sun | ||

** {{sun|UltraSPARC T1}} | ** {{sun|UltraSPARC T1}} | ||

| − | * Intel | + | * [[Intel]] |

** {{intel|Pentium 4 Extreme Edition}} | ** {{intel|Pentium 4 Extreme Edition}} | ||

** {{intel|Pentium M}} | ** {{intel|Pentium M}} | ||

** {{intel|Pentium D}} | ** {{intel|Pentium D}} | ||

** {{intel|EP80579}} | ** {{intel|EP80579}} | ||

| − | + | * [[STMicro]]electronics | |

| − | + | ** STM32 F4 | |

| + | ** STM32 F7 | ||

| + | ** STM32 G0 | ||

| + | ** STM32 G4 | ||

{{expand list}} | {{expand list}} | ||

== 90 nm Microarchitectures == | == 90 nm Microarchitectures == | ||

| − | * AMD | + | * [[AMD]] |

** {{amd|K8|l=arch}} | ** {{amd|K8|l=arch}} | ||

| − | * ARM | + | * [[ARM]] |

** {{armh|ARM7|l=arch}} | ** {{armh|ARM7|l=arch}} | ||

| − | * Intel | + | * [[IBM]] |

| + | ** {{ibm|z9|l=arch}} | ||

| + | * [[Intel]] | ||

** {{intel|Pentium M|l=arch}} | ** {{intel|Pentium M|l=arch}} | ||

| + | * VIA Technologies | ||

| + | ** {{via|Esther|l=arch}} | ||

| + | |||

{{expand list}} | {{expand list}} | ||

== Documents == | == Documents == | ||

* [[:File:samsung foundry - 45, 65, 90 (August, 2007).pdf|Samsung foundry - 45 nm, 65 nm, 90 nm guide (August, 2007)]] | * [[:File:samsung foundry - 45, 65, 90 (August, 2007).pdf|Samsung foundry - 45 nm, 65 nm, 90 nm guide (August, 2007)]] | ||

| + | |||

| + | [[category:lithography]] | ||

Latest revision as of 22:27, 19 March 2025

The 90 nanometer (90 nm) lithography process is a full node semiconductor manufacturing process following the 110 nm process stopgap.

- Commercial integrated circuit manufacturing using 90 nm process began in 2003.

This technology was superseded by the 80 nm (HN) / 65 nm process (FN) in 2006.

Contents

Industry[edit]

Introduced in late 2002, Intel's 90 nm process became the first volume production to introduce strained silicon transistors.

Specifications[edit]

| Fab / Manuf |

|---|

| Process Name |

| 1st Production |

| Type |

| Wafer |

| Metal Layers |

| |

| Contacted Gate Pitch |

| Interconnect Pitch (M1P) |

| SRAM bit cell |

| DRAM bit cell |

| Intel | TSMC | Samsung | Fujitsu | IBM / Toshiba / Sony / AMD |

Motorola | TI | |||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| P1262 | CS-100 / CS-101 | HiPerMOS 8 | |||||||||||

| 2002 | 2003 | 2003 | 2004 | 2003 | 2004 | 2005 | |||||||

| Bulk | PDSOI | Bulk | |||||||||||

| 300mm | |||||||||||||

| 7 | 10 | 9 | |||||||||||

| Value | 130 nm Δ | Value | 130 nm Δ | Value | 130 nm Δ | Value | 130 nm Δ | Value | 130 nm Δ | Value | 130 nm Δ | Value | 130 nm Δ |

| 260 nm | 0.82x | 240 nm | 0.77x | 245 nm | 0.70x | ? nm | ?x | ? nm | ?x | ? nm | ?x | ? nm | ?x . |

| 220 nm | 0.63x | 240 nm | 0.71x | 245 nm | 0.70x | ? nm | ?x | ? nm | ?x | ? nm | ?x | ? nm | ?x . |

| 1.0 µm² | 0.50x | 0.999 µm² |

0.47x | 0.999 µm² |

?x | 1.07 µm² | 0.54x | 0.999 µm² |

?x | ? µm² | ?x | ? µm² | ?x |

| 0.275 µm² |

0.19 µm² | ?x | |||||||||||

90 nm Microprocessors[edit]

- AMD

- Cavium

- HAL (Fujitsu)

- IBM

- Loongson

- Qualcomm

- Sun

- Intel

- STMicroelectronics

- STM32 F4

- STM32 F7

- STM32 G0

- STM32 G4

This list is incomplete; you can help by expanding it.

90 nm Microarchitectures[edit]

This list is incomplete; you can help by expanding it.

Semiconductor lithography processes technology

Semiconductor lithography processes technology