(→Industry) |

(→Industry) |

||

| Line 3: | Line 3: | ||

== Industry == | == Industry == | ||

| − | In ISSCC 2017, the memory group at [[TSMC]] detailed their test 128 MiB SRAM chip which featured a 42.64 mm² die. The chip is manufactured on TSMC's 7nm HK-MG FinFET process using 4P4E LELELELE patterning technique | + | In ISSCC 2017, the memory group at [[TSMC]] detailed their test 128 MiB SRAM chip which featured a 42.64 mm² die. The chip is manufactured on TSMC's 7nm HK-MG FinFET process using 4P4E LELELELE patterning technique. The over die is 0.34x smaller than their [[16 nm process]] version. At the same conference, [[Samsung]] detailed limited use for [[EUV]] in their 7nm node, though not much more is known. On February 8 2017 Intel announced a $7B investment in Arizona's Fab 42 which will eventually produce chips on a 7 nm process. |

| Line 9: | Line 9: | ||

| − | {{ | + | {{finfet nodes comp |

| − | | | + | <!-- Intel --> |

| − | | | + | | process 1 fab = [[Intel]] |

| − | | | + | | process 1 name = P1276 (CPU), P1277 (SoC) |

| − | | | + | | process 1 date = |

| − | | | + | | process 1 lith = 193 nm |

| − | | | + | | process 1 immersion = Yes |

| − | | | + | | process 1 exposure = SAQP |

| − | | | + | | process 1 wafer type = Bulk |

| − | | | + | | process 1 wafer size = 300 nm |

| − | | | + | | process 1 transistor = FinFET |

| − | | | + | | process 1 volt = |

| + | | process 1 delta from = [[10 nm]] Δ | ||

| + | | process 1 fin pitch = | ||

| + | | process 1 fin pitch Δ = | ||

| + | | process 1 fin width = | ||

| + | | process 1 fin width Δ = | ||

| + | | process 1 fin height = | ||

| + | | process 1 fin height Δ = | ||

| + | | process 1 gate len = | ||

| + | | process 1 gate len Δ = | ||

| + | | process 1 cpp = | ||

| + | | process 1 cpp Δ = | ||

| + | | process 1 mmp = | ||

| + | | process 1 mmp Δ = | ||

| + | | process 1 sram hp = | ||

| + | | process 1 sram hp Δ = | ||

| + | | process 1 sram hd = | ||

| + | | process 1 sram hd Δ = | ||

| + | | process 1 sram lv = | ||

| + | | process 1 sram lv Δ = | ||

| + | | process 1 dram = | ||

| + | | process 1 dram Δ = | ||

| + | <!-- TSMC --> | ||

| + | | process 2 fab = [[TSMC]] | ||

| + | | process 2 name = | ||

| + | | process 2 date = | ||

| + | | process 2 lith = 193 nm | ||

| + | | process 2 immersion = Yes | ||

| + | | process 2 exposure = LELELELE | ||

| + | | process 2 wafer type = Bulk | ||

| + | | process 2 wafer size = 300 nm | ||

| + | | process 2 transistor = FinFET | ||

| + | | process 2 volt = | ||

| + | | process 2 delta from = [[10 nm]] Δ | ||

| + | | process 2 fin pitch = | ||

| + | | process 2 fin pitch Δ = | ||

| + | | process 2 fin width = | ||

| + | | process 2 fin width Δ = | ||

| + | | process 2 fin height = | ||

| + | | process 2 fin height Δ = | ||

| + | | process 2 gate len = | ||

| + | | process 2 gate len Δ = | ||

| + | | process 2 cpp = 54 | ||

| + | | process 2 cpp Δ = 0.84x | ||

| + | | process 2 mmp = 38 | ||

| + | | process 2 mmp Δ = 0.90x | ||

| + | | process 2 sram hp = | ||

| + | | process 2 sram hp Δ = | ||

| + | | process 2 sram hd = 0.027 µm² | ||

| + | | process 2 sram hd Δ = 0.64x | ||

| + | | process 2 sram lv = | ||

| + | | process 2 sram lv Δ = | ||

| + | | process 2 dram = | ||

| + | | process 2 dram Δ = | ||

| + | <!-- Common Platform --> | ||

| + | | process 3 fab = Common Platform<info>[[IBM]], [[Samsung]], [[GlobalFoundries]]</info> | ||

| + | | process 3 name = | ||

| + | | process 3 date = | ||

| + | | process 3 lith = EUV | ||

| + | | process 3 immersion = | ||

| + | | process 3 exposure = SE | ||

| + | | process 3 wafer type = Bulk | ||

| + | | process 3 wafer size = 300 nm | ||

| + | | process 3 transistor = FinFet | ||

| + | | process 3 volt = | ||

| + | | process 3 delta from = [[10 nm]] Δ | ||

| + | | process 3 fin pitch = | ||

| + | | process 3 fin pitch Δ = | ||

| + | | process 3 fin width = | ||

| + | | process 3 fin width Δ = | ||

| + | | process 3 fin height = | ||

| + | | process 3 fin height Δ = | ||

| + | | process 3 gate len = | ||

| + | | process 3 gate len Δ = | ||

| + | | process 3 cpp = 48 nm | ||

| + | | process 3 cpp Δ = 0.75x | ||

| + | | process 3 mmp = 36 nm | ||

| + | | process 3 mmp Δ = 0.75x | ||

| + | | process 3 sram hp = | ||

| + | | process 3 sram hp Δ = | ||

| + | | process 3 sram hd = | ||

| + | | process 3 sram hd Δ = | ||

| + | | process 3 sram lv = | ||

| + | | process 3 sram lv Δ = | ||

| + | | process 3 dram = | ||

| + | | process 3 dram Δ = | ||

}} | }} | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

=== TSMC === | === TSMC === | ||

Revision as of 23:29, 6 April 2017

The 7 nanometer (7 nm) lithography process is a full node semiconductor manufacturing process following the 10 nm process node. The term "7 nm" is simply a commercial name for a generation of a certain size and its technology, as opposed to gate length or half pitch. Commercial mass production of integrated circuit using 7 nm process is set to begin sometimes in 2019 or 2020. This technology will be replaced by 5 nm process around 2022.

Industry

In ISSCC 2017, the memory group at TSMC detailed their test 128 MiB SRAM chip which featured a 42.64 mm² die. The chip is manufactured on TSMC's 7nm HK-MG FinFET process using 4P4E LELELELE patterning technique. The over die is 0.34x smaller than their 16 nm process version. At the same conference, Samsung detailed limited use for EUV in their 7nm node, though not much more is known. On February 8 2017 Intel announced a $7B investment in Arizona's Fab 42 which will eventually produce chips on a 7 nm process.

| Process Name | |

|---|---|

| 1st Production | |

| Litho- graphy |

Lithography |

| Immersion | |

| Exposure | |

| Wafer | Type |

| Size | |

| Tran- sistor |

Type |

| Voltage | |

| Fin | Pitch |

| Width | |

| Height | |

| Gate Length (Lg) | |

| Contacted Gate Pitch (CPP) | |

| Minimum Metal Pitch (MMP) | |

| SRAM bitcell |

High-Perf (HP) |

| High-Density (HD) | |

| Low-Voltage (LV) | |

| DRAM bitcell |

eDRAM |

| Intel | TSMC | Common Platform | |||

|---|---|---|---|---|---|

| P1276 (CPU), P1277 (SoC) | |||||

| 193 nm | 193 nm | EUV | |||

| Yes | Yes | ||||

| SAQP | LELELELE | SE | |||

| Bulk | Bulk | Bulk | |||

| 300 nm | 300 nm | 300 nm | |||

| FinFET | FinFET | FinFet | |||

| Value | 10 nm Δ | Value | 10 nm Δ | Value | 10 nm Δ |

| 54 | 0.84x | 48 nm | 0.75x | ||

| 38 | 0.90x | 36 nm | 0.75x | ||

| 0.027 µm² | 0.64x | ||||

TSMC

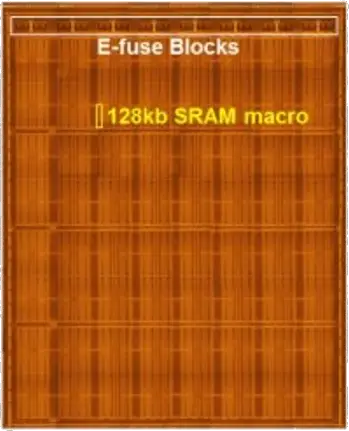

TSMC demonstrated their 256 Mebibit SRAM wafer from their 7nm HKMG FinFET process. Their chip makes use of 34% of the area of their 16 nm process demo chip counterpart.

7 nm Microprocessors

- MediaTek

This list is incomplete; you can help by expanding it.

7 nm Microarchitectures

This list is incomplete; you can help by expanding it.

References

- Chang, Jonathan, et al. "12.1 A 7nm 256Mb SRAM in high-k metal-gate FinFET technology with write-assist circuitry for low-V MIN applications." Solid-State Circuits Conference (ISSCC), 2017 IEEE International. IEEE, 2017.

- Standaert, T., et al. "BEOL process integration for the 7 nm technology node." Interconnect Technology Conference/Advanced Metallization Conference (IITC/AMC), 2016 IEEE International. IEEE, 2016.

- Samsung/GlobalFoundries, IEEE International Electron Devices Meeting (IEDM) 2016

Semiconductor lithography processes technology

Semiconductor lithography processes technology