(→Industry) |

(→Industry) |

||

| (12 intermediate revisions by 6 users not shown) | |||

| Line 32: | Line 32: | ||

| process 1 mmp Δ = 0.71x | | process 1 mmp Δ = 0.71x | ||

| process 1 sram hp = 0.130 µm² | | process 1 sram hp = 0.130 µm² | ||

| − | | process 1 sram hp Δ = | + | | process 1 sram hp Δ = 0.65x |

| process 1 sram hd = 0.092 µm² | | process 1 sram hd = 0.092 µm² | ||

| − | | process 1 sram hd Δ = | + | | process 1 sram hd Δ = 0.62x |

| process 1 sram lv = 0.108 µm² | | process 1 sram lv = 0.108 µm² | ||

| − | | process 1 sram lv Δ = | + | | process 1 sram lv Δ = 0.63x |

| process 1 dram = 0.029 µm² | | process 1 dram = 0.029 µm² | ||

| process 1 dram Δ = | | process 1 dram Δ = | ||

<!-- Intel 22FFL --> | <!-- Intel 22FFL --> | ||

| process 2 fab = [[Intel]] | | process 2 fab = [[Intel]] | ||

| − | | process 2 name = 22FFL | + | | process 2 name = 22FFL (P1222) |

| process 2 date = 2017 | | process 2 date = 2017 | ||

| process 2 lith = 193 nm | | process 2 lith = 193 nm | ||

| Line 49: | Line 49: | ||

| process 2 wafer size = 300 mm | | process 2 wafer size = 300 mm | ||

| process 2 transistor = FinFET | | process 2 transistor = FinFET | ||

| − | | process 2 volt = | + | | process 2 volt = 0.7 V |

| process 2 delta from = [[32 nm]] Δ | | process 2 delta from = [[32 nm]] Δ | ||

| process 2 fin pitch = 45 nm | | process 2 fin pitch = 45 nm | ||

| Line 73: | Line 73: | ||

<!-- Samsung --> | <!-- Samsung --> | ||

| process 3 fab = [[IBM]] | | process 3 fab = [[IBM]] | ||

| − | | process 3 name = | + | | process 3 name = 22HP |

| process 3 date = 2013 | | process 3 date = 2013 | ||

| process 3 lith = 193 | | process 3 lith = 193 | ||

| Line 81: | Line 81: | ||

| process 3 wafer size = 300 mm | | process 3 wafer size = 300 mm | ||

| process 3 transistor = Planar | | process 3 transistor = Planar | ||

| − | | process 3 volt = | + | | process 3 volt = 0.75 V |

| process 3 delta from = [[32 nm]] Δ | | process 3 delta from = [[32 nm]] Δ | ||

| process 3 fin pitch = - | | process 3 fin pitch = - | ||

| Line 89: | Line 89: | ||

| process 3 fin height = | | process 3 fin height = | ||

| process 3 fin height Δ = | | process 3 fin height Δ = | ||

| − | | process 3 gate len = | + | | process 3 gate len = 25-33 nm |

| − | | process 3 gate len Δ = | + | | process 3 gate len Δ = 0.83-1.1x |

| process 3 cpp = 100 nm | | process 3 cpp = 100 nm | ||

| − | | process 3 cpp Δ = | + | | process 3 cpp Δ = 0.79x |

| process 3 mmp = 80 nm | | process 3 mmp = 80 nm | ||

| − | | process 3 mmp Δ = | + | | process 3 mmp Δ = 0.80x |

| process 3 sram hp = 0.144 µm² | | process 3 sram hp = 0.144 µm² | ||

| − | | process 3 sram hp Δ = | + | | process 3 sram hp Δ = |

| process 3 sram hd = 0.128 µm² | | process 3 sram hd = 0.128 µm² | ||

| − | | process 3 sram hd Δ = | + | | process 3 sram hd Δ = 0.86x |

| − | | process 3 sram lv = | + | | process 3 sram lv = |

| − | | process 3 sram lv Δ = | + | | process 3 sram lv Δ = |

| process 3 dram = 0.026 µm² | | process 3 dram = 0.026 µm² | ||

| − | | process 3 dram Δ = | + | | process 3 dram Δ = 0.67x |

}} | }} | ||

| Line 141: | Line 141: | ||

| Options || High Performance (HP) || Standard Perf/Power (SP) || Low Power (LP) || Ultra-Low Power (ULP) || 1.8 V || 3.3 V | | Options || High Performance (HP) || Standard Perf/Power (SP) || Low Power (LP) || Ultra-Low Power (ULP) || 1.8 V || 3.3 V | ||

|- | |- | ||

| − | | V<sub>dd</sub> (V) || 0. | + | | V<sub>dd</sub> (V) || 0.7 V / 1 V || 0.75 V / 1 V || 0.75 V / 1 V || 0.75 V / 1.2 V || 1.5 V / 1.8 V / 3.3 V || 3.3 V / >5V |

|- | |- | ||

| Gate Pitch (nm) || 90 || 90 || 90 || 108 || min. 180 || min 450 | | Gate Pitch (nm) || 90 || 90 || 90 || 108 || min. 180 || min 450 | ||

| Line 193: | Line 193: | ||

== 22 nm Microarchitectures== | == 22 nm Microarchitectures== | ||

| − | * Intel | + | * Intel |

| − | ** {{intel|Haswell}} | + | ** {{intel|Haswell|l=arch}} |

| − | ** {{intel|Ivy Bridge}} | + | ** {{intel|Ivy Bridge|l=arch}} |

| − | ** {{intel|Silvermont}} | + | ** {{intel|Silvermont|l=arch}} |

| − | + | * IBM | |

| + | ** {{ibm|POWER8|l=arch}} | ||

| + | ** {{ibm|z13|l=arch}} | ||

{{expand list}} | {{expand list}} | ||

| Line 204: | Line 206: | ||

== References == | == References == | ||

| − | * | + | * IEDM 2012 |

| − | * | + | * IEDM 2014 |

| − | * | + | * ISSCC 2015 |

| − | |||

| − | [[ | + | [[category:lithography]] |

Latest revision as of 08:52, 25 November 2020

The 22 nanometer (22 nm) lithography process is a full node semiconductor manufacturing process following the 28 nm process stopgap. The term "22 nm" is simply a commercial name for a generation of a certain size and its technology, as opposed to gate length or half pitch. Commercial integrated circuit manufacturing using 22 nm process began in 2008 for memory and 2012 for MPUs. This technology was replaced by with 20 nm process (HN) in 2014 and 16 nm process (FN) in late 2015.

Contents

Industry[edit]

The 22 nm became Intel's first generation of Tri-gate FinFET transistors and the first such transistor on the market. This process became 3rd generation high-k + metal gate transistors for Intel. In 2017 Intel announce the introduction of a new process "22FFL" specifically for low power IOT and mobile products for their custom foundry.

| Process Name | |

|---|---|

| 1st Production | |

| Lithography | Lithography |

| Immersion | |

| Exposure | |

| Wafer | Type |

| Size | |

| Transistor | Type |

| Voltage | |

| Fin | Pitch |

| Width | |

| Height | |

| Gate Length (Lg) | |

| Contacted Gate Pitch (CPP) | |

| Minimum Metal Pitch (MMP) | |

| SRAM bitcell | High-Perf (HP) |

| High-Density (HD) | |

| Low-Voltage (LV) | |

| DRAM bitcell | eDRAM |

| Intel | Intel | IBM | |||

|---|---|---|---|---|---|

| P1270 (CPU) / P1271 (SoC) | 22FFL (P1222) | 22HP | |||

| 2011 | 2017 | 2013 | |||

| 193 nm | 193 nm | 193 | |||

| Yes | Yes | Yes | |||

| SADP | SADP | ||||

| Bulk | Bulk | SOI | |||

| 300 mm | 300 mm | 300 mm | |||

| FinFET | FinFET | Planar | |||

| 0.75 V | 0.7 V | 0.75 V | |||

| Value | 32 nm Δ | Value | 32 nm Δ | Value | 32 nm Δ |

| 60 nm | N/A | 45 nm | N/A | N/A | |

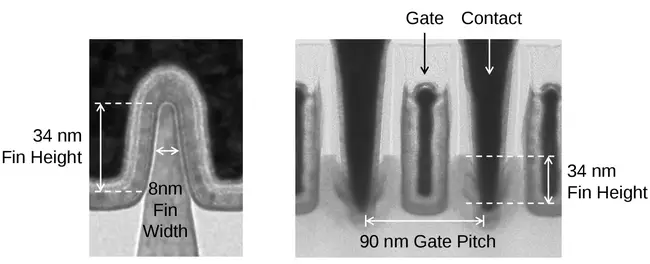

| 8 nm | |||||

| 34 nm | |||||

| 26 nm | 30 nm | 25-33 nm | 0.83-1.1x | ||

| 90 nm | 0.80x | 108 nm | 100 nm | 0.79x | |

| 80 nm | 0.71x | 90 nm | 80 nm | 0.80x | |

| 0.130 µm² | 0.65x | 0.144 µm² | |||

| 0.092 µm² | 0.62x | 0.088 µm² | 0.128 µm² | 0.86x | |

| 0.108 µm² | 0.63x | ||||

| 0.029 µm² | 0.026 µm² | 0.67x | |||

Intel[edit]

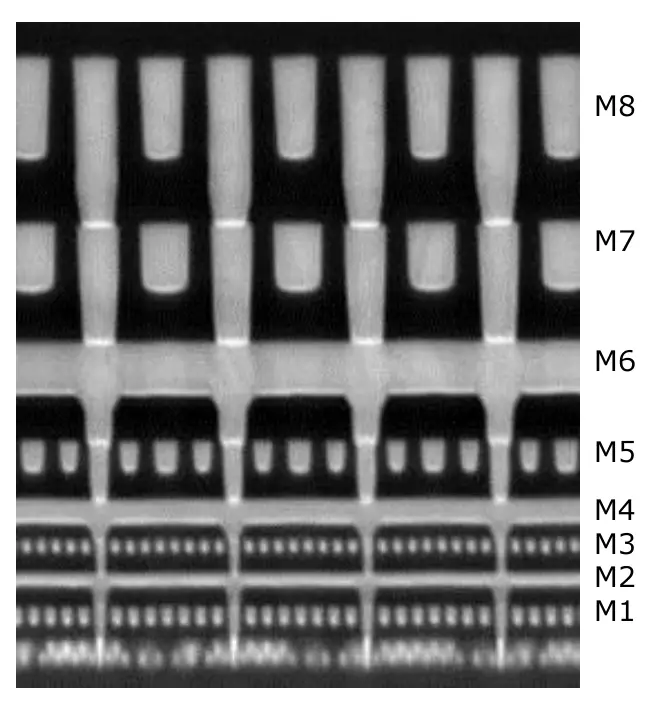

| Intel 22nm SoC Interconnect Design Rules | ||||||

|---|---|---|---|---|---|---|

| Layer | Pitch | Process | Dielectric Materials | CPU | SoC | Image |

| Fin | 60 nm | - | - | Fin | Fin |

|

| Contact | 90 nm | SAC | - | Contact | Contact | |

| M1 | 90 nm | SAV | ULK CDO | M1 | M1 | |

| MT - 1x | 80 nm | SAV | ULK CDO | M2/M3 | 2-6 layers | |

| MT - 1.4x | 112 nm | SAV | ULK CDO | M4 | Semi-global | |

| MT - 2x | 160 nm | SAV | ULK CDO | M5 | Semi-global | |

| MT - 3x | 240 nm | SAV | ULK CDO | M6 | Global Routing | |

| MT - 4x | 320 nm 360 nm |

Via First | LK CDO | M7/M8 | Global Routing | |

| MT - TOP | 14 µm | Plate Up | Polymer | M9 | Top Metal | |

| Intel 22nm SoC Transistor Characteristics | ||||||

|---|---|---|---|---|---|---|

| Transistor Type | High Speed Logic | Low Power Logic | High Voltage Logic | |||

| Options | High Performance (HP) | Standard Perf/Power (SP) | Low Power (LP) | Ultra-Low Power (ULP) | 1.8 V | 3.3 V |

| Vdd (V) | 0.7 V / 1 V | 0.75 V / 1 V | 0.75 V / 1 V | 0.75 V / 1.2 V | 1.5 V / 1.8 V / 3.3 V | 3.3 V / >5V |

| Gate Pitch (nm) | 90 | 90 | 90 | 108 | min. 180 | min 450 |

| Lgate (nm) | 30 | 34 | 34 | 40 | min. 80 | in 280 |

| N/PMOS Idsat/Ioff (mA/µm) | 1.08/0.91 @ 0.75 V, 100 nA/µm | 0.71/0.59 @0.75 V, 1 nA/µm | 0.41/0.37 @ 0.75 V, 30 pA/µm | 0.35/0.33 @ 0.75 V, 15 pA/µm | 0.92/0.8 @ 1.8 V, 10 pA/µm | 1/0.8 @ 3.3 V, 10 pA/µm |

Find models[edit]

Click to browse all 22 nm MPU models

22 nm Microprocessors[edit]

This list is incomplete; you can help by expanding it.

Click to browse all 22 nm MPU models

22 nm Microarchitectures[edit]

- Intel

- IBM

This list is incomplete; you can help by expanding it.

Documents[edit]

References[edit]

- IEDM 2012

- IEDM 2014

- ISSCC 2015

Semiconductor lithography processes technology

Semiconductor lithography processes technology