| Edit Values | |

| Zen 2 µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | AMD |

| Manufacturer | GlobalFoundries, TSMC |

| Introduction | 2019 |

| Process | 14 nm, 7 nm, 12 nm |

| Pipeline | |

| Type | Superscalar |

| OoOE | Yes |

| Speculative | Yes |

| Reg Renaming | Yes |

| Stages | 19 |

| Decode | 4-way |

| Instructions | |

| ISA | x86-64 |

| Extensions | MOVBE, MMX, SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4.2, POPCNT, AVX, AVX2, AES, PCLMUL, RDRND, F16C, BMI, BMI2, RDSEED, ADCX, PREFETCHW, CLFLUSHOPT, XSAVE, SHA, CLZERO |

| Cores | |

| Core Names | Rome |

| Succession | |

Zen 2 is AMD's successor to Zen+, a 7 nm process microarchitecture for mainstream mobile, desktops, workstations, and servers. Zen 2 will eventually be replaced by Zen 3.

For performance desktop and mobile computing, Zen is branded as Athlon, Ryzen 3, Ryzen 5, Ryzen 7, Ryzen 9, and Ryzen Threadripper processors. For servers, Zen is branded as EPYC.

Contents

History

Zen 2 succeeded Zen in 2019. In February of 2017 Lisa Su, AMD's CEO announced their future roadmap to include Zen 2 and later Zen 3. On Investor's Day May 2017 Jim Anderson, AMD Senior Vice President, confirmed that Zen 2 was set to utilize 7 nm process. Initial details of Zen 2 and Rome were unveiled during AMD's Next Horizon event on November 6, 2018.

Codenames

| Core | C/T | Target |

|---|---|---|

| Rome | Up to 64/128 | High-end server multiprocessors |

| Castle Peak | Up to 64/128? | Workstation & enthusiasts market processors |

| Matisse | Up to 16/32 | Mainstream to high-end desktops & enthusiasts market processors |

| Renoir | Up to 4/8? | Mainstream APUs with Navi GPUs |

| River Hawk | Up to 2/4? | Low-power/Cost-sensitive embedded processors with Navi GPU |

Brands

| AMD Zen-based processor brands | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| Logo | Family | General Description | Differentiating Features | |||||||

| Cores | Unlocked | AVX2 | SMT | IGP | ECC | MP | ||||

| Mainstream | ||||||||||

|

Ryzen 3 | Entry level Performance | ? | |||||||

|

Ryzen 5 | Mid-range Performance | Hexa | ✔ | ✔ | ✔ | ✘ | ✔ | ✘ | |

|

Ryzen 7 | High-end Performance | Octa | ✔ | ✔ | ✔ | ✘ | ✔ | ✘ | |

| Ryzen 9 | High-end Performance | 12-16 | ✔ | ✔ | ✔ | ✘ | ✔ | ✘ | ||

| Enthusiasts / Workstations | ||||||||||

|

Ryzen Threadripper | Enthusiasts | 12-64 | ? | ||||||

| Servers | ||||||||||

|

EPYC | High-performance Server Processor | 8-64 | ✘ | ✔ | ✔ | ✘ | ✔ | ✔ | |

| Embedded / Edge | ||||||||||

|

EPYC Embedded | Embedded / Edge Server Processor | ? | |||||||

|

Ryzen Embedded | Embedded APUs | ? | |||||||

Process technology

Zen 2 comprises multiple different components:

- The Core Chiplet Die (CCD) is fabricated on TSMC 7 nm HPC process

- The client I/O Die (cIOD) is fabricated on GlobalFoundries 12 nm process

- The server I/O Die (sIOD) is fabricated on GlobalFoundries 14 nm process

Compiler support

| Compiler | Arch-Specific | Arch-Favorable |

|---|---|---|

| GCC | -march=znver2 |

-mtune=znver2

|

| LLVM | -march=znver2 |

-mtune=znver2

|

- Note: Initial support in GCC 9 and LLVM 9.

Architecture

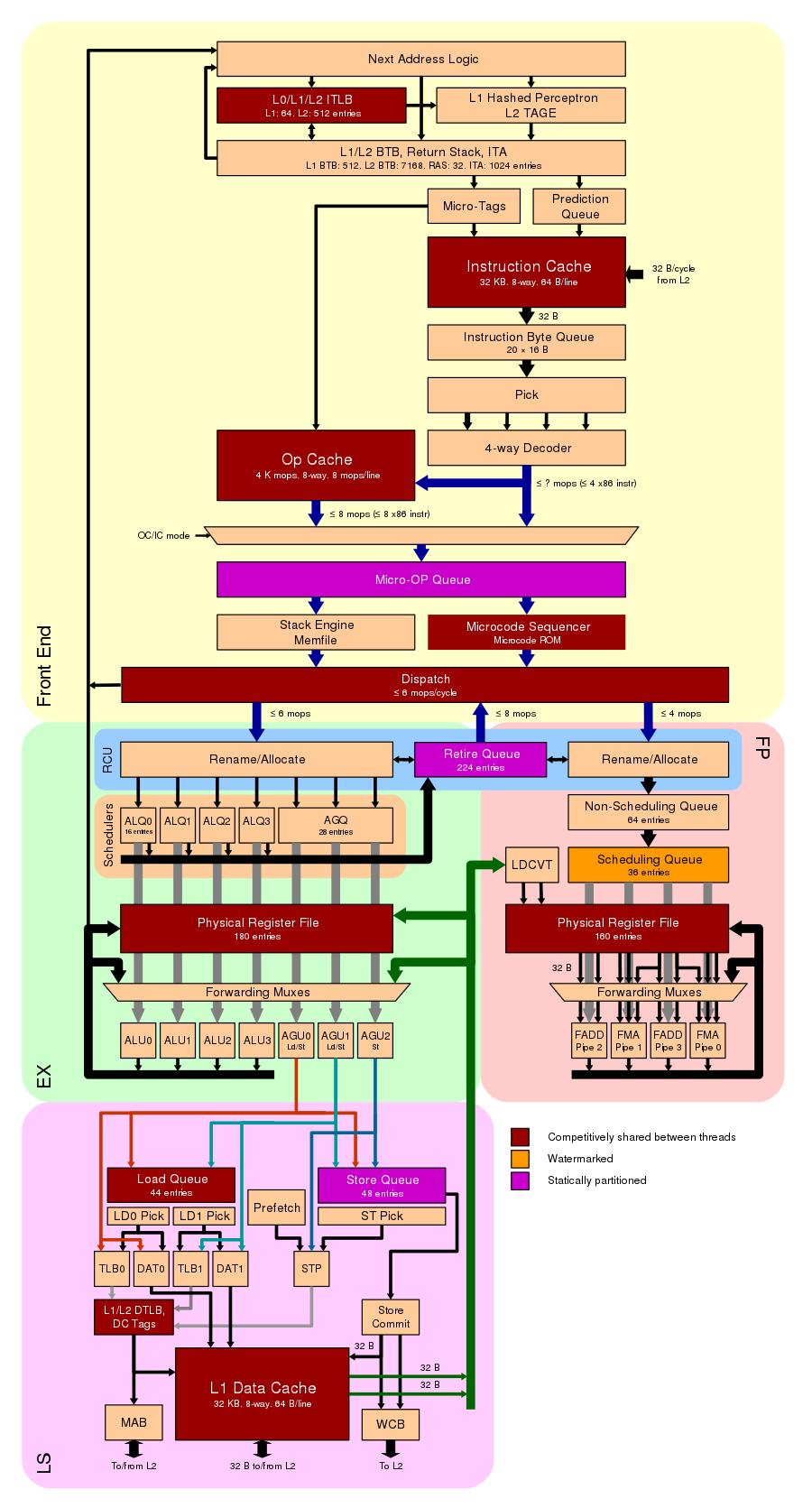

Zen 2 inherits most of the design from Zen+ but improves the instruction stream bandwidth and floating-point throughput performance.

Key changes from Zen+

- 7 nm process (from 12 nm)

- I/O die utilizes 12 nm

- Core

- Higher IPC (AMD self-reported up to 15% IPC)

- Front-end

- Improved branch prediction unit

- Improved prefetcher

- Improved µOP cache tags

- Improved µOP cache

- Larger µOP cache (4096 entries, up from 2048)

- Increased dispatch bandwidth

- Improved branch prediction unit

- Back-end

- Increased retire bandwidth (??-wide, up from 8-wide)

- FPU

- 2x wider datapath (256-bit, up from 128-bit)

- 2x wider EUs (256-bit FMAs, up from 128-bit FMAs)

- 2x wider LSU (2x256-bit L/S, up from 128-bit)

- Improved DP vector mult. latency (3 cycles, down from 4)

- Integer

- Increased number of registers (180, up from 168)

- Additional AGU (3, up from 2)

- Larger scheduler (4x16 ALU + 1x28 AGU, up from 4x14 ALU + 2x14 AGU

- Larger Reorder Buffer (224, up from 192)

- Memory subsystem

- 0.5x L1 instruction cache (32 KiB, down from 64 KiB)

- 8-way associativity (from 4-way)

- 1.33 larger L2 DTLB (2048-entry, up from 1536)

- 48 entry store queue (was 44)

- CCX

- 2x L3 cache slice (16 MiB, up from 8 MiB)

- Increased L3 latency (~40 cycles, up from ~35 cycles)

- Security

- In-silicon Spectre enhancements

- Increase number of keys/VMs supported

- I/O

- PCIe 4.0 (from 3.0)

- Infinity Fabric 2

- 2.3x transfer rate per link (25 GT/s, up from ~10.6 GT/s)

- Decoupling of MemClk from FClk, allowing 2:1 ratio in addition to 1:1

- DDR4-3200 support, up from DDR4-2933

This list is incomplete; you can help by expanding it.

New instructions

Zen 2 introduced a number of new x86 instructions:

-

CLWB- Write back modified cache line and may retain line in cache hierarchy -

WBNOINVD- Write back and do not flush internal caches, initiate same of external caches -

MCOMMIT- Commit stores to memory -

RDPID- Read Processor ID -

RDPRU- Read Processor Register

Block Diagram

Individual Core

Memory Hierarchy

- Cache

- L0 Op Cache:

- 4,096 Ops, 8-way set associative

- 64 sets, 8 Op line size

- Parity protected

- 4,096 Ops, 8-way set associative

- L1I Cache:

- 32 KiB, 8-way set associative

- 64 sets, 64 B line size

- Shared by the two threads, per core

- Parity protected

- 32 KiB, 8-way set associative

- L1D Cache:

- 32 KiB, 8-way set associative

- 64 sets, 64 B line size

- Write-back policy

- 4-5 cycles latency for Int

- 7-8 cycles latency for FP

- ECC

- 32 KiB, 8-way set associative

- L2 Cache:

- 512 KiB, 8-way set associative

- 1,024 sets, 64 B line size

- Write-back policy

- Inclusive of L1

- ≥ 12 cycles latency

- ECC

- 512 KiB, 8-way set associative

- L3 Cache:

- Matisse, Castle Peak, Rome: 16 MiB/CCX, shared across all cores

- TBD: 4 MiB/CCX, shared across all cores

- 16-way set associative

- 16,384 sets, 64 B line size

- Write-back policy, Victim cache

- 39 cycles average latency

- ECC

- QoS Monitoring and Enforcement

- L0 Op Cache:

- System DRAM

- Rome:

- 8 channels per socket, up to 16 DIMMs, max. 4 TiB

- Up to PC4-25600L (DDR4-3200 RDIMM/LRDIMM), ECC supported

- Castle Peak, sTRX4:

- 4 channels, up to 8 DIMMs, max. 256 GiB

- Up to PC4-25600U (DDR4-3200 UDIMM), ECC supported

- Matisse:

- 2 channels, up to 4 DIMMs, max. 128 GiB

- Up to PC4-25600U (DDR4-3200 UDIMM), ECC supported

- Rome:

Translation Lookaside Buffers

- ITLB

- 64 entry L1 TLB, fully associative, all page sizes

- 512 entry L2 TLB, 8-way set associative

- 4-Kbyte and 2-Mbyte pages

- Parity protected

- DTLB

- 64 entry L1 TLB, fully associative, all page sizes

- 2,048 entry L2 TLB, 16-way set associative

- 4-Kbyte and 2-Mbyte pages, PDEs to speed up table walks

- Parity protected

Core

Zen 2 largely builds on Zen. Most of the fine details have not been revealed by AMD yet.

Front End

In order to feed the backend, which has been widened to support 256-bit operation, the front-end throughput was improved. AMD reported that the branch prediction unit has been reworked. This includes improvements to the prefetcher and various undisclosed optimizations to the instruction cache. The µOP cache was also tweaked including changes to the µOP cache tags and the µOP cache itself which has been enlarged to improve the instruction stream throughput.

Execution Engine

AMD stated that both the dispatch bandwidth and the retire bandwidth has been increased.

Floating Point Unit

Like the Zen/Zen+ microarchitecture, the Zen 2 floating point unit utilizes a coprocessor architectural model comprising a dedicated rename unit, a single 4-issue, out-of-order scheduler, a 160-entry physical register file (PRF), and four execution pipelines. The in-order retire queue is shared with the integer unit. The FPU handles x87, MMX, SSE, and AVX instructions. FP loads and stores co-opt the EX unit for address calculations and the LS unit for memory accesses.

In the Zen/Zen+ microarchitecture the floating point physical registers, execution units, and data paths are 128 bits wide. For efficiency AVX-256 instructions which perform the same operation on the 128-bit upper and lower half of a YMM register are decoded into two macro-ops which pass through the FPU individually as execution resources become available and retire together. Accordingly the peak throughput is four SSE/AVX-128 instructions or two AVX-256 instructions per cycle.

Zen 2 doubles the width of the physical registers, execution units, and data paths to 256 bits. The L1 data cache bandwidth was doubled to match. The number of micro-ops issued by the FP scheduler remains four, implying most AVX-256 instructions decode to a single macro-op which conserves queue entries and reduces pressure on RCU and scheduling resources. AMD did not disclose how the FPU was restructured. Die shots suggest two execution blocks splitting the PRF and FP ALUs, one operating on the lower 128 bits of a YMM register, executing x87, MMX, SSE, and AVX instructions, the other on the upper 128 bits for AVX-256 instructions. This improvement doubles the peak throughput of AVX-256 instructions to four per cycle, or in other words, up to 32 FLOPs/cycle in single precision or up to 16 FLOPs/cycle in double precision. Another improvement reduces the latency of double-precision vector multiplications from 4 to 3 cycles, equal to the latency of single-precision multiplications. The latency of fused multiply-add (FMA) instructions remains 5 cycles.

The rename unit receives up to four macro-ops per cycle from dispatch. It maps x87, MMX, SSE, and AVX architectural registers and temporary registers used by microcoded instructions to physical registers. MMX and x87 registers occupy the lowest 64 or 80 bits of a PR. The Zen/Zen+ rename unit allocates two 128-bit PRs for each YMM register. Only one PR is needed for SSE and AVX-128 instructions, the upper half of the destination YMM register in another PR remains unchanged or is zeroed, respectively, which consumes no execution resources. (SSE instructions behave this way for compatibility with legacy software which is unaware of, and does not preserve, the upper half of YMM registers through library calls or interrupts.) Zen 2 allocates a single 256-bit PR and tracks in the register allocation table (RAT) if the upper half of the YMM register was zeroed. This necessitates register merging when SSE and AVX instructions are mixed and the upper half of the YMM register contains non-zero data. To avoid this the AVX ISA exposes an SSE mode where the FPU maintains the upper half of YMM registers separately. Zen 2 handles transitions between the SSE and AVX mode by microcode which takes approximately 100 cycles in either direction. Zeroing the upper half of all YMM registers with the VZEROUPPER or VZEROALL instruction before executing SSE instructions prevents the transition.

Zen 2 inherits the move elimination and XMM register merge optimizations from its predecessors. Register to register moves are performed by renaming the source register and do not occupy any scheduling or execution resources. XMM register merging occurs when SSE instructions such as SQRTSS leave the upper 64 or 96 bits of the destination register unchanged, causing a dependency on previous instructions writing to this register. AMD family 15h and later processors can eliminate this dependency in a sequence of scalar FP instructions by recording in the RAT if those bits were zeroed. By setting a Z-bit in the RAT the rename unit also tracks if an architectural register was completely zeroed. All-zero registers are not mapped, the zero data bits are injected at the bypass network which conserves power and PRF entries, and allows for more instructions in flight. Earlier AMD microarchitectures, apparently including Zen/Zen+, recognize zeroing idioms such as XORPS combining a register with itself and eliminate the dependency on the source register. AMD did not disclose if or how this is implemented in Zen 2. Family 16h processors recognize zeroing idioms in the instruction decode unit and set the Z-bit on the destination register in the floating point rename unit, completing the operation without consuming scheduling or execution resources.

As in the Zen/Zen+ microarchitecture the 64-entry non-scheduling queue decouples dispatch and the FP scheduler. This allows dispatch to send operations to the integer side, in particular to expedite floating point loads and store address calculations, while the FP scheduler, whose capacity cannot be arbitrarily increased for complexity reasons, is busy with higher latency FP operations. The 36-entry out-of-order scheduler issues up to four micro-ops per cycle to the execution pipelines. A 160-entry physical register file holds the speculative and committed contents of architectural and temporary registers. The PRF has 8 read ports and 4 write ports for ALU results, each 256 bits wide in Zen 2, and two additional write ports supporting up to two 256-bit load operations per cycle, up from two 128-bit loads in Zen. The FPU is capable of superforwarding load data to dependent instructions through the bypass network, obviating a write and read of the PRF. The bypass network enables back-to-back execution of dependent instructions by forwarding results from the FP ALUs to the previous pipeline stage.

The floating point pipelines are asymmetric, each supporting a different set of operations, and the ALUs are grouped in domains, to conserve die space and reduce signal path lengths which permits higher clock frequencies. The number of execution resources available reflects the density of different instruction types in x86 code. Each pipe receives two operands from the PRF or bypass network. Pipe 0 and 1 support FMA instructions which take three operands; The third operand is obtained by borrowing a PRF read port from pipe 3, stalling this pipe for one cycle, unless the operand is available on the bypass network. All pipes can perform logical operations. Other operations are supported by one, two, or three pipes. The execution domains distinguish vector integer operations, floating point operations, and store operations. Instructions consuming data produced in another domain incur a one cycle penalty. Only pipe 2 executes floating point store-data micro-ops, sending data to the store queue at a rate of up to one 256-bit store per cycle, up from one 128-bit store in Zen. It also takes care of transfers between integer and FP registers on dedicated data busses.

Same as Zen/Zen+ the Zen 2 FPU handles denormal floating-point values natively, this can still incur a small penalty in some instances (MUL/DIV/SQRT).

Load-Store Unit

The load-store unit handles memory reads and writes. The width of data paths and buffers doubled from 128 bits in the Zen/Zen+ microarchitecture to 256 bits.

The LS unit contains a 44-entry load queue (LDQ) which receives load operations from dispatch through either of the two load AGUs in the EX unit and the linear address of the load computed there. A load op stays in the LDQ until the load completes or a fault occurs. Adding the AGQ depth of 28 entries, dispatch can issue up to 72 load operations at a time. A 48-entry store queue (STQ), up from 44 entries in Zen, receives store operations from dispatch, a linear address computed by any of the three AGUs, and store data from the integer or floating point execution units. A store op likewise stays in the STQ until the store is committed or a fault occurs. Loads and stores are speculative due to branch prediction.

Three largely independent pipelines can execute up to two 256-bit load operations and one 256-bit store per cycle. The load pipes translate linear to physical addresses in parallel with L1 data cache accesses. The LS unit can perform loads and stores out of order. It supports loads bypassing older loads and loads bypassing older non-conflicting stores, observing architectural load and store ordering rules. Store-to-load forwarding is supported when an older store containing all of the load's bytes, with no particular alignment since the Piledriver microarchitecture, is in the STQ and store data has been produced. Memory dependence prediction, to speculatively reorder loads and stores before the physical address has been determined, was introduced by AMD in the Bulldozer microarchitecture.

A two-level translation lookaside buffer (TLB) assists load and store address translation. The fully-associative L1 data TLB contains 64 entries and holds 4-Kbyte, 2-Mbyte, and 1-Gbyte page table entries. The L2 data TLB is a unified 12-way set-associative cache with 2048 entries, up from 1536 entries in Zen, holding 4-Kbyte and 2-Mbyte page table entries, as well as page directory entries (PDEs) to speed up DTLB and ITLB table walks. 1-Gbyte pages are smashed into 2-Mbyte entries but installed as 1-Gbyte entries when reloaded into the L1 TLB.

Two hardware page table walkers handle L2 TLB misses, presumably one serving the DTLB, another the ITLB. In addition to the PDE entries, the table walkers include a 64-entry page directory cache which holds page-map-level-4 and page-directory-pointer entries speeding up DTLB and ITLB walks. The Zen/Zen+ microarchitecture supports page table entry (PTE) coalescing; this feature is probably also present in Zen 2. When the table walker loads a PTE, which occupies 8 bytes in the x86-64 architecture, from memory it also examines the seven other PTEs in the same 64-byte cache line. If they assign a contiguous 32 KiB block of physical pages with the same attributes to the 8 virtual pages, they are coalesced into a single TLB entry greatly improving the efficiency of this cache.

The LS unit relies on a 32 KiB, 8-way set associative, write-back, ECC-protected L1 data cache (DC). It supports two loads, if they access different DC banks, and one store per cycle, each up to 256 bits wide. The line width is 64 bytes, however cache stores are aligned to a 32-byte boundary. Loads spanning a 64-byte boundary and stores spanning a 32-byte boundary incur a penalty of one cycle. In the Zen/Zen+ microarchitecture 256-bit vectors are loaded and stored as two 128-bit halves; the load and store boundaries are 32 and 16 bytes respectively. Zen 2 can load and store 256-bit vectors in a single operation, but stores must be 32-byte aligned now to avoid the penalty. As in Zen aligned and unaligned load and store instructions (for example MOVUPS/MOVAPS) provide identical performance.

The DC load-to-use latency is 4 cycles to the integer unit, 7 cycles to the FPU. The AGUs and LS unit are optimized for simple address generation modes: Base + displacement, base + index, and displacement-only. More complex modes and/or a non-zero segment base increase the latency by one cycle.

The L1 DC tags contain a linear-address-based microtag which allows loads to predict the way holding the requested data before the physical address has been determined, reducing power consumption and bank conflicts. A hardware prefetcher brings data into the L1 DC to reduce misses. The LS unit can track up to 22 in-flight cache misses, these are recorded in the miss address buffer (MAB).

The LS unit supports memory type range register (MTRR) and the page attribute table (PAT) extensions. Write-combining, if enabled for a memory range, merges multiple stores targeting locations within the address range of a write buffer to reduce memory bus utilization. Write-combining is also used for non-temporal store instructions such as MOVNTI. The LS unit can gather writes from 8 different 64-byte cache lines.

Each core benefits from a private 512 KiB, 8-way set associative, write-back, ECC-protected L2 cache. The line width is 64 bytes. The data path between the L1 data or instruction cache and the L2 cache is 32 bytes wide. The L2 cache has a variable load-to-use latency of no less than 12 cycles.

Rome

Rome is codename for AMD's server chip based on the Zen 2 core. Like prior generation (Naples), Rome utilizes a chiplet multi-chip package design. Each chip comprises of nine dies - one centralized I/O die and eight compute dies. The compute dies are fabricated on TSMC's 7 nm process in order to take advantage of the lower power and higher density. On the other hand, the I/O makes use of GlobalFoundries mature 14 nm process.

The centralized I/O die incorporates eight Infinity Fabric links, 128 PCIe Gen 4 lanes, and eight DDR4 memory channels. The full capabilities of the I/O have not been disclosed yet. Attached to the I/O die are eight compute dies - each with eight Zen 2 core - for a total of 64 cores and 128 threads per chip.

All Zen 2 Chips

| List of all Zen-based Processors | |||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Processor | Features | ||||||||||||||||||||||||

| Model | Price | Process | Launched | Family | Core | C | T | TDP | L3 | Base | Turbo | Max Mem | SMT | SEV | SME | TSME | |||||||||

| Uniprocessors | |||||||||||||||||||||||||

| 7232P | $ 450.00 € 405.00 £ 364.50 ¥ 46,498.50 | 7 nm 0.007 μm , 14 nm7.0e-6 mm 0.014 μm 1.4e-5 mm | 7 August 2019 | EPYC | Rome | 8 | 16 | 120 W 120,000 mW 0.161 hp 0.12 kW | 32 MiB 32,768 KiB 33,554,432 B 0.0313 GiB | 3.1 GHz 3,100 MHz 3,100,000 kHz | 3.2 GHz 3,200 MHz 3,200,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | |||||||||

| 7302P | $ 825.00 € 742.50 £ 668.25 ¥ 85,247.25 | 7 nm 0.007 μm , 14 nm7.0e-6 mm 0.014 μm 1.4e-5 mm | 7 August 2019 | EPYC | Rome | 16 | 32 | 155 W 155,000 mW 0.208 hp 0.155 kW | 128 MiB 131,072 KiB 134,217,728 B 0.125 GiB | 3 GHz 3,000 MHz 3,000,000 kHz | 3.3 GHz 3,300 MHz 3,300,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | |||||||||

| 7402P | $ 1,250.00 € 1,125.00 £ 1,012.50 ¥ 129,162.50 | 7 nm 0.007 μm , 14 nm7.0e-6 mm 0.014 μm 1.4e-5 mm | 7 August 2019 | EPYC | Rome | 24 | 48 | 180 W 180,000 mW 0.241 hp 0.18 kW | 128 MiB 131,072 KiB 134,217,728 B 0.125 GiB | 2.8 GHz 2,800 MHz 2,800,000 kHz | 3.35 GHz 3,350 MHz 3,350,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | |||||||||

| 7502P | $ 2,300.00 € 2,070.00 £ 1,863.00 ¥ 237,659.00 | 7 nm 0.007 μm , 14 nm7.0e-6 mm 0.014 μm 1.4e-5 mm | 7 August 2019 | EPYC | Rome | 32 | 64 | 180 W 180,000 mW 0.241 hp 0.18 kW | 128 MiB 131,072 KiB 134,217,728 B 0.125 GiB | 2.5 GHz 2,500 MHz 2,500,000 kHz | 3.35 GHz 3,350 MHz 3,350,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | |||||||||

| 7702P | $ 4,425.00 € 3,982.50 £ 3,584.25 ¥ 457,235.25 | 7 nm 0.007 μm , 14 nm7.0e-6 mm 0.014 μm 1.4e-5 mm | 7 August 2019 | EPYC | Rome | 64 | 128 | 200 W 200,000 mW 0.268 hp 0.2 kW | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 2 GHz 2,000 MHz 2,000,000 kHz | 3.35 GHz 3,350 MHz 3,350,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | |||||||||

| 4300G | 7 nm 0.007 μm 7.0e-6 mm | 21 July 2020 | Ryzen 3 | Renoir | 4 | 8 | 65 W 65,000 mW 0.0872 hp 0.065 kW | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 3.8 GHz 3,800 MHz 3,800,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✔ | ✘ | ✘ | ✘ | ||||||||||

| 4300GE | 7 nm 0.007 μm 7.0e-6 mm | 21 July 2020 | Ryzen 3 | Renoir | 4 | 8 | 35 W 35,000 mW 0.0469 hp 0.035 kW | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 3.5 GHz 3,500 MHz 3,500,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✔ | ✘ | ✘ | ✘ | ||||||||||

| 4300U | 7 nm 0.007 μm 7.0e-6 mm | 6 January 2020 | Ryzen 3 | Renoir | 4 | 4 | 15 W 15,000 mW 0.0201 hp 0.015 kW | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 2.7 GHz 2,700 MHz 2,700,000 kHz | 3.7 GHz 3,700 MHz 3,700,000 kHz | 64 GiB 65,536 MiB 67,108,864 KiB 68,719,476,736 B 0.0625 TiB | ✘ | ✘ | ✘ | ✘ | ||||||||||

| 5300U | 7 nm 0.007 μm 7.0e-6 mm | 12 January 2021 | Ryzen 3 | Lucienne | 4 | 8 | 15 W 15,000 mW 0.0201 hp 0.015 kW | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 2.6 GHz 2,600 MHz 2,600,000 kHz | 3.8 GHz 3,800 MHz 3,800,000 kHz | 64 GiB 65,536 MiB 67,108,864 KiB 68,719,476,736 B 0.0625 TiB | ✔ | ✘ | ✘ | ✘ | ||||||||||

| PRO 4350G | 7 nm 0.007 μm 7.0e-6 mm | 21 July 2020 | Ryzen 3 | Renoir | 4 | 8 | 65 W 65,000 mW 0.0872 hp 0.065 kW | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 3.8 GHz 3,800 MHz 3,800,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✔ | ✘ | ✘ | ✔ | ||||||||||

| PRO 4350GE | 7 nm 0.007 μm 7.0e-6 mm | 21 July 2020 | Ryzen 3 | Renoir | 4 | 8 | 35 W 35,000 mW 0.0469 hp 0.035 kW | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 3.5 GHz 3,500 MHz 3,500,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✔ | ✘ | ✘ | ✔ | ||||||||||

| PRO 4450U | 7 nm 0.007 μm 7.0e-6 mm | 7 May 2020 | Ryzen 3 | Renoir | 4 | 8 | 15 W 15,000 mW 0.0201 hp 0.015 kW | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 2.5 GHz 2,500 MHz 2,500,000 kHz | 3.7 GHz 3,700 MHz 3,700,000 kHz | 64 GiB 65,536 MiB 67,108,864 KiB 68,719,476,736 B 0.0625 TiB | ✔ | ✘ | ✘ | ✔ | ||||||||||

| 3500 | 7 nm 0.007 μm , 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | Ryzen 5 | Matisse | 6 | 6 | 65 W 65,000 mW 0.0872 hp 0.065 kW | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 3.6 GHz 3,600 MHz 3,600,000 kHz | 4.1 GHz 4,100 MHz 4,100,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✘ | ✘ | ✘ | ✘ | |||||||||||

| 3500X | 7 nm 0.007 μm , 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | Ryzen 5 | Matisse | 6 | 6 | 65 W 65,000 mW 0.0872 hp 0.065 kW | 32 MiB 32,768 KiB 33,554,432 B 0.0313 GiB | 3.6 GHz 3,600 MHz 3,600,000 kHz | 4.1 GHz 4,100 MHz 4,100,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✘ | ✘ | ✘ | ✘ | |||||||||||

| 3600 | $ 199.00 € 179.10 £ 161.19 ¥ 20,562.67 | 7 nm 0.007 μm , 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | 7 July 2019 | Ryzen 5 | Matisse | 6 | 12 | 65 W 65,000 mW 0.0872 hp 0.065 kW | 32 MiB 32,768 KiB 33,554,432 B 0.0313 GiB | 3.6 GHz 3,600 MHz 3,600,000 kHz | 4.2 GHz 4,200 MHz 4,200,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✔ | ✘ | ✘ | ✘ | |||||||||

| 3600X | $ 249.00 € 224.10 £ 201.69 ¥ 25,729.17 | 7 nm 0.007 μm , 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | 7 July 2019 | Ryzen 5 | Matisse | 6 | 12 | 95 W 95,000 mW 0.127 hp 0.095 kW | 32 MiB 32,768 KiB 33,554,432 B 0.0313 GiB | 3.8 GHz 3,800 MHz 3,800,000 kHz | 4.4 GHz 4,400 MHz 4,400,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✔ | ✘ | ✘ | ✘ | |||||||||

| 3600XT | $ 249.00 € 224.10 £ 201.69 ¥ 25,729.17 | 7 nm 0.007 μm , 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | 7 July 2020 | Ryzen 5 | Matisse | 6 | 12 | 95 W 95,000 mW 0.127 hp 0.095 kW | 32 MiB 32,768 KiB 33,554,432 B 0.0313 GiB | 3.8 GHz 3,800 MHz 3,800,000 kHz | 4.5 GHz 4,500 MHz 4,500,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✔ | ✘ | ✘ | ✘ | |||||||||

| 4500U | 7 nm 0.007 μm 7.0e-6 mm | 6 January 2020 | Ryzen 5 | Renoir | 6 | 6 | 15 W 15,000 mW 0.0201 hp 0.015 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 2.3 GHz 2,300 MHz 2,300,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 64 GiB 65,536 MiB 67,108,864 KiB 68,719,476,736 B 0.0625 TiB | ✘ | ✘ | ✘ | ✘ | ||||||||||

| 4600G | 7 nm 0.007 μm 7.0e-6 mm | 21 July 2020 | Ryzen 5 | Renoir | 6 | 12 | 65 W 65,000 mW 0.0872 hp 0.065 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 3.7 GHz 3,700 MHz 3,700,000 kHz | 4.2 GHz 4,200 MHz 4,200,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✔ | ✘ | ✘ | ✘ | ||||||||||

| 4600GE | 7 nm 0.007 μm 7.0e-6 mm | 21 July 2020 | Ryzen 5 | Renoir | 6 | 12 | 35 W 35,000 mW 0.0469 hp 0.035 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 3.3 GHz 3,300 MHz 3,300,000 kHz | 4.2 GHz 4,200 MHz 4,200,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✔ | ✘ | ✘ | ✘ | ||||||||||

| 4600H | 7 nm 0.007 μm 7.0e-6 mm | 6 January 2020 | Ryzen 5 | Renoir | 6 | 12 | 45 W 45,000 mW 0.0603 hp 0.045 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 3 GHz 3,000 MHz 3,000,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 64 GiB 65,536 MiB 67,108,864 KiB 68,719,476,736 B 0.0625 TiB | ✔ | ✘ | ✘ | ✘ | ||||||||||

| 4600HS | 7 nm 0.007 μm 7.0e-6 mm | 16 March 2020 | Ryzen 5 | Renoir | 6 | 12 | 35 W 35,000 mW 0.0469 hp 0.035 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 3 GHz 3,000 MHz 3,000,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 64 GiB 65,536 MiB 67,108,864 KiB 68,719,476,736 B 0.0625 TiB | ✔ | ✘ | ✘ | ✘ | ||||||||||

| 4600U | 7 nm 0.007 μm 7.0e-6 mm | 6 January 2020 | Ryzen 5 | Renoir | 6 | 12 | 15 W 15,000 mW 0.0201 hp 0.015 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 2.1 GHz 2,100 MHz 2,100,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 64 GiB 65,536 MiB 67,108,864 KiB 68,719,476,736 B 0.0625 TiB | ✔ | ✘ | ✘ | ✘ | ||||||||||

| 4680U | 7 nm 0.007 μm 7.0e-6 mm | 13 April 2021 | Ryzen 5 | Renoir | 6 | 12 | 15 W 15,000 mW 0.0201 hp 0.015 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 2.1 GHz 2,100 MHz 2,100,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 64 GiB 65,536 MiB 67,108,864 KiB 68,719,476,736 B 0.0625 TiB | ✔ | ✘ | ✘ | ✘ | ||||||||||

| 5500U | 7 nm 0.007 μm 7.0e-6 mm | 12 January 2021 | Ryzen 5 | Lucienne | 6 | 12 | 15 W 15,000 mW 0.0201 hp 0.015 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 2.1 GHz 2,100 MHz 2,100,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 64 GiB 65,536 MiB 67,108,864 KiB 68,719,476,736 B 0.0625 TiB | ✔ | ✘ | ✘ | ✘ | ||||||||||

| PRO 3600 | 7 nm 0.007 μm , 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | 30 September 2019 | Ryzen 5 | Matisse | 6 | 12 | 65 W 65,000 mW 0.0872 hp 0.065 kW | 32 MiB 32,768 KiB 33,554,432 B 0.0313 GiB | 3.6 GHz 3,600 MHz 3,600,000 kHz | 4.2 GHz 4,200 MHz 4,200,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✔ | ✘ | ✘ | ✔ | ||||||||||

| PRO 4650G | 7 nm 0.007 μm 7.0e-6 mm | 21 July 2020 | Ryzen 5 | Renoir | 6 | 12 | 65 W 65,000 mW 0.0872 hp 0.065 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 3.7 GHz 3,700 MHz 3,700,000 kHz | 4.2 GHz 4,200 MHz 4,200,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✔ | ✘ | ✘ | ✔ | ||||||||||

| PRO 4650GE | 7 nm 0.007 μm 7.0e-6 mm | 21 July 2020 | Ryzen 5 | Renoir | 6 | 12 | 35 W 35,000 mW 0.0469 hp 0.035 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 3.3 GHz 3,300 MHz 3,300,000 kHz | 4.2 GHz 4,200 MHz 4,200,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✔ | ✘ | ✘ | ✔ | ||||||||||

| PRO 4650U | 7 nm 0.007 μm 7.0e-6 mm | 7 May 2020 | Ryzen 5 | Renoir | 6 | 12 | 15 W 15,000 mW 0.0201 hp 0.015 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 2.1 GHz 2,100 MHz 2,100,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 64 GiB 65,536 MiB 67,108,864 KiB 68,719,476,736 B 0.0625 TiB | ✔ | ✘ | ✘ | ✔ | ||||||||||

| 3700X | $ 329.00 € 296.10 £ 266.49 ¥ 33,995.57 | 7 nm 0.007 μm , 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | 7 July 2019 | Ryzen 7 | Matisse | 8 | 16 | 65 W 65,000 mW 0.0872 hp 0.065 kW | 32 MiB 32,768 KiB 33,554,432 B 0.0313 GiB | 3.6 GHz 3,600 MHz 3,600,000 kHz | 4.4 GHz 4,400 MHz 4,400,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✔ | ✘ | ✘ | ✘ | |||||||||

| 3800X | $ 399.00 € 359.10 £ 323.19 ¥ 41,228.67 | 7 nm 0.007 μm , 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | 7 July 2019 | Ryzen 7 | Matisse | 8 | 16 | 105 W 105,000 mW 0.141 hp 0.105 kW | 32 MiB 32,768 KiB 33,554,432 B 0.0313 GiB | 3.9 GHz 3,900 MHz 3,900,000 kHz | 4.5 GHz 4,500 MHz 4,500,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✔ | ✘ | ✘ | ✘ | |||||||||

| 3800XT | $ 399.00 € 359.10 £ 323.19 ¥ 41,228.67 | 7 nm 0.007 μm , 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | 7 July 2020 | Ryzen 7 | Matisse | 8 | 16 | 105 W 105,000 mW 0.141 hp 0.105 kW | 32 MiB 32,768 KiB 33,554,432 B 0.0313 GiB | 3.9 GHz 3,900 MHz 3,900,000 kHz | 4.7 GHz 4,700 MHz 4,700,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✔ | ✘ | ✘ | ✘ | |||||||||

| 4700G | 7 nm 0.007 μm 7.0e-6 mm | 21 July 2020 | Ryzen 7 | Renoir | 8 | 16 | 65 W 65,000 mW 0.0872 hp 0.065 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 3.6 GHz 3,600 MHz 3,600,000 kHz | 4.4 GHz 4,400 MHz 4,400,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✔ | ✘ | ✘ | ✘ | ||||||||||

| 4700GE | 7 nm 0.007 μm 7.0e-6 mm | 21 July 2020 | Ryzen 7 | Renoir | 8 | 16 | 35 W 35,000 mW 0.0469 hp 0.035 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 3.1 GHz 3,100 MHz 3,100,000 kHz | 4.3 GHz 4,300 MHz 4,300,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✔ | ✘ | ✘ | ✘ | ||||||||||

| 4700U | 7 nm 0.007 μm 7.0e-6 mm | 6 January 2020 | Ryzen 7 | Renoir | 8 | 8 | 15 W 15,000 mW 0.0201 hp 0.015 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 2 GHz 2,000 MHz 2,000,000 kHz | 4.1 GHz 4,100 MHz 4,100,000 kHz | 64 GiB 65,536 MiB 67,108,864 KiB 68,719,476,736 B 0.0625 TiB | ✘ | ✘ | ✘ | ✘ | ||||||||||

| 4800H | 7 nm 0.007 μm 7.0e-6 mm | 6 January 2020 | Ryzen 7 | Renoir | 8 | 16 | 45 W 45,000 mW 0.0603 hp 0.045 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 2.9 GHz 2,900 MHz 2,900,000 kHz | 4.2 GHz 4,200 MHz 4,200,000 kHz | 64 GiB 65,536 MiB 67,108,864 KiB 68,719,476,736 B 0.0625 TiB | ✔ | ✘ | ✘ | ✘ | ||||||||||

| 4800HS | 7 nm 0.007 μm 7.0e-6 mm | 16 March 2020 | Ryzen 7 | Renoir | 8 | 16 | 35 W 35,000 mW 0.0469 hp 0.035 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 2.9 GHz 2,900 MHz 2,900,000 kHz | 4.2 GHz 4,200 MHz 4,200,000 kHz | 64 GiB 65,536 MiB 67,108,864 KiB 68,719,476,736 B 0.0625 TiB | ✔ | ✘ | ✘ | ✘ | ||||||||||

| 4800U | 7 nm 0.007 μm 7.0e-6 mm | 6 January 2020 | Ryzen 7 | Renoir | 8 | 16 | 15 W 15,000 mW 0.0201 hp 0.015 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 1.8 GHz 1,800 MHz 1,800,000 kHz | 4.2 GHz 4,200 MHz 4,200,000 kHz | 64 GiB 65,536 MiB 67,108,864 KiB 68,719,476,736 B 0.0625 TiB | ✔ | ✘ | ✘ | ✘ | ||||||||||

| 4980U | 7 nm 0.007 μm 7.0e-6 mm | 13 April 2021 | Ryzen 7 | Renoir | 8 | 16 | 15 W 15,000 mW 0.0201 hp 0.015 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 2 GHz 2,000 MHz 2,000,000 kHz | 4.4 GHz 4,400 MHz 4,400,000 kHz | 64 GiB 65,536 MiB 67,108,864 KiB 68,719,476,736 B 0.0625 TiB | ✔ | ✘ | ✘ | ✘ | ||||||||||

| 5700U | 7 nm 0.007 μm 7.0e-6 mm | 12 January 2021 | Ryzen 7 | Lucienne | 8 | 16 | 15 W 15,000 mW 0.0201 hp 0.015 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 1.8 GHz 1,800 MHz 1,800,000 kHz | 4.3 GHz 4,300 MHz 4,300,000 kHz | 64 GiB 65,536 MiB 67,108,864 KiB 68,719,476,736 B 0.0625 TiB | ✔ | ✘ | ✘ | ✘ | ||||||||||

| PRO 3700 | 7 nm 0.007 μm , 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | 30 September 2019 | Ryzen 7 | Matisse | 8 | 16 | 65 W 65,000 mW 0.0872 hp 0.065 kW | 32 MiB 32,768 KiB 33,554,432 B 0.0313 GiB | 3.6 GHz 3,600 MHz 3,600,000 kHz | 4.4 GHz 4,400 MHz 4,400,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✔ | ✘ | ✘ | ✔ | ||||||||||

| PRO 4750G | 7 nm 0.007 μm 7.0e-6 mm | 21 July 2020 | Ryzen 7 | Renoir | 8 | 16 | 65 W 65,000 mW 0.0872 hp 0.065 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 3.6 GHz 3,600 MHz 3,600,000 kHz | 4.4 GHz 4,400 MHz 4,400,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✔ | ✘ | ✘ | ✔ | ||||||||||

| PRO 4750GE | 7 nm 0.007 μm 7.0e-6 mm | 21 July 2020 | Ryzen 7 | Renoir | 8 | 16 | 35 W 35,000 mW 0.0469 hp 0.035 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 3.1 GHz 3,100 MHz 3,100,000 kHz | 4.3 GHz 4,300 MHz 4,300,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✔ | ✘ | ✘ | ✔ | ||||||||||

| PRO 4750U | 7 nm 0.007 μm 7.0e-6 mm | 7 May 2020 | Ryzen 7 | Renoir | 8 | 16 | 15 W 15,000 mW 0.0201 hp 0.015 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 1.7 GHz 1,700 MHz 1,700,000 kHz | 4.1 GHz 4,100 MHz 4,100,000 kHz | 64 GiB 65,536 MiB 67,108,864 KiB 68,719,476,736 B 0.0625 TiB | ✔ | ✘ | ✘ | ✔ | ||||||||||

| 3900 | 7 nm 0.007 μm , 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | 24 September 2019 | Ryzen 9 | Matisse | 12 | 24 | 65 W 65,000 mW 0.0872 hp 0.065 kW | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 3.1 GHz 3,100 MHz 3,100,000 kHz | 4.3 GHz 4,300 MHz 4,300,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✔ | ✘ | ✘ | ✘ | ||||||||||

| 3900X | $ 499.00 € 449.10 £ 404.19 ¥ 51,561.67 | 7 nm 0.007 μm , 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | 7 July 2019 | Ryzen 9 | Matisse | 12 | 24 | 105 W 105,000 mW 0.141 hp 0.105 kW | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 3.8 GHz 3,800 MHz 3,800,000 kHz | 4.6 GHz 4,600 MHz 4,600,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✔ | ✘ | ✘ | ✘ | |||||||||

| 3900XT | $ 499.00 € 449.10 £ 404.19 ¥ 51,561.67 | 7 nm 0.007 μm , 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | 7 July 2020 | Ryzen 9 | Matisse | 12 | 24 | 105 W 105,000 mW 0.141 hp 0.105 kW | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 3.8 GHz 3,800 MHz 3,800,000 kHz | 4.7 GHz 4,700 MHz 4,700,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✔ | ✘ | ✘ | ✘ | |||||||||

| 3950X | $ 749.00 € 674.10 £ 606.69 ¥ 77,394.17 | 7 nm 0.007 μm , 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | 25 November 2019 | Ryzen 9 | Matisse | 16 | 32 | 105 W 105,000 mW 0.141 hp 0.105 kW | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 3.5 GHz 3,500 MHz 3,500,000 kHz | 4.7 GHz 4,700 MHz 4,700,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✔ | ✘ | ✘ | ✘ | |||||||||

| 4900H | 7 nm 0.007 μm 7.0e-6 mm | 16 March 2020 | Ryzen 9 | Renoir | 8 | 16 | 45 W 45,000 mW 0.0603 hp 0.045 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 3.3 GHz 3,300 MHz 3,300,000 kHz | 4.4 GHz 4,400 MHz 4,400,000 kHz | 64 GiB 65,536 MiB 67,108,864 KiB 68,719,476,736 B 0.0625 TiB | ✔ | ✘ | ✘ | ✘ | ||||||||||

| 4900HS | 7 nm 0.007 μm 7.0e-6 mm | 16 March 2020 | Ryzen 9 | Renoir | 8 | 16 | 35 W 35,000 mW 0.0469 hp 0.035 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 3 GHz 3,000 MHz 3,000,000 kHz | 4.3 GHz 4,300 MHz 4,300,000 kHz | 64 GiB 65,536 MiB 67,108,864 KiB 68,719,476,736 B 0.0625 TiB | ✔ | ✘ | ✘ | ✘ | ||||||||||

| PRO 3900 | 7 nm 0.007 μm , 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | 30 September 2019 | Ryzen 9 | Matisse | 12 | 24 | 65 W 65,000 mW 0.0872 hp 0.065 kW | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 3.1 GHz 3,100 MHz 3,100,000 kHz | 4.3 GHz 4,300 MHz 4,300,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✔ | ✘ | ✘ | ✔ | ||||||||||

| V2516 | 7 nm 0.007 μm 7.0e-6 mm | 10 November 2020 | Ryzen Embedded | Grey Hawk | 6 | 12 | 15 W 15,000 mW 0.0201 hp 0.015 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 2.1 GHz 2,100 MHz 2,100,000 kHz | 64 GiB 65,536 MiB 67,108,864 KiB 68,719,476,736 B 0.0625 TiB | ✔ | ✘ | ✔ | ✘ | |||||||||||

| V2546 | 7 nm 0.007 μm 7.0e-6 mm | 10 November 2020 | Ryzen Embedded | Grey Hawk | 6 | 12 | 45 W 45,000 mW 0.0603 hp 0.045 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 3 GHz 3,000 MHz 3,000,000 kHz | 64 GiB 65,536 MiB 67,108,864 KiB 68,719,476,736 B 0.0625 TiB | ✔ | ✘ | ✔ | ✘ | |||||||||||

| V2718 | 7 nm 0.007 μm 7.0e-6 mm | 10 November 2020 | Ryzen Embedded | Grey Hawk | 8 | 16 | 15 W 15,000 mW 0.0201 hp 0.015 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 1.7 GHz 1,700 MHz 1,700,000 kHz | 64 GiB 65,536 MiB 67,108,864 KiB 68,719,476,736 B 0.0625 TiB | ✔ | ✘ | ✔ | ✘ | |||||||||||

| V2748 | 7 nm 0.007 μm 7.0e-6 mm | 10 November 2020 | Ryzen Embedded | Grey Hawk | 8 | 16 | 45 W 45,000 mW 0.0603 hp 0.045 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 2.9 GHz 2,900 MHz 2,900,000 kHz | 64 GiB 65,536 MiB 67,108,864 KiB 68,719,476,736 B 0.0625 TiB | ✔ | ✘ | ✔ | ✘ | |||||||||||

| 3960X | $ 1,399.00 € 1,259.10 £ 1,133.19 ¥ 144,558.67 | 7 nm 0.007 μm , 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | 25 November 2019 | Ryzen Threadripper | Castle Peak | 24 | 48 | 280 W 280,000 mW 0.375 hp 0.28 kW | 128 MiB 131,072 KiB 134,217,728 B 0.125 GiB | 3.8 GHz 3,800 MHz 3,800,000 kHz | 4.5 GHz 4,500 MHz 4,500,000 kHz | 256 GiB 262,144 MiB 268,435,456 KiB 274,877,906,944 B 0.25 TiB | ✔ | ✘ | ✘ | ✔ | |||||||||

| 3970X | $ 1,999.00 € 1,799.10 £ 1,619.19 ¥ 206,556.67 | 7 nm 0.007 μm , 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | 25 November 2019 | Ryzen Threadripper | Castle Peak | 32 | 64 | 280 W 280,000 mW 0.375 hp 0.28 kW | 128 MiB 131,072 KiB 134,217,728 B 0.125 GiB | 3.7 GHz 3,700 MHz 3,700,000 kHz | 4.5 GHz 4,500 MHz 4,500,000 kHz | 256 GiB 262,144 MiB 268,435,456 KiB 274,877,906,944 B 0.25 TiB | ✔ | ✘ | ✘ | ✔ | |||||||||

| 3980X | 7 nm 0.007 μm , 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | Ryzen Threadripper | Castle Peak | 48 | 96 | 280 W 280,000 mW 0.375 hp 0.28 kW | 3.2 GHz 3,200 MHz 3,200,000 kHz | 4.5 GHz 4,500 MHz 4,500,000 kHz | 512 GiB 524,288 MiB 536,870,912 KiB 549,755,813,888 B 0.5 TiB | ✔ | ✘ | ✘ | ✔ | ||||||||||||

| 3990X | $ 3,990.00 € 3,591.00 £ 3,231.90 ¥ 412,286.70 | 7 nm 0.007 μm , 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | 7 February 2020 | Ryzen Threadripper | Castle Peak | 64 | 128 | 280 W 280,000 mW 0.375 hp 0.28 kW | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 2.9 GHz 2,900 MHz 2,900,000 kHz | 4.3 GHz 4,300 MHz 4,300,000 kHz | 256 GiB 262,144 MiB 268,435,456 KiB 274,877,906,944 B 0.25 TiB | ✔ | ✘ | ✘ | ✔ | |||||||||

| PRO 3945WX | 7 nm 0.007 μm , 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | 14 July 2020 | Ryzen Threadripper | Castle Peak | 12 | 24 | 280 W 280,000 mW 0.375 hp 0.28 kW | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 4 GHz 4,000 MHz 4,000,000 kHz | 4.3 GHz 4,300 MHz 4,300,000 kHz | 2,048 GiB 2,097,152 MiB 2,147,483,648 KiB 2,199,023,255,552 B 2 TiB | ✔ | ✘ | ✘ | ✔ | ||||||||||

| PRO 3955WX | 7 nm 0.007 μm , 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | 14 July 2020 | Ryzen Threadripper | Castle Peak | 16 | 32 | 280 W 280,000 mW 0.375 hp 0.28 kW | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 3.9 GHz 3,900 MHz 3,900,000 kHz | 4.3 GHz 4,300 MHz 4,300,000 kHz | 2,048 GiB 2,097,152 MiB 2,147,483,648 KiB 2,199,023,255,552 B 2 TiB | ✔ | ✘ | ✘ | ✔ | ||||||||||

| PRO 3975WX | 7 nm 0.007 μm , 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | 14 July 2020 | Ryzen Threadripper | Castle Peak | 32 | 64 | 280 W 280,000 mW 0.375 hp 0.28 kW | 128 MiB 131,072 KiB 134,217,728 B 0.125 GiB | 3.5 GHz 3,500 MHz 3,500,000 kHz | 4.2 GHz 4,200 MHz 4,200,000 kHz | 2,048 GiB 2,097,152 MiB 2,147,483,648 KiB 2,199,023,255,552 B 2 TiB | ✔ | ✘ | ✘ | ✔ | ||||||||||

| PRO 3995WX | 7 nm 0.007 μm , 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | 14 July 2020 | Ryzen Threadripper | Castle Peak | 64 | 128 | 280 W 280,000 mW 0.375 hp 0.28 kW | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 2.7 GHz 2,700 MHz 2,700,000 kHz | 4.2 GHz 4,200 MHz 4,200,000 kHz | 2,048 GiB 2,097,152 MiB 2,147,483,648 KiB 2,199,023,255,552 B 2 TiB | ✔ | ✘ | ✘ | ✔ | ||||||||||

| Multiprocessors (dual-socket) | |||||||||||||||||||||||||

| 7252 | $ 475.00 € 427.50 £ 384.75 ¥ 49,081.75 | 7 nm 0.007 μm , 14 nm7.0e-6 mm 0.014 μm 1.4e-5 mm | 7 August 2019 | EPYC | Rome | 8 | 16 | 120 W 120,000 mW 0.161 hp 0.12 kW | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 3.1 GHz 3,100 MHz 3,100,000 kHz | 3.2 GHz 3,200 MHz 3,200,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | |||||||||

| 7262 | $ 575.00 € 517.50 £ 465.75 ¥ 59,414.75 | 7 nm 0.007 μm , 14 nm7.0e-6 mm 0.014 μm 1.4e-5 mm | 7 August 2019 | EPYC | Rome | 8 | 16 | 155 W 155,000 mW 0.208 hp 0.155 kW | 128 MiB 131,072 KiB 134,217,728 B 0.125 GiB | 3.2 GHz 3,200 MHz 3,200,000 kHz | 3.4 GHz 3,400 MHz 3,400,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | |||||||||

| 7272 | $ 625.00 € 562.50 £ 506.25 ¥ 64,581.25 | 7 nm 0.007 μm , 14 nm7.0e-6 mm 0.014 μm 1.4e-5 mm | 7 August 2019 | EPYC | Rome | 12 | 24 | 120 W 120,000 mW 0.161 hp 0.12 kW | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 2.9 GHz 2,900 MHz 2,900,000 kHz | 3.2 GHz 3,200 MHz 3,200,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | |||||||||

| 7282 | $ 650.00 € 585.00 £ 526.50 ¥ 67,164.50 | 7 nm 0.007 μm , 14 nm7.0e-6 mm 0.014 μm 1.4e-5 mm | 7 August 2019 | EPYC | Rome | 16 | 32 | 120 W 120,000 mW 0.161 hp 0.12 kW | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 2.8 GHz 2,800 MHz 2,800,000 kHz | 3.2 GHz 3,200 MHz 3,200,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | |||||||||

| 7302 | $ 978.00 € 880.20 £ 792.18 ¥ 101,056.74 | 7 nm 0.007 μm , 14 nm7.0e-6 mm 0.014 μm 1.4e-5 mm | 7 August 2019 | EPYC | Rome | 16 | 32 | 155 W 155,000 mW 0.208 hp 0.155 kW | 128 MiB 131,072 KiB 134,217,728 B 0.125 GiB | 3 GHz 3,000 MHz 3,000,000 kHz | 3.3 GHz 3,300 MHz 3,300,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | |||||||||

| 7352 | $ 1,350.00 € 1,215.00 £ 1,093.50 ¥ 139,495.50 | 7 nm 0.007 μm , 14 nm7.0e-6 mm 0.014 μm 1.4e-5 mm | 7 August 2019 | EPYC | Rome | 24 | 48 | 155 W 155,000 mW 0.208 hp 0.155 kW | 128 MiB 131,072 KiB 134,217,728 B 0.125 GiB | 2.3 GHz 2,300 MHz 2,300,000 kHz | 3.2 GHz 3,200 MHz 3,200,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | |||||||||

| 7402 | $ 1,783.00 € 1,604.70 £ 1,444.23 ¥ 184,237.39 | 7 nm 0.007 μm , 14 nm7.0e-6 mm 0.014 μm 1.4e-5 mm | 7 August 2019 | EPYC | Rome | 24 | 48 | 180 W 180,000 mW 0.241 hp 0.18 kW | 128 MiB 131,072 KiB 134,217,728 B 0.125 GiB | 2.8 GHz 2,800 MHz 2,800,000 kHz | 3.35 GHz 3,350 MHz 3,350,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | |||||||||

| 7452 | $ 2,025.00 € 1,822.50 £ 1,640.25 ¥ 209,243.25 | 7 nm 0.007 μm , 14 nm7.0e-6 mm 0.014 μm 1.4e-5 mm | 7 August 2019 | EPYC | Rome | 32 | 64 | 155 W 155,000 mW 0.208 hp 0.155 kW | 128 MiB 131,072 KiB 134,217,728 B 0.125 GiB | 2.35 GHz 2,350 MHz 2,350,000 kHz | 3.35 GHz 3,350 MHz 3,350,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | |||||||||

| 7502 | $ 2,600.00 € 2,340.00 £ 2,106.00 ¥ 268,658.00 | 7 nm 0.007 μm , 14 nm7.0e-6 mm 0.014 μm 1.4e-5 mm | 7 August 2019 | EPYC | Rome | 32 | 64 | 180 W 180,000 mW 0.241 hp 0.18 kW | 128 MiB 131,072 KiB 134,217,728 B 0.125 GiB | 2.5 GHz 2,500 MHz 2,500,000 kHz | 3.35 GHz 3,350 MHz 3,350,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | |||||||||

| 7532 | 7 nm 0.007 μm , 14 nm7.0e-6 mm 0.014 μm 1.4e-5 mm | 19 February 2020 | EPYC | Rome | 32 | 64 | 200 W 200,000 mW 0.268 hp 0.2 kW | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 2.4 GHz 2,400 MHz 2,400,000 kHz | 3.3 GHz 3,300 MHz 3,300,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | ||||||||||

| 7542 | $ 3,400.00 € 3,060.00 £ 2,754.00 ¥ 351,322.00 | 7 nm 0.007 μm , 14 nm7.0e-6 mm 0.014 μm 1.4e-5 mm | 7 August 2019 | EPYC | Rome | 32 | 64 | 225 W 225,000 mW 0.302 hp 0.225 kW | 128 MiB 131,072 KiB 134,217,728 B 0.125 GiB | 2.9 GHz 2,900 MHz 2,900,000 kHz | 3.4 GHz 3,400 MHz 3,400,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | |||||||||

| 7552 | $ 4,025.00 € 3,622.50 £ 3,260.25 ¥ 415,903.25 | 7 nm 0.007 μm , 14 nm7.0e-6 mm 0.014 μm 1.4e-5 mm | 7 August 2019 | EPYC | Rome | 48 | 96 | 200 W 200,000 mW 0.268 hp 0.2 kW | 192 MiB 196,608 KiB 201,326,592 B 0.188 GiB | 2.2 GHz 2,200 MHz 2,200,000 kHz | 3.35 GHz 3,350 MHz 3,350,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | |||||||||

| 7642 | $ 4,775.00 € 4,297.50 £ 3,867.75 ¥ 493,400.75 | 7 nm 0.007 μm , 14 nm7.0e-6 mm 0.014 μm 1.4e-5 mm | 7 August 2019 | EPYC | Rome | 48 | 96 | 225 W 225,000 mW 0.302 hp 0.225 kW | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 2.3 GHz 2,300 MHz 2,300,000 kHz | 3.3 GHz 3,300 MHz 3,300,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | |||||||||

| 7662 | 7 nm 0.007 μm , 14 nm7.0e-6 mm 0.014 μm 1.4e-5 mm | 19 February 2020 | EPYC | Rome | 64 | 128 | 225 W 225,000 mW 0.302 hp 0.225 kW | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 2 GHz 2,000 MHz 2,000,000 kHz | 3.3 GHz 3,300 MHz 3,300,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | ||||||||||

| 7702 | $ 6,450.00 € 5,805.00 £ 5,224.50 ¥ 666,478.50 | 7 nm 0.007 μm , 14 nm7.0e-6 mm 0.014 μm 1.4e-5 mm | 7 August 2019 | EPYC | Rome | 64 | 128 | 200 W 200,000 mW 0.268 hp 0.2 kW | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 2 GHz 2,000 MHz 2,000,000 kHz | 3.35 GHz 3,350 MHz 3,350,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | |||||||||

| 7742 | $ 6,950.00 € 6,255.00 £ 5,629.50 ¥ 718,143.50 | 7 nm 0.007 μm , 14 nm7.0e-6 mm 0.014 μm 1.4e-5 mm | 7 August 2019 | EPYC | Rome | 64 | 128 | 225 W 225,000 mW 0.302 hp 0.225 kW | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 2.25 GHz 2,250 MHz 2,250,000 kHz | 3.4 GHz 3,400 MHz 3,400,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | |||||||||

| 7F32 | $ 2,100.00 € 1,890.00 £ 1,701.00 ¥ 216,993.00 | 7 nm 0.007 μm , 14 nm7.0e-6 mm 0.014 μm 1.4e-5 mm | 14 April 2020 | EPYC | Rome | 8 | 16 | 180 W 180,000 mW 0.241 hp 0.18 kW | 128 MiB 131,072 KiB 134,217,728 B 0.125 GiB | 3.7 GHz 3,700 MHz 3,700,000 kHz | 3.9 GHz 3,900 MHz 3,900,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | |||||||||

| 7F52 | $ 3,100.00 € 2,790.00 £ 2,511.00 ¥ 320,323.00 | 7 nm 0.007 μm , 14 nm7.0e-6 mm 0.014 μm 1.4e-5 mm | 14 April 2020 | EPYC | Rome | 16 | 32 | 240 W 240,000 mW 0.322 hp 0.24 kW | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 3.5 GHz 3,500 MHz 3,500,000 kHz | 3.9 GHz 3,900 MHz 3,900,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | |||||||||

| 7F72 | $ 2,450.00 € 2,205.00 £ 1,984.50 ¥ 253,158.50 | 7 nm 0.007 μm , 14 nm7.0e-6 mm 0.014 μm 1.4e-5 mm | 14 April 2020 | EPYC | Rome | 24 | 48 | 240 W 240,000 mW 0.322 hp 0.24 kW | 192 MiB 196,608 KiB 201,326,592 B 0.188 GiB | 3.2 GHz 3,200 MHz 3,200,000 kHz | 3.7 GHz 3,700 MHz 3,700,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | |||||||||

| 7H12 | 7 nm 0.007 μm , 14 nm7.0e-6 mm 0.014 μm 1.4e-5 mm | 18 September 2019 | EPYC | Rome | 64 | 128 | 280 W 280,000 mW 0.375 hp 0.28 kW | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 2.6 GHz 2,600 MHz 2,600,000 kHz | 3.3 GHz 3,300 MHz 3,300,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | ||||||||||

| Count: 83 | |||||||||||||||||||||||||

Bibliography

- AMD 'Tech Day', February 22, 2017

- AMD 2017 Financial Analyst Day, May 16, 2017

- AMD GCC 9 znver2 enablement patch

- AMD 'Next Horizon', November 6, 2018

- AMD. Lisa Su Keynote. May 26, 2019

- AMD 'Next Horizon Gaming' event at E3, June 10, 2019

See Also

- Intel Ice Lake

| codename | Zen 2 + |

| designer | AMD + |

| first launched | 2019 + |

| full page name | amd/microarchitectures/zen 2 + |

| instance of | microarchitecture + |

| instruction set architecture | x86-64 + |

| manufacturer | GlobalFoundries + and TSMC + |

| microarchitecture type | CPU + |

| name | Zen 2 + |

| pipeline stages | 19 + |

| process | 14 nm (0.014 μm, 1.4e-5 mm) +, 7 nm (0.007 μm, 7.0e-6 mm) + and 12 nm (0.012 μm, 1.2e-5 mm) + |