From WikiChip

Difference between revisions of "arm holdings/microarchitectures/cortex-a53"

| (36 intermediate revisions by 11 users not shown) | |||

| Line 1: | Line 1: | ||

{{armh title|Cortex-A53|arch}} | {{armh title|Cortex-A53|arch}} | ||

{{microarchitecture | {{microarchitecture | ||

| − | | name | + | |atype=CPU |

| − | | designer | + | |name=Cortex-A53 |

| − | | manufacturer | + | |designer=ARM Holdings |

| − | | introduction | + | |manufacturer=TSMC |

| − | | | + | |manufacturer 2=Samsung |

| − | | process | + | |manufacturer 3=GlobalFoundries |

| − | | process | + | |introduction=October 30, 2012 |

| − | | process | + | |process=40 nm |

| − | | process | + | |process 2=28 nm |

| − | | process | + | |process 3=20 nm |

| − | | cores | + | |process 4=16 nm |

| − | | cores 2 | + | |process 5=14 nm |

| − | | cores 3 | + | |process 6=10 nm |

| − | | cores 4 | + | |cores=1 |

| + | |cores 2=2 | ||

| + | |cores 3=3 | ||

| + | |cores 4=4 | ||

| + | |type=In-order | ||

| + | |oooe=No | ||

| + | |speculative=Yes | ||

| + | |renaming=No | ||

| + | |stages=8 | ||

| + | |decode=2-way | ||

| + | |isa=ARMv8 | ||

| + | |feature=Hardware virtualization | ||

| + | |extension=FPU | ||

| + | |extension 2=NEON | ||

| + | |extension 3=TrustZone | ||

| + | |l1i=8-64 KiB | ||

| + | |l1i per=core | ||

| + | |l1i desc=2-way set associative | ||

| + | |l1d=8-64 KiB | ||

| + | |l1d per=core | ||

| + | |l1d desc=4-way set associative | ||

| + | |l2=128 KiB - 2 MiB | ||

| + | |l2 per=cluster | ||

| + | |l2 desc=16-way set associative | ||

| + | |predecessor=Cortex-A7 | ||

| + | |predecessor link=arm_holdings/microarchitectures/cortex-a7 | ||

| + | |successor=Cortex-A55 | ||

| + | |successor link=arm_holdings/microarchitectures/cortex-a55 | ||

| + | |Max clock rate=2,45GHz boost | ||

| + | |pipeline=Yes | ||

| + | |issues=2 | ||

| + | |core names=<!-- Yes if specify --> | ||

| + | }} | ||

| + | '''Cortex-A53''' (formerly '''Apollo''') is an ultra-high efficiency [[microarchitecture]] designed by [[ARM Holdings]] as a successor to the {{armh|Cortex-A7|l=arch}}. The Cortex-A53, which implemented the {{arm|ARMv8}} ISA, is typically found in entry-level smartphone and other embedded devices. Often A53 cores are combined with higher performance processors (e.g. based on {{armh|Cortex-A57|l=arch}} or {{armh|Cortex-A72|l=arch}}) in {{armh|big.LITTLE}} configuration to achieve better energy/performance. | ||

| − | + | Note that this microarchitecture is designed as a synthesizable [[IP core]] and is sold to other semiconductor companies to be implemented in their own chips. | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | == Process Technology == | |

| − | + | {{empty section}} | |

| − | |||

| − | |||

| − | |||

| − | | | + | == Compiler support == |

| − | | | + | {| class="wikitable" |

| − | | | + | |- |

| − | | | + | ! Compiler !! Arch-Specific || Arch-Favorable || Arch-Target |

| − | | | + | |- |

| − | | | + | | [[GCC]] || <code>-march=armv8-a</code> || <code>-mtune=cortex-a53</code> || <code>-mcpu=cortex-a53</code> |

| − | | | + | |- |

| − | | | + | | [[LLVM]] || <code>-march=armv8-a</code> || <code>-mtune=cortex-a53</code> || <code>-mcpu=cortex-a53</code> |

| − | | | + | |} |

| − | | | ||

| − | | | ||

| − | | | ||

| − | | | ||

| − | + | Note that for big.LITTLE systems it's possible to specify more specific performance tunes: | |

| − | |||

| − | |||

| − | |||

| − | + | * <code>-mtune=cortex-a57.cortex-a53</code> | |

| − | + | * <code>-mtune=cortex-a72.cortex-a53</code> | |

| − | + | * <code>-mtune=cortex-a73.cortex-a53</code> | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

== Architecture == | == Architecture == | ||

| + | === Key changes from {{\\|Cortex-A7}} === | ||

| + | {{empty section}} | ||

| + | === Block Diagram === | ||

| + | {{empty section}} | ||

| + | === Memory Hierarchy === | ||

{{empty section}} | {{empty section}} | ||

| + | |||

| + | == Licensees == | ||

| + | Arm named the following companies as licensees. | ||

| + | |||

| + | {{collist | ||

| + | |count = 2 | ||

| + | | | ||

| + | * [[Allwinner]] (A64, H5, H6, H64) | ||

| + | * [[Amlogic]] (S805X, S905, S912) | ||

| + | * [[AMD]] | ||

| + | * [[Broadcom]] | ||

| + | * [[Samsung]] | ||

| + | * [[Altera]] | ||

| + | * [[STMicroelectronics]] | ||

| + | * [[MediaTek]] | ||

| + | * [[Qualcomm]] | ||

| + | * [[Xilinx]] | ||

| + | }} | ||

== Die == | == Die == | ||

| − | {{ | + | === 20 nm === |

| + | ==== Samsung [[Exynos 5433]] ==== | ||

| + | * Samsung [[20 nm process]] | ||

| + | * 113 mm² die size | ||

| + | * Mali-T760 (6 EU) | ||

| + | * Quad-core Cortex-A53 ([[small cores]]) | ||

| + | ** 32 KiB L1I$ and 32 KiB L1D$ per core, and a shared 256 KiB L2 | ||

| + | ** 4.4 mm² per cluster | ||

| + | *** ~1 mm² per core | ||

| + | *** ~0.55 mm² for 256 KiB L2 cache | ||

| + | * Quad-core {{\\|Cortex-A57}} ([[big cores]]) | ||

| + | ** 48KB L1I$ and 32KB L1D$ per core, and a shared 2 MiB L2 | ||

| + | ** 15.85 mm² per cluster | ||

| + | *** ~3 mm² per core | ||

| + | *** ~3.87 mm² for 2 MiB L2 cache | ||

| + | |||

| + | |||

| + | :[[File:exynos 5433 die.png|600px]] | ||

| + | |||

| + | ==== MediaTek [[Helio X20]] ==== | ||

| + | |||

| + | * TSMC [[20 nm process]] | ||

| + | * 100 mm² die size | ||

| + | * Quad-core ULP Cortex-A53 | ||

| + | ** ~21.81 mm² per cluster | ||

| + | *** ~4.23 mm² per core | ||

| + | * Quad-core efficient Cortex-A53 | ||

| + | ** ~29.73 mm² per cluster | ||

| + | *** ~5.41 mm² per core | ||

| + | * Dual-core High-performance {{\\|Cortex-A72}} + 1 MiB L2 | ||

| + | ** ~27.36 mm² per cluster | ||

| + | *** ~ 9.60 mm² per core | ||

| + | *** ~ 7.50 mm² for 1 MiB L2 | ||

| + | |||

| + | |||

| + | :[[File:mt6797 die.png|600px]] | ||

| + | |||

| + | === 16 nm === | ||

| + | ==== Renesas [[R-Car H3]] ==== | ||

| + | * TSMC [[16 nm process]] | ||

| + | * 12.94 mm × 8.61 mm | ||

| + | * 111.36 mm² die size | ||

| + | * Quad-core Cortex-A53 | ||

| + | ** ~3.27 mm² cluster | ||

| + | ** ~0.60 mm² core | ||

| + | ** ~0.7`mm² L2 cache | ||

| + | * Quad-core {{\\|Cortex-A57}} | ||

| + | ** ~10.21 mm² cluster | ||

| + | ** ~1.66 mm² core | ||

| + | ** ~3.28 mm² L2 cache | ||

| + | * {{\\|Cortex-R7}} (dual-core [[lock-step]]) | ||

| + | ** ~1.04 mm² cluster | ||

| + | * GX6650 GPU | ||

| + | ** ~28.12 mm² | ||

| + | |||

| + | |||

| + | : [[File:r-car h3 die shot.png|650px]] | ||

== All Cortex-A53 Chips == | == All Cortex-A53 Chips == | ||

| − | {{ | + | <!-- NOTE: |

| + | This table is generated automatically from the data in the actual articles. | ||

| + | If a microprocessor is missing from the list, an appropriate article for it needs to be | ||

| + | created and tagged accordingly. | ||

| + | |||

| + | Missing a chip? please dump its name here: http://en.wikichip.org/wiki/WikiChip:wanted_chips | ||

| + | --> | ||

| + | {{comp table start}} | ||

| + | <table class="comptable sortable tc18 tc19 tc20 tc21 tc22 tc23"> | ||

| + | <tr class="comptable-header"><th> </th><th colspan="25">List of all Cortex-A53 Chips</th></tr> | ||

| + | <tr class="comptable-header"><th> </th><th colspan="10">Main processor</th><th colspan="3">IGP</th></tr> | ||

| + | {{comp table header 1|cols=Launched, Designer, Family, Process, Core, C, T, L2$, L3$, Frequency, Max Mem, Designer, Name, Frequency}} | ||

| + | {{#ask: [[Category:all microprocessor models]] [[microarchitecture::Cortex-A53]] | ||

| + | |?full page name | ||

| + | |?model number | ||

| + | |?first launched | ||

| + | |?designer | ||

| + | |?microprocessor family | ||

| + | |?process | ||

| + | |?core name | ||

| + | |?core count | ||

| + | |?thread count | ||

| + | |?l2$ size | ||

| + | |?l3$ size | ||

| + | |?base frequency#GHz | ||

| + | |?max memory#GiB | ||

| + | |?integrated gpu designer | ||

| + | |?integrated gpu | ||

| + | |?integrated gpu base frequency | ||

| + | |format=template | ||

| + | |template=proc table 3 | ||

| + | |searchlabel= | ||

| + | |sort=microprocessor family, model number | ||

| + | |order=asc,asc | ||

| + | |userparam=15 | ||

| + | |mainlabel=- | ||

| + | |limit=100 | ||

| + | |valuesep=, | ||

| + | }} | ||

| + | {{comp table count|ask=[[Category:all microprocessor models]] [[microarchitecture::Cortex-A53]]}} | ||

| + | </table> | ||

| + | {{comp table end}} | ||

| + | |||

| + | == Bibliography == | ||

| + | * Pyo, Jungyul, et al. "23.1 20nm high-K metal-gate heterogeneous 64b quad-core CPUs and hexa-core GPU for high-performance and energy-efficient mobile application processor." Solid-State Circuits Conference-(ISSCC), 2015 IEEE International. IEEE, 2015 | ||

| + | * Mair, Hugh T., et al. "4.3 A 20nm 2.5 GHz ultra-low-power tri-cluster CPU subsystem with adaptive power allocation for optimal mobile SoC performance." Solid-State Circuits Conference (ISSCC), 2016 IEEE International. IEEE, 2016. | ||

Latest revision as of 09:34, 30 October 2025

| Edit Values | |

| Cortex-A53 µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | ARM Holdings |

| Manufacturer | TSMC, Samsung, GlobalFoundries |

| Introduction | October 30, 2012 |

| Process | 40 nm, 28 nm, 20 nm, 16 nm, 14 nm, 10 nm |

| Core Configs | 1, 2, 3, 4 |

| Pipeline | |

| Type | In-order |

| OoOE | No |

| Speculative | Yes |

| Reg Renaming | No |

| Stages | 8 |

| Decode | 2-way |

| Instructions | |

| ISA | ARMv8 |

| Extensions | FPU, NEON, TrustZone |

| Cache | |

| L1I Cache | 8-64 KiB/core 2-way set associative |

| L1D Cache | 8-64 KiB/core 4-way set associative |

| L2 Cache | 128 KiB - 2 MiB/cluster 16-way set associative |

| Succession | |

Cortex-A53 (formerly Apollo) is an ultra-high efficiency microarchitecture designed by ARM Holdings as a successor to the Cortex-A7. The Cortex-A53, which implemented the ARMv8 ISA, is typically found in entry-level smartphone and other embedded devices. Often A53 cores are combined with higher performance processors (e.g. based on Cortex-A57 or Cortex-A72) in big.LITTLE configuration to achieve better energy/performance.

Note that this microarchitecture is designed as a synthesizable IP core and is sold to other semiconductor companies to be implemented in their own chips.

Contents

Process Technology[edit]

| This section is empty; you can help add the missing info by editing this page. |

Compiler support[edit]

| Compiler | Arch-Specific | Arch-Favorable | Arch-Target |

|---|---|---|---|

| GCC | -march=armv8-a |

-mtune=cortex-a53 |

-mcpu=cortex-a53

|

| LLVM | -march=armv8-a |

-mtune=cortex-a53 |

-mcpu=cortex-a53

|

Note that for big.LITTLE systems it's possible to specify more specific performance tunes:

-

-mtune=cortex-a57.cortex-a53 -

-mtune=cortex-a72.cortex-a53 -

-mtune=cortex-a73.cortex-a53

Architecture[edit]

Key changes from Cortex-A7[edit]

| This section is empty; you can help add the missing info by editing this page. |

Block Diagram[edit]

| This section is empty; you can help add the missing info by editing this page. |

Memory Hierarchy[edit]

| This section is empty; you can help add the missing info by editing this page. |

Licensees[edit]

Arm named the following companies as licensees.

Die[edit]

20 nm[edit]

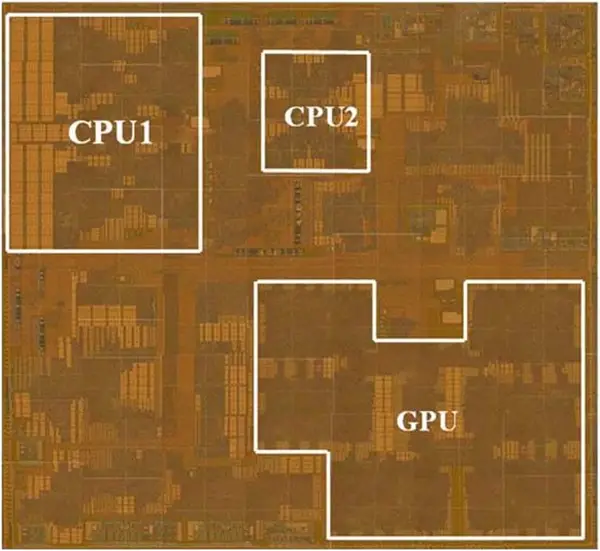

Samsung Exynos 5433[edit]

- Samsung 20 nm process

- 113 mm² die size

- Mali-T760 (6 EU)

- Quad-core Cortex-A53 (small cores)

- 32 KiB L1I$ and 32 KiB L1D$ per core, and a shared 256 KiB L2

- 4.4 mm² per cluster

- ~1 mm² per core

- ~0.55 mm² for 256 KiB L2 cache

- Quad-core Cortex-A57 (big cores)

- 48KB L1I$ and 32KB L1D$ per core, and a shared 2 MiB L2

- 15.85 mm² per cluster

- ~3 mm² per core

- ~3.87 mm² for 2 MiB L2 cache

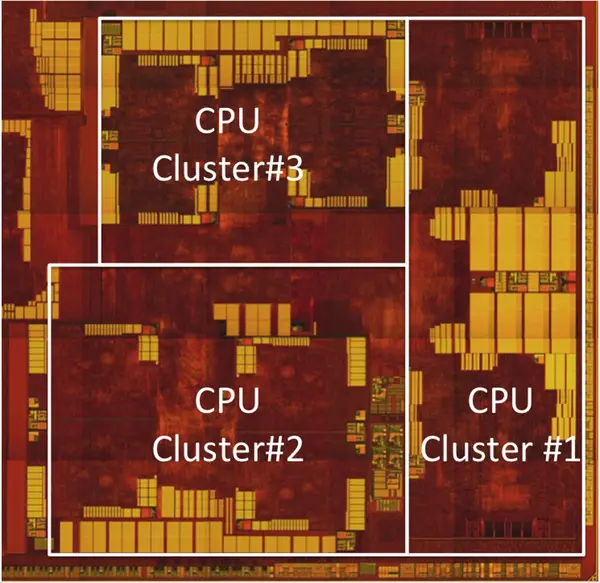

MediaTek Helio X20[edit]

- TSMC 20 nm process

- 100 mm² die size

- Quad-core ULP Cortex-A53

- ~21.81 mm² per cluster

- ~4.23 mm² per core

- ~21.81 mm² per cluster

- Quad-core efficient Cortex-A53

- ~29.73 mm² per cluster

- ~5.41 mm² per core

- ~29.73 mm² per cluster

- Dual-core High-performance Cortex-A72 + 1 MiB L2

- ~27.36 mm² per cluster

- ~ 9.60 mm² per core

- ~ 7.50 mm² for 1 MiB L2

- ~27.36 mm² per cluster

16 nm[edit]

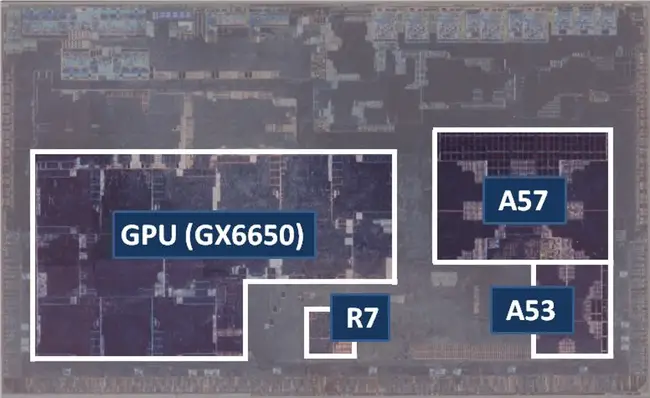

Renesas R-Car H3[edit]

- TSMC 16 nm process

- 12.94 mm × 8.61 mm

- 111.36 mm² die size

- Quad-core Cortex-A53

- ~3.27 mm² cluster

- ~0.60 mm² core

- ~0.7`mm² L2 cache

- Quad-core Cortex-A57

- ~10.21 mm² cluster

- ~1.66 mm² core

- ~3.28 mm² L2 cache

- Cortex-R7 (dual-core lock-step)

- ~1.04 mm² cluster

- GX6650 GPU

- ~28.12 mm²

All Cortex-A53 Chips[edit]

| List of all Cortex-A53 Chips | |||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Main processor | IGP | ||||||||||||||||||||||||

| Model | Launched | Designer | Family | Process | Core | C | T | L2$ | L3$ | Frequency | Max Mem | Designer | Name | Frequency | |||||||||||

| 7270 | November 2016 | Samsung, ARM Holdings | Exynos | 14 nm 0.014 μm 1.4e-5 mm | Cortex-A53 | 2 | 2 | 1 GHz 1,000 MHz 1,000,000 kHz | |||||||||||||||||

| 7420 | April 2015 | Samsung, ARM Holdings | Exynos | 14 nm 0.014 μm 1.4e-5 mm | Cortex-A53, Cortex-A57 | 8 | 8 | 2.1 GHz 2,100 MHz , 1.5 GHz2,100,000 kHz 1,500 MHz 1,500,000 kHz | |||||||||||||||||

| 7570 | 30 August 2016 | Samsung, ARM Holdings | Exynos | 14 nm 0.014 μm 1.4e-5 mm | Cortex-A53 | 4 | 4 | 1.4 GHz 1,400 MHz 1,400,000 kHz | |||||||||||||||||

| 7580 | June 2015 | Samsung, ARM Holdings | Exynos | 28 nm 0.028 μm 2.8e-5 mm | Cortex-A53 | 8 | 8 | 1.6 GHz 1,600 MHz 1,600,000 kHz | |||||||||||||||||

| 7870 | 17 February 2016 | Samsung, ARM Holdings | Exynos | 14 nm 0.014 μm 1.4e-5 mm | Cortex-A53 | 8 | 8 | 1.6 GHz 1,600 MHz 1,600,000 kHz | |||||||||||||||||

| 7872 | 17 January 2018 | Samsung, ARM Holdings | Exynos | 14 nm 0.014 μm 1.4e-5 mm | 6 | 6 | 2 GHz 2,000 MHz , 1.5 GHz2,000,000 kHz 1,500 MHz 1,500,000 kHz | ||||||||||||||||||

| 7880 | March 2017 | Samsung, ARM Holdings | Exynos | 14 nm 0.014 μm 1.4e-5 mm | Cortex-A53 | 8 | 8 | 1.9 GHz 1,900 MHz 1,900,000 kHz | |||||||||||||||||

| 7885 | 13 February 2018 | Samsung, ARM Holdings | Exynos | 14 nm 0.014 μm 1.4e-5 mm | Cortex-A73, Cortex-A53 | 8 | 8 | 2.2 GHz 2,200 MHz , 1.6 GHz2,200,000 kHz 1,600 MHz 1,600,000 kHz | |||||||||||||||||

| 7904 | 21 January 2019 | Samsung, Arm Holdings | Exynos | 14 nm 0.014 μm 1.4e-5 mm | Cortex-A73, Cortex-A53 | 8 | 8 | 1.8 GHz 1,800 MHz 1,800,000 kHz | |||||||||||||||||

| 8890 | 21 February 2016 | Samsung | Exynos | 14 nm 0.014 μm 1.4e-5 mm | Exynos M1, Cortex-A53 | 8 | 8 | 2 MiB 2,048 KiB , 0.25 MiB2,097,152 B 0.00195 GiB 256 KiB 262,144 B 2.441406e-4 GiB | 2.3 GHz 2,300 MHz , 1.6 GHz2,300,000 kHz 1,600 MHz 1,600,000 kHz | 4 GiB 4,096 MiB 4,194,304 KiB 4,294,967,296 B 0.00391 TiB | ARM Holdings | Mali-T880 | |||||||||||||

| 8895 | 29 March 2017 | Samsung, ARM Holdings | Exynos | 10 nm 0.01 μm 1.0e-5 mm | Cortex-A53, Mongoose 2 | 8 | 8 | 1 MiB 1,024 KiB , 0.5 MiB1,048,576 B 9.765625e-4 GiB 512 KiB 524,288 B 4.882812e-4 GiB | 2 MiB 2,048 KiB 2,097,152 B 0.00195 GiB | 2.314 GHz 2,314 MHz , 1.69 GHz2,314,000 kHz 1,690 MHz 1,690,000 kHz | 8 GiB 8,192 MiB 8,388,608 KiB 8,589,934,592 B 0.00781 TiB | ARM Holdings | Mali-G71 | ||||||||||||

| 9110 | 9 August 2018 | Samsung, ARM Holdings | Exynos | 10 nm 0.01 μm 1.0e-5 mm | Cortex-A53 | 2 | 2 | 1 GiB 1,024 MiB 1,048,576 KiB 1,073,741,824 B 9.765625e-4 TiB | ARM Holdings | Mali-T720 | |||||||||||||||

| 9610 | October 2018 | Samsung, ARM Holdings | Exynos | 10 nm 0.01 μm 1.0e-5 mm | Cortex-A73, Cortex-A53 | 8 | 8 | 2.3 GHz 2,300 MHz , 1.7 GHz2,300,000 kHz 1,700 MHz 1,700,000 kHz | ARM Holdings | Mali-G72 | |||||||||||||||

| Helio A22 | 17 July 2018 | MediaTek, ARM Holdings | Helio | 12 nm 0.012 μm 1.2e-5 mm | Cortex-A53 | 4 | 4 | 2 GHz 2,000 MHz 2,000,000 kHz | 6 GiB 6,144 MiB 6,291,456 KiB 6,442,450,944 B 0.00586 TiB | Imagination Technologies | PowerVR GE8320 | ||||||||||||||

| Helio P22 | 22 May 2018 | MediaTek, ARM Holdings | Helio | 12 nm 0.012 μm 1.2e-5 mm | Cortex-A53 | 8 | 8 | 2 GHz 2,000 MHz 2,000,000 kHz | 6 GiB 6,144 MiB 6,291,456 KiB 6,442,450,944 B 0.00586 TiB | Imagination Technologies | PowerVR GE8320 | ||||||||||||||

| Helio P30 | 28 August 2017 | MediaTek, ARM Holdings | Helio | 16 nm 0.016 μm 1.6e-5 mm | Cortex-A53 | 8 | 8 | 1.65 GHz 1,650 MHz , 2.3 GHz1,650,000 kHz 2,300 MHz 2,300,000 kHz | 6 GiB 6,144 MiB 6,291,456 KiB 6,442,450,944 B 0.00586 TiB | ARM Holdings | Mali-G71 | ||||||||||||||

| Helio X10 | 27 March 2015 | MediaTek, ARM Holdings | Helio | 28 nm 0.028 μm 2.8e-5 mm | Cortex-A53 | 8 | 8 | 2 MiB 2,048 KiB 2,097,152 B 0.00195 GiB | 2 GHz 2,000 MHz 2,000,000 kHz | 4 GiB 4,096 MiB 4,194,304 KiB 4,294,967,296 B 0.00391 TiB | Imagination Technologies | PowerVR G6200 | |||||||||||||

| Helio X10 M | 27 March 2015 | MediaTek, ARM Holdings | Helio | 28 nm 0.028 μm 2.8e-5 mm | Cortex-A53 | 8 | 8 | 2 MiB 2,048 KiB 2,097,152 B 0.00195 GiB | 2 GHz 2,000 MHz 2,000,000 kHz | 4 GiB 4,096 MiB 4,194,304 KiB 4,294,967,296 B 0.00391 TiB | Imagination Technologies | PowerVR G6200 | |||||||||||||

| Helio X10 T | 27 March 2015 | MediaTek, ARM Holdings | Helio | 28 nm 0.028 μm 2.8e-5 mm | Cortex-A53 | 8 | 8 | 2 MiB 2,048 KiB 2,097,152 B 0.00195 GiB | 2.2 GHz 2,200 MHz 2,200,000 kHz | 4 GiB 4,096 MiB 4,194,304 KiB 4,294,967,296 B 0.00391 TiB | Imagination Technologies | PowerVR G6200 | |||||||||||||

| Helio X20 | 16 March 2016 | MediaTek, ARM Holdings | Helio | 20 nm 0.02 μm 2.0e-5 mm | Cortex-A53, Cortex-A72 | 10 | 10 | 1.85 GHz 1,850 MHz , 1.4 GHz1,850,000 kHz 1,400 MHz , 2.1 GHz1,400,000 kHz 2,100 MHz 2,100,000 kHz | ARM Holdings | Mali-T880 | |||||||||||||||

| Helio X20 M | 16 March 2016 | MediaTek, ARM Holdings | Helio | 20 nm 0.02 μm 2.0e-5 mm | Cortex-A53, Cortex-A72 | 10 | 10 | 2 GHz 2,000 MHz , 1.85 GHz2,000,000 kHz 1,850 MHz , 1.4 GHz1,850,000 kHz 1,400 MHz 1,400,000 kHz | 6 GiB 6,144 MiB 6,291,456 KiB 6,442,450,944 B 0.00586 TiB | ARM Holdings | Mali-T880 | ||||||||||||||

| Helio X23 | 2 December 2016 | MediaTek, ARM Holdings | Helio | 20 nm 0.02 μm 2.0e-5 mm | Cortex-A53, Cortex-A72 | 10 | 10 | 2.3 GHz 2,300 MHz , 1.85 GHz2,300,000 kHz 1,850 MHz , 1.4 GHz1,850,000 kHz 1,400 MHz 1,400,000 kHz | 4 GiB 4,096 MiB 4,194,304 KiB 4,294,967,296 B 0.00391 TiB | ARM Holdings | Mali-T880 | ||||||||||||||

| Helio X25 | 16 March 2016 | ARM Holdings, MediaTek | Helio | 20 nm 0.02 μm 2.0e-5 mm | Cortex-A53, Cortex-A72 | 10 | 10 | 2.5 GHz 2,500 MHz , 2 GHz2,500,000 kHz 2,000 MHz , 1.55 GHz2,000,000 kHz 1,550 MHz 1,550,000 kHz | 6 GiB 6,144 MiB 6,291,456 KiB 6,442,450,944 B 0.00586 TiB | ARM Holdings | Mali-T880 | ||||||||||||||

| Helio X27 | 2 December 2016 | MediaTek, ARM Holdings | Helio | 20 nm 0.02 μm 2.0e-5 mm | Cortex-A53, Cortex-A72 | 10 | 10 | 2.6 GHz 2,600 MHz , 2 GHz2,600,000 kHz 2,000 MHz , 1.6 GHz2,000,000 kHz 1,600 MHz 1,600,000 kHz | ARM Holdings | Mali-T880 | |||||||||||||||

| Helio X30 | 27 February 2017 | MediaTek, ARM Holdings | Helio | 10 nm 0.01 μm 1.0e-5 mm | Cortex-A35, Cortex-A53, Cortex-A73 | 10 | 10 | 2.5 GHz 2,500 MHz , 2.2 GHz2,500,000 kHz 2,200 MHz , 1.9 GHz2,200,000 kHz 1,900 MHz 1,900,000 kHz | 8 GiB 8,192 MiB 8,388,608 KiB 8,589,934,592 B 0.00781 TiB | Imagination Technologies | PowerVR GT7400 Plus | ||||||||||||||

| P10 | January 2016 | MediaTek, ARM Holdings | Helio | 28 nm 0.028 μm 2.8e-5 mm | Cortex-A53 | 8 | 8 | 2 MiB 2,048 KiB 2,097,152 B 0.00195 GiB | 2 GHz 2,000 MHz , 1.2 GHz2,000,000 kHz 1,200 MHz 1,200,000 kHz | 4 GiB 4,096 MiB 4,194,304 KiB 4,294,967,296 B 0.00391 TiB | ARM Holdings | Mali-T860 | |||||||||||||

| P10 M | January 2016 | MediaTek, ARM Holdings | Helio | 28 nm 0.028 μm 2.8e-5 mm | Cortex-A53 | 8 | 8 | 2 MiB 2,048 KiB 2,097,152 B 0.00195 GiB | 1.8 GHz 1,800 MHz , 1.2 GHz1,800,000 kHz 1,200 MHz 1,200,000 kHz | 4 GiB 4,096 MiB 4,194,304 KiB 4,294,967,296 B 0.00391 TiB | ARM Holdings | Mali-T860 | |||||||||||||

| P15 | April 2017 | MediaTek, ARM Holdings | Helio | 28 nm 0.028 μm 2.8e-5 mm | Cortex-A53 | 8 | 8 | 2 MiB 2,048 KiB 2,097,152 B 0.00195 GiB | 2.2 GHz 2,200 MHz , 1.2 GHz2,200,000 kHz 1,200 MHz 1,200,000 kHz | 4 GiB 4,096 MiB 4,194,304 KiB 4,294,967,296 B 0.00391 TiB | ARM Holdings | Mali-T860 | |||||||||||||

| P20 | November 2016 | MediaTek, ARM Holdings | Helio | 16 nm 0.016 μm 1.6e-5 mm | Cortex-A53 | 8 | 8 | 2 MiB 2,048 KiB 2,097,152 B 0.00195 GiB | 2.3 GHz 2,300 MHz 2,300,000 kHz | 6 GiB 6,144 MiB 6,291,456 KiB 6,442,450,944 B 0.00586 TiB | ARM Holdings | Mali-T880 | |||||||||||||

| P23 | 28 August 2017 | MediaTek, ARM Holdings | Helio | 16 nm 0.016 μm 1.6e-5 mm | Cortex-A53 | 8 | 8 | 1.65 GHz 1,650 MHz 1,650,000 kHz | 6 GiB 6,144 MiB 6,291,456 KiB 6,442,450,944 B 0.00586 TiB | ARM Holdings | Mali-G71 | ||||||||||||||

| P25 | 8 February 2017 | MediaTek, ARM Holdings | Helio | 16 nm 0.016 μm 1.6e-5 mm | Cortex-A53 | 8 | 8 | 2 MiB 2,048 KiB 2,097,152 B 0.00195 GiB | 2.6 GHz 2,600 MHz 2,600,000 kHz | 6 GiB 6,144 MiB 6,291,456 KiB 6,442,450,944 B 0.00586 TiB | ARM Holdings | Mali-T880 | |||||||||||||

| P60 | 26 February 2018 | ARM Holdings, MediaTek | Helio | 12 nm 0.012 μm 1.2e-5 mm | Cortex-A53, Cortex-A73 | 8 | 8 | 2 GHz 2,000 MHz 2,000,000 kHz | 8 GiB 8,192 MiB 8,388,608 KiB 8,589,934,592 B 0.00781 TiB | ARM Holdings | Mali-G72 | ||||||||||||||

| P70 | 24 October 2018 | MediaTek, ARM Holdings | Helio | 12 nm 0.012 μm 1.2e-5 mm | Cortex-A73, Cortex-A53 | 8 | 8 | 2.1 GHz 2,100 MHz , 2 GHz2,100,000 kHz 2,000 MHz 2,000,000 kHz | 8 GiB 8,192 MiB 8,388,608 KiB 8,589,934,592 B 0.00781 TiB | ARM Holdings | Mali-G72 | ||||||||||||||

| 710 | 19 July 2018 | HiSilicon, ARM Holdings | Kirin | 12 nm 0.012 μm 1.2e-5 mm | Cortex-A53, Cortex-A73 | 8 | 8 | 2.2 GHz 2,200 MHz , 1.7 GHz2,200,000 kHz 1,700 MHz 1,700,000 kHz | 6 GiB 6,144 MiB 6,291,456 KiB 6,442,450,944 B 0.00586 TiB | ARM Holdings | Mali-G51 | ||||||||||||||

| 970 | 1 September 2017 | HiSilicon, ARM Holdings | Kirin | 10 nm 0.01 μm 1.0e-5 mm | Cortex-A53, Cortex-A73 | 8 | 8 | 1 MiB 1,024 KiB , 2 MiB1,048,576 B 9.765625e-4 GiB 2,048 KiB 2,097,152 B 0.00195 GiB | 1.8 GHz 1,800 MHz , 2.36 GHz1,800,000 kHz 2,360 MHz 2,360,000 kHz | 8 GiB 8,192 MiB 8,388,608 KiB 8,589,934,592 B 0.00781 TiB | ARM Holdings | Mali-G72 | |||||||||||||

| H3 | March 2018 | Renesas, ARM Holdings | R-Car | 16 nm 0.016 μm 1.6e-5 mm | Cortex-A53, Cortex-A57, Cortex-R7 | 9 | 9 | 2 MiB 2,048 KiB , 0.5 MiB2,097,152 B 0.00195 GiB 512 KiB 524,288 B 4.882812e-4 GiB | Imagination Technologies | PowerVR GX6650 | |||||||||||||||

| H3 (SiP) | March 2018 | Renesas, ARM Holdings | R-Car | 16 nm 0.016 μm 1.6e-5 mm | Cortex-A53, Cortex-A57, Cortex-R7 | 9 | 9 | 2.5 MiB 2,560 KiB 2,621,440 B 0.00244 GiB | Imagination Technologies | PowerVR GX6650 | |||||||||||||||

| M3 | October 2016 | Renesas, ARM Holdings | R-Car | 16 nm 0.016 μm 1.6e-5 mm | Cortex-A53, Cortex-A57, Cortex-R7 | 7 | 7 | 1.5 MiB 1,536 KiB 1,572,864 B 0.00146 GiB | Imagination Technologies | PowerVR GX6250 | |||||||||||||||

| M3 (SiP) | October 2016 | ARM Holdings, Renesas | R-Car | 16 nm 0.016 μm 1.6e-5 mm | Cortex-A53, Cortex-A57, Cortex-R7 | 7 | 7 | 1.5 MiB 1,536 KiB 1,572,864 B 0.00146 GiB | Imagination Technologies | PowerVR GX6250 | |||||||||||||||

| SDM429 | 26 June 2018 | Qualcomm, ARM Holdings | Snapdragon 400 | 12 nm 0.012 μm 1.2e-5 mm | Cortex-A53 | 4 | 4 | 1.95 GHz 1,950 MHz 1,950,000 kHz | 4 GiB 4,096 MiB 4,194,304 KiB 4,294,967,296 B 0.00391 TiB | Qualcomm | Adreno 504 | ||||||||||||||

| SDM439 | 26 June 2018 | Qualcomm | Snapdragon 400 | 12 nm 0.012 μm 1.2e-5 mm | Cortex-A53 | 8 | 8 | 1.45 GHz 1,450 MHz , 1.95 GHz1,450,000 kHz 1,950 MHz 1,950,000 kHz | 4 GiB 4,096 MiB 4,194,304 KiB 4,294,967,296 B 0.00391 TiB | Qualcomm | Adreno 505 | ||||||||||||||

| SM4250 | 20 January 2020 | Qualcomm | Snapdragon 400 | 11 nm 0.011 μm 1.1e-5 mm | Kryo 240 Gold, Kryo 240 Silver | 8 | 8 | 1.8 GHz 1,800 MHz , 1.6 GHz1,800,000 kHz 1,600 MHz 1,600,000 kHz | Qualcomm | Adreno 610 | |||||||||||||||

| SM6115 | 20 January 2020 | Qualcomm | Snapdragon 600, Snapdragon 6 | 11 nm 0.011 μm 1.1e-5 mm | Kryo 260 Gold, Kryo 260 Silver | 8 | 8 | 1.8 GHz 1,800 MHz , 2 GHz1,800,000 kHz 2,000 MHz 2,000,000 kHz | 8 GiB 8,192 MiB 8,388,608 KiB 8,589,934,592 B 0.00781 TiB | Qualcomm | Adreno 610 | ||||||||||||||

| SDM632 | 26 June 2018 | Qualcomm | Snapdragon 600 | 14 nm 0.014 μm 1.4e-5 mm | Kryo 250 Silver, Kryo 250 Gold | 8 | 8 | 1.8 GHz 1,800 MHz 1,800,000 kHz | 8 GiB 8,192 MiB 8,388,608 KiB 8,589,934,592 B 0.00781 TiB | Qualcomm | Adreno 506 | ||||||||||||||

| SDM660 | 8 May 2017 | Qualcomm, ARM Holdings | Snapdragon 600 | 14 nm 0.014 μm 1.4e-5 mm | Kryo 260 Gold, Kryo 260 Silver | 8 | 8 | 2.2 GHz 2,200 MHz , 1.84 GHz2,200,000 kHz 1,840 MHz 1,840,000 kHz | 8 GiB 8,192 MiB 8,388,608 KiB 8,589,934,592 B 0.00781 TiB | Qualcomm | Adreno 512 | ||||||||||||||

| SM6125 | 9 April 2019 | Qualcomm, ARM Holdings | Snapdragon 600 | 11 nm 0.011 μm 1.1e-5 mm | Kryo 260 Gold, Kryo 260 Silver | 8 | 8 | 1.8 GHz 1,800 MHz , 2 GHz1,800,000 kHz 2,000 MHz 2,000,000 kHz | 8 GiB 8,192 MiB 8,388,608 KiB 8,589,934,592 B 0.00781 TiB | Qualcomm | Adreno 610 | ||||||||||||||

| BM1880 | 17 October 2018 | Bitmain | Sophon | Cortex-A53, RISC-V | 4 GiB 4,096 MiB 4,194,304 KiB 4,294,967,296 B 0.00391 TiB | ||||||||||||||||||||

| S1 | Xiaomi, ARM Holdings | Surge | 28 nm 0.028 μm 2.8e-5 mm | Cortex-A53 | 8 | 8 | 1.4 GHz 1,400 MHz , 2.2 GHz1,400,000 kHz 2,200 MHz 2,200,000 kHz | ARM Holdings | Mali-T860 | ||||||||||||||||

| S2 | Xiaomi, ARM Holdings | Surge | 10 nm 0.01 μm 1.0e-5 mm | Cortex-A53, Cortex-A73 | 8 | 8 | ARM Holdings | Mali-G71 | |||||||||||||||||

| Count: 50 | |||||||||||||||||||||||||

Bibliography[edit]

- Pyo, Jungyul, et al. "23.1 20nm high-K metal-gate heterogeneous 64b quad-core CPUs and hexa-core GPU for high-performance and energy-efficient mobile application processor." Solid-State Circuits Conference-(ISSCC), 2015 IEEE International. IEEE, 2015

- Mair, Hugh T., et al. "4.3 A 20nm 2.5 GHz ultra-low-power tri-cluster CPU subsystem with adaptive power allocation for optimal mobile SoC performance." Solid-State Circuits Conference (ISSCC), 2016 IEEE International. IEEE, 2016.

Facts about "Cortex-A53 - Microarchitectures - ARM"

| codename | Cortex-A53 + |

| core count | 1 +, 2 +, 3 + and 4 + |

| designer | ARM Holdings + |

| first launched | October 30, 2012 + |

| full page name | arm holdings/microarchitectures/cortex-a53 + |

| instance of | microarchitecture + |

| instruction set architecture | ARMv8 + |

| manufacturer | TSMC +, Samsung + and GlobalFoundries + |

| microarchitecture type | CPU + |

| name | Cortex-A53 + |

| pipeline stages | 8 + |

| process | 40 nm (0.04 μm, 4.0e-5 mm) +, 28 nm (0.028 μm, 2.8e-5 mm) +, 20 nm (0.02 μm, 2.0e-5 mm) +, 16 nm (0.016 μm, 1.6e-5 mm) +, 14 nm (0.014 μm, 1.4e-5 mm) + and 10 nm (0.01 μm, 1.0e-5 mm) + |