From WikiChip

Exynos 5433 - Samsung

| Edit Values | |

| Exynos 5433 | |

| General Info | |

| Designer | Samsung, ARM Holdings |

| Manufacturer | Samsung |

| Model Number | 5433 |

| Market | Mobile |

| Introduction | September 7, 2014 (announced) September 7, 2014 (launched) |

| General Specs | |

| Family | Exynos |

| Series | Exynos 7 |

| Frequency | 1,900 MHz, 1,300 MHz, 2,340 MHz, 1,101 MHz |

| Microarchitecture | |

| ISA | ARMv8 (ARM) |

| Microarchitecture | Cortex-A57, Cortex-A53 |

| Core Name | Cortex-A57, Cortex-A53 |

| Process | 20 nm |

| Technology | CMOS |

| Die | 113 mm² |

| Word Size | 64 bit |

| Cores | 8 |

| Threads | 8 |

| Multiprocessing | |

| Max SMP | 1-Way (Uniprocessor) |

| Electrical | |

| Vcore | 1.00 V- |

| cTDP down | 12 W |

| cTDP down frequency | 1,900 MHz |

| cTDP up | 18 W |

| cTDP up frequency | 2,340 MHz |

| Tjunction | 100°C – |

Exynos 5433 is a 64-bit octa-core ARM high performance mobile system on a chip designed by Samsung and introduced in early 2014. The processor is fabricated on Samsung's 20 nm process and features 8 cores in a big.LITTLE configuration consisting of 4 Cortex-A57 big cores and 4 Cortex-A53 little cores. This chip supports up to 3 GiB of dual-channel LPDDR3-1866 memory and incorporates a Mali-T760 MP6 GPU.

Cache[edit]

- Main articles: Cortex-A57 § Cache and Cortex-A53 § Cache

Cortex-A57 Cluster:

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||

|

|||||||||||||||||||||||||

Cortex-A53 Cluster:

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||

|

|||||||||||||||||||||||||

Memory controller[edit]

|

Integrated Memory Controller

|

||||||||||||||||

|

||||||||||||||||

Graphics[edit]

|

Integrated Graphics Information

|

||||||||||||||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||||||||||||||

- Full HD 120fps encoding and decoding

- HEVC decoding, VP8 Codec

Camera[edit]

- Front 3.7 MP

- Rear 16 MP

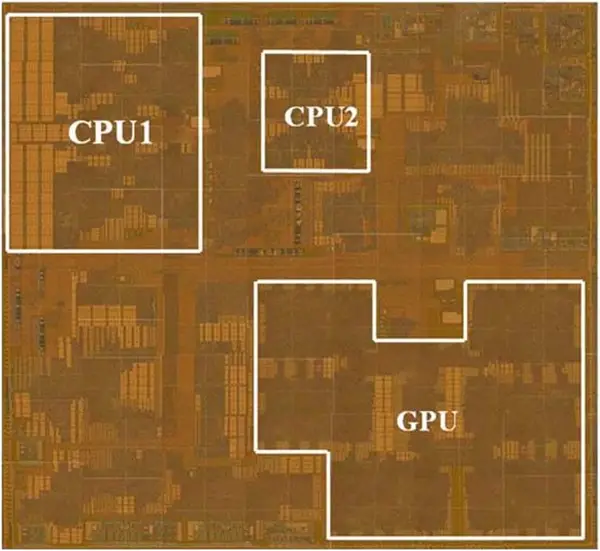

Die[edit]

- Samsung 20 nm process

- 113 mm² die size

- Mali-T760 (6 EU)

- Quad-core Cortex-A53 (small cores)

- 32 KiB L1I$ and 32 KiB L1D$ per core, and a shared 256 KiB L2

- 4.4 mm² per cluster

- ~1 mm² per core

- ~0.55 mm² for 256 KiB L2 cache

- Quad-core Cortex-A57 (big cores)

- 48KB L1I$ and 32KB L1D$ per core, and a shared 2 MiB L2

- 15.85 mm² per cluster

- ~3 mm² per core

- ~3.87 mm² for 2 MiB L2 cache

Utilizing devices[edit]

- Samsung Galaxy Note 4

- Samsung Galaxy Note Edge

- Samsung Galaxy Tab S2

This list is incomplete; you can help by expanding it.

Bibliography[edit]

- Pyo, Jungyul, et al. "23.1 20nm high-K metal-gate heterogeneous 64b quad-core CPUs and hexa-core GPU for high-performance and energy-efficient mobile application processor." Solid-State Circuits Conference-(ISSCC), 2015 IEEE International. IEEE, 2015

Categories:

- all integrated circuit models

- integrated circuit models by samsung

- integrated circuit models by samsung based on cortex-a57

- integrated circuit models by samsung based on cortex-a53

- integrated circuit models by arm holdings

- integrated circuit models by arm holdings based on cortex-a57

- integrated circuit models by arm holdings based on cortex-a53

Facts about "Exynos 5433 - Samsung"

| base frequency | 1,900 MHz (1.9 GHz, 1,900,000 kHz) +, 1,300 MHz (1.3 GHz, 1,300,000 kHz) +, 2,340 MHz (2.34 GHz, 2,340,000 kHz) + and 1,101 MHz (1.101 GHz, 1,101,000 kHz) + |

| core count | 8 + |

| core name | Cortex-A57 + and Cortex-A53 + |

| core voltage (min) | 1 V (10 dV, 100 cV, 1,000 mV) + |

| designer | Samsung + and ARM Holdings + |

| die area | 113 mm² (0.175 in², 1.13 cm², 113,000,000 µm²) + |

| family | Exynos + |

| first announced | September 7, 2014 + |

| first launched | September 7, 2014 + |

| full page name | samsung/exynos/5433 + |

| has ecc memory support | false + |

| instance of | integrated circuit + |

| integrated gpu | Mali-T760 + |

| integrated gpu base frequency | 700 MHz (0.7 GHz, 700,000 KHz) + |

| integrated gpu designer | ARM Holdings + |

| integrated gpu execution units | 6 + |

| isa | ARMv8 + |

| isa family | ARM + |

| l1$ size | 320 KiB (327,680 B, 0.313 MiB) + and 256 KiB (262,144 B, 0.25 MiB) + |

| l1d$ size | 128 KiB (131,072 B, 0.125 MiB) + |

| l1i$ size | 192 KiB (196,608 B, 0.188 MiB) + and 128 KiB (131,072 B, 0.125 MiB) + |

| l2$ size | 2 MiB (2,048 KiB, 2,097,152 B, 0.00195 GiB) + and 0.25 MiB (256 KiB, 262,144 B, 2.441406e-4 GiB) + |

| ldate | September 7, 2014 + |

| manufacturer | Samsung + |

| market segment | Mobile + |

| max cpu count | 1 + |

| max memory bandwidth | 13.91 GiB/s (14,243.84 MiB/s, 14.936 GB/s, 14,935.749 MB/s, 0.0136 TiB/s, 0.0149 TB/s) + |

| max memory channels | 2 + |

| microarchitecture | Cortex-A57 + and Cortex-A53 + |

| min junction temperature | 373.15 K (100 °C, 212 °F, 671.67 °R) + |

| model number | 5433 + |

| name | Exynos 5433 + |

| process | 20 nm (0.02 μm, 2.0e-5 mm) + |

| series | Exynos 7 + |

| smp max ways | 1 + |

| supported memory type | LPDDR3-1866 + |

| tdp down | 12 W (12,000 mW, 0.0161 hp, 0.012 kW) + |

| tdp down frequency | 1,900 MHz (1.9 GHz, 1,900,000 kHz) + |

| tdp up | 18 W (18,000 mW, 0.0241 hp, 0.018 kW) + |

| tdp up frequency | 2,340 MHz (2.34 GHz, 2,340,000 kHz) + |

| technology | CMOS + |

| thread count | 8 + |

| used by | Samsung Galaxy Note 4 +, Samsung Galaxy Note Edge + and Samsung Galaxy Tab S2 + |

| word size | 64 bit (8 octets, 16 nibbles) + |