From WikiChip

Difference between revisions of "lake"

(→See also) |

|||

| (13 intermediate revisions by 4 users not shown) | |||

| Line 1: | Line 1: | ||

| + | {{title|Lake}} | ||

| + | |||

| + | === Overview === | ||

'''Lake''' may refer to: | '''Lake''' may refer to: | ||

| + | {| border="0" cellpadding="5" width="90%" | ||

| + | |- | ||

| + | |width="25%" valign="top" align="left"| | ||

| + | :; <big>[[Intel]]</big> | ||

| + | |||

| + | :; Nervana | ||

| + | * {{nervana|Lake Crest|l=arch}} | ||

| + | :; IGPs | ||

| + | * {{intel|Ironlake}} | ||

| + | |||

| + | :; Platforms | ||

| + | * {{intel|Rock Lake|l=platform}} | ||

| + | |width="25%" valign="top" align="left"| | ||

| + | :; '''[[Microarchitectures]]''' | ||

| + | |||

| + | :; '''Client''' | ||

| + | * {{intel|Alder Lake|l=arch}} | ||

| + | * {{intel|Amber Lake|l=arch}} | ||

| + | * {{intel|Comet Lake|l=arch}} | ||

| + | * {{intel|Cannon Lake|l=arch}} | ||

| + | * {{intel|Coffee Lake|l=arch}} | ||

| + | |width="25%" valign="top" align="left"| | ||

| + | * {{intel|Skylake (client)|Skylake|l=arch}} | ||

| + | * {{intel|Kaby Lake|l=arch}} | ||

| + | * {{intel|Ice Lake (client)|Ice Lake|l=arch}} | ||

| + | * {{intel|Tiger Lake|l=arch}} | ||

| + | * {{intel|Rocket Lake|l=arch}} | ||

| + | * {{intel|Raptor Lake|l=arch}} | ||

| + | * {{intel|Meteor Lake|l=arch}} | ||

| + | * {{intel|Whiskey Lake|l=arch}} | ||

| + | |width="25%" valign="top" align="left"| | ||

| + | :; '''Server''' | ||

| + | * {{intel|Skylake (server)|Skylake|l=arch}} | ||

| + | * {{intel|Cascade Lake|l=arch}} | ||

| + | * {{intel|Cooper Lake|l=arch}} | ||

| + | * {{intel|Ice Lake (server)|Ice Lake|l=arch}} | ||

| + | : '''Edge''' • {{intel|Lakefield|l=arch}} | ||

| + | : '''MCU''' • {{intel|Lakemont|l=arch}} | ||

| + | |} | ||

| + | ---- | ||

| + | {| border="0" cellpadding="5" width="90%" | ||

| + | |- | ||

| + | |width="25%" valign="top" align="left"| | ||

| + | :; <big>'''Cores'''</big> | ||

| + | |||

| + | :; Client | ||

| + | * [[Amber Lake]] | ||

| + | :• {{intel|Amber Lake Y|l=core}} | ||

| + | * [[Coffee Lake]] | ||

| + | :• {{intel|Coffee Lake ER|l=core}} | ||

| + | :• {{intel|Coffee Lake E|l=core}} | ||

| + | :• {{intel|Coffee Lake R|l=core}} | ||

| + | :• {{intel|Coffee Lake S|l=core}} | ||

| + | :• {{intel|Coffee Lake HR|l=core}} | ||

| + | :• {{intel|Coffee Lake H|l=core}} | ||

| + | :• {{intel|Coffee Lake U|l=core}} | ||

| + | |width="25%" valign="top" align="left"| | ||

| + | * {{intel|Apollo Lake|l=core}} | ||

| + | * {{intel|Elkhart Lake|l=core}} | ||

| + | * {{intel|Gemini Lake|l=core}} | ||

| + | * [[Kaby Lake]] | ||

| + | :• {{intel|Kaby Lake X|l=core}} | ||

| + | :• {{intel|Kaby Lake DT|l=core}} | ||

| + | :• {{intel|Kaby Lake R|l=core}} | ||

| + | :• {{intel|Kaby Lake S|l=core}} | ||

| + | :• {{intel|Kaby Lake G|l=core}} | ||

| + | :• {{intel|Kaby Lake H|l=core}} | ||

| + | :• {{intel|Kaby Lake U|l=core}} | ||

| + | :• {{intel|Kaby Lake Y|l=core}} | ||

| + | |width="25%" valign="top" align="left"| | ||

| + | * [[Skylake]] | ||

| + | :• {{intel|Skylake DT|l=core}} | ||

| + | :• {{intel|Skylake S|l=core}} | ||

| + | :• {{intel|Skylake H|l=core}} | ||

| + | :• {{intel|Skylake U|l=core}} | ||

| + | :• {{intel|Skylake Y|l=core}} | ||

| + | * [[Whiskey Lake]] | ||

| + | :• {{intel|Whiskey Lake U|l=core}} | ||

| + | * [[Ice Lake]] | ||

| + | :• {{intel|Ice Lake U|l=core}} | ||

| + | :• {{intel|Ice Lake Y|l=core}} | ||

| + | * {{intel|Mercury Lake|l=core}} | ||

| + | |width="25%" valign="top" align="left"| | ||

| + | :; '''Server''' | ||

| + | * [[Skylake]] | ||

| + | :• {{intel|Skylake SP|l=core}} | ||

| + | :• {{intel|Skylake X|l=core}} | ||

| + | :• {{intel|Skylake W|l=core}} | ||

| + | :• {{intel|Skylake DE|l=core}} | ||

| + | * [[Cascade Lake]] | ||

| + | :• {{intel|Cascade Lake AP|l=core}} | ||

| + | :• {{intel|Cascade Lake SP|l=core}} | ||

| + | :• {{intel|Cascade Lake R|l=core}} | ||

| + | :• {{intel|Cascade Lake X|l=core}} | ||

| + | :• {{intel|Cascade Lake W|l=core}} | ||

| + | * [[Ice Lake]] • {{intel|Ice Lake SP|l=core}} | ||

| + | |} | ||

| + | |||

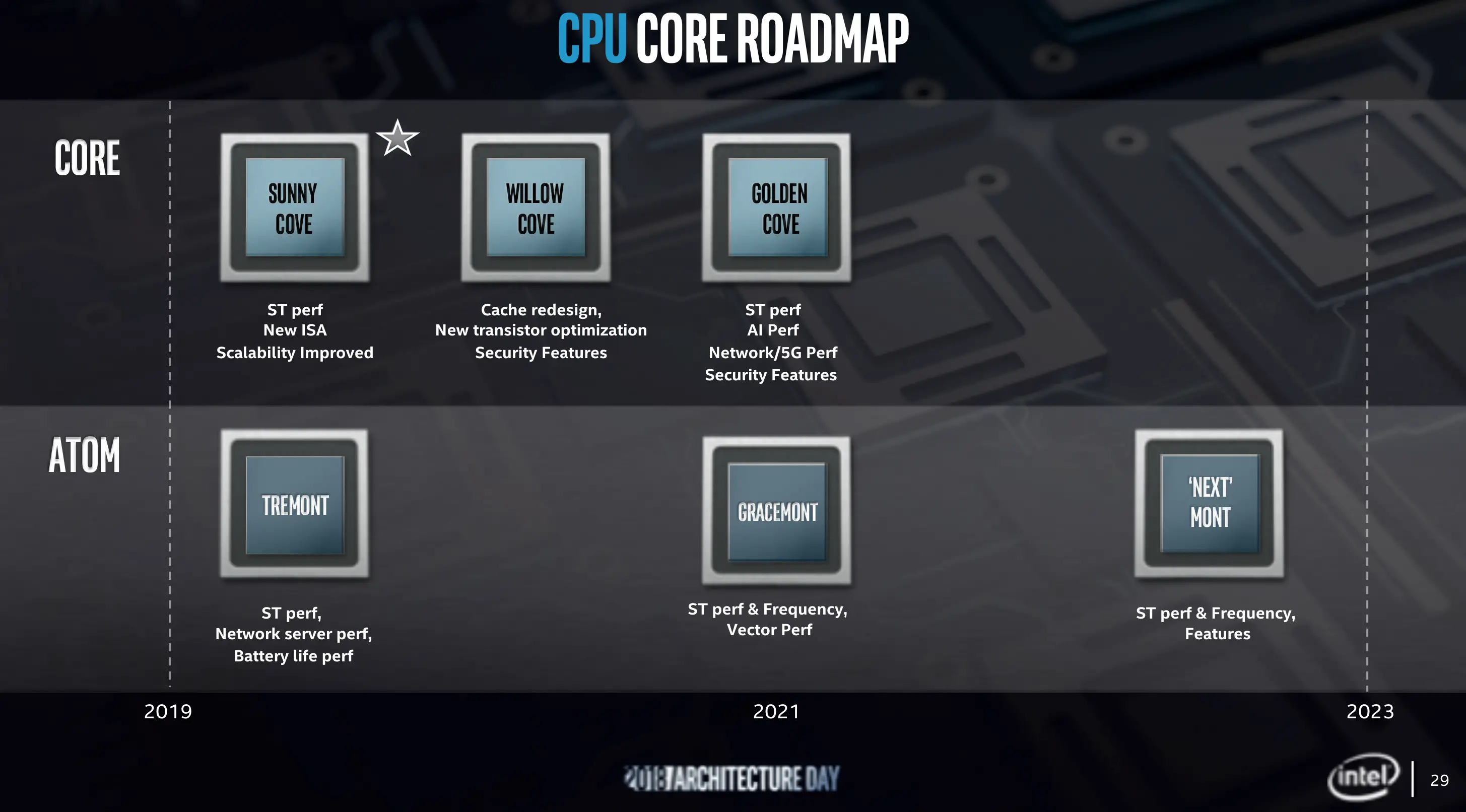

| + | == Intel CPU Core Roadmap == | ||

| + | {{see also|Intel Atom|intel/core}} | ||

| + | <!-- | ||

| + | {{Navbox | ||

| + | |state={{{state|nocollapse}}} | ||

| + | |name=Intel processor Roadmap | ||

| + | |title=Intel CPU core Roadmaps from [[P6]] to [[Panther Lake]] | ||

| + | |list1= --> | ||

| + | <table class="wikitable" style="border:none; text-align:center;"> | ||

| + | <tr> | ||

| + | <th colspan="2">[[Intel Atom]] (ULV)</th> | ||

| + | <td rowspan="39" style="border:none; background-color:var(--background-color-base);"></td> | ||

| + | <th rowspan="2">Node name</th> | ||

| + | <td rowspan="39" style="border:none; background-color:var(--background-color-base);"></td> | ||

| + | <th colspan="2">{{intel|core|Intel Core}}/[[Pentium]]</th> | ||

| + | <td rowspan="39" style="border:none; background-color:var(--background-color-base);"></td> | ||

| + | <td colspan="5" rowspan="7" style="border:none; background-color:var(--background-color-base);"></td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <th>[[Microarchitecture|Microarch]]</th> | ||

| + | <th>Core/Step</th> | ||

| + | <th>[[Microarchitecture|Microarch]]</th> | ||

| + | <th>Core/Step</th> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <td colspan="2" rowspan="13"></td> | ||

| + | <th>[[600 nm process|600 nm]]</th> | ||

| + | <td rowspan="8"><b>[[P6]]</b></td> | ||

| + | <td>[[Pentium Pro]]<br>(133 MHz)</td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <th>[[600 nm process|500 nm]]</th> | ||

| + | <td>[[Pentium Pro]]<br>(150 MHz)</td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <th rowspan="2">[[350 nm process|350 nm]]</th> | ||

| + | <td>{{intel|Pentium Pro|l=arch}}<br>(166–200 MHz)</td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <td>{{intel|Klamath|l=core}}</td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <th rowspan="2">[[250 nm process|250 nm]]</th> | ||

| + | <td>{{intel|Deschutes|l=core}}</td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <td>{{intel|Katmai|l=core}}</td> | ||

| + | <th>[[NetBurst]]</th> | ||

| + | <td colspan="4" rowspan="3" style="border:none; background-color:var(--background-color-base);"></td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <th>[[180 nm process|180 nm]]</th> | ||

| + | <td>{{intel|Coppermine|l=core}}</td> | ||

| + | <td>{{intel|Willamette|l=core}} (P4)</td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <th rowspan="2">[[130 nm process|130 nm]]</th> | ||

| + | <td>{{intel|Tualatin|l=core}}</td> | ||

| + | <td rowspan="2">{{intel|Northwood|l=core}} (P4)</td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <td rowspan="4">'''{{intel|Pentium M|l=arch}}'''</td> | ||

| + | <td>{{intel|Banias|l=core}}</td> | ||

| + | <td style="border:none; background-color:var(--background-color-base);"></td> | ||

| + | <th>[[NetBurst]] (HT)</th> | ||

| + | <td style="border:none; background-color:var(--background-color-base);"></td> | ||

| + | <th>NetBurst (×2)</th> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <th rowspan="2">[[90 nm process|90 nm]]</th> | ||

| + | <td rowspan="2">{{intel|Dothan|l=core}}</td> | ||

| + | <td>{{intel|Prescott|l=core}} (P4)</td> | ||

| + | <td style="border:none; background-color:var(--background-color-base); color:var(--color-base);">⇨</td> | ||

| + | <td>Prescott‑2M</td> | ||

| + | <td style="border:none; background-color:var(--background-color-base); color:var(--color-base);">⇨</td> | ||

| + | <td>{{intel|Smithfield|l=core}}</td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <td><s>[[Tejas/Jayhawk]]</s></td> | ||

| + | <td style="border:none; background-color:var(--background-color-base); color:var(--color-base);">→</td> | ||

| + | <td>⇩</td> | ||

| + | <td style="border:none; background-color:var(--background-color-base); color:var(--color-base);">→</td> | ||

| + | <td><s>[[Cedar Mill (Tejas)]]</s></td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <th rowspan="2">[[65 nm process|65 nm]]</th> | ||

| + | <td>[[Yonah]]</td> | ||

| + | <td><s>[[Nehalem]] ([[NetBurst]])</s></td> | ||

| + | <td style="border:none; background-color:var(--background-color-base);"></td> | ||

| + | <td>[[Cedar Mill]] (P4)</td> | ||

| + | <td style="border:none; background-color:var(--background-color-base); color:var(--color-base);">⇨</td> | ||

| + | <td>[[Presler]]</td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <td rowspan="2"><b>{{intel|Core}}</b></td> | ||

| + | <td>[[Merom]]</td> | ||

| + | <td colspan="5" style="text-align:left; color:var(--color-base); border:none; background-color:var(--background-color-base);">4 cores on mainstream desktop, DDR3 introduced</td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <td rowspan="4"><b>Bonnell</b></td> | ||

| + | <td rowspan="2">[[Bonnell]]</td> | ||

| + | <th rowspan="2">[[45 nm process|45 nm]]</th> | ||

| + | <td>[[Penryn]]</td> | ||

| + | <td colspan="5" style="border:none; background-color:var(--background-color-base);"></td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <td rowspan="2"><b>Nehalem</b></td> | ||

| + | <td>[[Nehalem]]</td> | ||

| + | <td colspan="5" style="text-align:left; color:var(--color-base); border:none; background-color:var(--background-color-base);">Hyper-threading reintroduced, integrated Memory controller, <br>PCH, L3-cache introduced, 256KB L2-cache/core</td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <td rowspan="2">[[Saltwell]]</td> | ||

| + | <th rowspan="2">[[32 nm process|32 nm]]</th> | ||

| + | <td>[[Westmere]]</td> | ||

| + | <td colspan="5" style="text-align:left; color:var(--color-base); border:none; background-color:var(--background-color-base);">Introduced GPU on same package and AES-NI</td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <td rowspan="2"><b>Sandy Bridge</b></td> | ||

| + | <td>[[Sandy Bridge]]</td> | ||

| + | <td colspan="5" style="text-align:left; color:var(--color-base); border:none; background-color:var(--background-color-base);">On-die ring bus, no more non-UEFI motherboards</td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <td rowspan="4"><b>Silvermont</b></td> | ||

| + | <td rowspan="2">{{intel|Silvermont|l=arch}}</td> | ||

| + | <th rowspan="2">[[22 nm process|22 nm]]</th> | ||

| + | <td>[[Ivy Bridge]]</td> | ||

| + | <td colspan="5" style="border:none; background-color:var(--background-color-base);"></td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <td rowspan="2"><b>Haswell</b></td> | ||

| + | <td>[[Haswell]]</td> | ||

| + | <td colspan="5" style="text-align:left; color:var(--color-base); border:none; background-color:var(--background-color-base);">Fully integrated voltage regulator</td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <td rowspan="2">{{intel|Airmont|l=arch}}</td> | ||

| + | <th rowspan="9">[[14 nm process|14 nm]]</th> | ||

| + | <td>[[Broadwell]]</td> | ||

| + | <td colspan="5" style="border:none; background-color:var(--background-color-base);"></td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <td rowspan="7"><b>Skylake</b></td> | ||

| + | <td>[[Skylake]]</td> | ||

| + | <td colspan="5" style="text-align:left; color:var(--color-base); border:none; background-color:var(--background-color-base);">DDR4 introduced on mainstream desktop</td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <td rowspan="3"><b>Goldmont</b></td> | ||

| + | <td rowspan="3">[[Goldmont]]</td> | ||

| + | <td>[[Kaby Lake]]</td> | ||

| + | <td colspan="5" style="border:none; background-color:var(--background-color-base);"></td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <td>[[Coffee Lake]]</td> | ||

| + | <td colspan="5" style="text-align:left; color:var(--color-base); border:none; background-color:var(--background-color-base);">6 cores on mainstream desktop</td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <td>[[Amber Lake]]</td> | ||

| + | <td colspan="5" style="text-align:left; color:var(--color-base); border:none; background-color:var(--background-color-base);">Mobile-only</td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <td rowspan="4"><b>Goldmont Plus</b></td> | ||

| + | <td rowspan="4">[[Goldmont Plus]]</td> | ||

| + | <td>[[Whiskey Lake]]</td> | ||

| + | <td colspan="5" style="text-align:left; color:var(--color-base); border:none; background-color:var(--background-color-base);">Mobile-only</td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <td>[[Coffee Lake]] Refresh</td> | ||

| + | <td colspan="5" style="text-align:left; color:var(--color-base); border:none; background-color:var(--background-color-base);">8 cores on mainstream desktop</td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <td>[[Comet Lake]]</td> | ||

| + | <td colspan="5" style="text-align:left; color:var(--color-base); border:none; background-color:var(--background-color-base);">10 cores on mainstream desktop</td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <td><b>{{intel|Rocket Lake|l=arch}}</b></td> | ||

| + | <td>{{intel|Cypress Cove|l=arch}}</td> | ||

| + | <td colspan="5" style="border:none; background-color:var(--background-color-base); text-align:left; color:var(--color-base);">Backported Sunny Cove microarchitecture for 14nm</td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <td rowspan="3"><b>Tremont</b></td> | ||

| + | <td rowspan="3">{{intel|Tremont|l=arch}}<br>({{intel|Lakefield|l=arch}})</td> | ||

| + | <th rowspan="3">[[10 nm process|10 nm]]</th> | ||

| + | <td><b>[[Cannon Lake]]</b></td> | ||

| + | <td>{{intel|Palm Cove|l=arch}}</td> | ||

| + | <td colspan="5" style="text-align:left; color:var(--color-base); border:none; background-color:var(--background-color-base);">Mobile-only</td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <td><b>[[Ice Lake]]</b></td> | ||

| + | <td>[[Sunny Cove]]</td> | ||

| + | <td colspan="5" style="text-align:left; color:var(--color-base); border:none; background-color:var(--background-color-base);">512 KB L2-cache/core</td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <td><b>{{intel|Tiger Lake|l=arch}}</b></td> | ||

| + | <td>{{intel|Willow Cove|l=arch}}</td> | ||

| + | <td colspan="5" style="border:none; background-color:var(--background-color-base); text-align:left; color:var(--color-base);">[[Intel]] X<sup>e</sup> graphics engine</td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <td rowspan="2"><b>Gracemont</b></td> | ||

| + | <td rowspan="2">{{intel|Gracemont|l=arch}}</td> | ||

| + | <th rowspan="2">[[7 nm process|Intel 7]]<br>(10nm ESF)</th> | ||

| + | <td><b>{{intel|Alder Lake|l=arch}}</b></td> | ||

| + | <td>{{intel|Golden Cove|l=arch}}</td> | ||

| + | <td colspan="5" style="border:none; background-color:var(--background-color-base); text-align:left; color:var(--color-base);">Hybrid, DDR5, PCIe 5.0</td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <td><b>{{intel|Raptor Lake|l=arch}}</b></td> | ||

| + | <td>{{intel|Raptor Cove|l=arch}}</td> | ||

| + | <td colspan="5" style="border:none; background-color:var(--background-color-base);"></td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <td><b>Crestmont</b></td> | ||

| + | <td>{{intel|Crestmont|l=arch}}</td> | ||

| + | <th>[[5 nm process|Intel 4]]</th> | ||

| + | <td><b>{{intel|Meteor Lake|l=arch}}</b></td> | ||

| + | <td>{{intel|Redwood Cove|l=arch}}</td> | ||

| + | <td colspan="5" style="border:none; background-color:var(--background-color-base); text-align:left; color:var(--color-base);">Mobile-only, NPU, [[chiplet]] architecture</td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <td rowspan="2"><b>Skymont</b></td> | ||

| + | <td rowspan="2">[[Skymont]]</td> | ||

| + | <th rowspan="2">N3B ([[TSMC]])</th> | ||

| + | <td><b>{{intel|Lunar Lake|l=arch}}</b></td> | ||

| + | <td>{{intel|Lion Cove|l=core}}</td> | ||

| + | <td colspan="5" style="border:none; background-color:var(--background-color-base); text-align:left; color:var(--color-base);">Low power mobile only (9-30W) </td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <td><b>{{intel|Arrow Lake|l=arch}}</b></td> | ||

| + | <td>{{intel|Lion Cove|l=core}}</td> | ||

| + | <td colspan="5" style="border:none; background-color:var(--background-color-base); text-align:left; color:var(--color-base);"></td> | ||

| + | </tr> | ||

| + | <tr> | ||

| + | <td><b>Darkmont</b></td> | ||

| + | <td>{{intel|Darkmont|l=arch}}</td> | ||

| + | <th>18A</th> | ||

| + | <td><b>{{intel|Panther Lake|l=arch}}</b></td> | ||

| + | <td>{{intel|Cougar Cove|l=core}}</td> | ||

| + | <td colspan="5" style="border:none; background-color:var(--background-color-base); text-align:left; color:var(--color-base);"></td> | ||

| + | </tr> | ||

| + | </table> <!-- | ||

| + | <ul style="text-align:left;"> | ||

| + | <li><s>Strike-through</s> indicates cancelled processors | ||

| + | <li>'''Bold names''' are microarchitectures | ||

| + | <li>''Italic names'' are future processors | ||

| + | </ul> --> | ||

| + | }} | ||

| + | |||

| + | [[File:sunny cove roadmap.png]] | ||

| − | + | == See also == | |

| − | * | + | :;[[Intel]] • {{intel|CPUID}} • [[intel/roadmap|Roadmap]] |

| − | + | *{{intel|Atom}} | |

| − | *** {{intel| | + | *{{intel|Core|l=arch}} |

| − | * | + | *{{intel|Celeron}} |

| − | * | + | *{{intel|Pentium}} |

| − | *** {{intel| | + | *{{intel|Xeon}} |

| − | * | + | *[[Lake]] |

| − | * | + | ---- |

| − | + | {| border="0" cellpadding="2" width="100%" | |

| − | *** {{intel| | + | |- |

| − | + | |width="29%" valign="top" align="left"| | |

| − | + | {{intel ice lake core see also}} | |

| − | + | |width="29%" valign="top" align="left"| | |

| + | {{intel cascade lake core see also}} | ||

| + | * '''{{intel|Comet Lake|l=arch}}''' | ||

| + | * '''{{intel|Rocket Lake|l=arch}}''' | ||

| + | |width="42%" valign="top" align="left"| | ||

| + | {{intel kaby lake core see also}} | ||

| + | * '''{{intel|Cooper Lake|l=arch}}''' | ||

| + | ** {{intel|Cooper Lake SP|l=core}} | ||

| + | |} | ||

| + | ---- | ||

| + | {| border="0" cellpadding="2" width="100%" | ||

| + | |- | ||

| + | |width="29%" valign="top" align="left"| | ||

| + | {{intel skylake core see also}} | ||

| + | |width="29%" valign="top" align="left"| | ||

| + | {{intel broadwell core see also}} | ||

| + | |width="42%" valign="top" align="left"| | ||

| + | {{intel cannon lake core see also}} | ||

| + | |} | ||

| + | ---- | ||

| + | {| border="0" cellpadding="2" width="100%" | ||

| + | |- | ||

| + | |width="29%" valign="top" align="left"| | ||

| + | {{intel alder lake core see also}} | ||

| + | * '''{{intel|Tiger Lake|l=arch}}''' | ||

| + | * '''{{intel|Raptor Lake|l=arch}}''' | ||

| + | * '''{{intel|Meteor Lake|l=arch}}''' | ||

| + | |width="29%" valign="top" align="left"| | ||

| + | {{intel sandy bridge core see also}} | ||

| + | * '''{{intel|Ivy Bridge|l=arch}}''' | ||

| + | ** {{intel|Ivy Bridge E|l=core}} | ||

| + | ** {{intel|Ivy Bridge M|l=core}} | ||

| + | |width="42%" valign="top" align="left"| | ||

| + | {{intel coffee lake core see also}} | ||

| + | |} | ||

{{disambig}} | {{disambig}} | ||

Latest revision as of 23:18, 13 May 2025

Overview[edit]

Lake may refer to:

|

|

|

|

|

|

|

Intel CPU Core Roadmap[edit]

- See also: Intel Atom and intel/core

| Intel Atom (ULV) | Node name | Intel Core/Pentium | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Microarch | Core/Step | Microarch | Core/Step | |||||||||

| 600 nm | P6 | Pentium Pro (133 MHz) |

||||||||||

| 500 nm | Pentium Pro (150 MHz) |

|||||||||||

| 350 nm | Pentium Pro (166–200 MHz) |

|||||||||||

| Klamath | ||||||||||||

| 250 nm | Deschutes | |||||||||||

| Katmai | NetBurst | |||||||||||

| 180 nm | Coppermine | Willamette (P4) | ||||||||||

| 130 nm | Tualatin | Northwood (P4) | ||||||||||

| Pentium M | Banias | NetBurst (HT) | NetBurst (×2) | |||||||||

| 90 nm | Dothan | Prescott (P4) | ⇨ | Prescott‑2M | ⇨ | Smithfield | ||||||

| → | ⇩ | → | ||||||||||

| 65 nm | Yonah | Cedar Mill (P4) | ⇨ | Presler | ||||||||

| Core | Merom | 4 cores on mainstream desktop, DDR3 introduced | ||||||||||

| Bonnell | Bonnell | 45 nm | Penryn | |||||||||

| Nehalem | Nehalem | Hyper-threading reintroduced, integrated Memory controller, PCH, L3-cache introduced, 256KB L2-cache/core |

||||||||||

| Saltwell | 32 nm | Westmere | Introduced GPU on same package and AES-NI | |||||||||

| Sandy Bridge | Sandy Bridge | On-die ring bus, no more non-UEFI motherboards | ||||||||||

| Silvermont | Silvermont | 22 nm | Ivy Bridge | |||||||||

| Haswell | Haswell | Fully integrated voltage regulator | ||||||||||

| Airmont | 14 nm | Broadwell | ||||||||||

| Skylake | Skylake | DDR4 introduced on mainstream desktop | ||||||||||

| Goldmont | Goldmont | Kaby Lake | ||||||||||

| Coffee Lake | 6 cores on mainstream desktop | |||||||||||

| Amber Lake | Mobile-only | |||||||||||

| Goldmont Plus | Goldmont Plus | Whiskey Lake | Mobile-only | |||||||||

| Coffee Lake Refresh | 8 cores on mainstream desktop | |||||||||||

| Comet Lake | 10 cores on mainstream desktop | |||||||||||

| Rocket Lake | Cypress Cove | Backported Sunny Cove microarchitecture for 14nm | ||||||||||

| Tremont | Tremont (Lakefield) |

10 nm | Cannon Lake | Palm Cove | Mobile-only | |||||||

| Ice Lake | Sunny Cove | 512 KB L2-cache/core | ||||||||||

| Tiger Lake | Willow Cove | Intel Xe graphics engine | ||||||||||

| Gracemont | Gracemont | Intel 7 (10nm ESF) |

Alder Lake | Golden Cove | Hybrid, DDR5, PCIe 5.0 | |||||||

| Raptor Lake | Raptor Cove | |||||||||||

| Crestmont | Crestmont | Intel 4 | Meteor Lake | Redwood Cove | Mobile-only, NPU, chiplet architecture | |||||||

| Skymont | Skymont | N3B (TSMC) | Lunar Lake | Lion Cove | Low power mobile only (9-30W) | |||||||

| Arrow Lake | Lion Cove | |||||||||||

| Darkmont | Darkmont | 18A | Panther Lake | Cougar Cove | ||||||||

}}

See also[edit]

|

|

|

|

|

|

|

|

|

| This is a disambiguation page used to distinguish between articles with similar names. If an internal link led you here, you may wish to change the link to point directly to the intended article. |