(typo correction) |

(Fixed indentation so bullets appear correctly under "Core" and "Front-end") |

||

| (18 intermediate revisions by 12 users not shown) | |||

| Line 7: | Line 7: | ||

|manufacturer 2=GlobalFoundries | |manufacturer 2=GlobalFoundries | ||

|introduction=October 8, 2020 | |introduction=October 8, 2020 | ||

| − | |process=7nm | + | |process=7nm, 12nm |

|cores=64 | |cores=64 | ||

|cores 2=56 | |cores 2=56 | ||

| Line 53: | Line 53: | ||

|extension 27=UMIP | |extension 27=UMIP | ||

|extension 28=CLZERO | |extension 28=CLZERO | ||

| + | |extension 29=VAES | ||

| + | |extension 30=VPCLMUL | ||

|predecessor=Zen 2 | |predecessor=Zen 2 | ||

|predecessor link=amd/microarchitectures/zen 2 | |predecessor link=amd/microarchitectures/zen 2 | ||

| Line 63: | Line 65: | ||

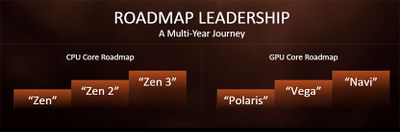

[[File:amd zen future roadmap.jpg|400px|right]] | [[File:amd zen future roadmap.jpg|400px|right]] | ||

Zen 3 was formally disclosed in a roadmap by Lisa Su, AMD's CEO, during AMD's Tech Day in February of 2017. Zen 3 will be the 3rd iteration of the {{\\|Zen}} microarchitecture. On Investor's Day in May 2017 Jim Anderson, AMD Senior Vice President, confirmed that Zen 3 is set to utilize [[7nm+ process]]. | Zen 3 was formally disclosed in a roadmap by Lisa Su, AMD's CEO, during AMD's Tech Day in February of 2017. Zen 3 will be the 3rd iteration of the {{\\|Zen}} microarchitecture. On Investor's Day in May 2017 Jim Anderson, AMD Senior Vice President, confirmed that Zen 3 is set to utilize [[7nm+ process]]. | ||

| + | |||

| + | == Codenames == | ||

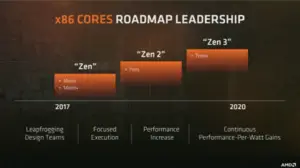

| + | [[File:amd zen2-3 roadmap.png|thumb|right|Zen 3 on the roadmap]] | ||

| + | |||

| + | '''Product Codenames:''' | ||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | ! Core !! C/T !! Target | ||

| + | |- | ||

| + | | {{amd|Milan|l=core}} || Up to 64/128 || High-end server [[multiprocessors]] | ||

| + | |- | ||

| + | | {{amd|Chagall|l=core}} || Up to 64/128 || Workstation & enthusiasts market processors | ||

| + | |- | ||

| + | | {{amd|Vermeer|l=core}} || Up to 16/32 || Mainstream to high-end desktops & enthusiasts market processors | ||

| + | |- | ||

| + | | {{amd|Cezanne|l=core}} || Up to 8/16 || Mainstream APUs with GPUs | ||

| + | |} | ||

| + | |||

| + | '''Architectural Codenames:''' | ||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | ! Arch !! Codename | ||

| + | |- | ||

| + | | Core || Cerebrus | ||

| + | |- | ||

| + | | CCD || Breckenridge | ||

| + | |} | ||

== Products == | == Products == | ||

| − | |||

{{future information}} | {{future information}} | ||

{| class="wikitable" | {| class="wikitable" | ||

|- | |- | ||

| − | ! | + | ! Processor Series !! Cores/Threads !! Market |

|- | |- | ||

| EPYC 7003 "{{amd|Milan|l=core}}" || Up to 64/128 || High-end server [[multiprocessors]] | | EPYC 7003 "{{amd|Milan|l=core}}" || Up to 64/128 || High-end server [[multiprocessors]] | ||

| Line 76: | Line 104: | ||

| {{amd|Trento|l=core}}<!--s/a Milan page--> || ?/? || High-performance computing | | {{amd|Trento|l=core}}<!--s/a Milan page--> || ?/? || High-performance computing | ||

|- | |- | ||

| − | | {{amd| | + | | Ryzen Threadripper 5900 "{{amd|Chagall|l=core}}" || Up to 64/128 || Workstation processors |

|- | |- | ||

| Ryzen 5000 "{{amd|Vermeer|l=core}}" || Up to 16/32 || Mainstream to high-end desktops & enthusiasts market processors | | Ryzen 5000 "{{amd|Vermeer|l=core}}" || Up to 16/32 || Mainstream to high-end desktops & enthusiasts market processors | ||

|- | |- | ||

| − | | Ryzen 5000 APU "{{amd|Cezanne|l=core}}" || Up to 8/16 || Mainstream desktop & mobile processors with GPU | + | | Ryzen 5000 APU "{{amd|Cezanne|l=core}}" || Up to 8/16 || Mainstream desktop & mobile processors with integrated GPU |

|} | |} | ||

== Process technology == | == Process technology == | ||

| − | Zen 3 | + | Zen 3 is fabricated on [[TSMC]]'s [[7 nm process|7nm+ process]] for the Core Compute Die (CCD), the same process used in Zen 2 Refresh processors, as well as [[GlobalFoundries]] [[14 nm process|12nm process]] for the Input/Output Die (IOD). |

| + | |||

| + | Note: Only the APU series of microprocessors retains the monolithic design, so they are fabricated solely on [[TSMC]]'s [[7 nm process|7nm+ process]]. | ||

| + | |||

| + | == Compiler support == | ||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | ! Compiler !! Arch-Specific || Arch-Favorable | ||

| + | |- | ||

| + | | [[GCC]] || <code>-march=znver3</code> || <code>-mtune=znver3</code> | ||

| + | |- | ||

| + | | [[LLVM]] || <code>-march=znver3</code> || <code>-mtune=znver3</code> | ||

| + | |} | ||

| + | * '''Note:''' Initial support in GCC 10.3 and LLVM 12.0. | ||

== Architecture == | == Architecture == | ||

| − | |||

| − | |||

=== Key changes from {{\\|Zen 2}} === | === Key changes from {{\\|Zen 2}} === | ||

| Line 98: | Line 137: | ||

** Higher [[IPC]] (AMD self-reported +19% IPC) | ** Higher [[IPC]] (AMD self-reported +19% IPC) | ||

** Front-end | ** Front-end | ||

| − | ** Increased branch prediction bandwidth | + | *** Increased branch prediction bandwidth |

*** "zero-bubble" branch prediction | *** "zero-bubble" branch prediction | ||

*** L1 BTB doubled from 512 to 1024 entries | *** L1 BTB doubled from 512 to 1024 entries | ||

| − | ** Improved prefetching | + | *** Improved prefetching |

| − | ** Improved µop cache | + | *** Improved µop cache |

| − | * Back-end | + | ** Back-end |

| − | ** Floating point unit: | + | *** Floating point unit: |

| − | *** FMA latency reduced by 1 cycle from 5 to 4. | + | **** FMA latency reduced by 1 cycle from 5 to 4. |

| − | *** Fifth and sixth dedicated execution ports added for floating point store and FP-to-int transfer, no longer sharing 2nd FADD port. | + | **** Fifth and sixth dedicated execution ports added for floating point store and FP-to-int transfer, no longer sharing 2nd FADD port. |

| − | *** Unified scheduler split into 1 scheduler per FMA/FADD/transfer port set. | + | **** Unified scheduler split into 1 scheduler per FMA/FADD/transfer port set. |

| − | *** 256b VAES and VPCLMULDQ support for doubled AES and AES-GCM cryptographic throughput. | + | **** 256b VAES and VPCLMULDQ support for doubled AES and AES-GCM cryptographic throughput. |

| − | *** Hardware implementation of BMI2 PDEP/PEXT bit scatter/gather operations, compared to prior microcode emulation. | + | **** Hardware implementation of BMI2 PDEP/PEXT bit scatter/gather operations, compared to prior microcode emulation. |

| − | ** Integer unit: | + | *** Integer unit: |

| − | *** Integer physical register file increased from 180 to 192 entries | + | **** Integer physical register file increased from 180 to 192 entries |

| − | *** Issue increased from 7 (existing 4 ALU and 3 AGU) to 10 with 1 new dedicated branch execution port and 2 separated store data pathways. | + | **** Issue increased from 7 (existing 4 ALU and 3 AGU) to 10 with 1 new dedicated branch execution port and 2 separated store data pathways. |

| − | *** Schedulers shared between pairs of ALU + AGU/branch ports instead of dedicated for each. | + | **** Schedulers shared between pairs of ALU + AGU/branch ports instead of dedicated for each. |

| − | *** Instruction redundancy increased between ports for reduced bottlenecking on a wider variety of instruction streams. | + | **** Instruction redundancy increased between ports for reduced bottlenecking on a wider variety of instruction streams. |

| − | *** 8/16/32/64 bit signed integer division/modulo latency improved from 17/22/30/46 cycles to 10/12/14/20. (Unsigned operations are ~1 cycle faster for some of both old/new cases.) Throughput improves proportionately. | + | **** 8/16/32/64 bit signed integer division/modulo latency improved from 17/22/30/46 cycles to 10/12/14/20. (Unsigned operations are ~1 cycle faster for some of both old/new cases.) Throughput improves proportionately. |

| − | ** Load/store: | + | *** Load/store: |

| − | *** Load throughput increased from 2 to 3, if not 256b. | + | **** Load throughput increased from 2 to 3, if not 256b. |

| − | *** Store throughput increased from 1 to 2, if not 256b. | + | **** Store throughput increased from 1 to 2, if not 256b. |

| − | *** Store queue increase from 48 to 64 slots. | + | **** Store queue increase from 48 to 64 slots. |

| − | *** Page table walkers tripled from 2 to 6 for TLB miss handling. | + | **** Page table walkers tripled from 2 to 6 for TLB miss handling. |

{{expand list}} | {{expand list}} | ||

| Line 134: | Line 173: | ||

* {{x86|PCID}} - Process Context Identifiers | * {{x86|PCID}} - Process Context Identifiers | ||

** <code>{{x86|INVPCID}}</code> - Invalidate TLB entry(s) in a specified PCID | ** <code>{{x86|INVPCID}}</code> - Invalidate TLB entry(s) in a specified PCID | ||

| − | * | + | * {{x86|INVLPGB}} - Broadcast TLB flushing |

| + | ** <code>INVLPGB</code> - Invalidate TLB entry(s) with broadcast to all processors | ||

** <code>TLBSYNC</code> - Synchronize TLB invalidations | ** <code>TLBSYNC</code> - Synchronize TLB invalidations | ||

* {{x86|PKU}} - Memory Protection Keys for Users | * {{x86|PKU}} - Memory Protection Keys for Users | ||

| Line 143: | Line 183: | ||

* {{x86|SME|SEV-SNP}} - 3rd generation Secure Encrypted Virtualization - Secure Nested Paging | * {{x86|SME|SEV-SNP}} - 3rd generation Secure Encrypted Virtualization - Secure Nested Paging | ||

** <code>PSMASH</code>, <code>PVALIDATE</code>, <code>RMPADJUST</code>, <code>RMPUPDATE</code> | ** <code>PSMASH</code>, <code>PVALIDATE</code>, <code>RMPADJUST</code>, <code>RMPUPDATE</code> | ||

| − | * {{x86|PSFD}} - Predictive Store Forwarding Disable (Speculation Control MSR)<ref name="amd-psf" | + | * {{x86|PSFD}} - Predictive Store Forwarding Disable (Speculation Control MSR)<ref name="amd-psf"/> |

| − | Sources:<ref name="amd-24593-apm2" | + | Sources: <ref name="amd-24593-apm2"/><ref name="amd-24594-apm3"/><ref name="amd-26568-apm4"/> |

=== Memory Hierarchy === | === Memory Hierarchy === | ||

| Line 170: | Line 210: | ||

** Inclusive of L1 | ** Inclusive of L1 | ||

** ≥ 12 cycles latency | ** ≥ 12 cycles latency | ||

| − | ** ECC | + | ** {{abbr|DEC-TED}} ECC, tag & state arrays {{abbr|SEC-DED}}<!--7 check bits for 42 tag bits; AMD-55898-0.50 Sec 3.5--> |

* L3 Cache: | * L3 Cache: | ||

| − | ** "{{amd|Milan|l=core}}": 32 MiB/CCX, up to 256 MiB total | + | ** "{{amd|Milan|l=core}}" & "{{amd|Chagall|l=core}}": 32 MiB/CCX, up to 256 MiB total |

** "{{amd|Vermeer|l=core}}": 32 MiB/CCX, up to 64 MiB total | ** "{{amd|Vermeer|l=core}}": 32 MiB/CCX, up to 64 MiB total | ||

| − | ** "{{amd|Cezanne|l=core}}": 16 MiB, | + | ** "{{amd|Cezanne|l=core}}": 16 MiB, 8 MiB usable on some SKUs |

| − | ** Shared by all cores in the CCX, configurable<ref name="amd-56375-qos" | + | ** Shared by all cores in the {{abbr|CCX}}, configurable<ref name="amd-56375-qos"/> |

** 16-way set associative | ** 16-way set associative | ||

** 64 B line size | ** 64 B line size | ||

| Line 181: | Line 221: | ||

** Write-back policy | ** Write-back policy | ||

** 46 cycles average load-to-use latency | ** 46 cycles average load-to-use latency | ||

| − | ** ECC | + | ** DEC-TED ECC, tag array & shadow tags SEC-DED<!--AMD-55898-0.50 Sec 3.5--> |

** QoS Monitoring and Enforcement V2.0 | ** QoS Monitoring and Enforcement V2.0 | ||

| Line 200: | Line 240: | ||

==== System DRAM ==== | ==== System DRAM ==== | ||

* EPYC 7003 "{{amd|Milan|l=core}}": | * EPYC 7003 "{{amd|Milan|l=core}}": | ||

| − | ** 8 channels per socket, up to 16 DIMMs, max. 4 TiB | + | ** 8 channels per socket, up to 16 DIMMs, max. 4 TiB |

| − | ** Up to PC4-25600L (DDR4-3200) | + | ** Up to PC4-25600L (DDR4-3200) |

| − | ** SR/DR RDIMM, 4R/8R LRDIMM, 3DS DIMM, NVDIMM-N | + | ** {{abbr|SR}}/{{abbr|DR}} {{abbr|RDIMM}}, {{abbr|4R}}/{{abbr|8R}} {{abbr|LRDIMM}}, {{abbr|3DS DIMM}}, {{abbr|NVDIMM-N}} |

| + | ** ECC supported (x4, x8, x16, chipkill)<!--AMD-55898-0.50 Sec 3.7--> | ||

| + | ** DRAM bus parity and write data CRC options<!--ibid--> | ||

| + | |||

| + | * Ryzen Threadripper 5900 "{{amd|Chagall|l=core}}": | ||

| + | ** 8 channels, up to 8 DIMMs, max. 2 TiB | ||

| + | ** Up to PC4-25600L (DDR4-3200) | ||

| + | ** SR/DR {{abbr|UDIMM}}, RDIMM, LRDIMM, 3DS DIMM | ||

| + | ** ECC supported | ||

| + | |||

* Ryzen 5000 "{{amd|Vermeer|l=core}}": | * Ryzen 5000 "{{amd|Vermeer|l=core}}": | ||

| + | ** 2 channels, up to 4 DIMMs, max. 128 GiB | ||

| + | ** Up to PC4-25600U (DDR4-3200 UDIMM), ECC supported | ||

| + | |||

* Ryzen 5000 APU "{{amd|Cezanne|l=core}}": | * Ryzen 5000 APU "{{amd|Cezanne|l=core}}": | ||

| + | ** {{amd|Socket AM4|l=pack}}: | ||

| + | *** 2 channels, up to 4 DIMMs, max. 128 GiB | ||

| + | *** Up to PC4-25600U (DDR4-3200 UDIMM), ECC supported ("PRO" models) | ||

| + | ** {{amd|FP6|FP6 package|l=pack}}, DDR4 mode: | ||

| + | *** 2 × 64-bit channels, up to 2 DIMMs, max. 64 GiB | ||

| + | *** Up to PC4-25600U (DDR4-3200 UDIMM), ECC supported(?) | ||

| + | ** FP6 package, LPDDR4 mode: | ||

| + | *** 4 × 32-bit channels, max. 32 GiB | ||

| + | *** Up to LPDDR4X-4266 | ||

| − | Sources:<ref name="amd-56375-qos"/><ref name="amd-56665-sog-19h"> | + | Sources: <ref name="amd-56375-qos"/><ref name="amd-56665-sog-19h"/><ref name="amd-55898-ppr-1901-0.35"/><ref name="amd-55898-ppr-1901-0.50"/><ref name="amd-56178-mdg-fp6"/> |

== All Zen 3 Chips == | == All Zen 3 Chips == | ||

| Line 288: | Line 349: | ||

== References == | == References == | ||

| − | <references/> | + | <references> |

| + | <ref name="amd-psf">{{cite techdoc|title=White Paper: Security Analysis of AMD Predictive Store Forwarding|url=https://www.amd.com/system/files/documents/security-analysis-predictive-store-forwarding.pdf|publ=AMD|date=2021-03}}</ref> | ||

| + | <ref name="amd-24593-apm2">{{cite techdoc|title=AMD64 Architecture Programmer’s Manual Volume 2: System Programming|url=https://www.amd.com/system/files/TechDocs/24593.pdf|publ=AMD|pid=24593|rev=3.37|date=2021-03}}</ref> | ||

| + | <ref name="amd-24594-apm3">{{cite techdoc|title=AMD64 Architecture Programmer’s Manual Volume 3: General-Purpose and System Instructions|url=https://www.amd.com/system/files/TechDocs/24594.pdf|publ=AMD|pid=24594|rev=3.32|date=2021-03}}</ref> | ||

| + | <ref name="amd-26568-apm4">{{cite techdoc|title=AMD64 Architecture Programmer’s Manual Volume 4: 128-Bit and 256-Bit Media Instructions|url=https://www.amd.com/system/files/TechDocs/26568.pdf|publ=AMD|pid=26568|rev=3.24|date=2020-05}}</ref> | ||

| + | <ref name="amd-56375-qos">{{cite techdoc|title=AMD64 Technology Platform Quality of Service Extensions|url=https://developer.amd.com/wp-content/resources/56375.pdf|publ=AMD|pid=56375|rev=1.02|date=2020-10}}</ref> | ||

| + | <ref name="amd-56665-sog-19h">{{cite techdoc|title=Software Optimization Guide for AMD Family 19h Processors (PUB)|url=https://www.amd.com/system/files/TechDocs/56665.zip|publ=AMD|pid=56665|rev=3.00|date=2020-11}}</ref> | ||

| + | <ref name="amd-55898-ppr-1901-0.35">{{cite techdoc|title=Preliminary Processor Programming Reference (PPR) for AMD Family 19h Model 01h, Revision B1 Processors|url=https://www.amd.com/system/files/TechDocs/55898_pub.zip|publ=AMD|pid=55898|rev=0.35|date=2021-02-05}}</ref> | ||

| + | <ref name="amd-55898-ppr-1901-0.50">{{cite techdoc|title=Preliminary Processor Programming Reference (PPR) for AMD Family 19h Model 01h, Revision B1 Processors|publ=AMD|pid=55898|rev=0.50|date=2021-05-27}}</ref> | ||

| + | <ref name="amd-56178-mdg-fp6">{{cite techdoc|title=FP6 Processor Motherboard Design Guide|publ=AMD|pid=56178|rev=1.03|date=2020-01}}</ref> | ||

| + | </references> | ||

== See Also == | == See Also == | ||

| − | * AMD {{\\|Zen}}, {{\\|Zen 2}} | + | * AMD {{\\|Zen}}, {{\\|Zen 2}}, {{\\|Zen 4}} |

* Intel {{intel|Tigerlake|l=arch}} | * Intel {{intel|Tigerlake|l=arch}} | ||

* Read also: [https://www.anandtech.com/print/16214/amd-zen-3-ryzen-deep-dive-review-5950x-5900x-5800x-and-5700x-tested AMD Zen 3 Ryzen Deep Dive Review] | * Read also: [https://www.anandtech.com/print/16214/amd-zen-3-ryzen-deep-dive-review-5950x-5900x-5800x-and-5700x-tested AMD Zen 3 Ryzen Deep Dive Review] | ||

* Read here: [https://techmotherboard.com/best-zen-3-cpu/ AMD Zen 3 Reviews] | * Read here: [https://techmotherboard.com/best-zen-3-cpu/ AMD Zen 3 Reviews] | ||

Revision as of 22:13, 6 April 2023

| Edit Values | |

| Zen 3 µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | AMD |

| Manufacturer | TSMC, GlobalFoundries |

| Introduction | October 8, 2020 |

| Process | 7nm, 12nm |

| Core Configs | 64, 56, 48, 32, 28, 24, 16, 12, 8, 6 |

| Pipeline | |

| Type | Superscalar |

| OoOE | Yes |

| Speculative | Yes |

| Reg Renaming | Yes |

| Stages | 19 |

| Decode | 4-way |

| Instructions | |

| ISA | x86-64 |

| Extensions | MOVBE, MMX, SSE, SSE2, SSE3, SSSE3, SSE4A, SSE4.1, SSE4.2, POPCNT, AVX, AVX2, AES, PCLMUL, FSGSBASE, RDRND, FMA3, F16C, BMI, BMI2, RDSEED, ADCX, PREFETCHW, CLFLUSHOPT, XSAVE, SHA, UMIP, CLZERO, VAES, VPCLMUL |

| Succession | |

Zen 3 is a microarchitecture developed by AMD as a successor to Zen 2. It was publicly released on October 8, 2020. Mainstream Desktop processors hit shelves on November 5, 2020.

Contents

[hide]History

Zen 3 was formally disclosed in a roadmap by Lisa Su, AMD's CEO, during AMD's Tech Day in February of 2017. Zen 3 will be the 3rd iteration of the Zen microarchitecture. On Investor's Day in May 2017 Jim Anderson, AMD Senior Vice President, confirmed that Zen 3 is set to utilize 7nm+ process.

Codenames

Product Codenames:

| Core | C/T | Target |

|---|---|---|

| Milan | Up to 64/128 | High-end server multiprocessors |

| Chagall | Up to 64/128 | Workstation & enthusiasts market processors |

| Vermeer | Up to 16/32 | Mainstream to high-end desktops & enthusiasts market processors |

| Cezanne | Up to 8/16 | Mainstream APUs with GPUs |

Architectural Codenames:

| Arch | Codename |

|---|---|

| Core | Cerebrus |

| CCD | Breckenridge |

Products

| Processor Series | Cores/Threads | Market |

|---|---|---|

| EPYC 7003 "Milan" | Up to 64/128 | High-end server multiprocessors |

| Trento | ?/? | High-performance computing |

| Ryzen Threadripper 5900 "Chagall" | Up to 64/128 | Workstation processors |

| Ryzen 5000 "Vermeer" | Up to 16/32 | Mainstream to high-end desktops & enthusiasts market processors |

| Ryzen 5000 APU "Cezanne" | Up to 8/16 | Mainstream desktop & mobile processors with integrated GPU |

Process technology

Zen 3 is fabricated on TSMC's 7nm+ process for the Core Compute Die (CCD), the same process used in Zen 2 Refresh processors, as well as GlobalFoundries 12nm process for the Input/Output Die (IOD).

Note: Only the APU series of microprocessors retains the monolithic design, so they are fabricated solely on TSMC's 7nm+ process.

Compiler support

| Compiler | Arch-Specific | Arch-Favorable |

|---|---|---|

| GCC | -march=znver3 |

-mtune=znver3

|

| LLVM | -march=znver3 |

-mtune=znver3

|

- Note: Initial support in GCC 10.3 and LLVM 12.0.

Architecture

Key changes from Zen 2

- CCD

- Unified 8-core CCX (from 2x 4-Core CCX per CCD)

- 32 MiB L3$ available equally to all cores in CCD.

- Increased L3 latency (~46 cycles, up from ~40 cycles)

- Core

- Higher IPC (AMD self-reported +19% IPC)

- Front-end

- Increased branch prediction bandwidth

- "zero-bubble" branch prediction

- L1 BTB doubled from 512 to 1024 entries

- Improved prefetching

- Improved µop cache

- Back-end

- Floating point unit:

- FMA latency reduced by 1 cycle from 5 to 4.

- Fifth and sixth dedicated execution ports added for floating point store and FP-to-int transfer, no longer sharing 2nd FADD port.

- Unified scheduler split into 1 scheduler per FMA/FADD/transfer port set.

- 256b VAES and VPCLMULDQ support for doubled AES and AES-GCM cryptographic throughput.

- Hardware implementation of BMI2 PDEP/PEXT bit scatter/gather operations, compared to prior microcode emulation.

- Integer unit:

- Integer physical register file increased from 180 to 192 entries

- Issue increased from 7 (existing 4 ALU and 3 AGU) to 10 with 1 new dedicated branch execution port and 2 separated store data pathways.

- Schedulers shared between pairs of ALU + AGU/branch ports instead of dedicated for each.

- Instruction redundancy increased between ports for reduced bottlenecking on a wider variety of instruction streams.

- 8/16/32/64 bit signed integer division/modulo latency improved from 17/22/30/46 cycles to 10/12/14/20. (Unsigned operations are ~1 cycle faster for some of both old/new cases.) Throughput improves proportionately.

- Load/store:

- Load throughput increased from 2 to 3, if not 256b.

- Store throughput increased from 1 to 2, if not 256b.

- Store queue increase from 48 to 64 slots.

- Page table walkers tripled from 2 to 6 for TLB miss handling.

- Floating point unit:

This list is incomplete; you can help by expanding it.

New Instructions

Zen 3 introduced the following ISA enhancements:

- VAES - 256-bit Vector AES instructions

-

VAESDEC- AES Decryption Round -

VAESDECLAST- AES Last Decryption Round -

VAESENC- AES Encryption Round -

VAESENCLAST- AES Last Encryption Round

-

-

VPCLMULQDQ- 256-bit Vector Carry-Less Multiplication of Quadwords - PCID - Process Context Identifiers

-

INVPCID- Invalidate TLB entry(s) in a specified PCID

-

- INVLPGB - Broadcast TLB flushing

-

INVLPGB- Invalidate TLB entry(s) with broadcast to all processors -

TLBSYNC- Synchronize TLB invalidations

-

- PKU - Memory Protection Keys for Users

-

RDPKRU- Read Protection Key Rights -

WRPKRU- Write Protection Key Rights

-

- CET_SS - Control-flow Enforcement Technology / Shadow Stack

-

CLRSSBSY,INCSSP,RDSSP,RSTORSSP,SAVEPREVSSP,SETSSBSY,WRSS,WRUSS

-

- SEV-SNP - 3rd generation Secure Encrypted Virtualization - Secure Nested Paging

-

PSMASH,PVALIDATE,RMPADJUST,RMPUPDATE

-

- PSFD - Predictive Store Forwarding Disable (Speculation Control MSR)[1]

Memory Hierarchy

Data and Instruction Caches

- L0 Op Cache:

- 4,096 Ops per core, 8-way set associative

- 8 Op line size

- Parity protected

- L1I Cache:

- 32 KiB per core, 8-way set associative

- 64 B line size

- Parity protected

- L1D Cache:

- 32 KiB per core, 8-way set associative

- 64 B line size

- Write-back policy

- 4-5 cycles latency for Int

- 7-8 cycles latency for FP

- ECC

- L2 Cache:

- 512 KiB per core, 8-way set associative

- 64 B line size

- Write-back policy

- Inclusive of L1

- ≥ 12 cycles latency

- DEC-TED ECC, tag & state arrays SEC-DED

- L3 Cache:

- "Milan" & "Chagall": 32 MiB/CCX, up to 256 MiB total

- "Vermeer": 32 MiB/CCX, up to 64 MiB total

- "Cezanne": 16 MiB, 8 MiB usable on some SKUs

- Shared by all cores in the CCX, configurable[5]

- 16-way set associative

- 64 B line size

- L2 victim cache

- Write-back policy

- 46 cycles average load-to-use latency

- DEC-TED ECC, tag array & shadow tags SEC-DED

- QoS Monitoring and Enforcement V2.0

Translation Lookaside Buffers

- ITLB

- 64 entry L1 TLB, fully associative, all page sizes

- 512 entry L2 TLB, 8-way set associative

- 4-Kbyte and 2-Mbyte pages

- Parity protected

- DTLB

- 64 entry L1 TLB, fully associative, all page sizes

- 2,048 entry L2 TLB, 16-way set associative

- 4-Kbyte and 2-Mbyte pages, PDEs to speed up table walks

- Parity protected

All caches and TLBs are competitively shared in multi-threaded mode.

System DRAM

- EPYC 7003 "Milan":

- Ryzen Threadripper 5900 "Chagall":

- 8 channels, up to 8 DIMMs, max. 2 TiB

- Up to PC4-25600L (DDR4-3200)

- SR/DR UDIMM, RDIMM, LRDIMM, 3DS DIMM

- ECC supported

- Ryzen 5000 "Vermeer":

- 2 channels, up to 4 DIMMs, max. 128 GiB

- Up to PC4-25600U (DDR4-3200 UDIMM), ECC supported

- Ryzen 5000 APU "Cezanne":

- Socket AM4:

- 2 channels, up to 4 DIMMs, max. 128 GiB

- Up to PC4-25600U (DDR4-3200 UDIMM), ECC supported ("PRO" models)

- FP6 package, DDR4 mode:

- 2 × 64-bit channels, up to 2 DIMMs, max. 64 GiB

- Up to PC4-25600U (DDR4-3200 UDIMM), ECC supported(?)

- FP6 package, LPDDR4 mode:

- 4 × 32-bit channels, max. 32 GiB

- Up to LPDDR4X-4266

- Socket AM4:

All Zen 3 Chips

| List of all Zen 3-based Processors | |||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Processor | Features | ||||||||||||||||||||||||

| Model | Price | Process | Launched | Family | Core | C | T | TDP | L3 | Base | Turbo | Max Mem | SMT | SEV | SME | TSME | |||||||||

| Uniprocessors | |||||||||||||||||||||||||

| 7313P | $ 913.00 € 821.70 £ 739.53 ¥ 94,340.29 | 15 March 2021 | EPYC | Milan | 16 | 32 | 155 W 155,000 mW 0.208 hp 0.155 kW | 128 MiB 131,072 KiB 134,217,728 B 0.125 GiB | 3 GHz 3,000 MHz 3,000,000 kHz | 3.7 GHz 3,700 MHz 3,700,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | ||||||||||

| 7443P | $ 1,337.00 € 1,203.30 £ 1,082.97 ¥ 138,152.21 | 15 March 2021 | EPYC | Milan | 24 | 48 | 200 W 200,000 mW 0.268 hp 0.2 kW | 128 MiB 131,072 KiB 134,217,728 B 0.125 GiB | 2.85 GHz 2,850 MHz 2,850,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | ||||||||||

| 7543P | $ 2,730.00 € 2,457.00 £ 2,211.30 ¥ 282,090.90 | 15 March 2021 | EPYC | Milan | 32 | 64 | 225 W 225,000 mW 0.302 hp 0.225 kW | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 2.8 GHz 2,800 MHz 2,800,000 kHz | 3.7 GHz 3,700 MHz 3,700,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | ||||||||||

| 7713P | $ 5,010.00 € 4,509.00 £ 4,058.10 ¥ 517,683.30 | 15 March 2021 | EPYC | Milan | 64 | 128 | 225 W 225,000 mW 0.302 hp 0.225 kW | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 2 GHz 2,000 MHz 2,000,000 kHz | 3.675 GHz 3,675 MHz 3,675,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | ||||||||||

| 5300G | 7 nm 0.007 μm 7.0e-6 mm | 13 April 2021 | Ryzen 3 | Cezanne | 4 | 8 | 65 W 65,000 mW 0.0872 hp 0.065 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 4 GHz 4,000 MHz 4,000,000 kHz | 4.2 GHz 4,200 MHz 4,200,000 kHz | ✔ | ✘ | ✘ | ✘ | |||||||||||

| 5300GE | 7 nm 0.007 μm 7.0e-6 mm | 13 April 2021 | Ryzen 3 | Cezanne | 4 | 8 | 35 W 35,000 mW 0.0469 hp 0.035 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 3.6 GHz 3,600 MHz 3,600,000 kHz | 4.2 GHz 4,200 MHz 4,200,000 kHz | ✔ | ✘ | ✘ | ✘ | |||||||||||

| 5400U | 7 nm 0.007 μm 7.0e-6 mm | 12 January 2021 | Ryzen 3 | Cezanne | 4 | 8 | 15 W 15,000 mW 0.0201 hp 0.015 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 2.6 GHz 2,600 MHz 2,600,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | ✔ | ✘ | ✘ | ✘ | |||||||||||

| PRO 5350G | 7 nm 0.007 μm 7.0e-6 mm | 1 June 2021 | Ryzen 3 | Cezanne | 4 | 8 | 65 W 65,000 mW 0.0872 hp 0.065 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 4 GHz 4,000 MHz 4,000,000 kHz | 4.2 GHz 4,200 MHz 4,200,000 kHz | ✔ | ✘ | ✘ | ✘ | |||||||||||

| PRO 5350GE | 7 nm 0.007 μm 7.0e-6 mm | 1 June 2021 | Ryzen 3 | Cezanne | 4 | 8 | 35 W 35,000 mW 0.0469 hp 0.035 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 3.6 GHz 3,600 MHz 3,600,000 kHz | 4.2 GHz 4,200 MHz 4,200,000 kHz | ✔ | ✘ | ✘ | ✘ | |||||||||||

| PRO 5450U | 7 nm 0.007 μm 7.0e-6 mm | 16 March 2021 | Ryzen 3 | Cezanne | 4 | 8 | 15 W 15,000 mW 0.0201 hp 0.015 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 2.6 GHz 2,600 MHz 2,600,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | ✔ | ✘ | ✘ | ✔ | |||||||||||

| 5600G | $ 259.00 € 233.10 £ 209.79 ¥ 26,762.47 | 7 nm 0.007 μm 7.0e-6 mm | 13 April 2021 | Ryzen 5 | Cezanne | 6 | 12 | 65 W 65,000 mW 0.0872 hp 0.065 kW | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 3.9 GHz 3,900 MHz 3,900,000 kHz | 4.4 GHz 4,400 MHz 4,400,000 kHz | ✔ | ✘ | ✘ | ✘ | ||||||||||

| 5600GE | 7 nm 0.007 μm 7.0e-6 mm | 13 April 2021 | Ryzen 5 | Cezanne | 6 | 12 | 35 W 35,000 mW 0.0469 hp 0.035 kW | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 3.4 GHz 3,400 MHz 3,400,000 kHz | 4.4 GHz 4,400 MHz 4,400,000 kHz | ✔ | ✘ | ✘ | ✘ | |||||||||||

| 5600H | 7 nm 0.007 μm 7.0e-6 mm | 12 January 2021 | Ryzen 5 | Cezanne | 6 | 12 | 45 W 45,000 mW 0.0603 hp 0.045 kW | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 3.3 GHz 3,300 MHz 3,300,000 kHz | 4.2 GHz 4,200 MHz 4,200,000 kHz | ✔ | ✘ | ✘ | ✘ | |||||||||||

| 5600HS | 7 nm 0.007 μm 7.0e-6 mm | 12 January 2021 | Ryzen 5 | Cezanne | 6 | 12 | 35 W 35,000 mW 0.0469 hp 0.035 kW | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 3 GHz 3,000 MHz 3,000,000 kHz | 4.2 GHz 4,200 MHz 4,200,000 kHz | ✔ | ✘ | ✘ | ✘ | |||||||||||

| 5600U | 7 nm 0.007 μm 7.0e-6 mm | 12 January 2021 | Ryzen 5 | Cezanne | 6 | 12 | 15 W 15,000 mW 0.0201 hp 0.015 kW | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 2.3 GHz 2,300 MHz 2,300,000 kHz | 4.2 GHz 4,200 MHz 4,200,000 kHz | ✔ | ✘ | ✘ | ✘ | |||||||||||

| 5600X | $ 299.00 € 269.10 £ 242.19 ¥ 30,895.67 | 7 nm 0.007 μm , 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | 5 November 2020 | Ryzen 5 | Vermeer | 6 | 12 | 65 W 65,000 mW 0.0872 hp 0.065 kW | 32 MiB 32,768 KiB 33,554,432 B 0.0313 GiB | 3.7 GHz 3,700 MHz 3,700,000 kHz | 4.6 GHz 4,600 MHz 4,600,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✔ | ✘ | ✘ | ✘ | |||||||||

| PRO 5650G | 7 nm 0.007 μm 7.0e-6 mm | 1 June 2021 | Ryzen 5 | Cezanne | 6 | 12 | 65 W 65,000 mW 0.0872 hp 0.065 kW | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 3.9 GHz 3,900 MHz 3,900,000 kHz | 4.4 GHz 4,400 MHz 4,400,000 kHz | ✔ | ✘ | ✘ | ✘ | |||||||||||

| PRO 5650GE | 7 nm 0.007 μm 7.0e-6 mm | 1 June 2021 | Ryzen 5 | Cezanne | 6 | 12 | 35 W 35,000 mW 0.0469 hp 0.035 kW | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 3.4 GHz 3,400 MHz 3,400,000 kHz | 4.4 GHz 4,400 MHz 4,400,000 kHz | ✔ | ✘ | ✘ | ✘ | |||||||||||

| PRO 5650U | 7 nm 0.007 μm 7.0e-6 mm | 16 March 2021 | Ryzen 5 | Cezanne | 6 | 12 | 15 W 15,000 mW 0.0201 hp 0.015 kW | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 2.3 GHz 2,300 MHz 2,300,000 kHz | 4.2 GHz 4,200 MHz 4,200,000 kHz | ✔ | ✘ | ✘ | ✔ | |||||||||||

| 5700G | $ 359.00 € 323.10 £ 290.79 ¥ 37,095.47 | 7 nm 0.007 μm 7.0e-6 mm | 13 April 2021 | Ryzen 7 | Cezanne | 8 | 16 | 65 W 65,000 mW 0.0872 hp 0.065 kW | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 3.8 GHz 3,800 MHz 3,800,000 kHz | 4.6 GHz 4,600 MHz 4,600,000 kHz | ✔ | ✘ | ✘ | ✘ | ||||||||||

| 5700GE | 7 nm 0.007 μm 7.0e-6 mm | 13 April 2021 | Ryzen 7 | Cezanne | 8 | 16 | 35 W 35,000 mW 0.0469 hp 0.035 kW | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 3.2 GHz 3,200 MHz 3,200,000 kHz | 4.6 GHz 4,600 MHz 4,600,000 kHz | ✔ | ✘ | ✘ | ✘ | |||||||||||

| 5800 | 7 nm 0.007 μm , 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | 12 January 2021 | Ryzen 7 | Vermeer | 8 | 16 | 65 W 65,000 mW 0.0872 hp 0.065 kW | 32 MiB 32,768 KiB 33,554,432 B 0.0313 GiB | 3.4 GHz 3,400 MHz 3,400,000 kHz | 4.6 GHz 4,600 MHz 4,600,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✔ | ✘ | ✘ | ✘ | ||||||||||

| 5800H | 7 nm 0.007 μm 7.0e-6 mm | 12 January 2021 | Ryzen 7 | Cezanne | 8 | 16 | 45 W 45,000 mW 0.0603 hp 0.045 kW | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 3.2 GHz 3,200 MHz 3,200,000 kHz | 4.4 GHz 4,400 MHz 4,400,000 kHz | ✔ | ✘ | ✘ | ✘ | |||||||||||

| 5800HS | 7 nm 0.007 μm 7.0e-6 mm | 12 January 2021 | Ryzen 7 | Cezanne | 8 | 16 | 35 W 35,000 mW 0.0469 hp 0.035 kW | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 2.8 GHz 2,800 MHz 2,800,000 kHz | 4.4 GHz 4,400 MHz 4,400,000 kHz | ✔ | ✘ | ✘ | ✘ | |||||||||||

| 5800U | 7 nm 0.007 μm 7.0e-6 mm | 12 January 2021 | Ryzen 7 | Cezanne | 8 | 16 | 15 W 15,000 mW 0.0201 hp 0.015 kW | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 1.9 GHz 1,900 MHz 1,900,000 kHz | 4.4 GHz 4,400 MHz 4,400,000 kHz | ✔ | ✘ | ✘ | ✘ | |||||||||||

| 5800X | $ 449.00 € 404.10 £ 363.69 ¥ 46,395.17 | 7 nm 0.007 μm , 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | 5 November 2020 | Ryzen 7 | Vermeer | 8 | 16 | 105 W 105,000 mW 0.141 hp 0.105 kW | 32 MiB 32,768 KiB 33,554,432 B 0.0313 GiB | 3.8 GHz 3,800 MHz 3,800,000 kHz | 4.7 GHz 4,700 MHz 4,700,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✔ | ✘ | ✘ | ✘ | |||||||||

| 5800X3D | $ 449.00 € 404.10 £ 363.69 ¥ 46,395.17 | 7 nm 0.007 μm , 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | 20 April 2022 | Ryzen 7 | Vermeer | 8 | 16 | 105 W 105,000 mW 0.141 hp 0.105 kW | 96 MiB 98,304 KiB 100,663,296 B 0.0938 GiB | 3.4 GHz 3,400 MHz 3,400,000 kHz | 4.5 GHz 4,500 MHz 4,500,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✘ | ✘ | ✘ | ✘ | |||||||||

| PRO 5750G | 7 nm 0.007 μm 7.0e-6 mm | 1 June 2021 | Ryzen 7 | Cezanne | 8 | 16 | 65 W 65,000 mW 0.0872 hp 0.065 kW | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 3.8 GHz 3,800 MHz 3,800,000 kHz | 4.6 GHz 4,600 MHz 4,600,000 kHz | ✔ | ✘ | ✘ | ✘ | |||||||||||

| PRO 5750GE | 7 nm 0.007 μm 7.0e-6 mm | 1 June 2021 | Ryzen 7 | Cezanne | 8 | 16 | 35 W 35,000 mW 0.0469 hp 0.035 kW | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 3.2 GHz 3,200 MHz 3,200,000 kHz | 4.6 GHz 4,600 MHz 4,600,000 kHz | ✔ | ✘ | ✘ | ✘ | |||||||||||

| PRO 5850U | 7 nm 0.007 μm 7.0e-6 mm | 16 March 2021 | Ryzen 7 | Cezanne | 8 | 16 | 15 W 15,000 mW 0.0201 hp 0.015 kW | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 1.9 GHz 1,900 MHz 1,900,000 kHz | 4.4 GHz 4,400 MHz 4,400,000 kHz | ✔ | ✘ | ✘ | ✔ | |||||||||||

| 5900 | 7 nm 0.007 μm , 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | 12 January 2021 | Ryzen 9 | Vermeer | 12 | 24 | 65 W 65,000 mW 0.0872 hp 0.065 kW | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 3 GHz 3,000 MHz 3,000,000 kHz | 4.7 GHz 4,700 MHz 4,700,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✔ | ✘ | ✘ | ✘ | ||||||||||

| 5900HS | 7 nm 0.007 μm 7.0e-6 mm | 12 January 2021 | Ryzen 9 | Cezanne | 8 | 16 | 35 W 35,000 mW 0.0469 hp 0.035 kW | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 3 GHz 3,000 MHz 3,000,000 kHz | 4.6 GHz 4,600 MHz 4,600,000 kHz | ✔ | ✘ | ✘ | ✘ | |||||||||||

| 5900HX | 7 nm 0.007 μm 7.0e-6 mm | 12 January 2021 | Ryzen 9 | Cezanne | 8 | 16 | 45 W 45,000 mW 0.0603 hp 0.045 kW | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 3.3 GHz 3,300 MHz 3,300,000 kHz | 4.6 GHz 4,600 MHz 4,600,000 kHz | ✔ | ✘ | ✘ | ✘ | |||||||||||

| 5900X | $ 549.00 € 494.10 £ 444.69 ¥ 56,728.17 | 7 nm 0.007 μm , 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | 5 November 2020 | Ryzen 9 | Vermeer | 12 | 24 | 105 W 105,000 mW 0.141 hp 0.105 kW | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 3.7 GHz 3,700 MHz 3,700,000 kHz | 4.8 GHz 4,800 MHz 4,800,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✔ | ✘ | ✘ | ✘ | |||||||||

| 5950X | $ 799.00 € 719.10 £ 647.19 ¥ 82,560.67 | 7 nm 0.007 μm , 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | 5 November 2020 | Ryzen 9 | Vermeer | 16 | 32 | 105 W 105,000 mW 0.141 hp 0.105 kW | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 3.4 GHz 3,400 MHz 3,400,000 kHz | 4.9 GHz 4,900 MHz 4,900,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✔ | ✘ | ✘ | ✘ | |||||||||

| 5980HS | 7 nm 0.007 μm 7.0e-6 mm | 12 January 2021 | Ryzen 9 | Cezanne | 8 | 16 | 35 W 35,000 mW 0.0469 hp 0.035 kW | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 3 GHz 3,000 MHz 3,000,000 kHz | 4.8 GHz 4,800 MHz 4,800,000 kHz | ✔ | ✘ | ✘ | ✘ | |||||||||||

| 5980HX | 7 nm 0.007 μm 7.0e-6 mm | 12 January 2021 | Ryzen 9 | Cezanne | 8 | 16 | 45 W 45,000 mW 0.0603 hp 0.045 kW | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 3.3 GHz 3,300 MHz 3,300,000 kHz | 4.8 GHz 4,800 MHz 4,800,000 kHz | ✔ | ✘ | ✘ | ✘ | |||||||||||

| PRO 5945WX | 7 nm 0.007 μm 7.0e-6 mm | 8 March 2022 | Ryzen Threadripper | Chagall | 12 | 24 | 280 W 280,000 mW 0.375 hp 0.28 kW | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 4.1 GHz 4,100 MHz 4,100,000 kHz | 4.5 GHz 4,500 MHz 4,500,000 kHz | 2,048 GiB 2,097,152 MiB 2,147,483,648 KiB 2,199,023,255,552 B 2 TiB | ✔ | ✘ | ✘ | ✔ | ||||||||||

| PRO 5955WX | 7 nm 0.007 μm 7.0e-6 mm | 8 March 2022 | Ryzen Threadripper | Chagall | 16 | 32 | 280 W 280,000 mW 0.375 hp 0.28 kW | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 4 GHz 4,000 MHz 4,000,000 kHz | 4.5 GHz 4,500 MHz 4,500,000 kHz | 2,048 GiB 2,097,152 MiB 2,147,483,648 KiB 2,199,023,255,552 B 2 TiB | ✔ | ✘ | ✘ | ✔ | ||||||||||

| PRO 5965WX | 7 nm 0.007 μm 7.0e-6 mm | 8 March 2022 | Ryzen Threadripper | Chagall | 24 | 48 | 280 W 280,000 mW 0.375 hp 0.28 kW | 128 MiB 131,072 KiB 134,217,728 B 0.125 GiB | 3.8 GHz 3,800 MHz 3,800,000 kHz | 4.5 GHz 4,500 MHz 4,500,000 kHz | 2,048 GiB 2,097,152 MiB 2,147,483,648 KiB 2,199,023,255,552 B 2 TiB | ✔ | ✘ | ✘ | ✔ | ||||||||||

| PRO 5975WX | 7 nm 0.007 μm 7.0e-6 mm | 8 March 2022 | Ryzen Threadripper | Chagall | 32 | 64 | 280 W 280,000 mW 0.375 hp 0.28 kW | 128 MiB 131,072 KiB 134,217,728 B 0.125 GiB | 3.6 GHz 3,600 MHz 3,600,000 kHz | 4.5 GHz 4,500 MHz 4,500,000 kHz | 2,048 GiB 2,097,152 MiB 2,147,483,648 KiB 2,199,023,255,552 B 2 TiB | ✔ | ✘ | ✘ | ✔ | ||||||||||

| PRO 5995WX | 7 nm 0.007 μm 7.0e-6 mm | 8 March 2022 | Ryzen Threadripper | Chagall | 64 | 128 | 280 W 280,000 mW 0.375 hp 0.28 kW | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 2.7 GHz 2,700 MHz 2,700,000 kHz | 4.5 GHz 4,500 MHz 4,500,000 kHz | 2,048 GiB 2,097,152 MiB 2,147,483,648 KiB 2,199,023,255,552 B 2 TiB | ✔ | ✘ | ✘ | ✔ | ||||||||||

| Multiprocessors (dual-socket) | |||||||||||||||||||||||||

| 72F3 | $ 2,468.00 € 2,221.20 £ 1,999.08 ¥ 255,018.44 | 15 March 2021 | EPYC | Milan | 8 | 16 | 180 W 180,000 mW 0.241 hp 0.18 kW | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 3.7 GHz 3,700 MHz 3,700,000 kHz | 4.1 GHz 4,100 MHz 4,100,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | ||||||||||

| 7313 | $ 1,083.00 € 974.70 £ 877.23 ¥ 111,906.39 | 15 March 2021 | EPYC | Milan | 16 | 32 | 155 W 155,000 mW 0.208 hp 0.155 kW | 128 MiB 131,072 KiB 134,217,728 B 0.125 GiB | 3 GHz 3,000 MHz 3,000,000 kHz | 3.7 GHz 3,700 MHz 3,700,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | ||||||||||

| 7343 | $ 1,565.00 € 1,408.50 £ 1,267.65 ¥ 161,711.45 | 15 March 2021 | EPYC | Milan | 16 | 32 | 190 W 190,000 mW 0.255 hp 0.19 kW | 128 MiB 131,072 KiB 134,217,728 B 0.125 GiB | 3.2 GHz 3,200 MHz 3,200,000 kHz | 3.9 GHz 3,900 MHz 3,900,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | ||||||||||

| 73F3 | $ 3,521.00 € 3,168.90 £ 2,852.01 ¥ 363,824.93 | 15 March 2021 | EPYC | Milan | 16 | 32 | 240 W 240,000 mW 0.322 hp 0.24 kW | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 3.5 GHz 3,500 MHz 3,500,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | ||||||||||

| 7413 | $ 1,825.00 € 1,642.50 £ 1,478.25 ¥ 188,577.25 | 15 March 2021 | EPYC | Milan | 24 | 48 | 180 W 180,000 mW 0.241 hp 0.18 kW | 128 MiB 131,072 KiB 134,217,728 B 0.125 GiB | 2.65 GHz 2,650 MHz 2,650,000 kHz | 3.6 GHz 3,600 MHz 3,600,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | ||||||||||

| 7443 | $ 2,010.00 € 1,809.00 £ 1,628.10 ¥ 207,693.30 | 15 March 2021 | EPYC | Milan | 24 | 48 | 200 W 200,000 mW 0.268 hp 0.2 kW | 128 MiB 131,072 KiB 134,217,728 B 0.125 GiB | 2.85 GHz 2,850 MHz 2,850,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | ||||||||||

| 7453 | $ 1,570.00 € 1,413.00 £ 1,271.70 ¥ 162,228.10 | 15 March 2021 | EPYC | Milan | 28 | 56 | 225 W 225,000 mW 0.302 hp 0.225 kW | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 2.75 GHz 2,750 MHz 2,750,000 kHz | 3.45 GHz 3,450 MHz 3,450,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | ||||||||||

| 74F3 | $ 2,900.00 € 2,610.00 £ 2,349.00 ¥ 299,657.00 | 15 March 2021 | EPYC | Milan | 24 | 48 | 240 W 240,000 mW 0.322 hp 0.24 kW | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 3.2 GHz 3,200 MHz 3,200,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | ||||||||||

| 7513 | $ 2,840.00 € 2,556.00 £ 2,300.40 ¥ 293,457.20 | 15 March 2021 | EPYC | Milan | 32 | 64 | 200 W 200,000 mW 0.268 hp 0.2 kW | 128 MiB 131,072 KiB 134,217,728 B 0.125 GiB | 2.6 GHz 2,600 MHz 2,600,000 kHz | 3.65 GHz 3,650 MHz 3,650,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | ||||||||||

| 7543 | $ 3,761.00 € 3,384.90 £ 3,046.41 ¥ 388,624.13 | 15 March 2021 | EPYC | Milan | 32 | 64 | 225 W 225,000 mW 0.302 hp 0.225 kW | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 2.8 GHz 2,800 MHz 2,800,000 kHz | 3.7 GHz 3,700 MHz 3,700,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | ||||||||||

| 75F3 | $ 4,860.00 € 4,374.00 £ 3,936.60 ¥ 502,183.80 | 15 March 2021 | EPYC | Milan | 32 | 64 | 280 W 280,000 mW 0.375 hp 0.28 kW | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 2.95 GHz 2,950 MHz 2,950,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | ||||||||||

| 7643 | $ 4,995.00 € 4,495.50 £ 4,045.95 ¥ 516,133.35 | 15 March 2021 | EPYC | Milan | 48 | 96 | 225 W 225,000 mW 0.302 hp 0.225 kW | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 2.3 GHz 2,300 MHz 2,300,000 kHz | 3.6 GHz 3,600 MHz 3,600,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | ||||||||||

| 7663 | $ 6,366.00 € 5,729.40 £ 5,156.46 ¥ 657,798.78 | 15 March 2021 | EPYC | Milan | 56 | 112 | 240 W 240,000 mW 0.322 hp 0.24 kW | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 2 GHz 2,000 MHz 2,000,000 kHz | 3.5 GHz 3,500 MHz 3,500,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | ||||||||||

| 7713 | $ 7,060.00 € 6,354.00 £ 5,718.60 ¥ 729,509.80 | 15 March 2021 | EPYC | Milan | 64 | 128 | 225 W 225,000 mW 0.302 hp 0.225 kW | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 2 GHz 2,000 MHz 2,000,000 kHz | 3.675 GHz 3,675 MHz 3,675,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | ||||||||||

| 7763 | $ 7,890.00 € 7,101.00 £ 6,390.90 ¥ 815,273.70 | 15 March 2021 | EPYC | Milan | 64 | 128 | 280 W 280,000 mW 0.375 hp 0.28 kW | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 2.45 GHz 2,450 MHz 2,450,000 kHz | 3.5 GHz 3,500 MHz 3,500,000 kHz | 4,096 GiB 4,194,304 MiB 4,294,967,296 KiB 4,398,046,511,104 B 4 TiB | ✔ | ✔ | ✔ | ✔ | ||||||||||

| Count: 57 | |||||||||||||||||||||||||

Designers

- Mark Evers, Chief Architect

Bibliography

- AMD 'Tech Day', February 22, 2017

- AMD 2017 Financial Analyst Day, May 16, 2017

References

- Jump up ↑ "White Paper: Security Analysis of AMD Predictive Store Forwarding", AMD, March 2021

- Jump up ↑ "AMD64 Architecture Programmer’s Manual Volume 2: System Programming", AMD Publ. #24593, Rev. 3.37, March 2021

- Jump up ↑ "AMD64 Architecture Programmer’s Manual Volume 3: General-Purpose and System Instructions", AMD Publ. #24594, Rev. 3.32, March 2021

- Jump up ↑ "AMD64 Architecture Programmer’s Manual Volume 4: 128-Bit and 256-Bit Media Instructions", AMD Publ. #26568, Rev. 3.24, May 2020

- ↑ Jump up to: 5.0 5.1 "AMD64 Technology Platform Quality of Service Extensions", AMD Publ. #56375, Rev. 1.02, October 2020

- Jump up ↑ "Software Optimization Guide for AMD Family 19h Processors (PUB)", AMD Publ. #56665, Rev. 3.00, November 2020

- Jump up ↑ "Preliminary Processor Programming Reference (PPR) for AMD Family 19h Model 01h, Revision B1 Processors", AMD Publ. #55898, Rev. 0.35, February 5, 2021

- Jump up ↑ "Preliminary Processor Programming Reference (PPR) for AMD Family 19h Model 01h, Revision B1 Processors", AMD Publ. #55898, Rev. 0.50, May 27, 2021

- Jump up ↑ "FP6 Processor Motherboard Design Guide", AMD Publ. #56178, Rev. 1.03, January 2020

See Also

- AMD Zen, Zen 2, Zen 4

- Intel Tigerlake

- Read also: AMD Zen 3 Ryzen Deep Dive Review

- Read here: AMD Zen 3 Reviews

| codename | Zen 3 + |

| core count | 64 +, 56 +, 48 +, 32 +, 28 +, 24 +, 16 +, 12 +, 8 + and 6 + |

| designer | AMD + |

| first launched | October 8, 2020 + |

| full page name | amd/microarchitectures/zen 3 + |

| instance of | microarchitecture + |

| instruction set architecture | x86-64 + |

| manufacturer | TSMC + and GlobalFoundries + |

| microarchitecture type | CPU + |

| name | Zen 3 + |

| pipeline stages | 19 + |