(→Individual Core) |

|||

| (96 intermediate revisions by 19 users not shown) | |||

| Line 26: | Line 26: | ||

|stages min=14 | |stages min=14 | ||

|stages max=19 | |stages max=19 | ||

| − | |isa | + | |isa=x86-64 |

| − | |||

| − | |||

|extension=MOVBE | |extension=MOVBE | ||

|extension 2=MMX | |extension 2=MMX | ||

| Line 73: | Line 71: | ||

|l3 desc=11-way set associative | |l3 desc=11-way set associative | ||

|core name=Skylake X | |core name=Skylake X | ||

| − | |core name 2=Skylake SP | + | |core name 2=Skylake W |

| + | |core name 3=Skylake SP | ||

|predecessor=Broadwell | |predecessor=Broadwell | ||

|predecessor link=intel/microarchitectures/broadwell | |predecessor link=intel/microarchitectures/broadwell | ||

| + | |successor=Cascade Lake | ||

| + | |successor link=intel/microarchitectures/cascade lake | ||

| + | |contemporary=Skylake (client) | ||

| + | |contemporary link=intel/microarchitectures/skylake (client) | ||

|pipeline=Yes | |pipeline=Yes | ||

|OoOE=Yes | |OoOE=Yes | ||

| Line 91: | Line 94: | ||

{| class="wikitable" | {| class="wikitable" | ||

|- | |- | ||

| − | ! Core !! Abbrev !! Target | + | ! Core !! Abbrev !! Platform !! Target |

|- | |- | ||

| − | | {{intel|Skylake | + | | {{intel|Skylake SP|l=core}} || SKL-SP || {{intel|Purley|l=platform}} || Server Scalable Processors |

|- | |- | ||

| − | | {{intel|Skylake | + | | {{intel|Skylake X|l=core}} || SKL-X || {{intel|Basin Falls|l=platform}} || High-end desktops & enthusiasts market |

| + | |- | ||

| + | | {{intel|Skylake W|l=core}} || SKL-W || {{intel|Basin Falls|l=platform}} || Enterprise/Business workstations | ||

| + | |- | ||

| + | | {{intel|Skylake DE|l=core}} || SKL-DE || || Dense server/edge computing | ||

|} | |} | ||

| Line 116: | Line 123: | ||

|- | |- | ||

! Cores !! {{intel|Hyper-Threading|HT}} !! {{intel|Turbo Boost|TBT}} !! {{x86|AVX-512}} !! AVX-512 Units !! {{intel|Ultra Path Interconnect|UPI}} links !! Scalability | ! Cores !! {{intel|Hyper-Threading|HT}} !! {{intel|Turbo Boost|TBT}} !! {{x86|AVX-512}} !! AVX-512 Units !! {{intel|Ultra Path Interconnect|UPI}} links !! Scalability | ||

| + | |- | ||

| + | | [[File:xeon logo (2015).png|50px|link=intel/xeon d]] || {{intel|Xeon D}} || style="text-align: left;" | Dense servers / edge computing || [[4 cores|4]]-[[18 cores|18]] || {{tchk|yes}} || {{tchk|yes}} || {{tchk|yes}} || 1 || colspan="2" {{tchk|no}} | ||

| + | |- | ||

| + | | [[File:xeon logo (2015).png|50px|link=intel/xeon w]] || {{intel|Xeon W}} || style="text-align: left;" | Business workstations || [[4 cores|4]]-[[18 cores|18]] || {{tchk|yes}} || {{tchk|yes}} || {{tchk|yes}} || 2 || colspan="2" {{tchk|no}} | ||

|- | |- | ||

| [[File:xeon bronze (2017).png|50px]] || {{intel|Xeon Bronze}} || style="text-align: left;" | Entry-level performance / <br>Cost-sensitive || [[6 cores|6]] - [[8 cores|8]] || {{tchk|no}} || {{tchk|no}} || {{tchk|yes}} || 1 || 2 || Up to 2 | | [[File:xeon bronze (2017).png|50px]] || {{intel|Xeon Bronze}} || style="text-align: left;" | Entry-level performance / <br>Cost-sensitive || [[6 cores|6]] - [[8 cores|8]] || {{tchk|no}} || {{tchk|no}} || {{tchk|yes}} || 1 || 2 || Up to 2 | ||

| Line 132: | Line 143: | ||

== Process Technology == | == Process Technology == | ||

| − | {{main| | + | {{main|14 nm lithography process}} |

| − | Unlike mainstream Skylake models, all Skylake server configuration models are fabricated on Intel's [[14 nm process#Intel|enhanced 14+ nm process]] which is used by {{\\|Kaby Lake}} | + | Unlike mainstream Skylake models, all Skylake server configuration models are fabricated on Intel's [[14 nm process#Intel|enhanced 14+ nm process]] which is used by {{\\|Kaby Lake}}. |

== Compatibility == | == Compatibility == | ||

| Line 150: | Line 161: | ||

|- | |- | ||

| Linux || Linux || style="background-color: #d6ffd8;" | Kernel 3.19 || Initial Support (MPX support) | | Linux || Linux || style="background-color: #d6ffd8;" | Kernel 3.19 || Initial Support (MPX support) | ||

| + | |- | ||

| + | | Apple || macOS || style="background-color: #d6ffd8;" | 10.12.3 || iMac Pro | ||

|} | |} | ||

| Line 170: | Line 183: | ||

! Core !! Extended<br>Family !! Family !! Extended<br>Model !! Model | ! Core !! Extended<br>Family !! Family !! Extended<br>Model !! Model | ||

|- | |- | ||

| − | | rowspan="2" | {{intel|Skylake X|X|l=core}} || | + | | rowspan="2" | {{intel|Skylake X|X|l=core}}, {{intel|Skylake SP|SP|l=core}}, {{intel|Skylake DE|DE|l=core}}, {{intel|Skylake W|W|l=core}} || 0 || 0x6 || 0x5 || 0x5 |

| − | |||

| − | |||

| − | | | ||

| − | | | ||

|- | |- | ||

| colspan="4" | Family 6 Model 85 | | colspan="4" | Family 6 Model 85 | ||

| Line 180: | Line 189: | ||

== Architecture == | == Architecture == | ||

| − | Skylake server configuration introduces a number of significant changes from both Intel's previous microarchitecture, {{\\|Broadwell}}, as well as the {{\\|Skylake (client)}} architecture. Unlike client models, Skylake servers and HEDT models will still incorporate the fully integrated voltage regulator (FIVR) on-die. Those chips also have an entirely new multi-core architecture | + | Skylake server configuration introduces a number of significant changes from both Intel's previous microarchitecture, {{\\|Broadwell}}, as well as the {{\\|Skylake (client)}} architecture. Unlike client models, Skylake servers and HEDT models will still incorporate the fully integrated voltage regulator (FIVR) on-die. Those chips also have an entirely new multi-core system architecture that brought a new {{intel|mesh interconnect}} network (from [[ring topology]]). |

=== Key changes from {{\\|Broadwell}} === | === Key changes from {{\\|Broadwell}} === | ||

| Line 186: | Line 195: | ||

* Improved "14 nm+" process (see {{\\|kaby_lake#Process_Technology|Kaby Lake § Process Technology}}) | * Improved "14 nm+" process (see {{\\|kaby_lake#Process_Technology|Kaby Lake § Process Technology}}) | ||

* {{intel|Omni-Path Architecture}} (OPA) | * {{intel|Omni-Path Architecture}} (OPA) | ||

| − | * Mesh architecture | + | * {{intel|Mesh architecture}} (from {{intel|Ring architecture|ring}}) |

** {{intel|Sub-NUMA Clustering}} (SNC) support (replaces the {{intel|Cluster-on-Die}} (COD) implementation) | ** {{intel|Sub-NUMA Clustering}} (SNC) support (replaces the {{intel|Cluster-on-Die}} (COD) implementation) | ||

* Chipset | * Chipset | ||

| Line 196: | Line 205: | ||

** DMI upgraded to Gen3 | ** DMI upgraded to Gen3 | ||

* Core | * Core | ||

| + | ** All the changes from Skylake Client (For full list, see {{\\|Skylake (Client)#Key changes from Broadwell|Skylake (Client) § Key changes from Broadwell}}) | ||

** Front End | ** Front End | ||

| − | *** LSD is disabled (Likely due to a bug | + | *** LSD is disabled (Likely due to a bug; see [[#Front-end|§ Front-end]] for details) |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

** Back-end | ** Back-end | ||

*** Port 4 now performs 512b stores (from 256b) | *** Port 4 now performs 512b stores (from 256b) | ||

| Line 224: | Line 218: | ||

*** Store is now 64B/cycle (from 32B/cycle) | *** Store is now 64B/cycle (from 32B/cycle) | ||

*** Load is now 2x64B/cycle (from 2x32B/cycle) | *** Load is now 2x64B/cycle (from 2x32B/cycle) | ||

| + | *** New Features | ||

| + | **** Adaptive Double Device Data Correction (ADDDC) | ||

* Memory | * Memory | ||

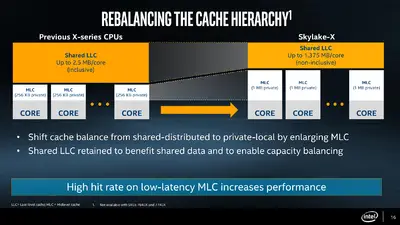

** L2$ | ** L2$ | ||

| − | *** Increased to 1 MiB/core (from | + | *** Increased to 1 MiB/core (from 256 KiB/core) |

| + | *** Latency increased from 12 to 14 | ||

** L3$ | ** L3$ | ||

| − | |||

*** Reduced to 1.375 MiB/core (from 2.5 MiB/core) | *** Reduced to 1.375 MiB/core (from 2.5 MiB/core) | ||

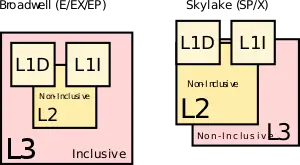

| + | *** Now non-inclusive (was inclusive) | ||

** DRAM | ** DRAM | ||

*** hex-channel DDR4-2666 (from quad-channel) | *** hex-channel DDR4-2666 (from quad-channel) | ||

| − | |||

* TLBs | * TLBs | ||

** ITLB | ** ITLB | ||

| Line 245: | Line 241: | ||

==== CPU changes ==== | ==== CPU changes ==== | ||

| − | + | See {{\\|Skylake (Client)#CPU changes|Skylake (Client) § CPU changes}} | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

====New instructions ==== | ====New instructions ==== | ||

| Line 262: | Line 247: | ||

Skylake server introduced a number of {{x86|extensions|new instructions}}: | Skylake server introduced a number of {{x86|extensions|new instructions}}: | ||

| − | + | * {{x86|MPX|<code>MPX</code>}} - Memory Protection Extensions | |

| − | * {{x86|MPX|<code>MPX</code>}} -Memory Protection Extensions | ||

* {{x86|XSAVEC|<code>XSAVEC</code>}} - Save processor extended states with compaction to memory | * {{x86|XSAVEC|<code>XSAVEC</code>}} - Save processor extended states with compaction to memory | ||

* {{x86|XSAVES|<code>XSAVES</code>}} - Save processor supervisor-mode extended states to memory. | * {{x86|XSAVES|<code>XSAVES</code>}} - Save processor supervisor-mode extended states to memory. | ||

| Line 271: | Line 255: | ||

** {{x86|AVX512CD|<code>AVX512CD</code>}} - AVX-512 Conflict Detection | ** {{x86|AVX512CD|<code>AVX512CD</code>}} - AVX-512 Conflict Detection | ||

** {{x86|AVX512BW|<code>AVX512BW</code>}} - AVX-512 Byte and Word | ** {{x86|AVX512BW|<code>AVX512BW</code>}} - AVX-512 Byte and Word | ||

| − | ** {{x86| | + | ** {{x86|AVX512DQ|<code>AVX512DQ</code>}} - AVX-512 Doubleword and Quadword |

| − | ** {{x86| | + | ** {{x86|AVX512VL|<code>AVX512VL</code>}} - AVX-512 Vector Length |

* {{x86|PKU|<code>PKU</code>}} - Memory Protection Keys for Userspace | * {{x86|PKU|<code>PKU</code>}} - Memory Protection Keys for Userspace | ||

* {{x86|PCOMMIT|<code>PCOMMIT</code>}} - PCOMMIT instruction | * {{x86|PCOMMIT|<code>PCOMMIT</code>}} - PCOMMIT instruction | ||

| − | * {{x86|CLWB|<code>CLWB</code>}} - | + | * {{x86|CLWB|<code>CLWB</code>}} - Force cache line write-back without flush |

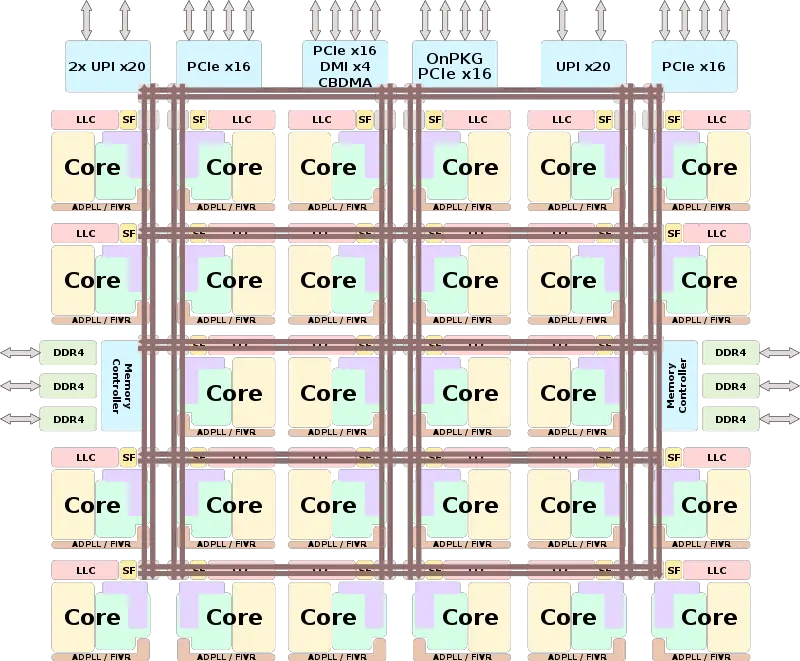

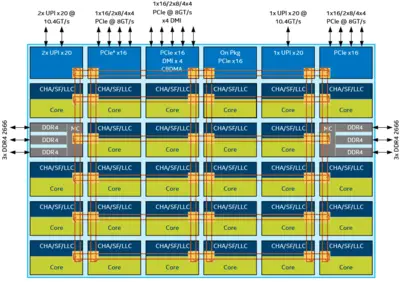

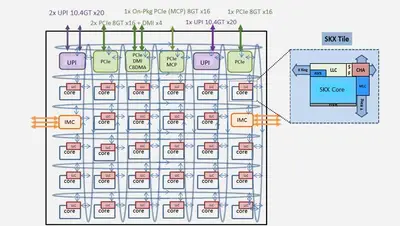

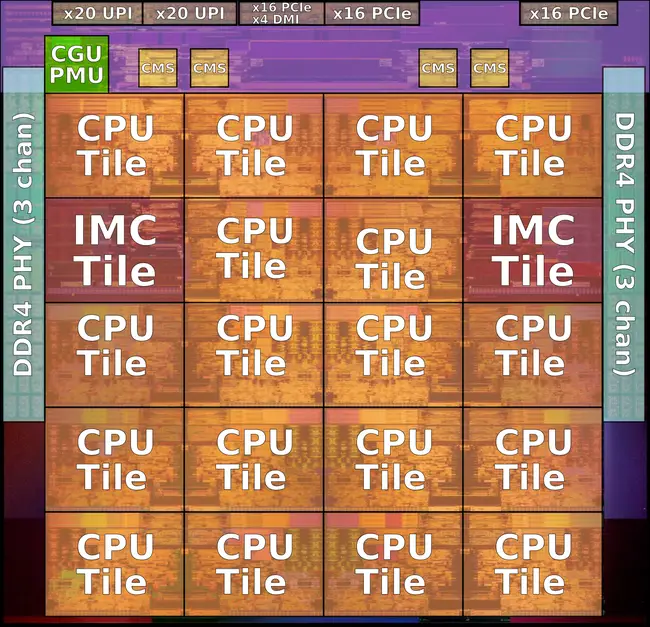

=== Block Diagram === | === Block Diagram === | ||

==== Entire SoC Overview ==== | ==== Entire SoC Overview ==== | ||

| − | + | ===== LCC SoC ===== | |

| − | [[File:skylake sp hcc block diagram.svg| | + | :[[File:skylake sp lcc block diagram.svg|500px]] |

| − | + | ===== HCC SoC ===== | |

| − | + | :[[File:skylake sp hcc block diagram.svg|600px]] | |

| − | + | ===== XCC SoC ===== | |

| − | + | :[[File:skylake sp xcc block diagram.svg|800px]] | |

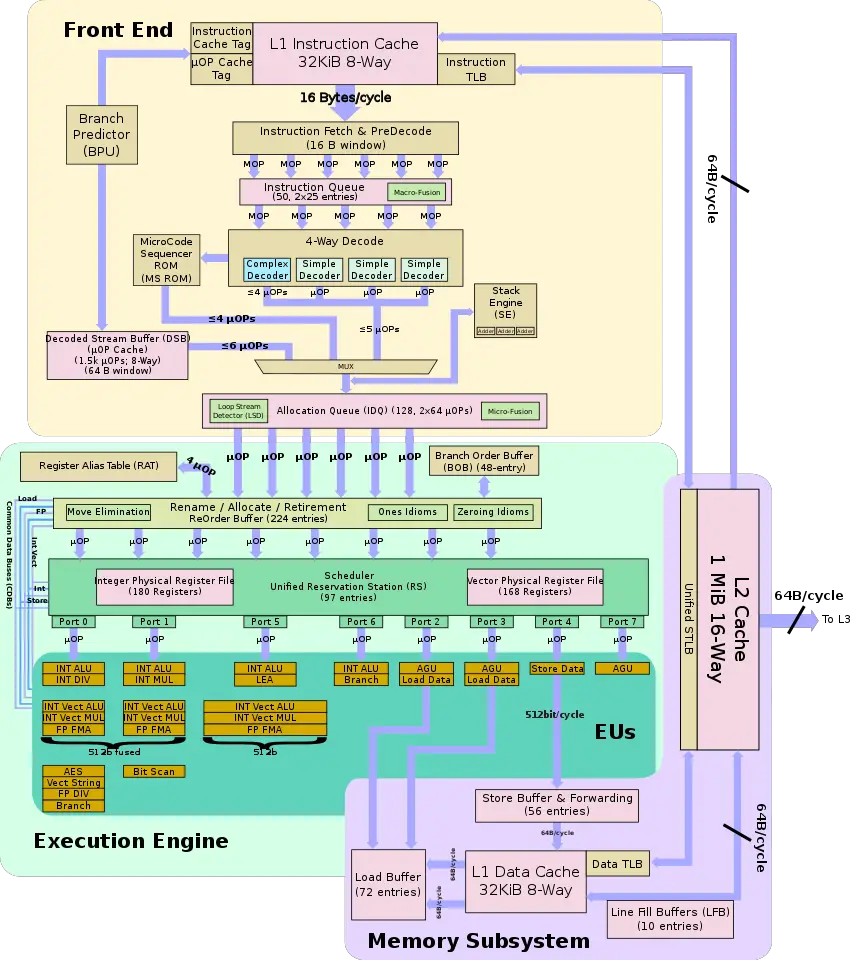

===== Individual Core ===== | ===== Individual Core ===== | ||

| − | [[File:skylake server block diagram.svg| | + | :[[File:skylake server block diagram.svg|850px]] |

=== Memory Hierarchy === | === Memory Hierarchy === | ||

| Line 294: | Line 278: | ||

* Cache | * Cache | ||

** L0 µOP cache: | ** L0 µOP cache: | ||

| − | *** 1,536 µOPs, 8-way set associative | + | *** 1,536 µOPs/core, 8-way set associative |

**** 32 sets, 6-µOP line size | **** 32 sets, 6-µOP line size | ||

| − | **** statically divided between threads | + | **** statically divided between threads, inclusive with L1I |

** L1I Cache: | ** L1I Cache: | ||

| − | *** 32 [[KiB]], 8-way set associative | + | *** 32 [[KiB]]/core, 8-way set associative |

**** 64 sets, 64 B line size | **** 64 sets, 64 B line size | ||

| − | **** shared by the | + | **** competitively shared by the threads/core |

** L1D Cache: | ** L1D Cache: | ||

| − | *** 32 KiB, 8-way set associative | + | *** 32 KiB/core, 8-way set associative |

*** 64 sets, 64 B line size | *** 64 sets, 64 B line size | ||

| − | *** shared by | + | *** competitively shared by threads/core |

*** 4 cycles for fastest load-to-use (simple pointer accesses) | *** 4 cycles for fastest load-to-use (simple pointer accesses) | ||

**** 5 cycles for complex addresses | **** 5 cycles for complex addresses | ||

| Line 311: | Line 295: | ||

*** Write-back policy | *** Write-back policy | ||

** L2 Cache: | ** L2 Cache: | ||

| − | *** | + | *** 1 MiB/core, 16-way set associative |

*** 64 B line size | *** 64 B line size | ||

| − | *** | + | *** Inclusive |

*** 64 B/cycle bandwidth to L1$ | *** 64 B/cycle bandwidth to L1$ | ||

*** Write-back policy | *** Write-back policy | ||

*** 14 cycles latency | *** 14 cycles latency | ||

** L3 Cache: | ** L3 Cache: | ||

| − | *** 1.375 MiB/ | + | *** 1.375 MiB/core, 11-way set associative, shared across all cores |

| − | **** Note that | + | **** Note that a few models have non-default cache sizes due to disabled cores |

| − | *** 64 B line size | + | *** 2,048 sets, 64 B line size |

| − | + | *** Non-inclusive victim cache | |

| − | *** Non- | ||

*** Write-back policy | *** Write-back policy | ||

*** 50-70 cycles latency | *** 50-70 cycles latency | ||

| + | ** Snoop Filter (SF): | ||

| + | *** 2,048 sets, 12-way set associative | ||

| + | * DRAM | ||

| + | ** 6 channels of DDR4, up to 2666 MT/s | ||

| + | *** RDIMM and LRDIMM | ||

| + | *** bandwidth of 21.33 GB/s | ||

| + | *** aggregated bandwidth of 128 GB/s | ||

Skylake TLB consists of dedicated L1 TLB for instruction cache (ITLB) and another one for data cache (DTLB). Additionally there is a unified L2 TLB (STLB). | Skylake TLB consists of dedicated L1 TLB for instruction cache (ITLB) and another one for data cache (DTLB). Additionally there is a unified L2 TLB (STLB). | ||

| Line 343: | Line 333: | ||

**** fixed partition | **** fixed partition | ||

*** 1G page translations: | *** 1G page translations: | ||

| − | **** 4 entries; | + | **** 4 entries; 4-way set associative |

**** fixed partition | **** fixed partition | ||

** STLB | ** STLB | ||

*** 4 KiB + 2 MiB page translations: | *** 4 KiB + 2 MiB page translations: | ||

| − | **** 1536 entries; 12-way set associative | + | **** 1536 entries; 12-way set associative. (Note: STLB is incorrectly reported as "6-way" by CPUID leaf 2 (EAX=02H). Skylake erratum SKL148 recommends software to simply ignore that value.) |

**** fixed partition | **** fixed partition | ||

*** 1 GiB page translations: | *** 1 GiB page translations: | ||

| Line 354: | Line 344: | ||

== Overview == | == Overview == | ||

| − | [[File:skylake | + | [[File:skylake server overview.svg|right|550px]] |

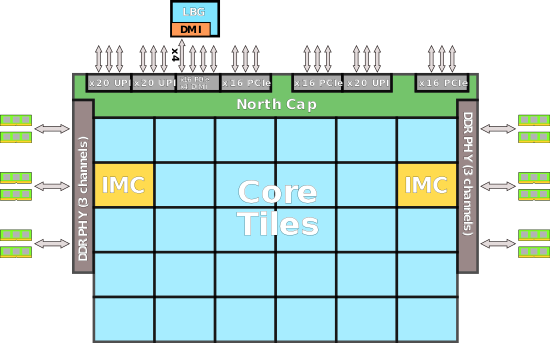

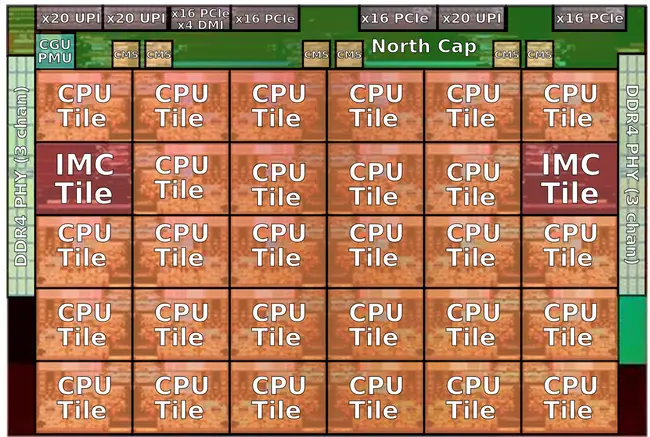

| − | Skylake- | + | The Skylake server architecture marks a significant departure from the previous decade of multi-core system architecture at Intel. Since {{\\|Westmere (server)|Westmere}} Intel has been using a {{intel|ring bus interconnect}} to interlink multiple cores together. As Intel continued to add more I/O, increase the memory bandwidth, and added more cores which increased the data traffic flow, that architecture started to show its weakness. With the introduction of the Skylake server architecture, the interconnect was entirely re-architected to a 2-dimensional {{intel|mesh interconnect}}. |

| + | |||

| + | A superset model is shown on the right. Skylake-based servers are the first mainstream servers to make use of Intel's new {{intel|mesh interconnect}} architecture, an architecture that was previously explored, experimented with, and enhanced with Intel's {{intel|Phi}} [[many-core processors]]. In this configuration, the cores, caches, and the memory controllers are organized in rows and columns - each with dedicated connections going through each of the rows and columns allowing for a shortest path between any tile, reducing latency, and improving the bandwidth. Those processors are offered from [[4 cores]] up to [[28 cores]] with 8 to 56 threads. In addition to the system-level architectural changes, with Skylake, Intel now has a separate core architecture for those chips which incorporate a plethora of new technologies and features including support for the new {{x86|AVX-512}} instruction set extension. | ||

| − | All models incorporate 6 channels of DDR4 supporting up to 12 DIMMS for a total of 768 GiB (with extended models support 1.5 TiB). For I/O all models incorporate 48x (3x16) lanes of PCIe 3.0. There is an additional x4 lanes PCIe 3.0 reserved exclusively for DMI for the the {{intel|Lewisburg|l=chipset}} chipset. For a selected number of models | + | All models incorporate 6 channels of DDR4 supporting up to 12 DIMMS for a total of 768 GiB (with extended models support 1.5 TiB). For I/O all models incorporate 48x (3x16) lanes of PCIe 3.0. There is an additional x4 lanes PCIe 3.0 reserved exclusively for DMI for the the {{intel|Lewisburg|l=chipset}} (LBG) chipset. For a selected number of models, specifically those with ''F'' suffix, they have an {{intel|Omni-Path}} Host Fabric Interface (HFI) on-package (see [[#Integrated_Omni-Path|Integrated Omni-Path]]). |

| − | Skylake processors are designed for scalability, supporting 2-way, 4-way, and 8-way multiprocessing through Intel's new {{intel|Ultra Path Interconnect}} (UPI) interconnect links, with two to three links being offered (see [[#Scalability|§ Scalability]]). High-end models have node controller support allowing higher way (e.g., 32-way multiprocessing). | + | Skylake processors are designed for scalability, supporting 2-way, 4-way, and 8-way multiprocessing through Intel's new {{intel|Ultra Path Interconnect}} (UPI) interconnect links, with two to three links being offered (see [[#Scalability|§ Scalability]]). High-end models have node controller support allowing for even higher way configuration (e.g., 32-way multiprocessing). |

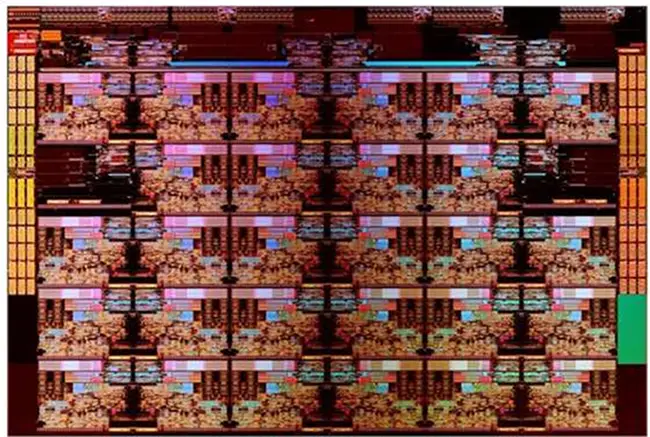

== Core == | == Core == | ||

| Line 372: | Line 364: | ||

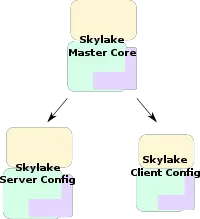

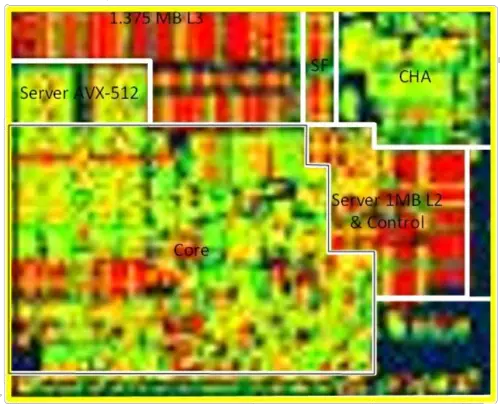

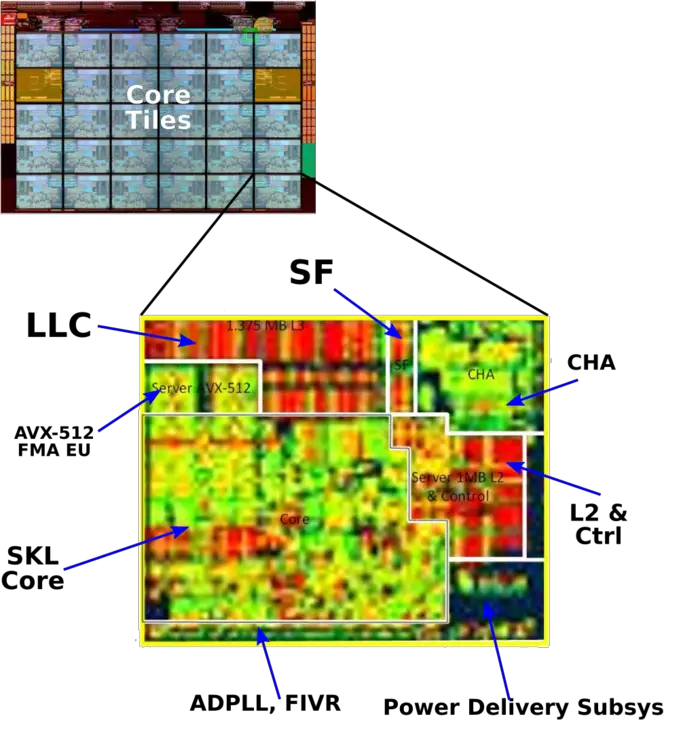

Intel has been experiencing a growing divergence in functionality over the last number of iterations of [[intel/microarchitectures|their microarchitecture]] between their mainstream consumer products and their high-end HPC/server models. Traditionally, Intel has been using the same exact core design for everything from their lowest end value models (e.g. {{intel|Celeron}}) all the way up to the highest-performance enterprise models (e.g. {{intel|Xeon E7}}). While the two have fundamentally different chip architectures, they use the same exact CPU core architecture as the building block. | Intel has been experiencing a growing divergence in functionality over the last number of iterations of [[intel/microarchitectures|their microarchitecture]] between their mainstream consumer products and their high-end HPC/server models. Traditionally, Intel has been using the same exact core design for everything from their lowest end value models (e.g. {{intel|Celeron}}) all the way up to the highest-performance enterprise models (e.g. {{intel|Xeon E7}}). While the two have fundamentally different chip architectures, they use the same exact CPU core architecture as the building block. | ||

| − | This design philosophy has changed with Skylake. In order to better accommodate the different functionalities of each segment without sacrificing features or making unnecessary compromises Intel went with a configurable core. The Skylake core is a single development project, making up a master superset core. The project | + | This design philosophy has changed with Skylake. In order to better accommodate the different functionalities of each segment without sacrificing features or making unnecessary compromises, Intel went with a configurable core. The Skylake core is a single development project, making up a master superset core. The project results in two derivatives: one for servers (the substance of this article) and {{\\|skylake (client)|one for clients}}. All mainstream models (from {{intel|Celeron}}/{{intel|Pentium (2009)|Pentium}} all the way up to {{intel|Core i7}}/{{intel|Xeon E3}}) use {{\\|skylake (client)|the client core configuration}}. Server models (e.g. {{intel|Xeon Gold}}/{{intel|Xeon Platinum}}) are using the new server configuration instead. |

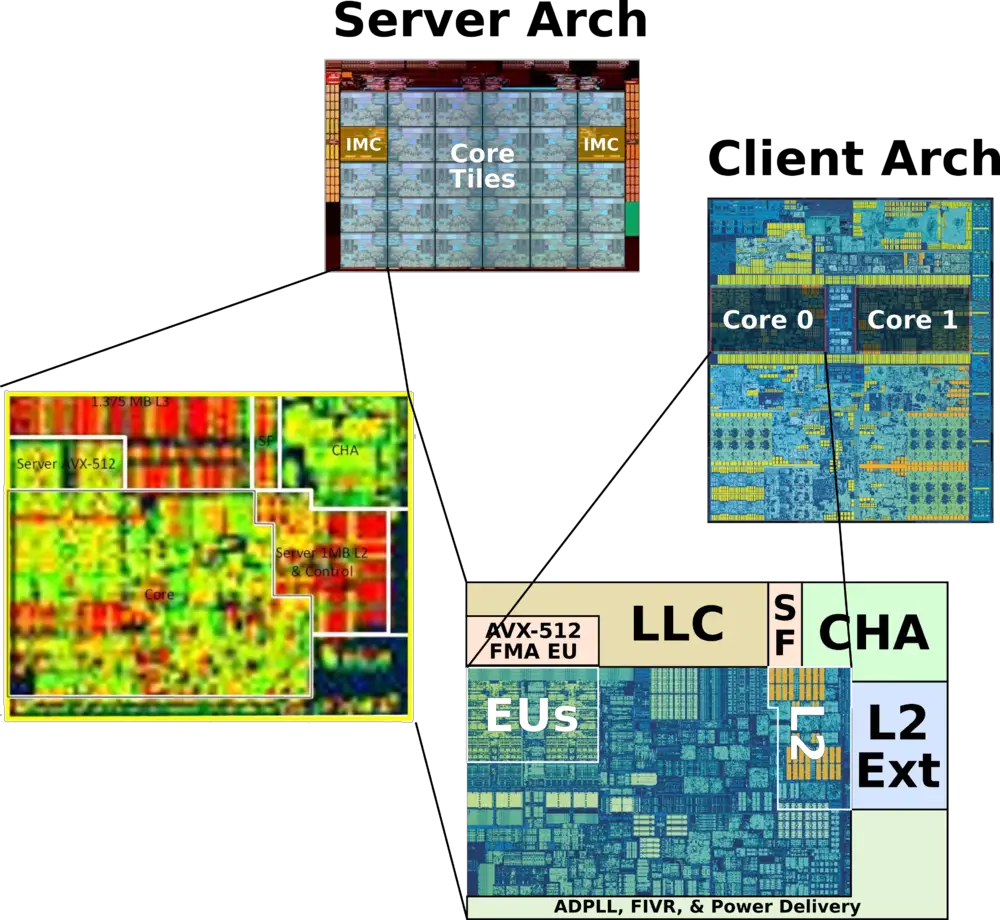

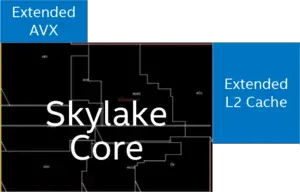

| − | The server core is considerably larger than the client one, featuring [[Advanced Vector Extensions 512]] (AVX-512). Skylake servers support what was formerly called AVX3.2 (AVX512F + AVX512CD + AVX512BW + AVX512DQ + AVX512VL). | + | The server core is considerably larger than the client one, featuring [[Advanced Vector Extensions 512]] (AVX-512). Skylake servers support what was formerly called AVX3.2 (AVX512F + AVX512CD + AVX512BW + AVX512DQ + AVX512VL). The server core also incorporates a number of new technologies not found in the client configuration. In addition to the execution units that were added, the cache hierarchy has changed for the server core as well, incorporating a large L2 and a portion of the LLC as well as the caching and home agent and the snoop filter that needs to accommodate the new cache changes. |

| + | |||

| + | Below is a visual that helps show how the server core was evolved from the client core. | ||

| + | |||

| + | :[[File:skylake sp mesh core tile zoom with client shown.png|1000px]] | ||

=== Pipeline === | === Pipeline === | ||

The Skylake core focuses on extracting performance and reducing power through a number of key ways. Intel builds Skylake on previous microarchitectures, descendants of {{\\|Sandy Bridge}}. For the core to increase the overall performance, Intel focused on extracting additional [[instruction parallelism|parallelism]]. | The Skylake core focuses on extracting performance and reducing power through a number of key ways. Intel builds Skylake on previous microarchitectures, descendants of {{\\|Sandy Bridge}}. For the core to increase the overall performance, Intel focused on extracting additional [[instruction parallelism|parallelism]]. | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

==== Front-end ==== | ==== Front-end ==== | ||

| − | + | For the most part, with the exception of the LSD, the front-end of the Skylake server core is identical to the client configuration. For in-depth detail of the Skylake front-end see {{\\|skylake_(client)#Front-end|Skylake (client) § Front-end}}. | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | The only major difference in the front-end from the client core configuration is the LSD. The Loop Stream Detector (LSD) has been disabled. While the exact reason is not known, it might be related to a severe issue that [https://lists.debian.org/debian-devel/2017/06/msg00308.html was experienced by] the OCaml Development Team. The issue [https://lists.debian.org/debian-devel/2017/06/msg00308.html was patched via microcode] on the client platform, however this change might indicate it was possibly disabled on there as well. The exact implications of this are unknown. | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | The Loop Stream Detector (LSD) has been disabled. While the exact reason is not known, it might be related to a severe issue that [https://lists.debian.org/debian-devel/2017/06/msg00308.html was experienced by] the OCaml Development Team. The issue [https://lists.debian.org/debian-devel/2017/06/msg00308.html was patched via microcode] on the client platform, however this change might indicate it was possibly disabled on there as well. The exact implications of this are unknown. | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

==== Execution engine ==== | ==== Execution engine ==== | ||

| − | + | The Skylake server configuration core back-end is identical to the client configuration up to the scheduler. For in-depth detail of the Skylake back-end up to that point, see {{\\|skylake_(client)#Execution engine|Skylake (client) § Execution engine}}. | |

| − | Skylake | ||

| − | |||

| − | |||

| − | |||

| − | + | ===== Scheduler & 512-SIMD addition ===== | |

| − | |||

| − | |||

| − | |||

| − | ===== | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

[[File:skylake scheduler server.svg|right|500px]] | [[File:skylake scheduler server.svg|right|500px]] | ||

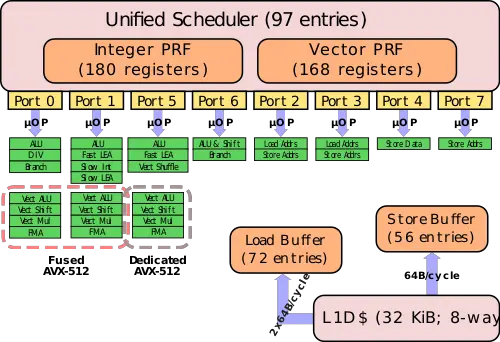

The scheduler itself was increased by 50%; with up to 97 entries (from 64 in {{\\|Broadwell}}) being competitively shared between the two threads. Skylake continues with a unified design; this is in contrast to designs such as [[AMD]]'s {{amd|Zen|l=arch}} which uses a split design each one holding different types of µOPs. Scheduler includes the two register files for integers and vectors. It's in those [[register files]] that output operand data is store. In Skylake, the [[integer]] [[register file]] was also slightly increased from 160 entries to 180. | The scheduler itself was increased by 50%; with up to 97 entries (from 64 in {{\\|Broadwell}}) being competitively shared between the two threads. Skylake continues with a unified design; this is in contrast to designs such as [[AMD]]'s {{amd|Zen|l=arch}} which uses a split design each one holding different types of µOPs. Scheduler includes the two register files for integers and vectors. It's in those [[register files]] that output operand data is store. In Skylake, the [[integer]] [[register file]] was also slightly increased from 160 entries to 180. | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

[[File:skylake sp added cach and vpu.png|left|300px]] | [[File:skylake sp added cach and vpu.png|left|300px]] | ||

| − | This is the first implementation to incorporate {{x86|AVX-512}}, a 512-bit [[SIMD]] [[x86]] instruction set extension. | + | This is the first implementation to incorporate {{x86|AVX-512}}, a 512-bit [[SIMD]] [[x86]] instruction set extension. AVX-512 operations can take place on every port. For 512-bit wide FMA SIMD operations, Intel introduced two different mechanisms ways: |

| − | In the simple implementation, the variants used in the {{intel|Xeon Bronze|entry-level}} and {{intel|Xeon Silver|mid-range}} Xeon servers, AVX-512 fuses Port 0 and Port 1 to form a 512-bit unit. Since those two ports are 256-wide, an AVX-512 option that is dispatched by the scheduler to port 0 will execute on both ports. Note that unrelated operations can still execute in parallel. For example, an AVX-512 operation and an Int ALU operation may execute in parallel - the AVX-512 is dispatched on port 0 and use the AVX unit on port 1 as well and the Int ALU operation will execute independently in parallel on port 1. | + | In the simple implementation, the variants used in the {{intel|Xeon Bronze|entry-level}} and {{intel|Xeon Silver|mid-range}} Xeon servers, AVX-512 fuses Port 0 and Port 1 to form a 512-bit FMA unit. Since those two ports are 256-wide, an AVX-512 option that is dispatched by the scheduler to port 0 will execute on both ports. Note that unrelated operations can still execute in parallel. For example, an AVX-512 operation and an Int ALU operation may execute in parallel - the AVX-512 is dispatched on port 0 and use the AVX unit on port 1 as well and the Int ALU operation will execute independently in parallel on port 1. |

| − | In the {{intel|Xeon Gold|high-end}} and {{intel|Xeon Platinum|highest}} performance Xeons, Intel added a second dedicated AVX-512 unit in addition to the fused Port0-1 operations described above. The dedicated unit is situated on Port 5. | + | In the {{intel|Xeon Gold|high-end}} and {{intel|Xeon Platinum|highest}} performance Xeons, Intel added a second dedicated 512-bit wide AVX-512 FMA unit in addition to the fused Port0-1 operations described above. The dedicated unit is situated on Port 5. |

Physically, Intel added 768 KiB L2 cache and the second AVX-512 VPU externally to the core. | Physically, Intel added 768 KiB L2 cache and the second AVX-512 VPU externally to the core. | ||

| Line 544: | Line 450: | ||

|colspan="3" | This table was taken verbatim from the Intel manual. Execution unit mapping to {{x86|MMX|MMX instructions}} are not included. | |colspan="3" | This table was taken verbatim from the Intel manual. Execution unit mapping to {{x86|MMX|MMX instructions}} are not included. | ||

|} | |} | ||

| − | |||

| − | |||

| − | |||

==== Memory subsystem ==== | ==== Memory subsystem ==== | ||

| Line 562: | Line 465: | ||

== New Technologies == | == New Technologies == | ||

| − | |||

| − | |||

| − | |||

=== Memory Protection Extension (MPX) === | === Memory Protection Extension (MPX) === | ||

| Line 577: | Line 477: | ||

=== Mode-Based Execute (MBE) Control === | === Mode-Based Execute (MBE) Control === | ||

| − | '''Mode-Based Execute''' ('''MBE''') is an enhancement to the Extended Page Tables (EPT) that provides finer level of control of execute permissions. With MBE the previous Execute Enable (''X'') bit is turned into | + | '''Mode-Based Execute''' ('''MBE''') is an enhancement to the Extended Page Tables (EPT) that provides finer level of control of execute permissions. With MBE the previous Execute Enable (''X'') bit is turned into Execute Userspace page (XU) and Execute Supervisor page (XS). The processor selects the mode based on the guest page permission. With proper software support, hypervisors can take advantage of this as well to ensure integrity of kernel-level code. |

== Mesh Architecture == | == Mesh Architecture == | ||

| + | {{main|intel/mesh interconnect architecture|l1=Intel's Mesh Interconnect Architecture}} | ||

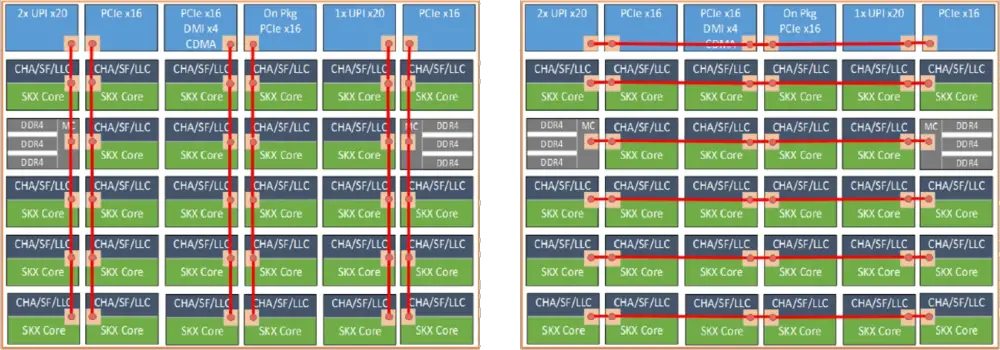

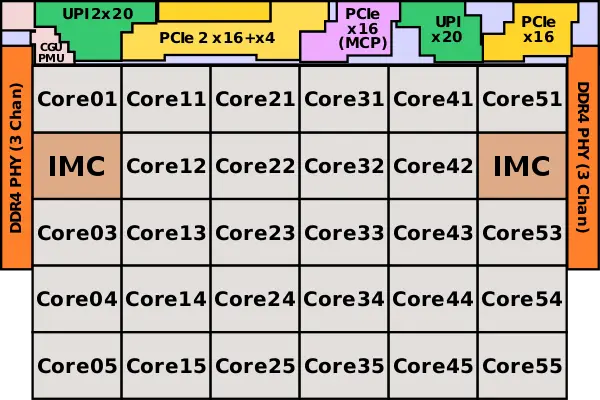

[[File:skylake sp xcc die config.png|right|400px]] | [[File:skylake sp xcc die config.png|right|400px]] | ||

On the {{intel|microarchitectures|previous number of generations}}, Intel has been adding cores onto the die and connecting them via a {{intel|ring architecture}}. This was sufficient until recently. With each generation, the added cores increased the access latency while lowering the available bandwidth per core. Intel mitigated this problem by splitting up the die into two halves each on its own ring. This reduced hopping distance and added additional bandwidth but it did not solve the growing fundamental inefficiencies of the ring architecture. | On the {{intel|microarchitectures|previous number of generations}}, Intel has been adding cores onto the die and connecting them via a {{intel|ring architecture}}. This was sufficient until recently. With each generation, the added cores increased the access latency while lowering the available bandwidth per core. Intel mitigated this problem by splitting up the die into two halves each on its own ring. This reduced hopping distance and added additional bandwidth but it did not solve the growing fundamental inefficiencies of the ring architecture. | ||

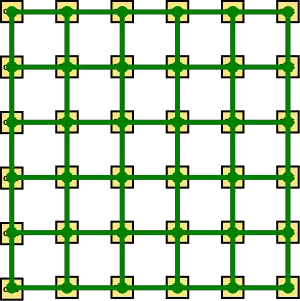

| − | This was completely addressed with the new mesh architecture that is implemented in the Skylake server processors. The mesh | + | This was completely addressed with the new {{intel|mesh architecture}} that is implemented in the Skylake server processors. The mesh consists of a 2-dimensional array of half rings going in the vertical and horizontal directions which allow communication to take the shortest path to the correct node. The new mesh architecture implements a modular design for the routing resources in order to remove the various bottlenecks. That is, the mesh architecture now integrates the caching agent, the home agent, and the IO subsystem on the mesh interconnect distributed across all the cores. Each core now has its own associated LLC slice as well as the snooping filter and the Caching and Home Agent (CHA). Additional nodes such as the two memory controllers, the {{intel|Ultra Path Interconnect}} (UPI) nodes and PCIe are not independent node on the mesh as well and they now behave identically to any other node/core in the network. This means that in addition to the performance increase expected from core-to-core and core-to-memory latency, there should be a substantial increase in I/O performance. The CHA which is found on each of the LLC slices now maps addresses being accessed to the specific LLC bank, memory controller, or I/O subsystem. This provides the necessary information required for the routing to take place. |

| + | |||

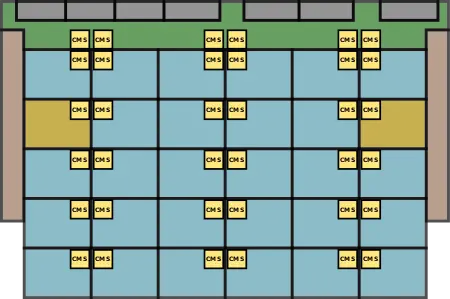

| + | === Organization === | ||

| + | [[File:skylake (server) half rings.png|right|400px]] | ||

| + | Each die has a grid of converged mesh stops (CMS). For example, for the XCC die, there are 36 CMSs. As the name implies, the CMS is a block that effectively interfaces between all the various subsystems and the mesh interconnect. The locations of the CMSes for the large core count is shown on the diagram below. It should be pointed that although the CMS appears to be inside the core tiles, most of the mesh is likely routed above the cores in a similar fashion to how Intel has done it with the ring interconnect which was wired above the caches in order reduce the die area. | ||

| + | |||

| + | |||

| + | :[[File:skylake server cms units.svg|450px]] | ||

| + | |||

| + | |||

| + | Each core tile interfaces with the mesh via its associated converged mesh stop (CMS). The CMSs at the very top are for the UPI links and PCIe links to interface with the mesh we annotated on the previous page. Additionally, the two integrated memory controllers have their own CMS they use to interface with the mesh as well. | ||

| + | |||

| + | Every stop at each tile is directly connected to its immediate four neighbors – north, south, east, and west. | ||

| + | |||

| + | |||

| + | ::[[File:skylake sp cms links.svg|300px]] | ||

| + | |||

| + | |||

| + | Every vertical column of CMSs form a bi-directional half ring. Similarly, every horizontal row forms a bi-directional half ring. | ||

| + | |||

| + | |||

| + | ::[[File:skylake sp mesh half rings.png|1000px]] | ||

| + | |||

| + | |||

| + | {{clear}} | ||

=== Cache Coherency === | === Cache Coherency === | ||

| − | Given the new mesh architecture, new tradeoffs were involved. The new {{intel|UPI}} inter-socket links are a valuable resource that could bottlenecked when flooded with unnecessary cross-socket snoop requests. There's also considerably higher memory bandwidth with Skylake which can impact performance. As a compromise, the previous four snoop modes (no-snoop, early snoop, home snoop, and directory) have been reduced to just directory-base coherency. This also alleviates the implementation | + | Given the new mesh architecture, new tradeoffs were involved. The new {{intel|UPI}} inter-socket links are a valuable resource that could bottlenecked when flooded with unnecessary cross-socket snoop requests. There's also considerably higher memory bandwidth with Skylake which can impact performance. As a compromise, the previous four snoop modes (no-snoop, early snoop, home snoop, and directory) have been reduced to just directory-base coherency. This also alleviates the implementation complexity (which is already complex enough in itself). |

[[File:snc clusters.png|right|350px]] | [[File:snc clusters.png|right|350px]] | ||

| − | It should be pointed out that the directory-base coherency optimizations that were done in previous generations have been furthered improved with Skylake - particularly OSB, {{intel|HitME}} cache, IO directory cache. Skylake maintained support for {{intel|Opportunistic Snoop Broadcast}} (OSB) which allows the network to opportunistically make use of the UPI links when idle or lightly loaded thereby avoiding an expensive memory directory lookup. With the mesh network and distributed CHAs, HitME is now distributed and scales with the CHAs, enhancing the speeding up of cache-to-cache transfers (Those are your migratory cache lines that frequently get transferred between nodes). Specifically for I/O operations, the I/O directory cache (IODC), which was introduced with {{intel|Haswell|l=arch}}, improves stream throughput by eliminating directory reads for InvItoE from | + | It should be pointed out that the directory-base coherency optimizations that were done in previous generations have been furthered improved with Skylake - particularly OSB, {{intel|HitME}} cache, IO directory cache. Skylake maintained support for {{intel|Opportunistic Snoop Broadcast}} (OSB) which allows the network to opportunistically make use of the UPI links when idle or lightly loaded thereby avoiding an expensive memory directory lookup. With the mesh network and distributed CHAs, HitME is now distributed and scales with the CHAs, enhancing the speeding up of cache-to-cache transfers (Those are your migratory cache lines that frequently get transferred between nodes). Specifically for I/O operations, the I/O directory cache (IODC), which was introduced with {{intel|Haswell|l=arch}}, improves stream throughput by eliminating directory reads for InvItoE from snoop caching agent. Previously this was implemented as a 64-entry directory cache to complement the directory in memory. In Skylake, with a distributed CHA at each node, the IODC is implemented as an eight-entry directory cache per CHA. |

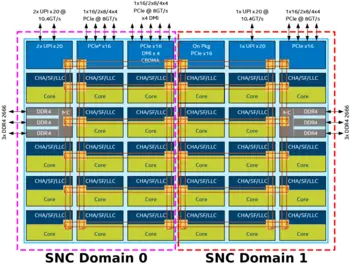

==== Sub-NUMA Clustering ==== | ==== Sub-NUMA Clustering ==== | ||

| − | In previous generations Intel had a feature called {{intel|cluster-on-die}} (COD) which was introduced with {{intel|Haswell|l=arch}}. With Skylake, there's a similar feature called {{intel|sub-NUMA cluster}} (SNC). With a memory controller physically located on each side of the die, SNC allows for the creation of two localized domains with each memory controller belonging to each domain. The processor can then map the addresses from the controller to the distributed home | + | In previous generations Intel had a feature called {{intel|cluster-on-die}} (COD) which was introduced with {{intel|Haswell|l=arch}}. With Skylake, there's a similar feature called {{intel|sub-NUMA cluster}} (SNC). With a memory controller physically located on each side of the die, SNC allows for the creation of two localized domains with each memory controller belonging to each domain. The processor can then map the addresses from the controller to the distributed home agents and LLC in its domain. This allows executing code to experience lower LLC and memory latency within its domain compared to accesses outside of the domain. |

| − | It should be pointed out that in contrast to COD, SNC has a unique location for every | + | It should be pointed out that in contrast to COD, SNC has a unique location for every address in the LLC and is never duplicated across LLC banks (previously, COD cache lines could have copies). Additionally, on multiprocessor systems, addresses mapped to memory on remote sockets are still uniformly distributed across all LLC banks irrespective of the localized SNC domain. |

== Scalability == | == Scalability == | ||

{{see also|intel/quickpath interconnect|intel/ultra path interconnect|l1=QuickPath Interconnect|l2=Ultra Path Interconnect}} | {{see also|intel/quickpath interconnect|intel/ultra path interconnect|l1=QuickPath Interconnect|l2=Ultra Path Interconnect}} | ||

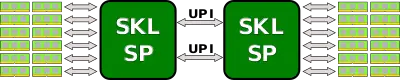

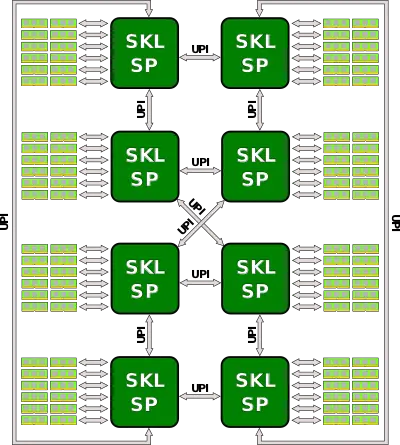

| − | In the last couple of generations, Intel has been utilizing {{intel|QuickPath Interconnect}} (QPI) which served as a high-speed point-to-point interconnect. QPI has been replaced the {{intel|Ultra Path Interconnect}} (UPI) which is higher-efficiency coherent interconnect for scalable systems, allowing multiple processors to share a single shared address space. Depending on the exact model, each processor can have | + | In the last couple of generations, Intel has been utilizing {{intel|QuickPath Interconnect}} (QPI) which served as a high-speed point-to-point interconnect. QPI has been replaced by the {{intel|Ultra Path Interconnect}} (UPI) which is higher-efficiency coherent interconnect for scalable systems, allowing multiple processors to share a single shared address space. Depending on the exact model, each processor can have either two or three UPI links connecting to the other processors. |

| − | UPI links eliminate some of the scalability | + | UPI links eliminate some of the scalability limitations that surfaced in QPI over the past few microarchitecture iterations. They use directory-based home snoop coherency protocol and operate at up either 10.4 GT/s or 9.6 GT/s. This is quite a bit different from previous generations. In addition to the various improvements done to the protocol layer, {{intel|Skylake SP|l=core}} now implements a distributed CHA that is situated along with the LLC bank on each core. It's in charge of tracking the various requests from the core as well as responding to snoop requests from both local and remote agents. The ease of distributing the home agent is a result of Intel getting rid of the requirement on preallocation of resources at the home agent. This also means that future architectures should be able to scale up well. |

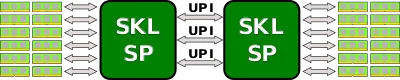

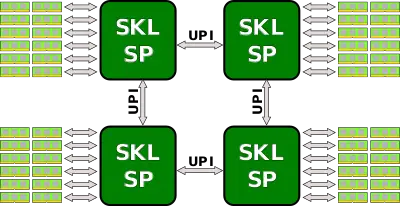

Depending on the exact model, Skylake processors can scale from 2-way all the way up to 8-way multiprocessing. Note that the high-end models that support 8-way multiprocessing also only come with three UPI links for this purpose while the lower end processors can have either two or three UPI links. Below are the typical configurations for those processors. | Depending on the exact model, Skylake processors can scale from 2-way all the way up to 8-way multiprocessing. Note that the high-end models that support 8-way multiprocessing also only come with three UPI links for this purpose while the lower end processors can have either two or three UPI links. Below are the typical configurations for those processors. | ||

| Line 628: | Line 553: | ||

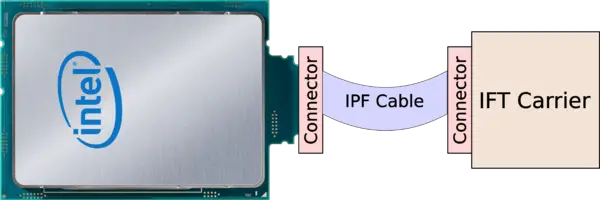

:: [[File:skylake sp with hfi to carrier.png|600px]] | :: [[File:skylake sp with hfi to carrier.png|600px]] | ||

| + | |||

| + | |||

| + | Regardless of the model, the integrated fabric die has a TDP of 8 Watts (note that this value is already included in the model's TDP value). | ||

{{clear}} | {{clear}} | ||

| Line 638: | Line 566: | ||

! !! Core !! Socket !! Permanent !! Platform !! Chipset !! Chipset Bus !! SMP Interconnect | ! !! Core !! Socket !! Permanent !! Platform !! Chipset !! Chipset Bus !! SMP Interconnect | ||

|- | |- | ||

| − | | [[File:skylake x (back).png|100px|link=intel/cores/skylake_x]] || {{intel|Skylake X|l=core}} || {{intel|LGA-2066}} || No || 2-chip || {{intel|Lewisburg}} || [[DMI 3.0]] || {{tchk|no}} | + | | [[File:skylake x (back).png|100px|link=intel/cores/skylake_x]] || {{intel|Skylake X|l=core}} || {{intel|LGA-2066}} || rowspan="2" | No || 2-chip || rowspan="2" | {{intel|Lewisburg}} || rowspan="2" | [[DMI 3.0]] || {{tchk|no}} |

|- | |- | ||

| − | | || {{intel|Skylake SP|l=core}} || {{intel|LGA-3647}} | + | | || {{intel|Skylake SP|l=core}} || {{intel|LGA-3647}} || 2-chip + 2-8-way SMP || {{intel|Ultra Path Interconnect|UPI}} |

|} | |} | ||

| Line 658: | Line 586: | ||

| HCC | | HCC | ||

|} | |} | ||

| + | |||

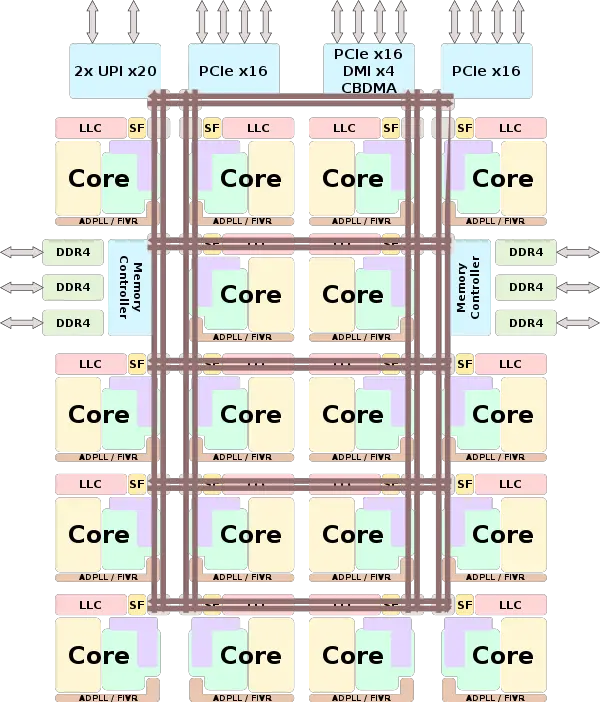

| + | == Floorplan == | ||

| + | [[File:skylake sp major blocks.svg|right|400px]] | ||

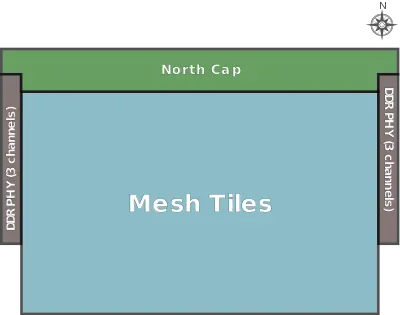

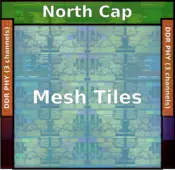

| + | All Skylake server dies consist of three major blocks: | ||

| + | |||

| + | * DDR PHYs | ||

| + | * North Cap | ||

| + | * Mesh Tiles | ||

| + | |||

| + | Those blocks are found on all die configuration and form the base for Intel's highly configurable floorplan. Depending on the market segment and model specification targets, Intel can add and remove rows of tiles. | ||

| + | |||

| + | <div style="text-align: center;"> | ||

| + | <div style="float: left;">'''XCC Die'''<br>[[File:skylake (server) die major blocks (xcc).png|250px]]</div> | ||

| + | <div style="float: left; margin-left: 30px;">'''HCC Die'''<br>[[File:skylake (server) die major blocks (hcc).png|175px]]</div> | ||

| + | </div> | ||

| + | |||

| + | {{clear}} | ||

| + | === Physical Layout === | ||

| + | ==== North Cap ==== | ||

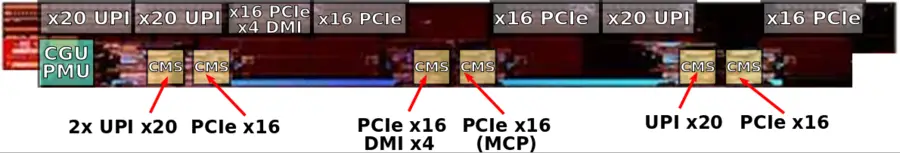

| + | The '''North Cap''' at the very top of the die contains all the I/O agents and PHYs as well as serial IP ports, and the fuse unit. For the most part this configuration largely the same for all the dies. For the smaller dies, the extras are removed (e.g., the in-package PCIe link is not needed). | ||

| + | |||

| + | At the very top of the North Cap are the various I/O connectivity. There are a total of 128 high-speed I/O lanes – 3×16 (48) PCIe lanes operating at 8 GT/s, x4 DMI lanes for hooking up the Lewisburg chipset, 16 on-package PCIe lanes (operating at 2.5/5/8 GT/s), and 3×20 (60) {{intel|Ultra-Path Interconnect}} (UPI) lanes operating at 10.4 GT/s for the [[multiprocessing]] support. | ||

| + | |||

| + | At the south-west corner of the North Cap is the clock generator unit (CGU) and the Global Power Management Unit (Global PMU). The CGU contains an all-digital (AD) filter phase-locked loops (PLL) and an all-digital uncore PLL. The filter ADPLL is dedicated to the generation of all on-die reference clock used for all the core PLLs and one uncore PLL. The power management unit also has its own dedicated all-digital PLL. | ||

| + | |||

| + | At the bottom part of the North Cap are the {{intel|mesh interconnect architecture#Overview|Mesh stops}} for the various I/O to interface with the Mesh. | ||

| + | |||

| + | ==== DDR PHYs ==== | ||

| + | There are the two DDR4 PHYs which are identical for all the dies (albeit in the low-end models, the extra channel is simply disabled). There are two independent and identical physical sections of 3 DDR4 channels each which reside on the east and west edges of the die. Each channel is 72-bit (64 bit and an 8-bit ECC), supporting 2-DIMM per channel with a data rate of up to 2666 MT/s for a bandwidth of 21.33 GB/s and an aggregated bandwidth of 128 GB/s. RDIMM and LRDIMM are supported. | ||

| + | |||

| + | The location of the PHYs was carefully chosen in order to ease the package design, specifically, they were chosen in order to maintain escape routing and pin-out order matching between the CPU and the DIMM slots to shorten package and PCB routing length in order to improve signal integrity. | ||

| + | |||

| + | ==== Layout ==== | ||

| + | :[[File:skylake (server) die area layout.svg|600px]] | ||

| + | |||

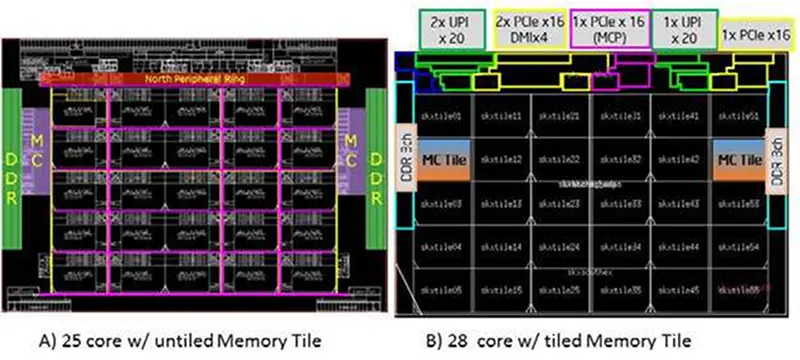

| + | ==== Evolution ==== | ||

| + | The original Skylake large die started out as a 5 by 5 core tile (25 tiles, 25 cores) as shown by the image from Intel on the left side. The memory controllers were next to the PHYs on the east and west side. An additional row was inserted to get to a 5 by 6 grid. Two core tiles one from each of the sides was then replaced by the new memory controller module which can interface with the mesh just like any other core tile. The final die is shown in the image below as well on the right side. | ||

| + | |||

| + | :[[File:skylaake server layout evoluation.png|800px]] | ||

== Die == | == Die == | ||

| + | {{see also|intel/microarchitectures/skylake_(client)#Die|l1=Client Skylake's Die}} | ||

[[File:intel xeon skylake sp.jpg|right|300px|thumb|Skylake SP chips and wafer.]] | [[File:intel xeon skylake sp.jpg|right|300px|thumb|Skylake SP chips and wafer.]] | ||

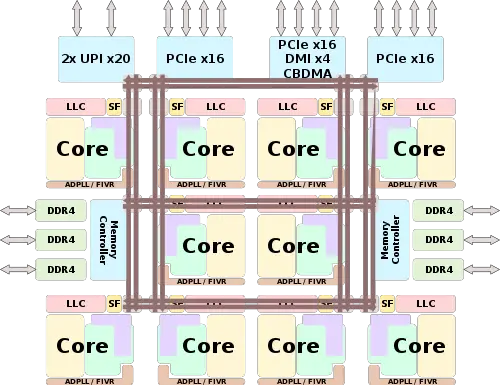

| − | Skylake Server class models and high-end desktop (HEDT) consist of 3 different dies: Low Core Count (LCC), High Core Count (HCC), | + | Skylake Server class models and high-end desktop (HEDT) consist of 3 different dies: |

| + | |||

| + | * 12 tiles (3x4), 10-core, Low Core Count (LCC) | ||

| + | * 20 tiles (5x4), 18-core, High Core Count (HCC) | ||

| + | * 30 tiles (5x6), 28-core, Extreme Core Count (XCC) | ||

| + | |||

| + | === North Cap === | ||

| + | '''HCC:''' | ||

| + | |||

| + | :[[File:skylake (server) northcap (hcc).png|700px]] | ||

| + | |||

| + | :[[File:skylake (server) northcap (hcc) (annotated).png|700px]] | ||

| + | |||

| + | '''XCC:''' | ||

| + | |||

| + | :[[File:skylake (server) northcap (xcc).png|900px]] | ||

| + | |||

| + | :[[File:skylake (server) northcap (xcc) (annotated).png|900px]] | ||

| + | |||

| + | |||

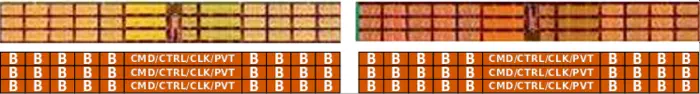

| + | === Memory PHYs === | ||

| + | Data bytes are located on the north and south sub-sections of the channel layout. Command, Control, Clock signals, and process, supply voltage, and temperature (PVT) compensation circuitry are located in the middle section of the channels. | ||

| + | |||

| + | :[[File:skylake sp memory phys (annotated).png|700px]] | ||

| + | |||

| + | === Core Tile === | ||

| + | * ~4.8375 x 3.7163 | ||

| + | * ~ 17.978 mm² die area | ||

| + | |||

| + | :[[File:skylake sp core.png|500px]] | ||

| + | |||

| + | :[[File:skylake sp mesh core tile zoom.png|700px]] | ||

=== Low Core Count (LCC) === | === Low Core Count (LCC) === | ||

* [[14 nm process]] | * [[14 nm process]] | ||

| − | * | + | * 12 metal layers |

* ~22.26 mm x ~14.62 mm | * ~22.26 mm x ~14.62 mm | ||

* ~325.44 mm² die size | * ~325.44 mm² die size | ||

* [[10 cores]] | * [[10 cores]] | ||

| + | * 12 tiles (3x4) | ||

| + | |||

| + | |||

| + | : (NOT official die shot, artist's rendering based on the larger die) | ||

| + | : [[File:skylake lcc die shot.jpg|650px]] | ||

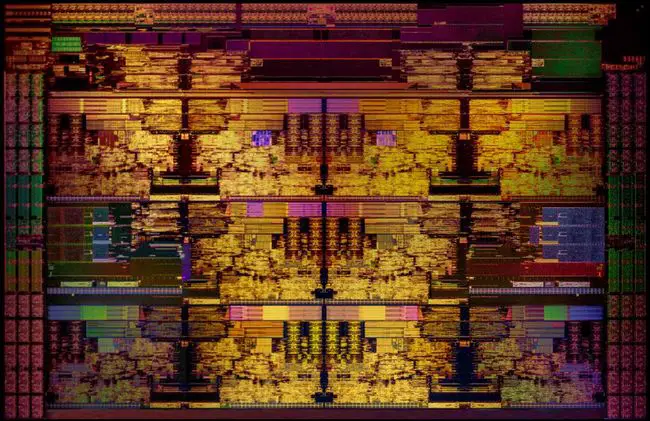

=== High Core Count (HCC) === | === High Core Count (HCC) === | ||

| Line 674: | Line 678: | ||

* [[14 nm process]] | * [[14 nm process]] | ||

| − | * | + | * 13 metal layers |

| − | * | + | * ~485 mm² die size (estimated) |

* [[18 cores]] | * [[18 cores]] | ||

| − | + | * 20 tiles (5x4) | |

: [[File:skylake (octadeca core).png|650px]] | : [[File:skylake (octadeca core).png|650px]] | ||

| − | |||

| − | |||

| Line 688: | Line 690: | ||

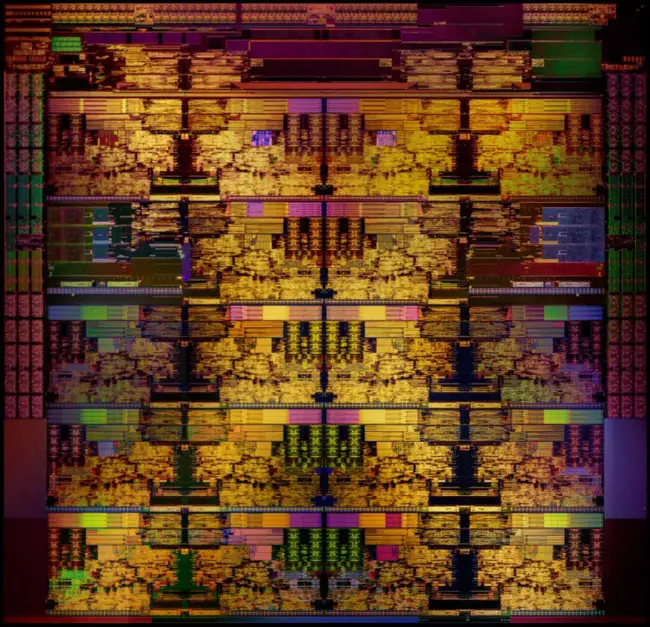

=== Extreme Core Count (XCC) === | === Extreme Core Count (XCC) === | ||

* [[14 nm process]] | * [[14 nm process]] | ||

| − | * | + | * 13 metal layers |

| − | * | + | * ~694 mm² die size (estimated) |

* [[28 cores]] | * [[28 cores]] | ||

| − | + | * 30 tiles (5x6) | |

| − | |||

| − | + | : [[File:skylake-sp hcc die shot.png|class=wikichip_ogimage|650px]] | |

: [[File:skylake-sp hcc die shot (annotated).png|650px]] | : [[File:skylake-sp hcc die shot (annotated).png|650px]] | ||

| − | |||

== All Skylake Chips == | == All Skylake Chips == | ||

| Line 715: | Line 715: | ||

{{comp table header 1|cols=Launched, Price, Family, Core Name, Cores, Threads, %L2$, %L3$, TDP, %Frequency, %Max Turbo, Max Mem, Turbo, SMT}} | {{comp table header 1|cols=Launched, Price, Family, Core Name, Cores, Threads, %L2$, %L3$, TDP, %Frequency, %Max Turbo, Max Mem, Turbo, SMT}} | ||

<tr class="comptable-header comptable-header-sep"><th> </th><th colspan="25">[[Uniprocessors]]</th></tr> | <tr class="comptable-header comptable-header-sep"><th> </th><th colspan="25">[[Uniprocessors]]</th></tr> | ||

| − | {{#ask: [[Category:microprocessor models by intel]] [[instance of::microprocessor]] [[microarchitecture::Skylake]] [[max cpu count::1 | + | {{#ask: [[Category:microprocessor models by intel]] [[instance of::microprocessor]] [[microarchitecture::Skylake (server)]] [[max cpu count::1]] |

|?full page name | |?full page name | ||

|?model number | |?model number | ||

| Line 743: | Line 743: | ||

<tr class="comptable-header comptable-header-sep"><th> </th><th colspan="25">[[Multiprocessors]] (2-way)</th></tr> | <tr class="comptable-header comptable-header-sep"><th> </th><th colspan="25">[[Multiprocessors]] (2-way)</th></tr> | ||

{{#ask: | {{#ask: | ||

| − | [[Category:microprocessor models by intel]] [[instance of::microprocessor]] [[microarchitecture::Skylake]] [[max cpu count::2]] | + | [[Category:microprocessor models by intel]] [[instance of::microprocessor]] [[microarchitecture::Skylake (server)]] [[max cpu count::2]] |

|?full page name | |?full page name | ||

|?model number | |?model number | ||

| Line 771: | Line 771: | ||

<tr class="comptable-header comptable-header-sep"><th> </th><th colspan="25">[[Multiprocessors]] (4-way)</th></tr> | <tr class="comptable-header comptable-header-sep"><th> </th><th colspan="25">[[Multiprocessors]] (4-way)</th></tr> | ||

{{#ask: | {{#ask: | ||

| − | [[Category:microprocessor models by intel]] [[instance of::microprocessor]] [[microarchitecture::Skylake]] [[max cpu count::4]] | + | [[Category:microprocessor models by intel]] [[instance of::microprocessor]] [[microarchitecture::Skylake (server)]] [[max cpu count::4]] |

|?full page name | |?full page name | ||

|?model number | |?model number | ||

| Line 799: | Line 799: | ||

<tr class="comptable-header comptable-header-sep"><th> </th><th colspan="25">[[Multiprocessors]] (8-way)</th></tr> | <tr class="comptable-header comptable-header-sep"><th> </th><th colspan="25">[[Multiprocessors]] (8-way)</th></tr> | ||

{{#ask: | {{#ask: | ||

| − | [[Category:microprocessor models by intel]] [[instance of::microprocessor]] [[microarchitecture::Skylake]] [[max cpu count::8]] | + | [[Category:microprocessor models by intel]] [[instance of::microprocessor]] [[microarchitecture::Skylake (server)]] [[max cpu count::8]] |

|?full page name | |?full page name | ||

|?model number | |?model number | ||

| Line 825: | Line 825: | ||

|limit=60 | |limit=60 | ||

}} | }} | ||

| − | {{comp table count|ask=[[Category:microprocessor models by intel]] [[instance of::microprocessor]] [[microarchitecture::Skylake | + | {{comp table count|ask=[[Category:microprocessor models by intel]] [[instance of::microprocessor]] [[microarchitecture::Skylake (server)]]}} |

</table> | </table> | ||

{{comp table end}} | {{comp table end}} | ||

| + | == References == | ||

| + | * Intel Unveils Powerful Intel Xeon Scalable Processors, Live Event, July 11, 2017 | ||

| + | * [[:File:intel xeon scalable processor architecture deep dive.pdf|Intel Xeon Scalable Process Architecture Deep Dive]], Akhilesh Kumar & Malay Trivedi, Skylake-SP CPU & Lewisburg PCH Architects, June 12th, 2017. | ||

| + | * IEEE Hot Chips (HC28) 2017. | ||

| + | * IEEE ISSCC 2018 | ||

| − | == | + | == Documents == |

| − | + | * [[:File:Intel-Core-X-Series-Processor-Family Product-Information.pdf|New Intel Core X-Series Processor Family]] | |

| − | * | + | * [[:File:intel-xeon-scalable-processors-product-brief.pdf|Intel Xeon (Skylake SP) Processors Product Brief]] |

| + | * [[:File:intel-xeon-scalable-processors-overview.pdf|Intel Xeon (Skylake SP) Processors Product Overview]] | ||

| + | * [[:File:intel-skylake-w-overview.pdf|Xeon (Skylake W) Workstations Overview]] | ||

| + | * [[:File:optimal hpc solutions for scalable xeons.pdf|Optimal HPC solutions with Intel Scalable Xeons]] | ||

Latest revision as of 23:59, 5 July 2022

| Edit Values | |

| Skylake (server) µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | Intel |

| Manufacturer | Intel |

| Introduction | May 4, 2017 |

| Process | 14 nm |

| Core Configs | 4, 6, 8, 10, 12, 14, 16, 18, 20, 22, 24, 26, 28 |

| Pipeline | |

| Type | Superscalar |

| OoOE | Yes |

| Speculative | Yes |

| Reg Renaming | Yes |

| Stages | 14-19 |

| Instructions | |

| ISA | x86-64 |

| Extensions | MOVBE, MMX, SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4.2, POPCNT, AVX, AVX2, AES, PCLMUL, FSGSBASE, RDRND, FMA3, F16C, BMI, BMI2, VT-x, VT-d, TXT, TSX, RDSEED, ADCX, PREFETCHW, CLFLUSHOPT, XSAVE, SGX, MPX, AVX-512 |

| Cache | |

| L1I Cache | 32 KiB/core 8-way set associative |

| L1D Cache | 32 KiB/core 8-way set associative |

| L2 Cache | 1 MiB/core 16-way set associative |

| L3 Cache | 1.375 MiB/core 11-way set associative |

| Cores | |

| Core Names | Skylake X, Skylake W, Skylake SP |

| Succession | |

| Contemporary | |

| Skylake (client) | |

Skylake (SKL) Server Configuration is Intel's successor to Broadwell, an enhanced 14nm+ process microarchitecture for enthusiasts and servers. Skylake succeeded Broadwell. Skylake is the "Architecture" phase as part of Intel's PAO model. The microarchitecture was developed by Intel's R&D center in Haifa, Israel.

For desktop enthusiasts, Skylake is branded Core i7, and Core i9 processors (under the Core X series). For scalable server class processors, Intel branded it as Xeon Bronze, Xeon Silver, Xeon Gold, and Xeon Platinum.

There are a fair number of major differences in the Skylake server configuration vs the client configuration.

Contents

Codenames[edit]

- See also: Client Skylake's Codenames

| Core | Abbrev | Platform | Target |

|---|---|---|---|

| Skylake SP | SKL-SP | Purley | Server Scalable Processors |

| Skylake X | SKL-X | Basin Falls | High-end desktops & enthusiasts market |

| Skylake W | SKL-W | Basin Falls | Enterprise/Business workstations |

| Skylake DE | SKL-DE | Dense server/edge computing |

Brands[edit]

- See also: Client Skylake's Brands

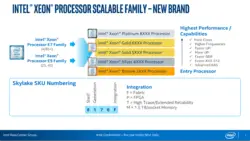

Intel introduced a number of new server chip families with the introduction of Skylake SP as well as a new enthusiasts family with the introduction of Skylake X.

| Logo | Family | General Description | Differentiating Features | ||||||

|---|---|---|---|---|---|---|---|---|---|

| Cores | HT | AVX | AVX2 | AVX-512 | TBT | ECC | |||

|

Core i7 | Enthusiasts/High Performance (X) | 6 - 8 | ✔ | ✔ | ✔ | ✔ | ✔ | ✘ |

|

Core i9 | Enthusiasts/High Performance | 10 - 18 | ✔ | ✔ | ✔ | ✔ | ✔ | ✘ |

| Logo | Family | General Description | Differentiating Features | ||||||

| Cores | HT | TBT | AVX-512 | AVX-512 Units | UPI links | Scalability | |||

|

Xeon D | Dense servers / edge computing | 4-18 | ✔ | ✔ | ✔ | 1 | ✘ | |

|

Xeon W | Business workstations | 4-18 | ✔ | ✔ | ✔ | 2 | ✘ | |

|

Xeon Bronze | Entry-level performance / Cost-sensitive |

6 - 8 | ✘ | ✘ | ✔ | 1 | 2 | Up to 2 |

|

Xeon Silver | Mid-range performance / Efficient lower power |

4 - 12 | ✔ | ✔ | ✔ | 1 | 2 | Up to 2 |

|

Xeon Gold 5000 | High performance | 4 - 14 | ✔ | ✔ | ✔ | 1 | 2 | Up to 4 |

| Xeon Gold 6000 | Higher performance | 6 - 22 | ✔ | ✔ | ✔ | 2 | 3 | Up to 4 | |

|

Xeon Platinum | Highest performance / flexibility | 4 - 28 | ✔ | ✔ | ✔ | 2 | 3 | Up to 8 |

Release Dates[edit]

Skylake-based Core X was introduced in May 2017 while Skylake SP was introduced in July 2017.

Process Technology[edit]

- Main article: 14 nm lithography process

Unlike mainstream Skylake models, all Skylake server configuration models are fabricated on Intel's enhanced 14+ nm process which is used by Kaby Lake.

Compatibility[edit]

| Vendor | OS | Version | Notes |

|---|---|---|---|

| Microsoft | Windows | Windows Server 2008 | Support |

| Windows Server 2008 R2 | |||

| Windows Server 2012 | |||

| Windows Server 2012 R2 | |||

| Windows Server 2016 | |||

| Linux | Linux | Kernel 3.19 | Initial Support (MPX support) |

| Apple | macOS | 10.12.3 | iMac Pro |

Compiler support[edit]

| Compiler | Arch-Specific | Arch-Favorable |

|---|---|---|

| ICC | -march=skylake-avx512 |

-mtune=skylake-avx512

|

| GCC | -march=skylake-avx512 |

-mtune=skylake-avx512

|

| LLVM | -march=skylake-avx512 |

-mtune=skylake-avx512

|

| Visual Studio | /arch:AVX2 |

/tune:skylake

|

CPUID[edit]

| Core | Extended Family |

Family | Extended Model |

Model |

|---|---|---|---|---|

| X, SP, DE, W | 0 | 0x6 | 0x5 | 0x5 |

| Family 6 Model 85 | ||||

Architecture[edit]

Skylake server configuration introduces a number of significant changes from both Intel's previous microarchitecture, Broadwell, as well as the Skylake (client) architecture. Unlike client models, Skylake servers and HEDT models will still incorporate the fully integrated voltage regulator (FIVR) on-die. Those chips also have an entirely new multi-core system architecture that brought a new mesh interconnect network (from ring topology).

Key changes from Broadwell[edit]

- Improved "14 nm+" process (see Kaby Lake § Process Technology)

- Omni-Path Architecture (OPA)

- Mesh architecture (from ring)

- Sub-NUMA Clustering (SNC) support (replaces the Cluster-on-Die (COD) implementation)

- Chipset

- Core

- All the changes from Skylake Client (For full list, see Skylake (Client) § Key changes from Broadwell)

- Front End

- LSD is disabled (Likely due to a bug; see § Front-end for details)

- Back-end

- Port 4 now performs 512b stores (from 256b)

- Port 0 & Port 1 can now be fused to perform AVX-512

- Port 5 now can do full 512b operations (not on all models)

- Memory Subsystem

- Larger store buffer (56 entries, up from 42)

- Page split load penalty reduced 20-fold

- Larger Write-back buffer

- Store is now 64B/cycle (from 32B/cycle)

- Load is now 2x64B/cycle (from 2x32B/cycle)

- New Features

- Adaptive Double Device Data Correction (ADDDC)

- Memory

- L2$

- Increased to 1 MiB/core (from 256 KiB/core)

- Latency increased from 12 to 14

- L3$

- Reduced to 1.375 MiB/core (from 2.5 MiB/core)

- Now non-inclusive (was inclusive)

- DRAM

- hex-channel DDR4-2666 (from quad-channel)

- L2$

- TLBs

- ITLB

- 4 KiB page translations was changed from 4-way to 8-way associative

- STLB

- 4 KiB + 2 MiB page translations was changed from 6-way to 12-way associative

- DMI/PEG are now on a discrete clock domain with BCLK sitting on its own domain with full-range granularity (1 MHz intervals)

- ITLB

- Testability

- New support for Direct Connect Interface (DCI), a new debugging transport protocol designed to allow debugging of closed cases (e.g. laptops, embedded) by accessing things such as JTAG through any USB 3 port.

CPU changes[edit]

See Skylake (Client) § CPU changes

New instructions[edit]

- See also: Client Skylake's New instructions

Skylake server introduced a number of new instructions:

-

MPX- Memory Protection Extensions -

XSAVEC- Save processor extended states with compaction to memory -

XSAVES- Save processor supervisor-mode extended states to memory. -

CLFLUSHOPT- Flush & Invalidates memory operand and its associated cache line (All L1/L2/L3 etc..) -

AVX-512, specifically: -

PKU- Memory Protection Keys for Userspace -

PCOMMIT- PCOMMIT instruction -

CLWB- Force cache line write-back without flush

Block Diagram[edit]

Entire SoC Overview[edit]

LCC SoC[edit]

HCC SoC[edit]

XCC SoC[edit]

Individual Core[edit]

Memory Hierarchy[edit]

Some major organizational changes were done to the cache hierarchy in Skylake server configuration vs Broadwell/Haswell. The memory hierarchy for Skylake's server and HEDT processors has been rebalanced. Note that the L3 is now non-inclusive and some of the SRAM from the L3 cache was moved into the private L2 cache.

- Cache

- L0 µOP cache:

- 1,536 µOPs/core, 8-way set associative

- 32 sets, 6-µOP line size

- statically divided between threads, inclusive with L1I

- 1,536 µOPs/core, 8-way set associative

- L1I Cache:

- 32 KiB/core, 8-way set associative

- 64 sets, 64 B line size

- competitively shared by the threads/core

- 32 KiB/core, 8-way set associative

- L1D Cache:

- 32 KiB/core, 8-way set associative

- 64 sets, 64 B line size

- competitively shared by threads/core

- 4 cycles for fastest load-to-use (simple pointer accesses)

- 5 cycles for complex addresses

- 128 B/cycle load bandwidth

- 64 B/cycle store bandwidth

- Write-back policy

- L2 Cache:

- 1 MiB/core, 16-way set associative

- 64 B line size

- Inclusive

- 64 B/cycle bandwidth to L1$

- Write-back policy

- 14 cycles latency

- L3 Cache:

- 1.375 MiB/core, 11-way set associative, shared across all cores

- Note that a few models have non-default cache sizes due to disabled cores

- 2,048 sets, 64 B line size

- Non-inclusive victim cache

- Write-back policy

- 50-70 cycles latency

- 1.375 MiB/core, 11-way set associative, shared across all cores

- Snoop Filter (SF):

- 2,048 sets, 12-way set associative

- L0 µOP cache:

- DRAM

- 6 channels of DDR4, up to 2666 MT/s

- RDIMM and LRDIMM

- bandwidth of 21.33 GB/s

- aggregated bandwidth of 128 GB/s

- 6 channels of DDR4, up to 2666 MT/s

Skylake TLB consists of dedicated L1 TLB for instruction cache (ITLB) and another one for data cache (DTLB). Additionally there is a unified L2 TLB (STLB).

- TLBs:

- ITLB

- 4 KiB page translations:

- 128 entries; 8-way set associative

- dynamic partitioning

- 2 MiB / 4 MiB page translations:

- 8 entries per thread; fully associative

- Duplicated for each thread

- 4 KiB page translations:

- DTLB

- 4 KiB page translations:

- 64 entries; 4-way set associative

- fixed partition

- 2 MiB / 4 MiB page translations:

- 32 entries; 4-way set associative

- fixed partition

- 1G page translations:

- 4 entries; 4-way set associative

- fixed partition

- 4 KiB page translations:

- STLB

- 4 KiB + 2 MiB page translations:

- 1536 entries; 12-way set associative. (Note: STLB is incorrectly reported as "6-way" by CPUID leaf 2 (EAX=02H). Skylake erratum SKL148 recommends software to simply ignore that value.)

- fixed partition

- 1 GiB page translations:

- 16 entries; 4-way set associative

- fixed partition

- 4 KiB + 2 MiB page translations:

- ITLB

Overview[edit]

The Skylake server architecture marks a significant departure from the previous decade of multi-core system architecture at Intel. Since Westmere Intel has been using a ring bus interconnect to interlink multiple cores together. As Intel continued to add more I/O, increase the memory bandwidth, and added more cores which increased the data traffic flow, that architecture started to show its weakness. With the introduction of the Skylake server architecture, the interconnect was entirely re-architected to a 2-dimensional mesh interconnect.

A superset model is shown on the right. Skylake-based servers are the first mainstream servers to make use of Intel's new mesh interconnect architecture, an architecture that was previously explored, experimented with, and enhanced with Intel's Phi many-core processors. In this configuration, the cores, caches, and the memory controllers are organized in rows and columns - each with dedicated connections going through each of the rows and columns allowing for a shortest path between any tile, reducing latency, and improving the bandwidth. Those processors are offered from 4 cores up to 28 cores with 8 to 56 threads. In addition to the system-level architectural changes, with Skylake, Intel now has a separate core architecture for those chips which incorporate a plethora of new technologies and features including support for the new AVX-512 instruction set extension.

All models incorporate 6 channels of DDR4 supporting up to 12 DIMMS for a total of 768 GiB (with extended models support 1.5 TiB). For I/O all models incorporate 48x (3x16) lanes of PCIe 3.0. There is an additional x4 lanes PCIe 3.0 reserved exclusively for DMI for the the Lewisburg (LBG) chipset. For a selected number of models, specifically those with F suffix, they have an Omni-Path Host Fabric Interface (HFI) on-package (see Integrated Omni-Path).

Skylake processors are designed for scalability, supporting 2-way, 4-way, and 8-way multiprocessing through Intel's new Ultra Path Interconnect (UPI) interconnect links, with two to three links being offered (see § Scalability). High-end models have node controller support allowing for even higher way configuration (e.g., 32-way multiprocessing).

Core[edit]

Overview[edit]

Skylake shares most of the development vectors with its predecessor while introducing a one of new constraint. The overall goals were:

- Performance improvements - the traditional way of milking more performance by increasing the instructions per cycle as well as clock frequency.

- Power efficiency - reduction of power for all functional blocks

- Security enhancements - new security features are implemented in hardware in the core

- Configurability

Configurability[edit]

Intel has been experiencing a growing divergence in functionality over the last number of iterations of their microarchitecture between their mainstream consumer products and their high-end HPC/server models. Traditionally, Intel has been using the same exact core design for everything from their lowest end value models (e.g. Celeron) all the way up to the highest-performance enterprise models (e.g. Xeon E7). While the two have fundamentally different chip architectures, they use the same exact CPU core architecture as the building block.

This design philosophy has changed with Skylake. In order to better accommodate the different functionalities of each segment without sacrificing features or making unnecessary compromises, Intel went with a configurable core. The Skylake core is a single development project, making up a master superset core. The project results in two derivatives: one for servers (the substance of this article) and one for clients. All mainstream models (from Celeron/Pentium all the way up to Core i7/Xeon E3) use the client core configuration. Server models (e.g. Xeon Gold/Xeon Platinum) are using the new server configuration instead.

The server core is considerably larger than the client one, featuring Advanced Vector Extensions 512 (AVX-512). Skylake servers support what was formerly called AVX3.2 (AVX512F + AVX512CD + AVX512BW + AVX512DQ + AVX512VL). The server core also incorporates a number of new technologies not found in the client configuration. In addition to the execution units that were added, the cache hierarchy has changed for the server core as well, incorporating a large L2 and a portion of the LLC as well as the caching and home agent and the snoop filter that needs to accommodate the new cache changes.

Below is a visual that helps show how the server core was evolved from the client core.

Pipeline[edit]

The Skylake core focuses on extracting performance and reducing power through a number of key ways. Intel builds Skylake on previous microarchitectures, descendants of Sandy Bridge. For the core to increase the overall performance, Intel focused on extracting additional parallelism.

Front-end[edit]

For the most part, with the exception of the LSD, the front-end of the Skylake server core is identical to the client configuration. For in-depth detail of the Skylake front-end see Skylake (client) § Front-end.

The only major difference in the front-end from the client core configuration is the LSD. The Loop Stream Detector (LSD) has been disabled. While the exact reason is not known, it might be related to a severe issue that was experienced by the OCaml Development Team. The issue was patched via microcode on the client platform, however this change might indicate it was possibly disabled on there as well. The exact implications of this are unknown.

Execution engine[edit]

The Skylake server configuration core back-end is identical to the client configuration up to the scheduler. For in-depth detail of the Skylake back-end up to that point, see Skylake (client) § Execution engine.

Scheduler & 512-SIMD addition[edit]

The scheduler itself was increased by 50%; with up to 97 entries (from 64 in Broadwell) being competitively shared between the two threads. Skylake continues with a unified design; this is in contrast to designs such as AMD's Zen which uses a split design each one holding different types of µOPs. Scheduler includes the two register files for integers and vectors. It's in those register files that output operand data is store. In Skylake, the integer register file was also slightly increased from 160 entries to 180.

This is the first implementation to incorporate AVX-512, a 512-bit SIMD x86 instruction set extension. AVX-512 operations can take place on every port. For 512-bit wide FMA SIMD operations, Intel introduced two different mechanisms ways:

In the simple implementation, the variants used in the entry-level and mid-range Xeon servers, AVX-512 fuses Port 0 and Port 1 to form a 512-bit FMA unit. Since those two ports are 256-wide, an AVX-512 option that is dispatched by the scheduler to port 0 will execute on both ports. Note that unrelated operations can still execute in parallel. For example, an AVX-512 operation and an Int ALU operation may execute in parallel - the AVX-512 is dispatched on port 0 and use the AVX unit on port 1 as well and the Int ALU operation will execute independently in parallel on port 1.

In the high-end and highest performance Xeons, Intel added a second dedicated 512-bit wide AVX-512 FMA unit in addition to the fused Port0-1 operations described above. The dedicated unit is situated on Port 5.

Physically, Intel added 768 KiB L2 cache and the second AVX-512 VPU externally to the core.

Scheduler Ports & Execution Units[edit]

| Scheduler Ports Designation | ||

|---|---|---|

| Port 0 | Integer/Vector Arithmetic, Multiplication, Logic, Shift, and String ops | 512-bit Vect ALU/Shift/Mul/FMA |

| FP Add, Multiply, FMA | ||

| Integer/FP Division and Square Root | ||

| AES Encryption | ||

| Branch2 | ||

| Port 1 | Integer/Vector Arithmetic, Multiplication, Logic, Shift, and Bit Scanning | |

| FP Add, Multiply, FMA | ||

| Port 5 | Integer/Vector Arithmetic, Logic | 512-bit Vect ALU/Shift/Mul/FMA |

| Vector Permute | ||

| x87 FP Add, Composite Int, CLMUL | ||

| Port 6 | Integer Arithmetic, Logic, Shift | |

| Branch | ||

| Port 2 | Load, AGU | |

| Port 3 | Load, AGU | |

| Port 4 | Store, AGU | |

| Port 7 | AGU | |

| Execution Units | ||

|---|---|---|

| Execution Unit | # of Units | Instructions |

| ALU | 4 | add, and, cmp, or, test, xor, movzx, movsx, mov, (v)movdqu, (v)movdqa, (v)movap*, (v)movup* |

| DIV | 1 | divp*, divs*, vdiv*, sqrt*, vsqrt*, rcp*, vrcp*, rsqrt*, idiv |

| Shift | 2 | sal, shl, rol, adc, sarx, adcx, adox, etc... |

| Shuffle | 1 | (v)shufp*, vperm*, (v)pack*, (v)unpck*, (v)punpck*, (v)pshuf*, (v)pslldq, (v)alignr, (v)pmovzx*, vbroadcast*, (v)pslldq, (v)psrldq, (v)pblendw |

| Slow Int | 1 | mul, imul, bsr, rcl, shld, mulx, pdep, etc... |

| Bit Manipulation | 2 | andn, bextr, blsi, blsmsk, bzhi, etc |

| FP Mov | 1 | (v)movsd/ss, (v)movd gpr |

| SIMD Misc | 1 | STTNI, (v)pclmulqdq, (v)psadw, vector shift count in xmm |

| Vec ALU | 3 | (v)pand, (v)por, (v)pxor, (v)movq, (v)movq, (v)movap*, (v)movup*, (v)andp*, (v)orp*, (v)paddb/w/d/q, (v)blendv*, (v)blendp*, (v)pblendd |

| Vec Shift | 2 | (v)psllv*, (v)psrlv*, vector shift count in imm8 |

| Vec Add | 2 | (v)addp*, (v)cmpp*, (v)max*, (v)min*, (v)padds*, (v)paddus*, (v)psign, (v)pabs, (v)pavgb, (v)pcmpeq*, (v)pmax, (v)cvtps2dq, (v)cvtdq2ps, (v)cvtsd2si, (v)cvtss2si |

| Vec Mul | 2 | (v)mul*, (v)pmul*, (v)pmadd* |

| This table was taken verbatim from the Intel manual. Execution unit mapping to MMX instructions are not included. | ||

Memory subsystem[edit]

Skylake's memory subsystem is in charge of the loads and store requests and ordering. Since Haswell, it's possible to sustain two memory reads (on ports 2 and 3) and one memory write (on port 4) each cycle. Each memory operation can be of any register size up to 512 bits. Skylake memory subsystem has been improved. The store buffer has been increased by 42 entries from Broadwell to 56 for a total of 128 simultaneous memory operations in-flight or roughly 60% of all µOPs. Special care was taken to reduce the penalty for page-split loads; previously scenarios involving page-split loads were thought to be rarer than they actually are. This was addressed in Skylake with page-split loads are now made equal to other splits loads. Expect page split load penalty down to 5 cycles from 100 cycles in Broadwell. The average latency to forward a load to store has also been improved and stores that miss in the L1$ generate L2$ requests to the next level cache much earlier in Skylake than before.

The L2 to L1 bandwidth in Skylake is the same as Haswell at 64 bytes per cycle in either direction. Note that one operation can be done each cycle; i.e., the L1 can either receive data from the L1 or send data to the Load/Store buffers each cycle, but not both. Latency from L2$ to L3$ has also been increased from 4 cycles/line to 2 cycles/line.