(Lucienne / Cezanne update.) |

(Update.) |

||

| Line 9: | Line 9: | ||

|microarch 2=Zen 3 | |microarch 2=Zen 3 | ||

|tdp=55 W | |tdp=55 W | ||

| − | |package name= | + | |package name=FP6 |

| − | |package type= | + | |package type=FC-OBGA |

|package contacts=1140 | |package contacts=1140 | ||

| − | |package dimension=25 mm | + | |package dimension=35 mm |

| − | |package dimension | + | |package dimension 2=25 mm |

| + | |package dimension 3=1.38 mm | ||

|package pitch=0.65 mm | |package pitch=0.65 mm | ||

}} | }} | ||

| + | '''FP6''' is a CPU package of [[AMD]] Ryzen mobile and embedded processors, the successor to the {{\\|FP5}} package. Its counterpart for desktop processors is the PGA-1331 package for {{\\|Socket AM4}}. | ||

| − | + | == Overview == | |

| + | FP6 is a 1140-contact, 0.65 mm non-uniform pitch, organic [[ball grid array]] package with a size of 35 mm × 25 mm × 1.38 mm. | ||

| − | + | It supports two 72-bit channels of [[DDR4]] memory or four 32-bit channels of [[LPDDR4x]] memory, two PCIe Gen 3 I/O interfaces with 20 lanes total, four digital display interfaces, four USB 3.2 Gen 2 ports, four USB 2.0 ports, and up to four SATA Gen 3 ports. | |

| + | |||

| + | The following AMD processor families use the FP6 package: | ||

| + | {| class="wikitable" | ||

| + | ! || CPU Family || Microarch. || Process || Products | ||

| + | |- | ||

| + | | Type 1 | ||

| + | | {{amd|CPUID#Family 23 (17h)|Family 17h}} Models 60h–6Fh | ||

| + | | {{amd|Zen 2|l=arch}} | ||

| + | | [[7 nm]] | ||

| + | | Ryzen 4000 "{{amd|Renoir|l=core}}" (Model 60h), Ryzen 5000 "{{amd|Lucienne|l=core}}" (Model 68h), Ryzen Embedded V2000 "{{amd|Grey Hawk|l=core}}" | ||

| + | |- | ||

| + | | Type 2 | ||

| + | | {{amd|CPUID#Family 25 (19h)|Family 19h}} Models 50h–5Fh | ||

| + | | {{amd|Zen 3|l=arch}} | ||

| + | | [[7 nm]] | ||

| + | | Ryzen 5000 "{{amd|Cezanne|l=core}}" (Model 50h) | ||

| + | |} | ||

| + | |||

| + | All FP6 packages carry a monolithic die which integrates eight CPU cores, two memory controllers, a graphics processor, and a controller hub. "Renoir" and "Cezanne" processors are also available in a desktop processor package for {{\\|Socket AM4}}. | ||

| + | |||

| + | FP6 supports DDR4 and LPDDR4x memory. The DDR4 interface offers two 64/72-bit channels and supports UDIMMs, SO-DIMMs, or DRAM Down (soldered to the motherboard) consisting of 8 or 16 x8 devices, or 4 or 8 x16 devices, i.e. up to one single or double rank DIMM per channel. In LPDDR4x mode the memory interface consists of two 64-bit channels with two 32-bit subchannels. It supports four x32 DRAM devices, each point-to-point connected to one subchannel. | ||

| + | |||

| + | FP6 has two PCIe interfaces, an 8-lane interface designated for discrete GPU attachment and a 12-lane general purpose interface where up to four lanes can be configured as SATA link. This interface is generally used for M.2 NVMe/SATA SSD connectors, M.2 WiFi, SATA ports, and on-board PCIe devices. Type-1 processors actually integrate one 16-lane, 3-port GFX controller and one 16-lane, 7-port controller but only a subset of these lanes are pinned out on the FP6 package. | ||

| + | |||

| + | Type-1 processors support two (backplane?) Ethernet ports,<!--AMD-55922--> if those are available on package FP6, perhaps supported only on embedded processors, is unclear. | ||

=== Features === | === Features === | ||

| − | * | + | * Lidless micro [[ball grid array]] package with stiffener frame, 35 mm × 25 mm × 1.38 mm |

| + | ** 1140 balls, 0.65 mm non-uniform pitch | ||

| + | ** Organic substrate, [[flip chip]] die attachment | ||

| − | * 2 × 64/72 bit DDR4 SDRAM interface | + | * 2 × 64/72 bit DDR4 SDRAM interface |

| − | ** Up to 2 DIMMs | + | ** Up to 1600 MHz, PC4-25600 (DDR4-3200), 51.2 GB/s total raw bandwidth |

| − | * Or 4 × 32 bit LPDDR4x SDRAM interface | + | ** Up to 2 DIMMs, one per channel |

| − | ** Up to 32 GiB total | + | ** {{abbr|SR}}/{{abbr|DR}} {{abbr|UDIMM}} or {{abbr|SO-DIMM}} or x8/x16 DRAM Down |

| + | ** ECC supported<!--V2000 specifications--> | ||

| + | ** Max. total memory capacity 64 GiB using two 32 GiB DIMMs | ||

| + | * ''Or'' 4 × 32 bit LPDDR4x SDRAM interface | ||

| + | ** Up to 2133 MHz, LPDDR4X-4266, 68.27 GB/s total raw bandwidth | ||

| + | ** x32 DRAM Down | ||

| + | ** Up to 32 GiB total | ||

| − | * PCIe | + | * 8-lane {{abbr|GFX}} PCIe interface |

| − | + | :{| class="wikitable" style="text-align:center" | |

| − | + | |Lane||23||22||21||20||19||18||17||16||15||14||13||12||11||10||9||8 | |

| − | + | |- | |

| + | |GFX||7||6||5||4||3||2||1||0||N/A||N/A||N/A||N/A||N/A||N/A||N/A||N/A | ||

| + | |- | ||

| + | | rowspan="2"|PCIe || colspan="8"|x8 || colspan="8"| | ||

| + | |- | ||

| + | | colspan="4"|x4 || colspan="4"|x4 || colspan="4"| || colspan="4"| | ||

| + | |- | ||

| + | | || colspan="4"|PHY || colspan="4"|PHY || colspan="4"|N/A || colspan="4"|N/A | ||

| + | |} | ||

| + | :* PCIe Gen 1, 2, 3 (8 GT/s), configurable 1x8 or 2x4 | ||

| − | * Up to | + | * 12-lane {{abbr|GPP}} PCIe interface |

| − | ** | + | :{| class="wikitable" style="text-align:center" |

| + | |Lane||15||14||13||12||11||10||9||8||7||6||5||4||3||2||1||0 | ||

| + | |- | ||

| + | |GPP||N/A||N/A||N/A||N/A||11||10||9||8||7||6||5||4||3||2||1||0 | ||

| + | |- | ||

| + | | rowspan="3"|PCIe || colspan="4"| || colspan="4"|x4 || colspan="4"|x4 || colspan="4"|x4 | ||

| + | |- | ||

| + | | colspan="2"| || colspan="2"| || colspan="2"|x2 || colspan="2"|x2 || colspan="2"|x2 || colspan="2"|x2 || colspan="2"|x2 || colspan="2"|x2 | ||

| + | |- | ||

| + | | || || || ||x1||x1||x1||x1||x1||x1||x1||x1||x1||x1||x1||x1 | ||

| + | |- | ||

| + | |SATA|| || || || || || ||3||2|| || || || ||1||0|| || | ||

| + | |- | ||

| + | | || colspan="4"|N/A || colspan="4"|PHY || colspan="4"|PHY || colspan="2"|PHY || colspan="2"|PHY | ||

| + | |} | ||

| + | :* PCIe Gen 1, 2, 3 (8 GT/s) | ||

| + | :* Up to 7 ports configurable x4, x2, x1 with power-of-two alignment (e.g. 1x4 + 2x1 + 3x2) | ||

| + | :* SATA Express supported on lanes 2-3 and 8-9 (two SATA controllers) | ||

| + | :* SATA Gen 1, 2, 3 (6 Gb/s) protocol supported on lanes 2, 3, 8, and 9 | ||

| + | :* Lanes 0-1, 2-3, 4-7, and 8-11 share a PHY group and must use the same protocol (PCIe or SATA) | ||

| + | :* Lane polarity inversion, per port lane reversal | ||

| + | |||

| + | * Four digital display interfaces DP0-DP3 | ||

| + | ** {{abbr|DP}} 1.4, DP++, {{abbr|eDP}} 1.3, <abbr title="Single-Link">SL</abbr> {{abbr|DVI}}, {{abbr|HDMI}} 2.1 protocols; {{abbr|LVDS}} and {{abbr|VGA}} via external DP to LVDS and DP to VGA translator | ||

| + | ** DP2-DP3 rerouted on die to USBC0, USBC4 for DP Alt Mode | ||

** Resolution up to 4096 × 2160 | ** Resolution up to 4096 × 2160 | ||

| − | * | + | * Eight USB ports from two USB controllers (ports 0-3 and 4-7) |

| − | ** 2 × USB 1.1, 2.0, 3.1 (10 Gb/s), Type-C | + | ** 2 × USB 1.1, 2.0, 3.2 Gen 1, 2 (10 Gb/s), Type-C, DP Alt Mode, Power Delivery capable |

| − | ** 2 × USB 1.1, 2.0, 3.1 (10 Gb/s) | + | ** 2 × USB 1.1, 2.0, 3.2 Gen 1, 2 (10 Gb/s), Type-A |

** 4 × USB 1.1, 2.0 | ** 4 × USB 1.1, 2.0 | ||

| − | |||

| − | |||

| − | Note some processor models support only a subset of these features. The chip may implement additional features which are undocumented or unavailable in the FP6 package | + | * Low speed interfaces (some sharing pins): |

| + | ** {{abbr|HDA}}/{{abbr|TDM}}/{{abbr|I<sup>2</sup>S}}/{{abbr|DMIC|Digital Microphone (Pulse-Density Modulation) interface}} | ||

| + | ** 1 × 4-wire or 2 × 2-wire {{abbr|UART}} | ||

| + | ** {{abbr|LPC}} | ||

| + | ** 2 × 1/2/4-bit {{abbr|SPI/eSPI}} | ||

| + | ** 4 × {{abbr|I<sup>2</sup>C}} | ||

| + | ** 2 × {{abbr|SMBus}} | ||

| + | ** {{abbr|SFH}} interface | ||

| + | ** {{abbr|GPIO}} | ||

| + | |||

| + | Note some processor models support only a subset of these features. The chip may implement additional features which are undocumented or unavailable in the FP6 package. | ||

== Processors using package FP6 == | == Processors using package FP6 == | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

<!-- NOTE: | <!-- NOTE: | ||

| − | + | This table is generated automatically from the data in the actual articles. | |

| − | + | If a microprocessor is missing from the list, an appropriate article for it needs to be | |

| − | + | created and tagged accordingly. | |

| − | + | Missing a chip? please dump its name here: https://en.wikichip.org/wiki/WikiChip:wanted_chips | |

| − | |||

--> | --> | ||

{{comp table start}} | {{comp table start}} | ||

| − | <table class="comptable sortable | + | <table class="comptable sortable"> |

| − | {{comp table header|main| | + | {{comp table header|main|2: |7:CPU|2:GPU|4: }} |

| − | + | {{comp table header|cols|Family|Codename|Microarch.|Cores|Threads|L2$|L3$|Base|Turbo|Brand|Frequ.|{{abbr|TDP}}|Launched|{{abbr|OPN}}}} | |

| − | {{comp table header|cols|Family| | + | {{#ask: [[Category:microprocessor models by amd]] [[package::~*FP6]] |

| − | {{#ask: [[Category:microprocessor models by amd | + | |?full page name |

| − | + | |?model number | |

| − | + | |?microprocessor family | |

| − | + | |?core name | |

| − | + | |?microarchitecture | |

| − | + | |?core count | |

| − | + | |?thread count | |

| − | + | |?l2$ size | |

| − | + | |?l3$ size | |

| − | + | |?base frequency#GHz | |

| − | + | |?turbo frequency#GHz | |

| − | + | |?integrated gpu | |

| − | + | |?integrated gpu max frequency#MHz | |

| − | + | |?tdp | |

| − | + | |?first launched | |

| − | + | |?part number | |

| + | |sort=model number | ||

| + | |format=template | ||

| + | |template=proc table 3 | ||

| + | |userparam=16 | ||

| + | |mainlabel=- | ||

| + | |valuesep=,<br/> | ||

}} | }} | ||

| − | {{comp table count|ask=[[Category:microprocessor models by amd | + | {{comp table count|ask=[[Category:microprocessor models by amd]] [[package::~*FP6]]}} |

</table> | </table> | ||

{{comp table end}} | {{comp table end}} | ||

| + | |||

| + | == Photos == | ||

| + | {{empty section}} | ||

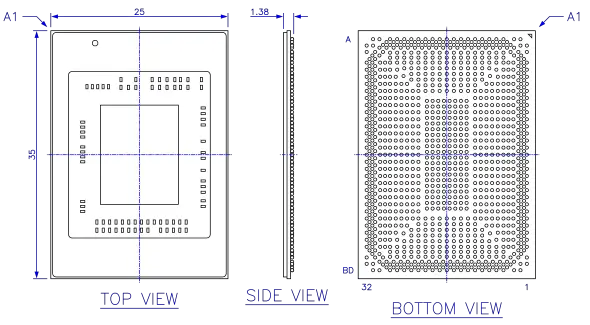

== Package Diagram == | == Package Diagram == | ||

| Line 91: | Line 171: | ||

Approximate dimensions of the "{{amd|Renoir|l=core}}" package. All dimensions in millimeters. | Approximate dimensions of the "{{amd|Renoir|l=core}}" package. All dimensions in millimeters. | ||

| − | == | + | == Pin Map == |

| + | {{empty section}} | ||

| + | |||

| + | === Pin Description === | ||

| + | <!--AMD-56178-1.03 does not document ECC pins or a DQS_H/L[8]. V2000 specifications are adamant that these processors come in a FP6 package and support ECC in DDR4 mode.--> | ||

| + | {| class="wikitable sortable" | ||

| + | !Signal!!Description | ||

| + | |- | ||

| + | |MA/MB_ACT_L||DDR4 DRAM Channel A/B Activation Command | ||

| + | |- | ||

| + | |MA/MB_ADD13_BANK2||DDR4 DRAM Column/Row Address 13 or Bank Address 2 | ||

| + | |- | ||

| + | |MA/MB_ADD[12:0]||DDR4 DRAM Column/Row Address | ||

| + | |- | ||

| + | |MA/MB_BANK[1:0]||DDR4 DRAM Bank Address | ||

| + | |- | ||

| + | |MA/MB_BG[1:0]||DDR4 DRAM Bank Group | ||

| + | |- | ||

| + | |MA/MB_CAS_L_ADD[15]||DDR4 DRAM Column Address Strobe or Column/Row Address 15 | ||

| + | |- | ||

| + | |MA/MB_CKE[1:0]||DDR4 DRAM Clock Enable | ||

| + | |- | ||

| + | |MA/MB_CLK_H/L[1:0]||DDR4 DRAM Differential Clock | ||

| + | |- | ||

| + | |MA/MB_CS_L[1:0]||DDR4 DRAM Chip Select | ||

| + | |- | ||

| + | |MA/MB_DATA[63:0]||DDR4 DRAM Data Bus | ||

| + | |- | ||

| + | |MA/MB_DM[7:0]||DDR4 DRAM Data Mask | ||

| + | |- | ||

| + | |MA/MB_DQS_H/L[7:0]||DDR4 DRAM Differential Data Strobe | ||

| + | |- | ||

| + | |MA/MB_ODT[1:0]||DDR4 DRAM Enable Pin for On Die Termination | ||

| + | |- | ||

| + | |MA/MB_RAS_L_ADD[16]||DDR4 DRAM Row Address Strobe or Column/Row Address 16 | ||

| + | |- | ||

| + | |MA/MB_WE_L_ADD[14]||DDR4 DRAM Write Enable or Column/Row Address 14 | ||

| + | |- | ||

| + | |MA/MB_ALERT_L||DRAM Alert input (CRC error and Command/Address parity error) | ||

| + | |- | ||

| + | |MA/MB_EVENT_L||DRAM Thermal Event input | ||

| + | |- | ||

| + | |MA/MB_PAROUT||DRAM Command and Address Parity output | ||

| + | |- | ||

| + | |MA/MB_RESET_L||DRAM Reset output | ||

| + | |- | ||

| + | |M_DDR4||DRAM Mode Select (DDR4: VDDIO_MEM_S3, LPDDR4: VSS) | ||

| + | |- | ||

| + | |M_LPDDR4||DRAM Mode Select (DDR4: VSS, LPDDR4: VDDIO_MEM_S3) | ||

| + | |- | ||

| + | |MA/MB_TEST||LPDDR4 DRAM Channel A/B Test | ||

| + | |- | ||

| + | |MAA/MAB/MBA/MBB_CA[5:0]||LPDDR4 DRAM Channel A/B Subchannel A/B Command/Address Bus | ||

| + | |- | ||

| + | |MAA/MAB/MBA/MBB_CKE[1:0]||LPDDR4 DRAM Channel A/B Subchannel A/B Clock Enable | ||

| + | |- | ||

| + | |MAA/MAB/MBA/MBB_CKT/CKC||LPDDR4 DRAM Channel A/B Subchannel A/B Differential Clock (True/Complement) | ||

| + | |- | ||

| + | |MAA/MAB/MBA/MBB_CS_L[1:0]||LPDDR4 DRAM Channel A/B Subchannel A/B Chip Select | ||

| + | |- | ||

| + | |MAA/MAB/MBA/MBB_DATA[31:0]||LPDDR4 DRAM Channel A/B Subchannel A/B Data Bus | ||

| + | |- | ||

| + | |MAA/MAB/MBA/MBB_DM[3:0]||LPDDR4 DRAM Channel A/B Subchannel A/B Data Mask | ||

| + | |- | ||

| + | |MAA/MAB/MBA/MBB_DQS_H/L[3:0]||LPDDR4 DRAM Channel A/B Subchannel A/B Differential Data Strobe | ||

| + | |- | ||

| + | |P_GFX_RXP/RXN[7:0]||PCIe Receive Data Differential Pairs | ||

| + | |- | ||

| + | |P_GFX_TXP/TXN[7:0]||PCIe Transmit Data Differential Pairs | ||

| + | |- | ||

| + | |P_GPP_RXP/RXN[11:0]||PCIe Receive Data Differential Pairs | ||

| + | |- | ||

| + | |P_GPP_TXP/TXN[11:0]||PCIe Transmit Data Differential Pairs | ||

| + | |- | ||

| + | |PCIE_RST0_L||Reset for PCIe devices or SPI TPM | ||

| + | |- | ||

| + | |PCIE_RST1_L||Reset for PCIe devices | ||

| + | |- | ||

| + | |SATA0/SATA1_RXP/RXN||SATA Receive Data Differential Pairs (alt. func. of GPP[2]/GPP[3]) | ||

| + | |- | ||

| + | |SATA0/SATA1_TXP/TXN||SATA Transmit Data Differential Pairs | ||

| + | |- | ||

| + | |SATA2/SATA3_RXP/RXN||SATA Receive Data Differential Pairs (alt. func. of GPP[8]/GPP[9]) | ||

| + | |- | ||

| + | |SATA2/SATA3_TXP/TXN||SATA Transmit Data Differential Pairs | ||

| + | |- | ||

| + | |DEVSLP0/DEVSLP1||{{abbr|DEVSLP}} for SATA port 0 & 2 / 1 & 3 | ||

| + | |- | ||

| + | |DP0-DP3_TXP/TXN[3:0]||DisplayPort 0-3 Main Link Differential Transmitter Lane 0-3 or {{abbr|DVI}}/{{abbr|HDMI}} Channel 2, 1, 0, Clock | ||

| + | |- | ||

| + | |DP0-DP3_AUXP/AUXN||DisplayPort 0-3 Auxiliary Channel or DVI/HDMI DDC Clock, Data | ||

| + | |- | ||

| + | |DP0-DP3_HPD||DisplayPort 0-3 Hot Plug Detect input | ||

| + | |- | ||

| + | |DP0_BLON||Display Panel Backlight Enable | ||

| + | |- | ||

| + | |DP0_DIGON||Display Panel Power Enable | ||

| + | |- | ||

| + | |DP0_VARY_BL||Display Backlight Brightness Control | ||

| + | |- | ||

| + | |DP_STEREOSYNC||StereoSync output for shutter glasses | ||

| + | |- | ||

| + | |USBC0/USBC4_RX1P/RX1N||USB Port 0/4 USB-C Receive Differential Pairs or DisplayPort 2/3 Transmitter Lane 3 | ||

| + | |- | ||

| + | |USBC0/USBC4_TX1P/TX1N||USB Port 0/4 USB-C Transmit Differential Pairs or DisplayPort 2/3 Transmitter Lane 2 | ||

| + | |- | ||

| + | |USBC0/USBC4_RX2P/RX2N||USB Port 0/4 USB-C Receive Differential Pairs or DisplayPort 2/3 Transmitter Lane 0 | ||

| + | |- | ||

| + | |USBC0/USBC4_TX2P/TX2N||USB Port 0/4 USB-C Transmit Differential Pairs or DisplayPort 2/3 Transmitter Lane 1 | ||

| + | |- | ||

| + | |USB1/USB5_RXP/RXN||USB Port 1/5 USB3 Super Speed Receive Differential Pairs | ||

| + | |- | ||

| + | |USB1/USB5_TXP/TXN||USB Port 1/5 USB3 Super Speed Transmit Differential Pairs | ||

| + | |- | ||

| + | |USB(0-7)_DP/DN||USB Port 0-7 USB2 I/O Differential Pairs | ||

| + | |- | ||

| + | |USBC_I2C_SCL||{{abbr|I<sup>2</sup>C}} Clock for USB-C PD Control | ||

| + | |- | ||

| + | |USBC_I2C_SDA||I<sup>2</sup>C Data for USB-C PD Control | ||

| + | |- | ||

| + | |USB_OC(0-3)_L||USB Over Current signal from USB connector | ||

| + | |- | ||

| + | |AZ_BITCLK||[[wikipedia:Intel High Definition Audio|Azalia HD Audio]] Interface Bit Clock | ||

| + | |- | ||

| + | |AZ_RST_L||HDA Reset | ||

| + | |- | ||

| + | |AZ_SDIN(0-2)||HDA Serial Data Input from Codec 0-2 | ||

| + | |- | ||

| + | |AZ_SDOUT||HDA Serial Data Output to Codec | ||

| + | |- | ||

| + | |AZ_SYNC||HDA Sync signal to Codec | ||

| + | |- | ||

| + | |TDM_BCLK_MIC||{{abbr|TDM}}/{{abbr|I<sup>2</sup>S}}<ref>In this context {{abbr|TDM}} refers to an unstandardized extension of the {{abbr|I<sup>2</sup>S}} protocol to transmit more than two channels over a single data line.</ref> Mic Serial Clock Input from Codec | ||

| + | |- | ||

| + | |TDM_DATA_MIC||TDM Mic Serial Data Input | ||

| + | |- | ||

| + | |TDM_FRM_MIC||TDM Mic Word Select / Frame Sync Input | ||

| + | |- | ||

| + | |TDM_BCLK_PLAYBACK||TDM Playback Serial Clock Input from Codec | ||

| + | |- | ||

| + | |TDM_DATA_PLAYBACK||TDM Playback Serial Data Output to Codec | ||

| + | |- | ||

| + | |TDM_FRM_PLAYBACK||TDM Playback Word Select / Frame Sync Input | ||

| + | |- | ||

| + | |TDM_BCLK_BT||TDM {{abbr|BT}} Serial Clock Input | ||

| + | |- | ||

| + | |TDM_DOUT_BT||TDM BT Serial Data Output | ||

| + | |- | ||

| + | |{{abbr|FCH}}_{{abbr|ACP}}_I2S_LRCLK_BT||TDM BT Word Select (Left-Right Clock) Input | ||

| + | |- | ||

| + | |FCH_ACP_I2S_SDIN_BT||TDM BT Serial Data Input | ||

| + | |- | ||

| + | |{{abbr|ACP}}_{{abbr|WOV}}_CLK||Digital Microphone Clock Output | ||

| + | |- | ||

| + | |ACP_WOV_MIC0_MIC1_DATA||DMIC Data Input (2 ch {{abbr|PDM}}) | ||

| + | |- | ||

| + | |ACP_WOV_MIC2_MIC3_DATA||DMIC Data | ||

| + | |- | ||

| + | |ACP_WOV_MIC4_MIC5_DATA||DMIC Data | ||

| + | |- | ||

| + | |SPKR||PC Speaker/Beeper PWM Output | ||

| + | |- | ||

| + | |UART0_CTS_L||{{abbr|UART}}0 Clear To Send Input (alt. func. of UART1_TXD) | ||

| + | |- | ||

| + | |UART0_INTR||UART0 Interrupt Request Input | ||

| + | |- | ||

| + | |UART0_RTS_L||UART0 Request To Send Output (UART1_RXD) | ||

| + | |- | ||

| + | |UART0/UART1_RXD||UART Receive Data | ||

| + | |- | ||

| + | |UART0/UART1_TXD||UART Transmit Data | ||

| + | |- | ||

| + | |SPI_CLK||{{abbr|SPI}} Clock Output | ||

| + | |- | ||

| + | |SPI_CLK2||SPI Clock Output | ||

| + | |- | ||

| + | |SPI_DO||SPI Data Out or Data 0 for multi-I/O SPI/eSPI device | ||

| + | |- | ||

| + | |SPI_DI||SPI Data In or Data 1 | ||

| + | |- | ||

| + | |SPI_WP_L||SPI Write Protect or Data 2 | ||

| + | |- | ||

| + | |SPI_HOLD_L||SPI Hold Signal (asserted low to hold the SPI transaction) or Data 3 | ||

| + | |- | ||

| + | |SPI_CS(1-3)_L||Chip Select for SPI ROM or other devices | ||

| + | |- | ||

| + | |SPI_TPM_CS_L||Chip Select for SPI {{abbr|TPM}} | ||

| + | |- | ||

| + | |SPI_ROM_REQ||SPI ROM Request | ||

| + | |- | ||

| + | |SPI_ROM_GNT||SPI ROM Grant | ||

| + | |- | ||

| + | |ESPI_CLK||[[wikipedia:Serial Peripheral Interface|Enhanced SPI]] Clock Output (SPI_CLK/ESPI_CLK) | ||

| + | |- | ||

| + | |ESPI_DATA||ESPI Data (SPI_DI) | ||

| + | |- | ||

| + | |ESPI1_DATA[3:0]||ESPI 1 Data[0], Data[1:0], Data[3:0] Input/Output (alt. func. of LAD0-LAD3) | ||

| + | |- | ||

| + | |ESPI_ALERT_L||ESPI Alert Input (alt. func. of LDRQ0_L) | ||

| + | |- | ||

| + | |ESPI_CS_L||ESPI Chip Select (SPI_CS2_L/ESPI_CS_L) | ||

| + | |- | ||

| + | |ESPI_RESET_L||ESPI Reset Input (ESPI_RESET_L/KBRST_L) | ||

| + | |- | ||

| + | |LAD(0-3)||{{abbr|LPC}} Command/Address/Data | ||

| + | |- | ||

| + | |LDRQ0_L||Encoded DMA/Bus Master Request 0 | ||

| + | |- | ||

| + | |LFRAME_L||LPC Bus Frame | ||

| + | |- | ||

| + | |LPCCLK(0-1)||LPC 33 MHz Clock | ||

| + | |- | ||

| + | |LPC_CLKRUN_L||LPC CLKRUN Signal | ||

| + | |- | ||

| + | |LPC_PD_L||LPC Power Down | ||

| + | |- | ||

| + | |LPC_PME_L||LPC Power Management Event | ||

| + | |- | ||

| + | |LPC_RST_L||LPC Reset output or SPI TPM Reset | ||

| + | |- | ||

| + | |SERIRQ||Serial IRQ for DMA | ||

| + | |- | ||

| + | |I2C(0-3)_SCL||{{abbr|I<sup>2</sup>C}} Bus 0-3 Clock | ||

| + | |- | ||

| + | |I2C(0-3)_SDA||I<sup>2</sup>C Bus 0-3 Data | ||

| + | |- | ||

| + | |SMBUS(0-1)_I2C_SCL||{{abbr|SMBus}} Clock (alt. func. of I2C2, I2C3) | ||

| + | |- | ||

| + | |SMBUS(0-1)_I2C_SDA||SMBus Data | ||

| + | |- | ||

| + | |SFH1_SCL||{{abbr|SFH}} bus Clock | ||

| + | |- | ||

| + | |SFH1_SDA||SFH bus Data | ||

| + | |- | ||

| + | |SFH_IPIO*||SFH Sensor | ||

| + | |- | ||

| + | |AGPIO*||Advanced {{abbr|GPIO}} pin for interrupt, wake, or I/O | ||

| + | |- | ||

| + | |EGPIO*||Enhanced GPIO for I/O only | ||

| + | |- | ||

| + | |AC_PRES||AC Power Present Input | ||

| + | |- | ||

| + | |BLINK||Blink LED S-state Indicator | ||

| + | |- | ||

| + | |GA20IN|| | ||

| + | |- | ||

| + | |INTRUDER_ALERT|| | ||

| + | |- | ||

| + | |KBRST_L||Keyboard Controller Reset Input (warm reset) | ||

| + | |- | ||

| + | |LLB_L||Low Low Bat signal from battery charger circuit | ||

| + | |- | ||

| + | |PWR_BTN_L||Power Button Input; Requests sleep state or causes wake event | ||

| + | |- | ||

| + | |PWR_GOOD||Power Good Input; Asserted when all voltages are within specification | ||

| + | |- | ||

| + | |PWROK||Power OK; Asserted by the processor after all power planes are active, the system clock generators are powered up and run stably | ||

| + | |- | ||

| + | |RESET_L||Reset signal | ||

| + | |- | ||

| + | |RSMRST_L||Resume Reset; Asserted on power up, deasserted when S5 power supplies are within specification | ||

| + | |- | ||

| + | |S0A3_GPIO|| | ||

| + | |- | ||

| + | |SLP_S3/S5_L||S3/S5 Sleep State Power Plane Control Signals for voltage regulator | ||

| + | |- | ||

| + | |SYS_RESET_L||System Reset input (reset button) | ||

| + | |- | ||

| + | |WAKE_L||PCIe WAKE_L signal, wake system out of sleep state | ||

| + | |- | ||

| + | |GPP_CLK(0-6)P/N||100 MHz Differential PCIe Reference Clock Outputs | ||

| + | |- | ||

| + | |CLK_REQ(0-6)_L||PCIe Clock Request | ||

| + | |- | ||

| + | |X32K_X1/X2||32768 Hz Real Time Clock XTAL for the integrated RTC | ||

| + | |- | ||

| + | |X48M_X1/X2||48 MHz clock XTAL for the integrated clock generator | ||

| + | |- | ||

| + | |RTCCLK||32768 Hz Real Time Clock output for a device requiring an RTC clock | ||

| + | |- | ||

| + | |X48M_OSC||48 MHz clock output for devices requiring a single-ended OSC input | ||

| + | |- | ||

| + | |ALERT_L||{{abbr|SB-TSI}} Interrupt | ||

| + | |- | ||

| + | |SIC||Sideband Interface ({{abbr|SB-TSI}}) Clock | ||

| + | |- | ||

| + | |SID||Sideband Interface Data | ||

| + | |- | ||

| + | |FANIN0||Fan 0 tachometer input | ||

| + | |- | ||

| + | |FANOUT0||Fan 0 PWM output | ||

| + | |- | ||

| + | |PROCHOT_L||Asserted to force the processor into {{abbr|HTC}}-active state | ||

| + | |- | ||

| + | |THERMTRIP_L||{{x86|Thermal protection|Temperature Trip}} Output | ||

| + | |- | ||

| + | |DBREQ_L||Debug Request input to JTAG controller | ||

| + | |- | ||

| + | |TCK||{{abbr|JTAG}} Clock | ||

| + | |- | ||

| + | |TDI||JTAG Data Input | ||

| + | |- | ||

| + | |TDO||JTAG Data Output | ||

| + | |- | ||

| + | |TMS||JTAG Mode Select | ||

| + | |- | ||

| + | |TRST_L||JTAG Reset | ||

| + | |- | ||

| + | |TEST*||Test Signals | ||

| + | |- | ||

| + | |SVC0||Serial VID ([[SVID2]]) Clock for VDDCR/VDDCR_SOC regulator | ||

| + | |- | ||

| + | |SVD0||Serial VID Data | ||

| + | |- | ||

| + | |SVT0||Serial VID Telemetry | ||

| + | |- | ||

| + | |VDDBT_RTC_G||Integrated Real Time Clock battery power supply | ||

| + | |- | ||

| + | |VDDCR||Core power supply | ||

| + | |- | ||

| + | |VDDCR_SENSE||Differential (with VSS_SENSE_A) feedback for VDDCR regulator | ||

| + | |- | ||

| + | |VDDCR_SOC||Power supply for integrated Northbridge | ||

| + | |- | ||

| + | |VDDCR_SOC_SENSE||Differential (with VSS_SENSE_A) feedback for VDDCR_SOC regulator | ||

| + | |- | ||

| + | |VDDIO_AUDIO||1.8 V or 1.5 V or 1.2 V always on | ||

| + | |- | ||

| + | |VDDIO_MEM_S3||Power supply for DIMMs and an auxiliary supply for the DDR section of the processor, 1.2 V for DDR4 | ||

| + | |- | ||

| + | |VDDIO_MEM_S3_SENSE||Differential (with VSS_SENSE_A) feedback for VDDIO_MEM_S3 regulator | ||

| + | |- | ||

| + | |VDDIO_VPH||Power supply for DisplayPort 0, 1.8 V, or optional 1.2 V for {{abbr|eDP}} | ||

| + | |- | ||

| + | |VDDP||Power supply for PCIe GPP, PCIe GFX, DisplayPort, and SATA PHY logic | ||

| + | |- | ||

| + | |VDDP_SENSE||Differential (with VSS_SENSE_B) feedback for VDDP regulator | ||

| + | |- | ||

| + | |VDDP_S5||Always on power supply for USB physical layer | ||

| + | |- | ||

| + | |VDDP_S5_SENSE||Differential (with VSS_SENSE_B) feedback for VDDP_S5 regulator | ||

| + | |- | ||

| + | |VDD_18||1.8 V supply voltage for analog circuits | ||

| + | |- | ||

| + | |VDD_18_S5||Always on 1.8 V supply voltage for analog circuits | ||

| + | |- | ||

| + | |VDD_33||3.3 V supply voltage | ||

| + | |- | ||

| + | |VDD_33_S5||Always on 3.3 V supply voltage | ||

| + | |- | ||

| + | |VSS||Ground | ||

| + | |- | ||

| + | |VSS_SENSE_A||VSS Sense pin for VDDCR/VDDCR_SOC regulator | ||

| + | |- | ||

| + | |VSS_SENSE_B||VSS Sense pin for VDDP regulator | ||

| + | |- | ||

| + | |RSVD||Reserved | ||

| + | |} | ||

| + | |||

| + | <references/> | ||

| + | |||

| + | == Bibliography == | ||

* {{cite techdoc|title=Processor Programming Reference (PPR) for AMD Family 17h Model 60h, Revision A1 Processors|url=https://www.amd.com/system/files/TechDocs/55922-A1-PUB.zip|publ=AMD|pid=55922|rev=3.05|date=2020-07-07}} | * {{cite techdoc|title=Processor Programming Reference (PPR) for AMD Family 17h Model 60h, Revision A1 Processors|url=https://www.amd.com/system/files/TechDocs/55922-A1-PUB.zip|publ=AMD|pid=55922|rev=3.05|date=2020-07-07}} | ||

| − | * {{cite techdoc|title=AMD Ryzen™ Embedded V2000 Processor Family|url=https://www.amd.com/system/files/documents/v2000-product-brief.pdf|publ=AMD|pid=20650345|rev=A|date=2020}} | + | * {{cite techdoc|title=FP6 Processor Motherboard Design Guide|publ=AMD|pid=56178|rev=1.03|date=2020-01}} |

| + | * {{cite techdoc|title=Product Brief: AMD Ryzen™ Embedded V2000 Processor Family|url=https://www.amd.com/system/files/documents/v2000-product-brief.pdf|publ=AMD|pid=20650345|rev=A|date=2020}} | ||

| + | * [https://www.amd.com/en/products/specifications/embedded "Embedded Processor Specifications"] AMD.com. | ||

== See also == | == See also == | ||

* {{\\|FP5|Package FP5}} | * {{\\|FP5|Package FP5}} | ||

* {{\\|Socket AM4}} | * {{\\|Socket AM4}} | ||

| − | |||

[[Category:amd]] | [[Category:amd]] | ||

Revision as of 14:58, 23 April 2022

| Edit Values | |

| Package FP6 | |

| General Info | |

| Designer | AMD |

| Introduction | March 16, 2020 (launched) |

| Market | Mobile, Embedded |

| Microarchitecture | Zen 2, Zen 3 |

| TDP | 55 W 55,000 mW 0.0738 hp 0.055 kW |

| Package | |

| Name | FP6 |

| Type | FC-OBGA |

| Contacts | 1140 |

| Dimension | 35 mm 3.5 cm × 25 mm1.378 in 2.5 cm × 1.38 mm0.984 in 0.0543 in |

| Pitch | 0.65 mm 0.0256 in |

FP6 is a CPU package of AMD Ryzen mobile and embedded processors, the successor to the FP5 package. Its counterpart for desktop processors is the PGA-1331 package for Socket AM4.

Contents

Overview

FP6 is a 1140-contact, 0.65 mm non-uniform pitch, organic ball grid array package with a size of 35 mm × 25 mm × 1.38 mm.

It supports two 72-bit channels of DDR4 memory or four 32-bit channels of LPDDR4x memory, two PCIe Gen 3 I/O interfaces with 20 lanes total, four digital display interfaces, four USB 3.2 Gen 2 ports, four USB 2.0 ports, and up to four SATA Gen 3 ports.

The following AMD processor families use the FP6 package:

| CPU Family | Microarch. | Process | Products | |

|---|---|---|---|---|

| Type 1 | Family 17h Models 60h–6Fh | Zen 2 | 7 nm | Ryzen 4000 "Renoir" (Model 60h), Ryzen 5000 "Lucienne" (Model 68h), Ryzen Embedded V2000 "Grey Hawk" |

| Type 2 | Family 19h Models 50h–5Fh | Zen 3 | 7 nm | Ryzen 5000 "Cezanne" (Model 50h) |

All FP6 packages carry a monolithic die which integrates eight CPU cores, two memory controllers, a graphics processor, and a controller hub. "Renoir" and "Cezanne" processors are also available in a desktop processor package for Socket AM4.

FP6 supports DDR4 and LPDDR4x memory. The DDR4 interface offers two 64/72-bit channels and supports UDIMMs, SO-DIMMs, or DRAM Down (soldered to the motherboard) consisting of 8 or 16 x8 devices, or 4 or 8 x16 devices, i.e. up to one single or double rank DIMM per channel. In LPDDR4x mode the memory interface consists of two 64-bit channels with two 32-bit subchannels. It supports four x32 DRAM devices, each point-to-point connected to one subchannel.

FP6 has two PCIe interfaces, an 8-lane interface designated for discrete GPU attachment and a 12-lane general purpose interface where up to four lanes can be configured as SATA link. This interface is generally used for M.2 NVMe/SATA SSD connectors, M.2 WiFi, SATA ports, and on-board PCIe devices. Type-1 processors actually integrate one 16-lane, 3-port GFX controller and one 16-lane, 7-port controller but only a subset of these lanes are pinned out on the FP6 package.

Type-1 processors support two (backplane?) Ethernet ports, if those are available on package FP6, perhaps supported only on embedded processors, is unclear.

Features

- Lidless micro ball grid array package with stiffener frame, 35 mm × 25 mm × 1.38 mm

- 1140 balls, 0.65 mm non-uniform pitch

- Organic substrate, flip chip die attachment

- 2 × 64/72 bit DDR4 SDRAM interface

- Up to 1600 MHz, PC4-25600 (DDR4-3200), 51.2 GB/s total raw bandwidth

- Up to 2 DIMMs, one per channel

- SR/DR UDIMM or SO-DIMM or x8/x16 DRAM Down

- ECC supported

- Max. total memory capacity 64 GiB using two 32 GiB DIMMs

- Or 4 × 32 bit LPDDR4x SDRAM interface

- Up to 2133 MHz, LPDDR4X-4266, 68.27 GB/s total raw bandwidth

- x32 DRAM Down

- Up to 32 GiB total

- 8-lane GFX PCIe interface

Lane 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 GFX 7 6 5 4 3 2 1 0 N/A N/A N/A N/A N/A N/A N/A N/A PCIe x8 x4 x4 PHY PHY N/A N/A

- PCIe Gen 1, 2, 3 (8 GT/s), configurable 1x8 or 2x4

- 12-lane GPP PCIe interface

Lane 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 GPP N/A N/A N/A N/A 11 10 9 8 7 6 5 4 3 2 1 0 PCIe x4 x4 x4 x2 x2 x2 x2 x2 x2 x1 x1 x1 x1 x1 x1 x1 x1 x1 x1 x1 x1 SATA 3 2 1 0 N/A PHY PHY PHY PHY

- PCIe Gen 1, 2, 3 (8 GT/s)

- Up to 7 ports configurable x4, x2, x1 with power-of-two alignment (e.g. 1x4 + 2x1 + 3x2)

- SATA Express supported on lanes 2-3 and 8-9 (two SATA controllers)

- SATA Gen 1, 2, 3 (6 Gb/s) protocol supported on lanes 2, 3, 8, and 9

- Lanes 0-1, 2-3, 4-7, and 8-11 share a PHY group and must use the same protocol (PCIe or SATA)

- Lane polarity inversion, per port lane reversal

- Four digital display interfaces DP0-DP3

- Eight USB ports from two USB controllers (ports 0-3 and 4-7)

- 2 × USB 1.1, 2.0, 3.2 Gen 1, 2 (10 Gb/s), Type-C, DP Alt Mode, Power Delivery capable

- 2 × USB 1.1, 2.0, 3.2 Gen 1, 2 (10 Gb/s), Type-A

- 4 × USB 1.1, 2.0

- Low speed interfaces (some sharing pins):

Note some processor models support only a subset of these features. The chip may implement additional features which are undocumented or unavailable in the FP6 package.

Processors using package FP6

| CPU | GPU | ||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Model | Family | Codename | Microarch. | Cores | Threads | L2$ | L3$ | Base | Turbo | Brand | Frequ. | TDP | Launched | OPN | |

| 5300U | Ryzen 3 | Lucienne | Zen 2 | 4 | 8 | 2 MiB 2,048 KiB 2,097,152 B 0.00195 GiB | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 2.6 GHz 2,600 MHz 2,600,000 kHz | 3.8 GHz 3,800 MHz 3,800,000 kHz | Radeon Vega 6 | 1,500 MHz 1.5 GHz 1,500,000 KHz | 15 W 15,000 mW 0.0201 hp 0.015 kW | 12 January 2021 | 100-000000376 | |

| 5400U | Ryzen 3 | Cezanne | Zen 3 | 4 | 8 | 2 MiB 2,048 KiB 2,097,152 B 0.00195 GiB | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 2.6 GHz 2,600 MHz 2,600,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | Radeon Vega 6 | 1,600 MHz 1.6 GHz 1,600,000 KHz | 15 W 15,000 mW 0.0201 hp 0.015 kW | 12 January 2021 | 100-000000288 | |

| 5500U | Ryzen 5 | Lucienne | Zen 2 | 6 | 12 | 3 MiB 3,072 KiB 3,145,728 B 0.00293 GiB | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 2.1 GHz 2,100 MHz 2,100,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | Radeon Vega 7 | 1,800 MHz 1.8 GHz 1,800,000 KHz | 15 W 15,000 mW 0.0201 hp 0.015 kW | 12 January 2021 | 100-000000375 | |

| 5600H | Ryzen 5 | Cezanne | Zen 3 | 6 | 12 | 3 MiB 3,072 KiB 3,145,728 B 0.00293 GiB | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 3.3 GHz 3,300 MHz 3,300,000 kHz | 4.2 GHz 4,200 MHz 4,200,000 kHz | Radeon Vega 7 | 1,800 MHz 1.8 GHz 1,800,000 KHz | 45 W 45,000 mW 0.0603 hp 0.045 kW | 12 January 2021 | 100-000000296 | |

| 5600HS | Ryzen 5 | Cezanne | Zen 3 | 6 | 12 | 3 MiB 3,072 KiB 3,145,728 B 0.00293 GiB | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 3 GHz 3,000 MHz 3,000,000 kHz | 4.2 GHz 4,200 MHz 4,200,000 kHz | Radeon Vega 7 | 1,800 MHz 1.8 GHz 1,800,000 KHz | 35 W 35,000 mW 0.0469 hp 0.035 kW | 12 January 2021 | 100-000000296 | |

| 5600U | Ryzen 5 | Cezanne | Zen 3 | 6 | 12 | 3 MiB 3,072 KiB 3,145,728 B 0.00293 GiB | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 2.3 GHz 2,300 MHz 2,300,000 kHz | 4.2 GHz 4,200 MHz 4,200,000 kHz | Radeon Vega 7 | 1,800 MHz 1.8 GHz 1,800,000 KHz | 15 W 15,000 mW 0.0201 hp 0.015 kW | 12 January 2021 | 100-000000287 | |

| 5700U | Ryzen 7 | Lucienne | Zen 2 | 8 | 16 | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 1.8 GHz 1,800 MHz 1,800,000 kHz | 4.3 GHz 4,300 MHz 4,300,000 kHz | Radeon Vega 8 | 1,900 MHz 1.9 GHz 1,900,000 KHz | 15 W 15,000 mW 0.0201 hp 0.015 kW | 12 January 2021 | 100-000000371 | |

| 5800H | Ryzen 7 | Cezanne | Zen 3 | 8 | 16 | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 3.2 GHz 3,200 MHz 3,200,000 kHz | 4.4 GHz 4,400 MHz 4,400,000 kHz | Radeon Vega 8 | 2,000 MHz 2 GHz 2,000,000 KHz | 45 W 45,000 mW 0.0603 hp 0.045 kW | 12 January 2021 | 100-000000295 | |

| 5800HS | Ryzen 7 | Cezanne | Zen 3 | 8 | 16 | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 2.8 GHz 2,800 MHz 2,800,000 kHz | 4.4 GHz 4,400 MHz 4,400,000 kHz | Radeon Vega 8 | 2,000 MHz 2 GHz 2,000,000 KHz | 35 W 35,000 mW 0.0469 hp 0.035 kW | 12 January 2021 | 100-000000295 | |

| 5800U | Ryzen 7 | Cezanne | Zen 3 | 8 | 16 | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 1.9 GHz 1,900 MHz 1,900,000 kHz | 4.4 GHz 4,400 MHz 4,400,000 kHz | Radeon Vega 8 | 2,000 MHz 2 GHz 2,000,000 KHz | 15 W 15,000 mW 0.0201 hp 0.015 kW | 12 January 2021 | 100-000000285 | |

| 5900HS | Ryzen 9 | Cezanne | Zen 3 | 8 | 16 | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 3 GHz 3,000 MHz 3,000,000 kHz | 4.6 GHz 4,600 MHz 4,600,000 kHz | Radeon Vega 8 | 2,100 MHz 2.1 GHz 2,100,000 KHz | 35 W 35,000 mW 0.0469 hp 0.035 kW | 12 January 2021 | 100-000000300 | |

| 5900HX | Ryzen 9 | Cezanne | Zen 3 | 8 | 16 | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 3.3 GHz 3,300 MHz 3,300,000 kHz | 4.6 GHz 4,600 MHz 4,600,000 kHz | Radeon Vega 8 | 2,100 MHz 2.1 GHz 2,100,000 KHz | 45 W 45,000 mW 0.0603 hp 0.045 kW | 12 January 2021 | 100-000000300 | |

| 5980HS | Ryzen 9 | Cezanne | Zen 3 | 8 | 16 | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 3 GHz 3,000 MHz 3,000,000 kHz | 4.8 GHz 4,800 MHz 4,800,000 kHz | Radeon Vega 8 | 2,100 MHz 2.1 GHz 2,100,000 KHz | 35 W 35,000 mW 0.0469 hp 0.035 kW | 12 January 2021 | 100-000000474 | |

| 5980HX | Ryzen 9 | Cezanne | Zen 3 | 8 | 16 | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 3.3 GHz 3,300 MHz 3,300,000 kHz | 4.8 GHz 4,800 MHz 4,800,000 kHz | Radeon Vega 8 | 2,100 MHz 2.1 GHz 2,100,000 KHz | 45 W 45,000 mW 0.0603 hp 0.045 kW | 12 January 2021 | 100-000000474 | |

| PRO 5450U | Ryzen 3 | Cezanne | Zen 3 | 4 | 8 | 2 MiB 2,048 KiB 2,097,152 B 0.00195 GiB | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 2.6 GHz 2,600 MHz 2,600,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | Radeon Vega 6 | 1,600 MHz 1.6 GHz 1,600,000 KHz | 15 W 15,000 mW 0.0201 hp 0.015 kW | 16 March 2021 | 100-000000291 | |

| PRO 5650U | Ryzen 5 | Cezanne | Zen 3 | 6 | 12 | 3 MiB 3,072 KiB 3,145,728 B 0.00293 GiB | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 2.3 GHz 2,300 MHz 2,300,000 kHz | 4.2 GHz 4,200 MHz 4,200,000 kHz | Radeon Vega 7 | 1,800 MHz 1.8 GHz 1,800,000 KHz | 15 W 15,000 mW 0.0201 hp 0.015 kW | 16 March 2021 | 100-000000290 | |

| PRO 5850U | Ryzen 7 | Cezanne | Zen 3 | 8 | 16 | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 1.9 GHz 1,900 MHz 1,900,000 kHz | 4.4 GHz 4,400 MHz 4,400,000 kHz | Radeon Vega 8 | 2,000 MHz 2 GHz 2,000,000 KHz | 15 W 15,000 mW 0.0201 hp 0.015 kW | 16 March 2021 | 100-000000289 | |

| Count: 17 | |||||||||||||||

Photos

| This section is empty; you can help add the missing info by editing this page. |

Package Diagram

Approximate dimensions of the "Renoir" package. All dimensions in millimeters.

Pin Map

| This section is empty; you can help add the missing info by editing this page. |

Pin Description

| Signal | Description |

|---|---|

| MA/MB_ACT_L | DDR4 DRAM Channel A/B Activation Command |

| MA/MB_ADD13_BANK2 | DDR4 DRAM Column/Row Address 13 or Bank Address 2 |

| MA/MB_ADD[12:0] | DDR4 DRAM Column/Row Address |

| MA/MB_BANK[1:0] | DDR4 DRAM Bank Address |

| MA/MB_BG[1:0] | DDR4 DRAM Bank Group |

| MA/MB_CAS_L_ADD[15] | DDR4 DRAM Column Address Strobe or Column/Row Address 15 |

| MA/MB_CKE[1:0] | DDR4 DRAM Clock Enable |

| MA/MB_CLK_H/L[1:0] | DDR4 DRAM Differential Clock |

| MA/MB_CS_L[1:0] | DDR4 DRAM Chip Select |

| MA/MB_DATA[63:0] | DDR4 DRAM Data Bus |

| MA/MB_DM[7:0] | DDR4 DRAM Data Mask |

| MA/MB_DQS_H/L[7:0] | DDR4 DRAM Differential Data Strobe |

| MA/MB_ODT[1:0] | DDR4 DRAM Enable Pin for On Die Termination |

| MA/MB_RAS_L_ADD[16] | DDR4 DRAM Row Address Strobe or Column/Row Address 16 |

| MA/MB_WE_L_ADD[14] | DDR4 DRAM Write Enable or Column/Row Address 14 |

| MA/MB_ALERT_L | DRAM Alert input (CRC error and Command/Address parity error) |

| MA/MB_EVENT_L | DRAM Thermal Event input |

| MA/MB_PAROUT | DRAM Command and Address Parity output |

| MA/MB_RESET_L | DRAM Reset output |

| M_DDR4 | DRAM Mode Select (DDR4: VDDIO_MEM_S3, LPDDR4: VSS) |

| M_LPDDR4 | DRAM Mode Select (DDR4: VSS, LPDDR4: VDDIO_MEM_S3) |

| MA/MB_TEST | LPDDR4 DRAM Channel A/B Test |

| MAA/MAB/MBA/MBB_CA[5:0] | LPDDR4 DRAM Channel A/B Subchannel A/B Command/Address Bus |

| MAA/MAB/MBA/MBB_CKE[1:0] | LPDDR4 DRAM Channel A/B Subchannel A/B Clock Enable |

| MAA/MAB/MBA/MBB_CKT/CKC | LPDDR4 DRAM Channel A/B Subchannel A/B Differential Clock (True/Complement) |

| MAA/MAB/MBA/MBB_CS_L[1:0] | LPDDR4 DRAM Channel A/B Subchannel A/B Chip Select |

| MAA/MAB/MBA/MBB_DATA[31:0] | LPDDR4 DRAM Channel A/B Subchannel A/B Data Bus |

| MAA/MAB/MBA/MBB_DM[3:0] | LPDDR4 DRAM Channel A/B Subchannel A/B Data Mask |

| MAA/MAB/MBA/MBB_DQS_H/L[3:0] | LPDDR4 DRAM Channel A/B Subchannel A/B Differential Data Strobe |

| P_GFX_RXP/RXN[7:0] | PCIe Receive Data Differential Pairs |

| P_GFX_TXP/TXN[7:0] | PCIe Transmit Data Differential Pairs |

| P_GPP_RXP/RXN[11:0] | PCIe Receive Data Differential Pairs |

| P_GPP_TXP/TXN[11:0] | PCIe Transmit Data Differential Pairs |

| PCIE_RST0_L | Reset for PCIe devices or SPI TPM |

| PCIE_RST1_L | Reset for PCIe devices |

| SATA0/SATA1_RXP/RXN | SATA Receive Data Differential Pairs (alt. func. of GPP[2]/GPP[3]) |

| SATA0/SATA1_TXP/TXN | SATA Transmit Data Differential Pairs |

| SATA2/SATA3_RXP/RXN | SATA Receive Data Differential Pairs (alt. func. of GPP[8]/GPP[9]) |

| SATA2/SATA3_TXP/TXN | SATA Transmit Data Differential Pairs |

| DEVSLP0/DEVSLP1 | DEVSLP for SATA port 0 & 2 / 1 & 3 |

| DP0-DP3_TXP/TXN[3:0] | DisplayPort 0-3 Main Link Differential Transmitter Lane 0-3 or DVI/HDMI Channel 2, 1, 0, Clock |

| DP0-DP3_AUXP/AUXN | DisplayPort 0-3 Auxiliary Channel or DVI/HDMI DDC Clock, Data |

| DP0-DP3_HPD | DisplayPort 0-3 Hot Plug Detect input |

| DP0_BLON | Display Panel Backlight Enable |

| DP0_DIGON | Display Panel Power Enable |

| DP0_VARY_BL | Display Backlight Brightness Control |

| DP_STEREOSYNC | StereoSync output for shutter glasses |

| USBC0/USBC4_RX1P/RX1N | USB Port 0/4 USB-C Receive Differential Pairs or DisplayPort 2/3 Transmitter Lane 3 |

| USBC0/USBC4_TX1P/TX1N | USB Port 0/4 USB-C Transmit Differential Pairs or DisplayPort 2/3 Transmitter Lane 2 |

| USBC0/USBC4_RX2P/RX2N | USB Port 0/4 USB-C Receive Differential Pairs or DisplayPort 2/3 Transmitter Lane 0 |

| USBC0/USBC4_TX2P/TX2N | USB Port 0/4 USB-C Transmit Differential Pairs or DisplayPort 2/3 Transmitter Lane 1 |

| USB1/USB5_RXP/RXN | USB Port 1/5 USB3 Super Speed Receive Differential Pairs |

| USB1/USB5_TXP/TXN | USB Port 1/5 USB3 Super Speed Transmit Differential Pairs |

| USB(0-7)_DP/DN | USB Port 0-7 USB2 I/O Differential Pairs |

| USBC_I2C_SCL | I2C Clock for USB-C PD Control |

| USBC_I2C_SDA | I2C Data for USB-C PD Control |

| USB_OC(0-3)_L | USB Over Current signal from USB connector |

| AZ_BITCLK | Azalia HD Audio Interface Bit Clock |

| AZ_RST_L | HDA Reset |

| AZ_SDIN(0-2) | HDA Serial Data Input from Codec 0-2 |

| AZ_SDOUT | HDA Serial Data Output to Codec |

| AZ_SYNC | HDA Sync signal to Codec |

| TDM_BCLK_MIC | TDM/I2S[1] Mic Serial Clock Input from Codec |

| TDM_DATA_MIC | TDM Mic Serial Data Input |

| TDM_FRM_MIC | TDM Mic Word Select / Frame Sync Input |

| TDM_BCLK_PLAYBACK | TDM Playback Serial Clock Input from Codec |

| TDM_DATA_PLAYBACK | TDM Playback Serial Data Output to Codec |

| TDM_FRM_PLAYBACK | TDM Playback Word Select / Frame Sync Input |

| TDM_BCLK_BT | TDM BT Serial Clock Input |

| TDM_DOUT_BT | TDM BT Serial Data Output |

| FCH_ACP_I2S_LRCLK_BT | TDM BT Word Select (Left-Right Clock) Input |

| FCH_ACP_I2S_SDIN_BT | TDM BT Serial Data Input |

| ACP_WOV_CLK | Digital Microphone Clock Output |

| ACP_WOV_MIC0_MIC1_DATA | DMIC Data Input (2 ch PDM) |

| ACP_WOV_MIC2_MIC3_DATA | DMIC Data |

| ACP_WOV_MIC4_MIC5_DATA | DMIC Data |

| SPKR | PC Speaker/Beeper PWM Output |

| UART0_CTS_L | UART0 Clear To Send Input (alt. func. of UART1_TXD) |

| UART0_INTR | UART0 Interrupt Request Input |

| UART0_RTS_L | UART0 Request To Send Output (UART1_RXD) |

| UART0/UART1_RXD | UART Receive Data |

| UART0/UART1_TXD | UART Transmit Data |

| SPI_CLK | SPI Clock Output |

| SPI_CLK2 | SPI Clock Output |

| SPI_DO | SPI Data Out or Data 0 for multi-I/O SPI/eSPI device |

| SPI_DI | SPI Data In or Data 1 |

| SPI_WP_L | SPI Write Protect or Data 2 |

| SPI_HOLD_L | SPI Hold Signal (asserted low to hold the SPI transaction) or Data 3 |

| SPI_CS(1-3)_L | Chip Select for SPI ROM or other devices |

| SPI_TPM_CS_L | Chip Select for SPI TPM |

| SPI_ROM_REQ | SPI ROM Request |

| SPI_ROM_GNT | SPI ROM Grant |

| ESPI_CLK | Enhanced SPI Clock Output (SPI_CLK/ESPI_CLK) |

| ESPI_DATA | ESPI Data (SPI_DI) |

| ESPI1_DATA[3:0] | ESPI 1 Data[0], Data[1:0], Data[3:0] Input/Output (alt. func. of LAD0-LAD3) |

| ESPI_ALERT_L | ESPI Alert Input (alt. func. of LDRQ0_L) |

| ESPI_CS_L | ESPI Chip Select (SPI_CS2_L/ESPI_CS_L) |

| ESPI_RESET_L | ESPI Reset Input (ESPI_RESET_L/KBRST_L) |

| LAD(0-3) | LPC Command/Address/Data |

| LDRQ0_L | Encoded DMA/Bus Master Request 0 |

| LFRAME_L | LPC Bus Frame |

| LPCCLK(0-1) | LPC 33 MHz Clock |

| LPC_CLKRUN_L | LPC CLKRUN Signal |

| LPC_PD_L | LPC Power Down |

| LPC_PME_L | LPC Power Management Event |

| LPC_RST_L | LPC Reset output or SPI TPM Reset |

| SERIRQ | Serial IRQ for DMA |

| I2C(0-3)_SCL | I2C Bus 0-3 Clock |

| I2C(0-3)_SDA | I2C Bus 0-3 Data |

| SMBUS(0-1)_I2C_SCL | SMBus Clock (alt. func. of I2C2, I2C3) |

| SMBUS(0-1)_I2C_SDA | SMBus Data |

| SFH1_SCL | SFH bus Clock |

| SFH1_SDA | SFH bus Data |

| SFH_IPIO* | SFH Sensor |

| AGPIO* | Advanced GPIO pin for interrupt, wake, or I/O |

| EGPIO* | Enhanced GPIO for I/O only |

| AC_PRES | AC Power Present Input |

| BLINK | Blink LED S-state Indicator |

| GA20IN | |

| INTRUDER_ALERT | |

| KBRST_L | Keyboard Controller Reset Input (warm reset) |

| LLB_L | Low Low Bat signal from battery charger circuit |

| PWR_BTN_L | Power Button Input; Requests sleep state or causes wake event |

| PWR_GOOD | Power Good Input; Asserted when all voltages are within specification |

| PWROK | Power OK; Asserted by the processor after all power planes are active, the system clock generators are powered up and run stably |

| RESET_L | Reset signal |

| RSMRST_L | Resume Reset; Asserted on power up, deasserted when S5 power supplies are within specification |

| S0A3_GPIO | |

| SLP_S3/S5_L | S3/S5 Sleep State Power Plane Control Signals for voltage regulator |

| SYS_RESET_L | System Reset input (reset button) |

| WAKE_L | PCIe WAKE_L signal, wake system out of sleep state |

| GPP_CLK(0-6)P/N | 100 MHz Differential PCIe Reference Clock Outputs |

| CLK_REQ(0-6)_L | PCIe Clock Request |

| X32K_X1/X2 | 32768 Hz Real Time Clock XTAL for the integrated RTC |

| X48M_X1/X2 | 48 MHz clock XTAL for the integrated clock generator |

| RTCCLK | 32768 Hz Real Time Clock output for a device requiring an RTC clock |

| X48M_OSC | 48 MHz clock output for devices requiring a single-ended OSC input |

| ALERT_L | SB-TSI Interrupt |

| SIC | Sideband Interface (SB-TSI) Clock |

| SID | Sideband Interface Data |

| FANIN0 | Fan 0 tachometer input |

| FANOUT0 | Fan 0 PWM output |

| PROCHOT_L | Asserted to force the processor into HTC-active state |

| THERMTRIP_L | Temperature Trip Output |

| DBREQ_L | Debug Request input to JTAG controller |

| TCK | JTAG Clock |

| TDI | JTAG Data Input |

| TDO | JTAG Data Output |

| TMS | JTAG Mode Select |

| TRST_L | JTAG Reset |

| TEST* | Test Signals |

| SVC0 | Serial VID (SVID2) Clock for VDDCR/VDDCR_SOC regulator |

| SVD0 | Serial VID Data |

| SVT0 | Serial VID Telemetry |

| VDDBT_RTC_G | Integrated Real Time Clock battery power supply |

| VDDCR | Core power supply |

| VDDCR_SENSE | Differential (with VSS_SENSE_A) feedback for VDDCR regulator |

| VDDCR_SOC | Power supply for integrated Northbridge |

| VDDCR_SOC_SENSE | Differential (with VSS_SENSE_A) feedback for VDDCR_SOC regulator |

| VDDIO_AUDIO | 1.8 V or 1.5 V or 1.2 V always on |

| VDDIO_MEM_S3 | Power supply for DIMMs and an auxiliary supply for the DDR section of the processor, 1.2 V for DDR4 |

| VDDIO_MEM_S3_SENSE | Differential (with VSS_SENSE_A) feedback for VDDIO_MEM_S3 regulator |

| VDDIO_VPH | Power supply for DisplayPort 0, 1.8 V, or optional 1.2 V for eDP |

| VDDP | Power supply for PCIe GPP, PCIe GFX, DisplayPort, and SATA PHY logic |

| VDDP_SENSE | Differential (with VSS_SENSE_B) feedback for VDDP regulator |

| VDDP_S5 | Always on power supply for USB physical layer |

| VDDP_S5_SENSE | Differential (with VSS_SENSE_B) feedback for VDDP_S5 regulator |

| VDD_18 | 1.8 V supply voltage for analog circuits |

| VDD_18_S5 | Always on 1.8 V supply voltage for analog circuits |

| VDD_33 | 3.3 V supply voltage |

| VDD_33_S5 | Always on 3.3 V supply voltage |

| VSS | Ground |

| VSS_SENSE_A | VSS Sense pin for VDDCR/VDDCR_SOC regulator |

| VSS_SENSE_B | VSS Sense pin for VDDP regulator |

| RSVD | Reserved |

- ↑ In this context TDM refers to an unstandardized extension of the I2S protocol to transmit more than two channels over a single data line.

Bibliography

- "Processor Programming Reference (PPR) for AMD Family 17h Model 60h, Revision A1 Processors", AMD Publ. #55922, Rev. 3.05, July 7, 2020

- "FP6 Processor Motherboard Design Guide", AMD Publ. #56178, Rev. 1.03, January 2020

- "Product Brief: AMD Ryzen™ Embedded V2000 Processor Family", AMD Publ. #20650345, Rev. A, 2020

- "Embedded Processor Specifications" AMD.com.

See also

| designer | AMD + |

| first launched | March 16, 2020 + |

| instance of | package + |

| market segment | Mobile + and Embedded + |

| microarchitecture | Zen 2 + and Zen 3 + |

| name | Package FP6 + |

| package | BGA-1140 + |

| package contacts | 1,140 + |

| package length | 25 mm (2.5 cm, 0.984 in) + |

| package pitch | 0.65 mm (0.0256 in) + |

| package type | Organic Micro Ball Grid Array + |

| package width | 35 mm (3.5 cm, 1.378 in) + |

| tdp | 55 W (55,000 mW, 0.0738 hp, 0.055 kW) + |