(→Key changes from {{\\|Zen}}) |

(→Zeppelin) |

||

| (76 intermediate revisions by 19 users not shown) | |||

| Line 1: | Line 1: | ||

{{amd title|Zen+|arch}} | {{amd title|Zen+|arch}} | ||

{{microarchitecture | {{microarchitecture | ||

| − | | atype | + | |atype=CPU |

| − | | name | + | |name=Zen+ |

| − | | designer | + | |designer=AMD |

| − | | manufacturer | + | |manufacturer=GlobalFoundries |

| − | | | + | |introduction=April 13, 2018 |

| − | | | + | |process=12 nm |

| − | | | + | |cores=1 |

| − | | | + | |cores 2=4 |

| + | |cores 3=6 | ||

| + | |cores 4=8 | ||

| + | |cores 5=12 | ||

| + | |cores 6=16 | ||

| + | |cores 7=24 | ||

| + | |cores 8=32 | ||

| + | |type=Superscalar | ||

| + | |oooe=Yes | ||

| + | |speculative=Yes | ||

| + | |renaming=Yes | ||

| + | |stages=19 | ||

| + | |decode=4-way | ||

| + | |isa=x86-64 | ||

| + | |extension=MOVBE | ||

| + | |extension 2=MMX | ||

| + | |extension 3=SSE | ||

| + | |extension 4=SSE2 | ||

| + | |extension 5=SSE3 | ||

| + | |extension 6=SSSE3 | ||

| + | |extension 7=SSE4.1 | ||

| + | |extension 8=SSE4.2 | ||

| + | |extension 9=POPCNT | ||

| + | |extension 10=AVX | ||

| + | |extension 11=AVX2 | ||

| + | |extension 12=AES | ||

| + | |extension 13=PCLMUL | ||

| + | |extension 14=RDRND | ||

| + | |extension 15=F16C | ||

| + | |extension 16=BMI | ||

| + | |extension 17=BMI2 | ||

| + | |extension 18=RDSEED | ||

| + | |extension 19=ADCX | ||

| + | |extension 20=PREFETCHW | ||

| + | |extension 21=CLFLUSHOPT | ||

| + | |extension 22=XSAVE | ||

| + | |extension 23=SHA | ||

| + | |extension 24=CLZERO | ||

| + | |l1i=64 KiB | ||

| + | |l1i per=core | ||

| + | |l1i desc=4-way set associative | ||

| + | |l1d=32 KiB | ||

| + | |l1d per=core | ||

| + | |l1d desc=8-way set associative | ||

| + | |l2=512 KiB | ||

| + | |l2 per=core | ||

| + | |l2 desc=8-way set associative | ||

| + | |l3=2 MiB | ||

| + | |l3 per=core | ||

| + | |l3 desc=16-way set associative | ||

| + | |core name=Colfax | ||

| + | |core name 2=Pinnacle Ridge | ||

| + | |core name 3=Picasso | ||

| + | |predecessor=Zen | ||

| + | |predecessor link=amd/microarchitectures/zen | ||

| + | |successor=Zen 2 | ||

| + | |successor link=amd/microarchitectures/zen 2 | ||

| + | |succession=Yes | ||

| + | }} | ||

| + | '''Zen+''' (Zen Plus) is the successor to {{\\|Zen}}, a [[12 nm]] [[microarchitecture]] designed by [[AMD]] and introduced in [[2018]] for the mainstream PC, enthusiast, and server markets. Zen+ was succeeded by {{\\|Zen 2}} in 2019. | ||

| − | + | Zen+ based processors are sold under the brand 2nd-Generation {{amd|Ryzen}} and 2nd-Generation {{amd|Threadripper}}. | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

== History == | == History == | ||

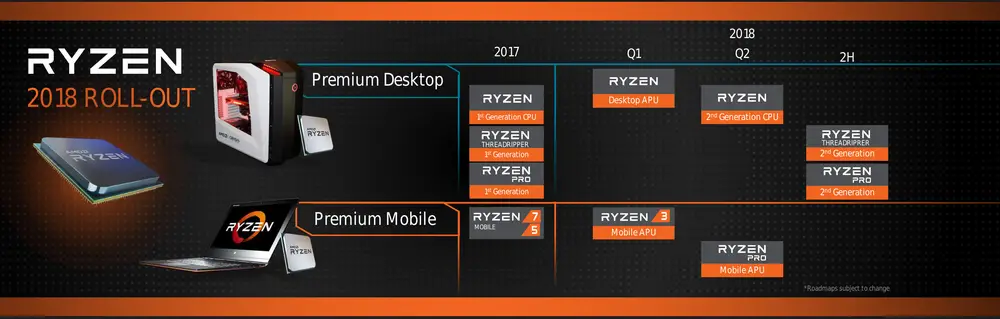

| − | Zen | + | [[File:amd zen+ roadmap.png|right|thumb|Zen+ Roadmap]] |

| + | Zen+ succeeded {{\\|Zen}} in April of 2018. Zen+ features the same core as Zen but takes advantage of the new [[GlobalFoundries]]' 12nm process to deliver higher clock speeds and improved power consumption. Zen+ was initially mentioned by AMD's senior fellow and lead architect of Zen, Michael Clark, during Hot Chips 28 in [[2016]] as part of AMD's continuing commitment in the high-performance computing market. | ||

== Codenames == | == Codenames == | ||

| − | |||

| − | |||

{| class="wikitable" | {| class="wikitable" | ||

|- | |- | ||

! Core !! C/T !! Target | ! Core !! C/T !! Target | ||

| + | |- | ||

| + | | {{amd|Colfax|l=core}} || Up to 32/64 || Enthusiasts market processors | ||

|- | |- | ||

| {{amd|Pinnacle Ridge|l=core}} || Up to 8/16 || Mainstream to high-end desktops & enthusiasts market processors | | {{amd|Pinnacle Ridge|l=core}} || Up to 8/16 || Mainstream to high-end desktops & enthusiasts market processors | ||

|- | |- | ||

| − | | {{amd|Picasso|l=core}} || 4/8 || Mainstream desktop & mobile processors with GPU | + | | {{amd|Picasso|l=core}} || From 2/4 to 4/8 || Mainstream desktop & mobile processors with GPU |

| + | |} | ||

| + | |||

| + | == Process Technology == | ||

| + | {{see also|12 nm process}} | ||

| + | Zen+ is manufactured on [[Global Foundries]]' [[12 nm process]] Leading-Performance (12LP), an enhanced version of their 14nm process. The enhanced process provides up to 15% higher density or up to 10% higher performance. 12LP brings around a 10% frequency bump for the {{amd|Ryzen}} lineup at the same power envelopes. | ||

| + | |||

| + | Note that AMD did not switch to standard libraries and instead chose to get whatever added performance they could get from the same physical design as [[14 nm]]. This also means some performance was left on the table and the die size is exactly the same as Zen. | ||

| + | |||

| + | == Compatibility == | ||

| + | [[Linux]] added initial support for Zen starting with Linux Kernel 4.10. [[Microsoft]] officially only supports Zen on Windows 10. | ||

| + | Windows 7 and 8 drivers are available for many mainboards. But drivers must be integrated into the installation image or installed first before switching to a Zen-based system. Otherwise support for any kind of USB device like keyboard and mouse would be missing. | ||

| + | |||

| + | {| class="wikitable" | ||

| + | ! Vendor !! OS !! Version !! Notes | ||

| + | |- | ||

| + | | rowspan="3" | [[Microsoft]] || rowspan="3" | Windows || style="background-color: #ffdad6;" | Windows 7 || No Support | ||

| + | |- | ||

| + | | style="background-color: #ffdad6;" | Windows 8 || No Support | ||

| + | |- | ||

| + | | style="background-color: #d6ffd8;" | Windows 10 || Support | ||

| + | |- | ||

| + | | Linux || Linux || style="background-color: #d6ffd8;" | Kernel 4.10 || Initial Support | ||

| + | |} | ||

| + | |||

| + | == Compiler support == | ||

| + | Zen+ is largely the same architecture as {{\\|Zen}} and thus uses the same compiler switches. | ||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | ! Compiler !! Arch-Specific || Arch-Favorable | ||

| + | |- | ||

| + | | [[AOCC]] || <code>‐march=znver1</code> || <code>-mtune=znver1</code> | ||

| + | |- | ||

| + | | [[GCC]] || <code>-march=znver1</code> || <code>-mtune=znver1</code> | ||

| + | |- | ||

| + | | [[LLVM]] || <code>-march=znver1</code> || <code>-mtune=znver1</code> | ||

| + | |- | ||

| + | | [[Visual Studio]] || <code>/arch:AVX2</code> || ? | ||

| + | |} | ||

| + | |||

| + | === CPUID === | ||

| + | {| class="wikitable tc1 tc2 tc3 tc4" | ||

| + | ! Core !! Extended<br>Family !! Family !! Extended<br>Model !! Model | ||

| + | |- | ||

| + | | rowspan="2" | {{amd|Pinnacle Ridge|l=core}} || 0x8 || 0xF || 0x0 || 0x8 | ||

| + | |- | ||

| + | | colspan="4" | Family 23 Model 8 | ||

| + | |- | ||

| + | | rowspan="2" | {{amd|Picasso|l=core}} || 0x8 || 0xF || 0x0 || 0x18 | ||

| + | |- | ||

| + | | colspan="4" | Family 23 Model 24 | ||

|} | |} | ||

| + | |||

| + | == Release Dates == | ||

| + | AMD launched 2nd generation {{amd|Ryzen}} on the 19th April of 2018. 2nd Generation {{amd|Ryzen Threadripper}} was introduced in August 2018 and Ryzen PRO processors has launched in the second half of 2018. | ||

| + | |||

| + | |||

| + | [[File:amd ryzen 2018 roll-out.png|1000px]] | ||

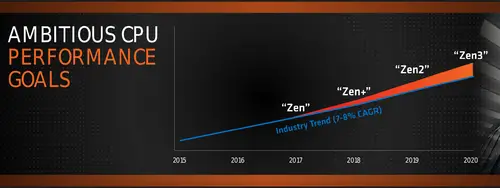

== Architecture == | == Architecture == | ||

| − | + | [[File:amd zen+ perf improvement.png|right|500px]] | |

| + | Serving as a light refresh over {{\\|Zen}}, those processors have around ten percent higher base frequency for the same power envelope. | ||

=== Key changes from {{\\|Zen}} === | === Key changes from {{\\|Zen}} === | ||

| + | * ~10% higher [[clock]] frequency | ||

| + | * ~3% single-thread IPC improvement | ||

* [[12 nm process]] (from [[14 nm]]) | * [[12 nm process]] (from [[14 nm]]) | ||

* {{amd|Precision Boost 2}} (from Precision Boost) | * {{amd|Precision Boost 2}} (from Precision Boost) | ||

| + | ** {{amd|Precision Boost Overdrive}} | ||

| + | * {{amd|XFR 2}} (from XFR 1) | ||

| + | * Cache | ||

| + | ** Improved cache prefetch | ||

| + | ** 12 cycle L2 latency for mainstream desktop (from 17 cycles) | ||

| + | * Memory | ||

| + | ** Higher DDR4 transfer rate (2933 MT/s from 2666 MT/s) | ||

| + | * Mainstream chipsets (See [[#Sockets/Platform|§ Sockets/Platform]]) | ||

| + | ** X370 → X470 | ||

| + | *** New StoreMI Technology | ||

| + | *** Lower Power | ||

| + | *** Bug fixes | ||

| + | *** OEM related issues resolved (unspecified) | ||

| + | * Family | ||

| + | ** {{amd|Threadripper}}: 2x cores (up to [[32 cores|32]], from [[16 cores|16]]) | ||

| + | |||

| + | === Block Diagram === | ||

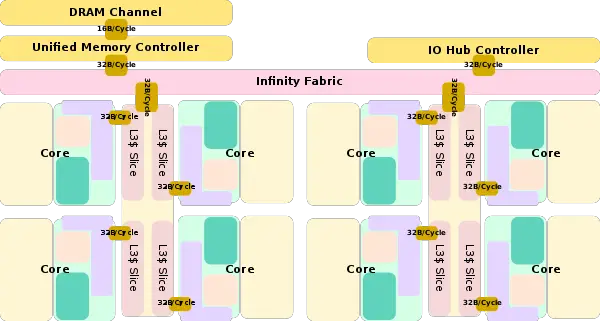

| + | ===== Entire SoC Overview ===== | ||

| + | [[File:zen soc block.svg|600px]] | ||

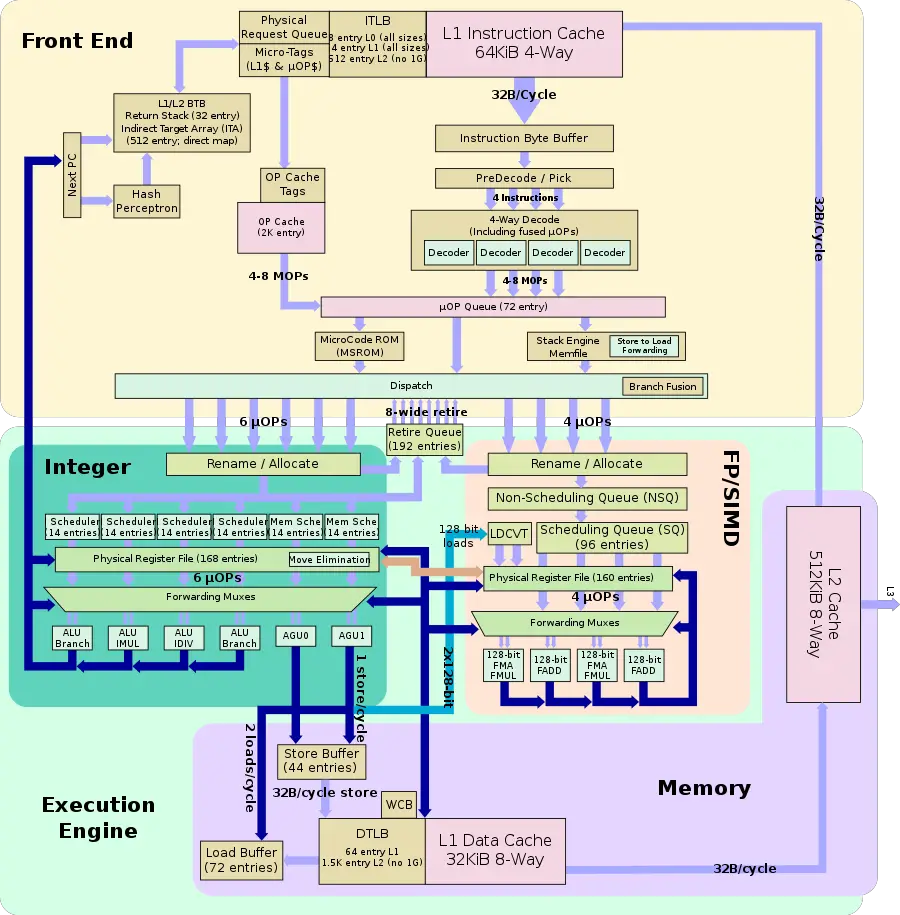

| + | ===== Individual Core ===== | ||

| + | [[File:zen block diagram.svg|900px]] | ||

| + | |||

| + | === Memory Hierarchy === | ||

| + | * Cache | ||

| + | ** L0 µOP cache: | ||

| + | *** 2,048 µOPs, 8-way set associative | ||

| + | **** 32-sets, 8-µOP line size | ||

| + | *** Parity protected | ||

| + | ** L1I Cache: | ||

| + | *** 64 KiB 4-way set associative | ||

| + | **** 256-sets, 64 B line size | ||

| + | **** Shared by the two threads, per core | ||

| + | *** Parity protected | ||

| + | ** L1D Cache: | ||

| + | *** 32 KiB 8-way set associative | ||

| + | **** 64-sets, 64 B line size | ||

| + | **** Write-back policy | ||

| + | *** 4-5 cycles latency for Int | ||

| + | *** 7-8 cycles latency for FP | ||

| + | *** SEC-DED ECC | ||

| + | ** L2 Cache: | ||

| + | *** 512 KiB 8-way set associative | ||

| + | *** 1,024-sets, 64 B line size | ||

| + | *** Write-back policy | ||

| + | *** Inclusive of L1 | ||

| + | *** 12 cycles latency | ||

| + | *** DEC-TED ECC | ||

| + | ** L3 Cache: | ||

| + | *** Victim cache | ||

| + | *** Summit Ridge, Naples: 8 MiB/CCX, shared across all cores. | ||

| + | *** Raven Ridge: 4 MiB/CCX, shared across all cores. | ||

| + | *** 16-way set associative | ||

| + | **** 8,192-sets, 64 B line size | ||

| + | *** 40 cycles latency | ||

| + | *** DEC-TED ECC | ||

| + | ** System DRAM: | ||

| + | *** 2 channels per die | ||

| + | *** Summit Ridge: up to PC4-21300U (DDR4-2666 UDIMM) | ||

| + | *** Raven Ridge: up to PC4-23466U (DDR4-2933 UDIMM) | ||

| + | *** Naples: up to PC4-21300L (DDR4-2666 RDIMM/LRDIMM) | ||

| + | *** ECC support: x4 DRAM device failure correction (Chipkill), x8 SEC-DED ECC, Patrol and Demand scrubbing, Data poisoning | ||

| + | |||

| + | Zen TLB consists of dedicated level one TLB for instruction cache and another one for data cache. | ||

| + | |||

| + | * TLBs | ||

| + | ** ITLB | ||

| + | *** 8 entry L0 TLB, all page sizes | ||

| + | *** 64 entry L1 TLB, all page sizes | ||

| + | *** 512 entry L2 TLB, no 1G pages | ||

| + | *** Parity protected | ||

| + | ** DTLB | ||

| + | *** 64 entry L1 TLB, all page sizes | ||

| + | *** 1,532-entry L2 TLB, no 1G pages | ||

| + | *** Parity protected | ||

| + | |||

| + | == Core == | ||

| + | === Pipeline === | ||

| + | Zen+ pipeline is identical to {{\\|Zen#Pipeline|Zen's}}. | ||

| + | |||

| + | === Memory Subsystem === | ||

| + | When AMD presented their paper at ISSCC 2018, WikiChip was able to confirm with AMD's SoC architect that {{\\|Zen|Zen's}} L2 latency was always designed to be 12 cycles. In fact all Zen-based microprocessors (including {{amd|EPYC}}, {{amd|Ryzen Threadripper}}, and Zen-based APUs) have an L2 latency of 12 cycles for all [[access patterns]]. Only mainstream Zen-based {{amd|Ryzen}} processors (i.e., {{amd|Summit Ridge|l=core}}) have a latency of 17 cycles. The problem has been sorted out with Zen+. | ||

| + | |||

| + | == Die == | ||

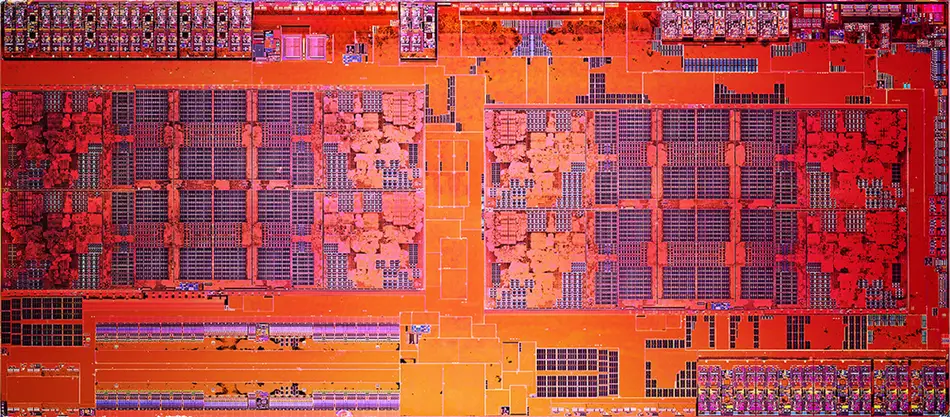

| + | === Zeppelin === | ||

| + | * [[12 nm process]] | ||

| + | * 12 metal layers | ||

| + | * 4,800,000,000 transistors | ||

| + | * ~22.058 mm x ~9.655 mm (Estimated) | ||

| + | * 212.97 mm² die size | ||

| + | |||

| + | :[[File:amd zen+ zeppelin die shot.png|950px]] | ||

| + | |||

| + | == Sockets/Platform == | ||

| + | All Zen+-based mainstream consumer microprocessors utilizes AMD's {{amd|Socket AM4}}, a unified socket infrastructure. All those processors are a complete [[system on a chip]] integrating the [[northbridge]] ([[memory controller]]) and the [[southbridge]] including 16 [[PCIe]] lanes for the [[GPU]], 4 PCIe lanes for the [[NVMe]]/SATA controllers as well as USB 3.0. The chipset, however, extends the processor with a number of additional connections beyond that offered by the SoC. | ||

| + | |||

| + | {{amd socket am4 chipsets}} | ||

| + | |||

| + | === StoreMI === | ||

| + | [[File:amd 400 series storemi logo.png|left|200px]] | ||

| + | A new feature AMD has added to the 400-series chipset is "{{amd|StoreMI}}", a technology with very similar capabilities to Intel's {{intel|Smart Response Technology}} which attempts to combine the benefits of fast, but expensive, [[solid-state drive|SSDs]] along with cheap high-capacity, but slow, [[hard disk drive|HDDs]]. StoreMI combines the two storage devices into a single virtual drive (single letter drive on {{microsoft|Windows}}) and automatically manages and moves the data across the drives. Essentially, the chipset uses the SSD as a cache for traditional hard drives. The idea is to keep the most recent and most accessed data on the SSD in order to improve real-world responsiveness while keeping the less used data in the slower mechanical hard disk in order to preserve the capacity of the SSD. It’s worth noting that this hierarchy of secondary storage devices can actually extend to main memory. Up to 2 GiB of RAM may be configured and reserved as another level of cache for the HDD on top of the SSD. | ||

| + | |||

| + | == All Zen+ Chips == | ||

| + | <!-- NOTE: | ||

| + | This table is generated automatically from the data in the actual articles. | ||

| + | If a microprocessor is missing from the list, an appropriate article for it needs to be | ||

| + | created and tagged accordingly. | ||

| + | |||

| + | Missing a chip? please dump its name here: http://en.wikichip.org/wiki/WikiChip:wanted_chips | ||

| + | --> | ||

| + | {{comp table start}} | ||

| + | <table class="comptable sortable tc6 tc7"> | ||

| + | {{comp table header|main|11:List of all Zen+ based Processors}} | ||

| + | {{comp table header|cols|Price|Launched|Family|Core|%Cores|%Threads|L2$|L3$|%Frequency|%Boost|%TDP}} | ||

| + | {{#ask: [[Category:microprocessor models by amd]] [[microarchitecture::Zen+]] | ||

| + | |?full page name | ||

| + | |?model number | ||

| + | |?release price | ||

| + | |?first launched | ||

| + | |?microprocessor family | ||

| + | |?core name | ||

| + | |?core count | ||

| + | |?thread count | ||

| + | |?l2$ size | ||

| + | |?l3$ size | ||

| + | |?base frequency#GHz | ||

| + | |?turbo frequency#GHz | ||

| + | |?tdp | ||

| + | |format=template | ||

| + | |template=proc table 3 | ||

| + | |userparam=13 | ||

| + | |mainlabel=- | ||

| + | }} | ||

| + | {{comp table count|ask=[[Category:microprocessor models by amd]] [[microarchitecture::Zen+]]}} | ||

| + | </table> | ||

| + | {{comp table end}} | ||

| + | |||

| + | == Bibliography == | ||

| + | * AMD CES Tech Day 2018, Jim Anderson | ||

| + | * AMD CES Tech Day 2018, Lisa Su | ||

| + | * AMD CES Tech Day 2018, Mark Papermaster | ||

| + | * David. S. (August 2018). "[https://fuse.wikichip.org/news/1569/amd-announces-threadripper-2-chiplets-aid-core-scaling/ AMD Announces Threadripper 2, Chiplets Aid Core Scaling]" | ||

| + | |||

| + | == Documents == | ||

| + | * [[:File:AMD CES Tech Day 2018 Jim Anderson.pdf|AMD Tech Day 2018, Jim Anderson]] | ||

| + | * [[:File:AMD CES Tech Day 2018 Lisa Su.pdf|AMD Tech Day 2018, Lisa Su]] | ||

| + | * [[:File:AMD CES Tech Day 2018 Mark Papermaster.pdf|AMD Tech Day 2018, Mark Papermaster]] | ||

== See Also == | == See Also == | ||

| − | + | * Intel {{intel|Coffee Lake|l=arch}} | |

| − | * Intel {{intel| | ||

Latest revision as of 07:39, 3 March 2024

| Edit Values | |

| Zen+ µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | AMD |

| Manufacturer | GlobalFoundries |

| Introduction | April 13, 2018 |

| Process | 12 nm |

| Core Configs | 1, 4, 6, 8, 12, 16, 24, 32 |

| Pipeline | |

| Type | Superscalar |

| OoOE | Yes |

| Speculative | Yes |

| Reg Renaming | Yes |

| Stages | 19 |

| Decode | 4-way |

| Instructions | |

| ISA | x86-64 |

| Extensions | MOVBE, MMX, SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4.2, POPCNT, AVX, AVX2, AES, PCLMUL, RDRND, F16C, BMI, BMI2, RDSEED, ADCX, PREFETCHW, CLFLUSHOPT, XSAVE, SHA, CLZERO |

| Cache | |

| L1I Cache | 64 KiB/core 4-way set associative |

| L1D Cache | 32 KiB/core 8-way set associative |

| L2 Cache | 512 KiB/core 8-way set associative |

| L3 Cache | 2 MiB/core 16-way set associative |

| Cores | |

| Core Names | Colfax, Pinnacle Ridge, Picasso |

| Succession | |

Zen+ (Zen Plus) is the successor to Zen, a 12 nm microarchitecture designed by AMD and introduced in 2018 for the mainstream PC, enthusiast, and server markets. Zen+ was succeeded by Zen 2 in 2019.

Zen+ based processors are sold under the brand 2nd-Generation Ryzen and 2nd-Generation Threadripper.

Contents

History[edit]

Zen+ succeeded Zen in April of 2018. Zen+ features the same core as Zen but takes advantage of the new GlobalFoundries' 12nm process to deliver higher clock speeds and improved power consumption. Zen+ was initially mentioned by AMD's senior fellow and lead architect of Zen, Michael Clark, during Hot Chips 28 in 2016 as part of AMD's continuing commitment in the high-performance computing market.

Codenames[edit]

| Core | C/T | Target |

|---|---|---|

| Colfax | Up to 32/64 | Enthusiasts market processors |

| Pinnacle Ridge | Up to 8/16 | Mainstream to high-end desktops & enthusiasts market processors |

| Picasso | From 2/4 to 4/8 | Mainstream desktop & mobile processors with GPU |

Process Technology[edit]

- See also: 12 nm process

Zen+ is manufactured on Global Foundries' 12 nm process Leading-Performance (12LP), an enhanced version of their 14nm process. The enhanced process provides up to 15% higher density or up to 10% higher performance. 12LP brings around a 10% frequency bump for the Ryzen lineup at the same power envelopes.

Note that AMD did not switch to standard libraries and instead chose to get whatever added performance they could get from the same physical design as 14 nm. This also means some performance was left on the table and the die size is exactly the same as Zen.

Compatibility[edit]

Linux added initial support for Zen starting with Linux Kernel 4.10. Microsoft officially only supports Zen on Windows 10. Windows 7 and 8 drivers are available for many mainboards. But drivers must be integrated into the installation image or installed first before switching to a Zen-based system. Otherwise support for any kind of USB device like keyboard and mouse would be missing.

| Vendor | OS | Version | Notes |

|---|---|---|---|

| Microsoft | Windows | Windows 7 | No Support |

| Windows 8 | No Support | ||

| Windows 10 | Support | ||

| Linux | Linux | Kernel 4.10 | Initial Support |

Compiler support[edit]

Zen+ is largely the same architecture as Zen and thus uses the same compiler switches.

| Compiler | Arch-Specific | Arch-Favorable |

|---|---|---|

| AOCC | ‐march=znver1 |

-mtune=znver1

|

| GCC | -march=znver1 |

-mtune=znver1

|

| LLVM | -march=znver1 |

-mtune=znver1

|

| Visual Studio | /arch:AVX2 |

? |

CPUID[edit]

| Core | Extended Family |

Family | Extended Model |

Model |

|---|---|---|---|---|

| Pinnacle Ridge | 0x8 | 0xF | 0x0 | 0x8 |

| Family 23 Model 8 | ||||

| Picasso | 0x8 | 0xF | 0x0 | 0x18 |

| Family 23 Model 24 | ||||

Release Dates[edit]

AMD launched 2nd generation Ryzen on the 19th April of 2018. 2nd Generation Ryzen Threadripper was introduced in August 2018 and Ryzen PRO processors has launched in the second half of 2018.

Architecture[edit]

Serving as a light refresh over Zen, those processors have around ten percent higher base frequency for the same power envelope.

Key changes from Zen[edit]

- ~10% higher clock frequency

- ~3% single-thread IPC improvement

- 12 nm process (from 14 nm)

- Precision Boost 2 (from Precision Boost)

- XFR 2 (from XFR 1)

- Cache

- Improved cache prefetch

- 12 cycle L2 latency for mainstream desktop (from 17 cycles)

- Memory

- Higher DDR4 transfer rate (2933 MT/s from 2666 MT/s)

- Mainstream chipsets (See § Sockets/Platform)

- X370 → X470

- New StoreMI Technology

- Lower Power

- Bug fixes

- OEM related issues resolved (unspecified)

- X370 → X470

- Family

- Threadripper: 2x cores (up to 32, from 16)

Block Diagram[edit]

Entire SoC Overview[edit]

Individual Core[edit]

Memory Hierarchy[edit]

- Cache

- L0 µOP cache:

- 2,048 µOPs, 8-way set associative

- 32-sets, 8-µOP line size

- Parity protected

- 2,048 µOPs, 8-way set associative

- L1I Cache:

- 64 KiB 4-way set associative

- 256-sets, 64 B line size

- Shared by the two threads, per core

- Parity protected

- 64 KiB 4-way set associative

- L1D Cache:

- 32 KiB 8-way set associative

- 64-sets, 64 B line size

- Write-back policy

- 4-5 cycles latency for Int

- 7-8 cycles latency for FP

- SEC-DED ECC

- 32 KiB 8-way set associative

- L2 Cache:

- 512 KiB 8-way set associative

- 1,024-sets, 64 B line size

- Write-back policy

- Inclusive of L1

- 12 cycles latency

- DEC-TED ECC

- L3 Cache:

- Victim cache

- Summit Ridge, Naples: 8 MiB/CCX, shared across all cores.

- Raven Ridge: 4 MiB/CCX, shared across all cores.

- 16-way set associative

- 8,192-sets, 64 B line size

- 40 cycles latency

- DEC-TED ECC

- System DRAM:

- 2 channels per die

- Summit Ridge: up to PC4-21300U (DDR4-2666 UDIMM)

- Raven Ridge: up to PC4-23466U (DDR4-2933 UDIMM)

- Naples: up to PC4-21300L (DDR4-2666 RDIMM/LRDIMM)

- ECC support: x4 DRAM device failure correction (Chipkill), x8 SEC-DED ECC, Patrol and Demand scrubbing, Data poisoning

- L0 µOP cache:

Zen TLB consists of dedicated level one TLB for instruction cache and another one for data cache.

- TLBs

- ITLB

- 8 entry L0 TLB, all page sizes

- 64 entry L1 TLB, all page sizes

- 512 entry L2 TLB, no 1G pages

- Parity protected

- DTLB

- 64 entry L1 TLB, all page sizes

- 1,532-entry L2 TLB, no 1G pages

- Parity protected

- ITLB

Core[edit]

Pipeline[edit]

Zen+ pipeline is identical to Zen's.

Memory Subsystem[edit]

When AMD presented their paper at ISSCC 2018, WikiChip was able to confirm with AMD's SoC architect that Zen's L2 latency was always designed to be 12 cycles. In fact all Zen-based microprocessors (including EPYC, Ryzen Threadripper, and Zen-based APUs) have an L2 latency of 12 cycles for all access patterns. Only mainstream Zen-based Ryzen processors (i.e., Summit Ridge) have a latency of 17 cycles. The problem has been sorted out with Zen+.

Die[edit]

Zeppelin[edit]

- 12 nm process

- 12 metal layers

- 4,800,000,000 transistors

- ~22.058 mm x ~9.655 mm (Estimated)

- 212.97 mm² die size

Sockets/Platform[edit]

All Zen+-based mainstream consumer microprocessors utilizes AMD's Socket AM4, a unified socket infrastructure. All those processors are a complete system on a chip integrating the northbridge (memory controller) and the southbridge including 16 PCIe lanes for the GPU, 4 PCIe lanes for the NVMe/SATA controllers as well as USB 3.0. The chipset, however, extends the processor with a number of additional connections beyond that offered by the SoC.

| Socket AM4 Platform [Edit] | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| Segment | Chipset | USB | SATA | SATAe | PCIe | RAID | Dual PCIe | Overclocking | ||

| 3.1 G1 | 3.1 G2 | 2.0 | ||||||||

| 500-series (Zen+, Zen 2, Zen 3) | ||||||||||

| Mainstream | B550 | 2 | 6 | 6 | 8 + 4x NVME | 0 | 16x Gen4 | 0,1,10 | ✔ | ✔ |

| Enthusiast | X570 | 0 | 8 | 4 | 14 + 4x NVME | 0 | 16x Gen4 | 0,1,10 | ||

| 400-series (Zen+) | ||||||||||

| Mainstream | B450 | 2 | 2 | 6 | 6 + 4x NVME | 1 | 6x Gen3 | 0,1,10 | ✘ | ✔ |

| Enthusiast | X470 | 6 | 2 | 6 | 10 + 4x NVME | 2 | 8x Gen3 | 0,1,10 | ✔ | |

| 300-series (Zen) | ||||||||||

| Small Form Factor | A300, B300 | 4 | 0 | 0 | 2 + 2x NVMe | 1 | 4x Gen3 | 0,1 | ✘ | |

| X300 | 4 | 0 | 0 | 2 + 2x NVMe | 1 | 4x Gen3 | 0,1 | ✔ | ||

| Entry-level | A320 | 6 | 1 | 6 | 4 + 2x NVMe | 2 | 4x Gen2 | 0,1,10 | ✘ | ✘ |

| Mainstream | B350 | 6 | 2 | 6 | 4 + 2x NVMe | 2 | 6x Gen2 | 0,1,10 | ✔ | |

| Enthusiast | X370 | 6 | 2 | 6 | 6 + 2x NVMe | 2 | 8x Gen2 | 0,1,10 | ✔ | |

StoreMI[edit]

A new feature AMD has added to the 400-series chipset is "StoreMI", a technology with very similar capabilities to Intel's Smart Response Technology which attempts to combine the benefits of fast, but expensive, SSDs along with cheap high-capacity, but slow, HDDs. StoreMI combines the two storage devices into a single virtual drive (single letter drive on Windows) and automatically manages and moves the data across the drives. Essentially, the chipset uses the SSD as a cache for traditional hard drives. The idea is to keep the most recent and most accessed data on the SSD in order to improve real-world responsiveness while keeping the less used data in the slower mechanical hard disk in order to preserve the capacity of the SSD. It’s worth noting that this hierarchy of secondary storage devices can actually extend to main memory. Up to 2 GiB of RAM may be configured and reserved as another level of cache for the HDD on top of the SSD.

All Zen+ Chips[edit]

| List of all Zen+ based Processors | |||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Model | Price | Launched | Family | Core | Cores | Threads | L2$ | L3$ | Frequency | Boost | TDP |

| PRO 300GE | 30 September 2019 | Athlon | Picasso | 2 | 4 | 1 MiB 1,024 KiB 1,048,576 B 9.765625e-4 GiB | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 3.4 GHz 3,400 MHz 3,400,000 kHz | 35 W 35,000 mW 0.0469 hp 0.035 kW | ||

| PRO 300U | 8 April 2019 | Athlon | Picasso | 2 | 4 | 1 MiB 1,024 KiB 1,048,576 B 9.765625e-4 GiB | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 2.4 GHz 2,400 MHz 2,400,000 kHz | 3.3 GHz 3,300 MHz 3,300,000 kHz | 15 W 15,000 mW 0.0201 hp 0.015 kW | |

| 2300X | 10 September 2018 | Ryzen 3 | Pinnacle Ridge | 4 | 4 | 2 MiB 2,048 KiB 2,097,152 B 0.00195 GiB | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 3.5 GHz 3,500 MHz 3,500,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | |

| 3200G | $ 99.00 € 89.10 £ 80.19 ¥ 10,229.67 | 7 July 2019 | Ryzen 3 | Picasso | 4 | 4 | 2 MiB 2,048 KiB 2,097,152 B 0.00195 GiB | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 3.6 GHz 3,600 MHz 3,600,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW |

| 3200U | 6 January 2019 | Ryzen 3 | Picasso | 2 | 4 | 1 MiB 1,024 KiB 1,048,576 B 9.765625e-4 GiB | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 2.6 GHz 2,600 MHz 2,600,000 kHz | 3.5 GHz 3,500 MHz 3,500,000 kHz | 15 W 15,000 mW 0.0201 hp 0.015 kW | |

| 3300U | 6 January 2019 | Ryzen 3 | Picasso | 4 | 4 | 2 MiB 2,048 KiB 2,097,152 B 0.00195 GiB | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 2.1 GHz 2,100 MHz 2,100,000 kHz | 3.5 GHz 3,500 MHz 3,500,000 kHz | 15 W 15,000 mW 0.0201 hp 0.015 kW | |

| PRO 3200G | 30 September 2019 | Ryzen 3 | Picasso | 4 | 4 | 2 MiB 2,048 KiB 2,097,152 B 0.00195 GiB | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 3.6 GHz 3,600 MHz 3,600,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | |

| PRO 3200GE | 30 September 2019 | Ryzen 3 | Picasso | 4 | 4 | 2 MiB 2,048 KiB 2,097,152 B 0.00195 GiB | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 3.3 GHz 3,300 MHz 3,300,000 kHz | 3.8 GHz 3,800 MHz 3,800,000 kHz | 35 W 35,000 mW 0.0469 hp 0.035 kW | |

| PRO 3300U | 8 April 2019 | Ryzen 3 | Picasso | 4 | 4 | 2 MiB 2,048 KiB 2,097,152 B 0.00195 GiB | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 2.1 GHz 2,100 MHz 2,100,000 kHz | 3.5 GHz 3,500 MHz 3,500,000 kHz | 15 W 15,000 mW 0.0201 hp 0.015 kW | |

| 2500X | 10 September 2018 | Ryzen 5 | Pinnacle Ridge | 4 | 8 | 2 MiB 2,048 KiB 2,097,152 B 0.00195 GiB | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 3.6 GHz 3,600 MHz 3,600,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | |

| 2600 | $ 170.00 € 153.00 £ 137.70 ¥ 17,566.10 | 19 April 2018 | Ryzen 5 | Pinnacle Ridge | 6 | 12 | 3 MiB 3,072 KiB 3,145,728 B 0.00293 GiB | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 3.4 GHz 3,400 MHz 3,400,000 kHz | 3.9 GHz 3,900 MHz 3,900,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW |

| 2600E | 10 September 2018 | Ryzen 5 | Pinnacle Ridge | 6 | 12 | 3 MiB 3,072 KiB 3,145,728 B 0.00293 GiB | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 3.1 GHz 3,100 MHz 3,100,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 45 W 45,000 mW 0.0603 hp 0.045 kW | |

| 2600X | $ 229.00 € 206.10 £ 185.49 ¥ 23,662.57 | 19 April 2018 | Ryzen 5 | Pinnacle Ridge | 6 | 12 | 3 MiB 3,072 KiB 3,145,728 B 0.00293 GiB | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 3.6 GHz 3,600 MHz 3,600,000 kHz | 4.2 GHz 4,200 MHz 4,200,000 kHz | 95 W 95,000 mW 0.127 hp 0.095 kW |

| 3400G | 7 July 2019 | Ryzen 5 | Picasso | 4 | 8 | 2 MiB 2,048 KiB 2,097,152 B 0.00195 GiB | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 3.7 GHz 3,700 MHz 3,700,000 kHz | 4.2 GHz 4,200 MHz 4,200,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | |

| 3500U | 6 January 2019 | Ryzen 5 | Picasso | 4 | 8 | 2 MiB 2,048 KiB 2,097,152 B 0.00195 GiB | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 2.1 GHz 2,100 MHz 2,100,000 kHz | 3.7 GHz 3,700 MHz 3,700,000 kHz | 15 W 15,000 mW 0.0201 hp 0.015 kW | |

| 3550H | 6 January 2019 | Ryzen 5 | Picasso | 4 | 8 | 2 MiB 2,048 KiB 2,097,152 B 0.00195 GiB | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 2.1 GHz 2,100 MHz 2,100,000 kHz | 3.7 GHz 3,700 MHz 3,700,000 kHz | 35 W 35,000 mW 0.0469 hp 0.035 kW | |

| 3580U | October 2019 | Ryzen 5 | Picasso | 4 | 8 | 2 MiB 2,048 KiB 2,097,152 B 0.00195 GiB | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 2.1 GHz 2,100 MHz 2,100,000 kHz | 3.7 GHz 3,700 MHz 3,700,000 kHz | 15 W 15,000 mW 0.0201 hp 0.015 kW | |

| PRO 2600 | 6 September 2018 | Ryzen 5 | Pinnacle Ridge | 6 | 12 | 3 MiB 3,072 KiB 3,145,728 B 0.00293 GiB | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 3.4 GHz 3,400 MHz 3,400,000 kHz | 3.9 GHz 3,900 MHz 3,900,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | |

| PRO 3400G | 30 September 2019 | Ryzen 5 | Picasso | 4 | 8 | 2 MiB 2,048 KiB 2,097,152 B 0.00195 GiB | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 3.7 GHz 3,700 MHz 3,700,000 kHz | 4.2 GHz 4,200 MHz 4,200,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | |

| PRO 3400GE | 30 September 2019 | Ryzen 5 | Picasso | 4 | 8 | 2 MiB 2,048 KiB 2,097,152 B 0.00195 GiB | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 3.3 GHz 3,300 MHz 3,300,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 35 W 35,000 mW 0.0469 hp 0.035 kW | |

| PRO 3500U | 8 April 2019 | Ryzen 5 | Picasso | 4 | 8 | 2 MiB 2,048 KiB 2,097,152 B 0.00195 GiB | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 2.1 GHz 2,100 MHz 2,100,000 kHz | 3.7 GHz 3,700 MHz 3,700,000 kHz | 15 W 15,000 mW 0.0201 hp 0.015 kW | |

| 2700 | $ 299.00 € 269.10 £ 242.19 ¥ 30,895.67 | 19 April 2018 | Ryzen 7 | Pinnacle Ridge | 8 | 16 | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 3.2 GHz 3,200 MHz 3,200,000 kHz | 4.1 GHz 4,100 MHz 4,100,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW |

| 2700E | 10 September 2018 | Ryzen 7 | Pinnacle Ridge | 8 | 16 | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 2.8 GHz 2,800 MHz 2,800,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 45 W 45,000 mW 0.0603 hp 0.045 kW | |

| 2700X Gold Edition | $ 329.00 € 296.10 £ 266.49 ¥ 33,995.57 | 29 April 2019 | Ryzen 7 | Pinnacle Ridge | 8 | 16 | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 3.7 GHz 3,700 MHz 3,700,000 kHz | 4.3 GHz 4,300 MHz 4,300,000 kHz | 105 W 105,000 mW 0.141 hp 0.105 kW |

| 2700X | $ 329.00 € 296.10 £ 266.49 ¥ 33,995.57 | 19 April 2018 | Ryzen 7 | Pinnacle Ridge | 8 | 16 | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 3.7 GHz 3,700 MHz 3,700,000 kHz | 4.3 GHz 4,300 MHz 4,300,000 kHz | 105 W 105,000 mW 0.141 hp 0.105 kW |

| 3700U | 6 January 2019 | Ryzen 7 | Picasso | 4 | 8 | 2 MiB 2,048 KiB 2,097,152 B 0.00195 GiB | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 2.3 GHz 2,300 MHz 2,300,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 15 W 15,000 mW 0.0201 hp 0.015 kW | |

| 3750H | 6 January 2019 | Ryzen 7 | Picasso | 4 | 8 | 2 MiB 2,048 KiB 2,097,152 B 0.00195 GiB | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 2.3 GHz 2,300 MHz 2,300,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 35 W 35,000 mW 0.0469 hp 0.035 kW | |

| 3780U | October 2019 | Ryzen 7 | Picasso | 4 | 8 | 2 MiB 2,048 KiB 2,097,152 B 0.00195 GiB | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 2.3 GHz 2,300 MHz 2,300,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 15 W 15,000 mW 0.0201 hp 0.015 kW | |

| PRO 2700 | 6 September 2018 | Ryzen 7 | Pinnacle Ridge | 8 | 16 | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 3.2 GHz 3,200 MHz 3,200,000 kHz | 4.1 GHz 4,100 MHz 4,100,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | |

| PRO 2700X | 6 September 2018 | Ryzen 7 | Pinnacle Ridge | 8 | 16 | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 3.6 GHz 3,600 MHz 3,600,000 kHz | 4.1 GHz 4,100 MHz 4,100,000 kHz | 105 W 105,000 mW 0.141 hp 0.105 kW | |

| PRO 3700U | 8 April 2019 | Ryzen 7 | Picasso | 4 | 8 | 2 MiB 2,048 KiB 2,097,152 B 0.00195 GiB | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 2.3 GHz 2,300 MHz 2,300,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 15 W 15,000 mW 0.0201 hp 0.015 kW | |

| 2920X | $ 649.00 € 584.10 £ 525.69 ¥ 67,061.17 | 29 October 2018 | Ryzen Threadripper | Colfax | 12 | 24 | 6 MiB 6,144 KiB 6,291,456 B 0.00586 GiB | 32 MiB 32,768 KiB 33,554,432 B 0.0313 GiB | 3.5 GHz 3,500 MHz 3,500,000 kHz | 4.3 GHz 4,300 MHz 4,300,000 kHz | 180 W 180,000 mW 0.241 hp 0.18 kW |

| 2950X | $ 899.00 € 809.10 £ 728.19 ¥ 92,893.67 | 31 August 2018 | Ryzen Threadripper | Colfax | 16 | 32 | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 32 MiB 32,768 KiB 33,554,432 B 0.0313 GiB | 3.5 GHz 3,500 MHz 3,500,000 kHz | 4.4 GHz 4,400 MHz 4,400,000 kHz | 180 W 180,000 mW 0.241 hp 0.18 kW |

| 2970WX | $ 1,299.00 € 1,169.10 £ 1,052.19 ¥ 134,225.67 | 29 October 2018 | Ryzen Threadripper | Colfax | 24 | 48 | 12 MiB 12,288 KiB 12,582,912 B 0.0117 GiB | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 3 GHz 3,000 MHz 3,000,000 kHz | 4.2 GHz 4,200 MHz 4,200,000 kHz | 250 W 250,000 mW 0.335 hp 0.25 kW |

| 2990WX | $ 1,799.00 € 1,619.10 £ 1,457.19 ¥ 185,890.67 | 13 August 2018 | Ryzen Threadripper | Colfax | 32 | 64 | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 3 GHz 3,000 MHz 3,000,000 kHz | 4.2 GHz 4,200 MHz 4,200,000 kHz | 250 W 250,000 mW 0.335 hp 0.25 kW |

| Count: 35 | |||||||||||

Bibliography[edit]

- AMD CES Tech Day 2018, Jim Anderson

- AMD CES Tech Day 2018, Lisa Su

- AMD CES Tech Day 2018, Mark Papermaster

- David. S. (August 2018). "AMD Announces Threadripper 2, Chiplets Aid Core Scaling"

Documents[edit]

See Also[edit]

- Intel Coffee Lake

| codename | Zen+ + |

| core count | 1 +, 4 +, 6 +, 8 +, 12 +, 16 +, 24 + and 32 + |

| designer | AMD + |

| first launched | April 13, 2018 + |

| full page name | amd/microarchitectures/zen+ + |

| instance of | microarchitecture + |

| instruction set architecture | x86-64 + |

| manufacturer | GlobalFoundries + |

| microarchitecture type | CPU + |

| name | Zen+ + |

| pipeline stages | 19 + |

| process | 12 nm (0.012 μm, 1.2e-5 mm) + |