From WikiChip

Difference between revisions of "zhaoxin/microarchitectures/wudaokou"

(→Sockets/Platform) |

(→Release Dates) |

||

| Line 40: | Line 40: | ||

== Release Dates == | == Release Dates == | ||

[[File:zhaoxin roadmap (2017).png|right|400px]] | [[File:zhaoxin roadmap (2017).png|right|400px]] | ||

| − | WuDaoKou | + | Development for WuDaoKou started in August 2013. WuDaoKou [[taped out]] on November 9, 2017. The architecture and SKUs were officially unveiled at a conference on December 28, 2018. |

== Process Technology == | == Process Technology == | ||

Revision as of 01:13, 31 January 2018

| Edit Values | |

| WuDaoKou µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | Zhaoxin |

| Manufacturer | HLMC |

| Introduction | December 28, 2017 |

| Process | 28 nm |

| Core Configs | 2, 4, 8 |

| Pipeline | |

| Type | Superscalar |

| OoOE | Yes |

| Speculative | Yes |

| Reg Renaming | Yes |

| Instructions | |

| ISA | x86-64 |

| Succession | |

WuDaoKou is the successor to Zhangjiang, a 28 nm x86 microarchitecture designed by Zhaoxin for mainstream laptops, desktops, and servers.

Contents

Brands

| Family | Series | Description |

|---|---|---|

| KaiXian | KX (5000) | Desktop, Laptops |

| KaisHeng | KH (20000) | Storage, Servers |

Release Dates

Development for WuDaoKou started in August 2013. WuDaoKou taped out on November 9, 2017. The architecture and SKUs were officially unveiled at a conference on December 28, 2018.

Process Technology

WuDaoKou is manufactured on HLMC's 28 nm process.

Architecture

Key changes from Zhangjiang

- 1.4x performance

- 8 cores per die (up from 4)

- SoC design

- New Uncore

- northbridge moved on-die

- PCIe 3.0 (from 2.0)

- DDR4 (From DDR3)

- New integrated graphics processor

- HD Audio Output/Codec

- DirectX 11.1

- Up to 3 displays

- DP / eDP / HDMI / VGA

- New Uncore

- Core

- Pipeline was reduced by 5 stages

- Execution engines were re-balanced

- Branch prediction unit was reworked and optimized

- FSB removed

- x4 PCIe 3.0 communication with southbridge chipset

- Chipset

- Gigabit Ethernet port (RGMII)

- USB 3.1 Gen2 (Type-C) ports

- SATA 3.0 ports

This list is incomplete; you can help by expanding it.

Block Diagram

| This section is empty; you can help add the missing info by editing this page. |

Memory Hierarchy

- Cache

- L1D Cache

- 32 KiB, 8-way set associative

- Per core

- L1I Cache

- 32 KiB, 8-way set associative

- Per core

- L2 Cache

- 4 MiB, 32-way set associative

- Per quad-core cluster

- L1D Cache

- System DRAM

- 2 Channels

- DDR4, Up to 2400 MT/s

Sockets/Platform

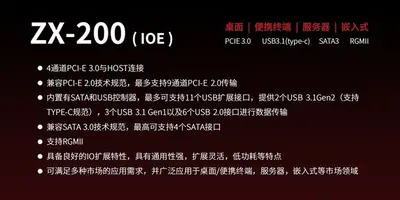

All parts use a HFCBGA 37.5×37.5 mm package and are effectively a system on a chip. However, for the most part, those parts get paired with a chipset which serves as an I/O extension chip. The chipset communicates with the microprocessor over standard PCIe 3.0 x4 lanes.

| Chipset | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| Chipset | TDP | PCIe | SATA | USB | Network | Process | Package | |||

| 2.0 | 3.0 | 3.0 | 2.0 | 3.1 Gen 1 | 3.1 Gen 2 | |||||

| ZX-200 | 6 W | 9 lanes | - | 4 | 6 | 3 | 2 | 10/100M/1 Gbps | 40 nm | FCBGA (21mm x 21mm) |

Die

- HLMC 28 nm process

- 187 mm² die size

- 2,100,000,000 transistors

All WuDaoKou Processors

| List of WuDaoKou-based Processors | |||||||

|---|---|---|---|---|---|---|---|

| Main processor | |||||||

| Model | Family | Launched | Cores | L2 | Frequency | Max Memory | ECC |

| KH-25800 | KaisHeng | 28 December 2017 | 8 | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 1.8 GHz 1,800 MHz 1,800,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✔ |

| KH-26800 | KaisHeng | 28 December 2017 | 8 | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 2 GHz 2,000 MHz 2,000,000 kHz | 128 GiB 131,072 MiB 134,217,728 KiB 137,438,953,472 B 0.125 TiB | ✔ |

| KX-5540 | KaiXian | 28 December 2017 | 4 | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 1.8 GHz 1,800 MHz 1,800,000 kHz | 64 GiB 65,536 MiB 67,108,864 KiB 68,719,476,736 B 0.0625 TiB | ✘ |

| KX-5640 | KaiXian | 28 December 2017 | 4 | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 2 GHz 2,000 MHz 2,000,000 kHz | 64 GiB 65,536 MiB 67,108,864 KiB 68,719,476,736 B 0.0625 TiB | ✘ |

| KX-U5580 | KaiXian | 28 December 2017 | 8 | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 1.8 GHz 1,800 MHz 1,800,000 kHz | 64 GiB 65,536 MiB 67,108,864 KiB 68,719,476,736 B 0.0625 TiB | ✘ |

| KX-U5580M | KaiXian | 28 December 2017 | 8 | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 1.8 GHz 1,800 MHz 1,800,000 kHz | 64 GiB 65,536 MiB 67,108,864 KiB 68,719,476,736 B 0.0625 TiB | ✘ |

| KX-U5680 | KaiXian | 28 December 2017 | 8 | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 2 GHz 2,000 MHz 2,000,000 kHz | 64 GiB 65,536 MiB 67,108,864 KiB 68,719,476,736 B 0.0625 TiB | ✘ |

| Count: 7 | |||||||

References

- Information was obtained directly from Zhaoxin

- Zhaoxin launches their highest-performance Chinese x86 chips

Facts about "WuDaoKou - Microarchitectures - Zhaoxin"

| codename | WuDaoKou + |

| core count | 2 +, 4 + and 8 + |

| designer | Zhaoxin + |

| first launched | December 28, 2017 + |

| full page name | zhaoxin/microarchitectures/wudaokou + |

| instance of | microarchitecture + |

| instruction set architecture | x86-64 + |

| manufacturer | HLMC + |

| microarchitecture type | CPU + |

| name | WuDaoKou + |

| process | 28 nm (0.028 μm, 2.8e-5 mm) + |