This article details Intel's semiconductor process technology history for research and posterity.

Overview

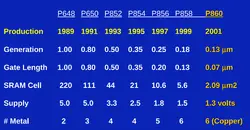

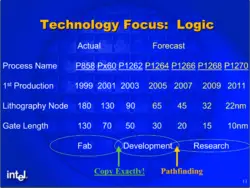

The table below shows the history of Intel's process scaling. Values were taken from various Intel documents including IDF presentations, ISSCC papers, and IEDM papers. Note that while a great deal of effort was put into ensuring the accuracy of the values, some numbers vary to a small degree between Intel's own documents and therefore discrepancies may exist. SRAM bitcell areas refer to a high-density 6T bitcell with the exception of the very first few processes where smaller cell designs were used. Additionally, the metal layer count is for the client dies (example consumer mobile & desktop); server models utilize considerably more layers. Finally, from the 45 nm node, Intel has switched to utilizing a high-κ material, therefore the oxide thickness shown refers to the equivalent oxide thickness instead.

Timeline

| Year | Process | Node | MLayers | µarchs | Gate | Interconnects | Attributes | |||

|---|---|---|---|---|---|---|---|---|---|---|

| 1977 | CHMOS I | 3 µm | 1 | 8085, 8086, 8088, 80186 |

Tox | 70 nm | Gate Dielectric | SiO2 | ||

| Vdd | 5 V | SRAM | 1120 µm² | |||||||

| Lg | 3.0 µm | |||||||||

| CPP | 7 µm | MMP | 11 µm | |||||||

| 1979 | CHMOS II | 2 µm | 1 | Tox | 40 nm | Gate Dielectric | SiO2 | |||

| Vdd | 5 V | SRAM | 1740 µm² | |||||||

| Lg | 2.0 µm | |||||||||

| CPP | 5.6 µm | MMP | 8 µm | |||||||

| 1982 | P646 (CHMOS III) |

1.5 µm | 1 | 80286, 80386 |

Tox | 25 nm | Gate Dielectric | SiO2 | ||

| Vdd | 5 V | SRAM | 951.7 µm² | |||||||

| Lg | 1.5 µm | |||||||||

| CPP | 4.0 µm | MMP | 6.4 µm | |||||||

| 1987 | P648 | 1.0 µm | 2 | 80486 | Tox | Gate Dielectric | SiO2 | |||

| Vdd | 5 V | SRAM | 220 µm² | |||||||

| Lg | 1.0 µm | |||||||||

| CPP | MMP | |||||||||

| 1989 | P650 | 0.8 µm | 3 | 80486 | Tox | 15 nm | Gate Dielectric | SiO2 | ||

| Vdd | 4 V | SRAM | 111 µm² | |||||||

| Lg | 800 µm | |||||||||

| CPP | 1.7 µm | MMP | 2 µm | |||||||

| 1991 | P652 | 0.6 µm | 4 | 80486, P5 |

Tox | 8 nm | Gate Dielectric | SiO2 | ||

| Vdd | 3.3 V | SRAM | ||||||||

| Lg | 600 µm | |||||||||

| CPP | MMP | 1.4 µm | ||||||||

| 1993 | P852 | 0.5 µm | 4 | P5 | Tox | 8 nm | Gate Dielectric | SiO2 | ||

| Vdd | 3.3 V | SRAM | 44 µm² | |||||||

| Lg | 500 nm | |||||||||

| CPP | MMP | |||||||||

| 1995 | P854 | 0.35 µm | 4 | P6 | Tox | 6 nm | Gate Dielectric | SiO2 | ||

| Vdd | 2.5 V | SRAM | 20.5 µm² | |||||||

| Lg | 350 nm | |||||||||

| CPP | 920 nm | MMP | 880 nm | |||||||

| 1997 | P856 | 0.25 µm | 5 | P6 | Tox | 4.08 nm | Gate Dielectric | SiO2 | ||

| Vdd | 1.8 V | SRAM | 10.26 µm² | |||||||

| Lg | 200 nm | |||||||||

| CPP | 500 nm | MMP | 640 nm | |||||||

| 1998 | P856.5 | 0.25 µm | 5 | P6 | Tox | 4.08 nm | Gate Dielectric | SiO2 | ||

| Vdd | 1.8 V | SRAM | 9.26 µm² | |||||||

| Lg | 200 nm | |||||||||

| CPP | 475 nm | MMP | 608 nm | |||||||

| 1999 | P858 | 0.18 µm | 6 | NetBurst |  |

Tox | 2.0 nm | Gate Dielectric | SiO2 | |

| Vdd | 1.6 V | SRAM | 5.59 µm² | |||||||

| Lg | 130 nm | |||||||||

| CPP | 480 nm | MMP | 500 nm | |||||||

| 2001 | P860 | 0.13 µm | 6 | Pentium M |  |

| Tox | 1.4 nm | Gate Dielectric | SiO2 |

| Vdd | 1.4 V | SRAM | 2.45 µm² | |||||||

| Lg | 70 nm | |||||||||

| CPP | 336 nm | MMP | 345 nm | |||||||

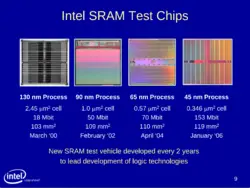

| 2003 | P1262 | 90 nm | 7 | Pentium M |  |

| Tox | 1.2 nm | Gate Dielectric | SiO2 |

| Vdd | 1.2 V | SRAM | 1.00 µm² | |||||||

| Lg | 50 nm | |||||||||

| CPP | 260 nm | MMP | 220 nm | |||||||

| 2005 | P1264 | 65 nm | 8 | Core, Modified Pentium M |

|

| Tox | 1.2 nm | Gate Dielectric | SiO2 |

| Vdd | SRAM | 0.570 µm² | ||||||||

| Lg | 35 nm | |||||||||

| CPP | 220 nm | MMP | 210 nm | |||||||

| 2007 | P1266 | 45 nm | 9 | Penryn, Nehalem |

|

| Toxe | 1 nm | Gate Dielectric | High-κ |

| Vdd | SRAM | 0.346 µm² | ||||||||

| Lg | 25 nm | |||||||||

| CPP | 160 nm | MMP | 180 nm | |||||||

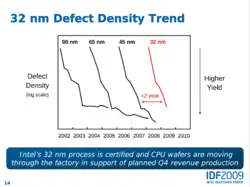

| 2009 | P1268 | 32 nm | 10 | Westmere, Sandy Bridge |

|

| Toxe | Gate Dielectric | High-κ | |

| Vdd | 0.75 V | SRAM | 0.148 µm² | |||||||

| Lg | 30 nm | |||||||||

| CPP | 112.5 nm | MMP | 112.5 nm | |||||||

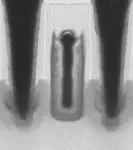

| 2011 | P1270 | 22 nm | 11 | Ivy Bridge, Haswell |

|

| Toxe | Gate Dielectric | High-κ | |

| Vdd | 0.75 V | SRAM | 0.092 µm² | |||||||

| Lg | 26 nm | |||||||||

| CPP | 90 nm | MMP | 80 nm | |||||||

| Pfin | 60 nm | |||||||||

| Wfin | 8 nm | Hfin | 34 nm | |||||||

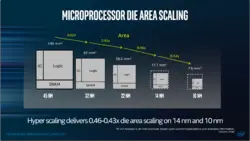

| 2014 | P1272 | 14 nm | 12 | Broadwell, Skylake, Kaby Lake, Coffee Lake |

|

| Toxe | Gate Dielectric | High-κ | |

| Vdd | 0.70 V | SRAM | 0.0499 µm² | |||||||

| Lg | 20 nm | |||||||||

| CPP | 70 nm | MMP | 52 nm | |||||||

| Pfin | 42 nm | |||||||||

| Wfin | 8 nm | Hfin | 42-46 nm | |||||||

| 2017 | P1274 | 10 nm | 12 | Cannon Lake, Icelake, Tigerlake |

Toxe | Gate Dielectric | High-κ | |||

| Vdd | 0.70 V | SRAM | 0.0312 µm² | |||||||

| Lg | 18 nm | |||||||||

| CPP | 54 nm | MMP | 36 nm | |||||||

| Pfin | 34 nm | |||||||||

| Wfin | 7 nm | Hfin | 44-55 nm | |||||||

| 202? | P1276 | 7 nm | ||||||||

| 202? | P1278 | 5 nm | ||||||||

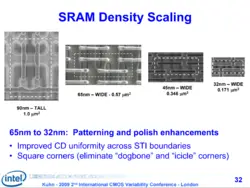

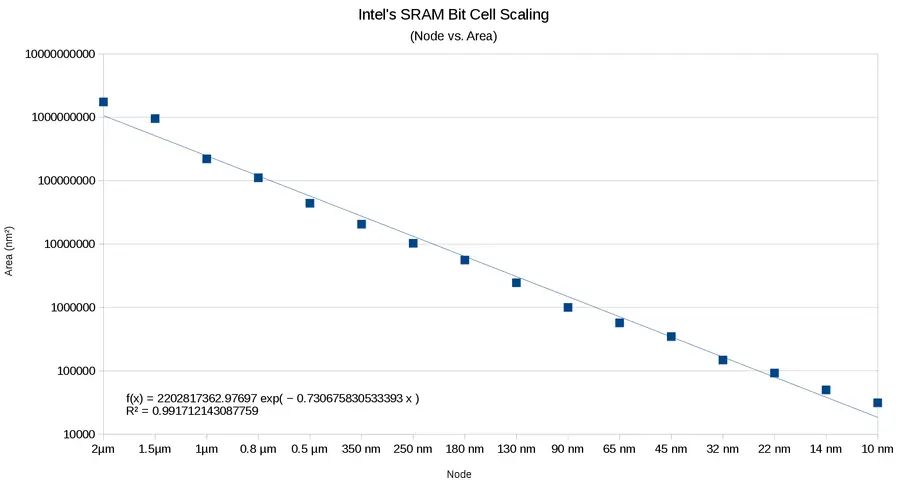

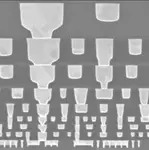

SRAM Scaling

For Intel, from 2 µm to 10 nm, SRAM 6T bit cells have had an average shrink of 0.496x in an attempt to maintain Moore's Law double density observation/requirement. Note that SRAM shrunk more significantly prior to the 65 nm process node. It should also be noted that logic typically scales better than the typical 6T SRAM cells, so raw logic density scaled more over time. Nonetheless, the size of the SRAM can be as much as three to four times the density of the typical logic cell.

Other processes

Semiconductor Process history by company:

- DEC

- Intel