(added info on the GNA) |

(→Overview) |

||

| Line 158: | Line 158: | ||

== Overview == | == Overview == | ||

[[File:ice lake overview.svg|right|500px]] | [[File:ice lake overview.svg|right|500px]] | ||

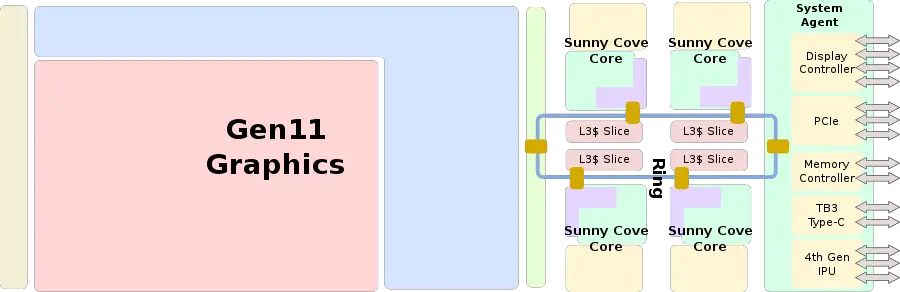

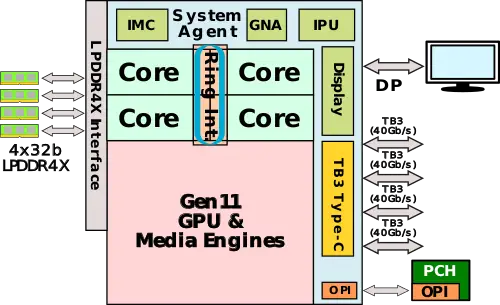

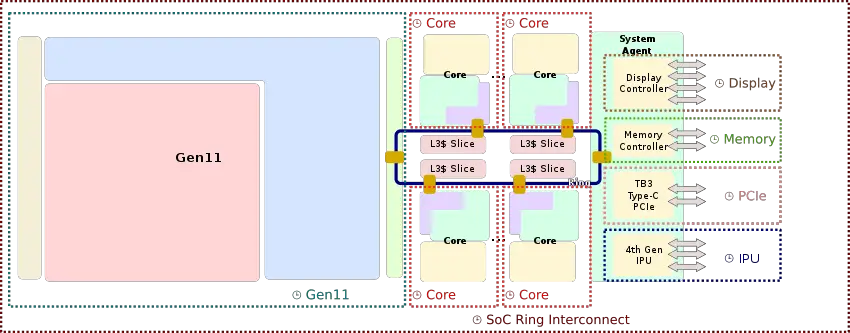

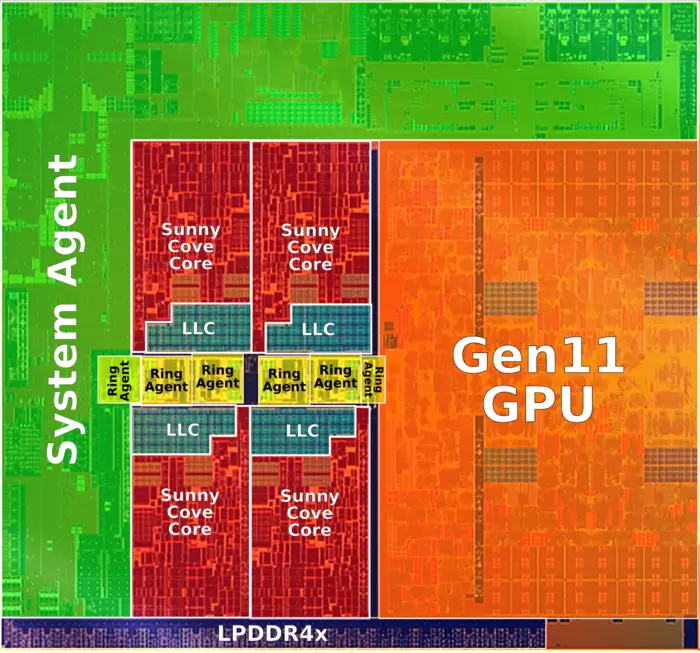

| − | The Ice Lake [[system on a chip]] is a [[10-nanometer]] SoC aimed at mainstream to premium mobile and thin | + | The Ice Lake [[system on a chip]] is a [[10-nanometer]] SoC that is aimed at the mainstream to premium mobile and the thin-and-light market. The microprocessor consists of five major components: CPU cores, LLC, {{intel|ring interconnect}}, {{intel|system agent}}, and {{\\|Gen11}} graphics. While a lot of what Ice Lake provides is inherited from the prior generations, Intel claims that every IP on Ice Lake has been enhanced in one way or another. A major enhancement in Ice Lake over the prior generation is the integration of up to four {{\\|Sunny Cove}} cores which provide a significant uplift in IPC. Those cores also bring {{x86|AVX-512}} support for the client market. Those cores, along with the system agent and the GPU, are linked over Intel's {{intel|ring interconnect}}. The chip is fed through a new [[integrated memory controller]] that supports quad-channel 32-bit LPDDR4X memory, providing bandwidths in the range of 50-60 GB/s. Ice Lake has a new integrated GPU which is based on their {{\\|Gen11}} microarchitecture which provides a large improvement in graphics performance. |

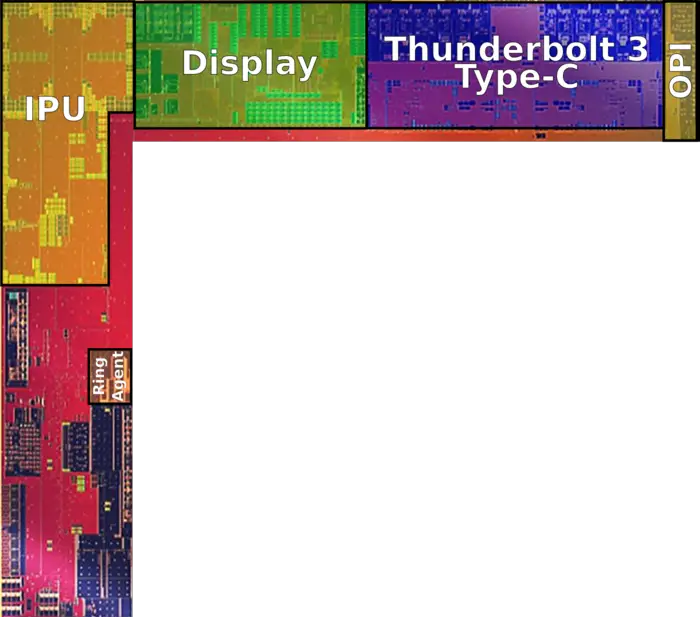

The system architecture in Ice Lake has been redesigned. Intel added a new Gaussian Neural Accelerator (GNA) for the acceleration of inference applications. There is a new 4th-generation [[image processing unit]] (IPU). There is a new Thunderbolt 3 integration. Ice Lake has four Thunderbolt 3 ports. All four ports have the same capabilities and can be used simultaneously at full performance at up to 40 Gbps per port. Intel also upgraded the display engine to {{\\|Gen11}} with an improved display pipe that has a new Adaptive Sync and HDR-capable display pipes that support HDR 3 and DisplayPort 1.4, supporting error correction and compression. | The system architecture in Ice Lake has been redesigned. Intel added a new Gaussian Neural Accelerator (GNA) for the acceleration of inference applications. There is a new 4th-generation [[image processing unit]] (IPU). There is a new Thunderbolt 3 integration. Ice Lake has four Thunderbolt 3 ports. All four ports have the same capabilities and can be used simultaneously at full performance at up to 40 Gbps per port. Intel also upgraded the display engine to {{\\|Gen11}} with an improved display pipe that has a new Adaptive Sync and HDR-capable display pipes that support HDR 3 and DisplayPort 1.4, supporting error correction and compression. | ||

Revision as of 22:14, 4 June 2019

| Edit Values | |

| Ice Lake (client) µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | Intel |

| Manufacturer | Intel |

| Introduction | May 27, 2019 |

| Process | 10 nm |

| Instructions | |

| ISA | x86-64 |

| Cache | |

| L1I Cache | 32 KiB/core 8-way set associative |

| L1D Cache | 48 KiB/core 12-way set associative |

| L2 Cache | 512 KiB/512 KiB 12-way set associative |

| L3 Cache | 2 MiB/core 16-way set associative |

| Cores | |

| Core Names | Ice Lake Y, Ice Lake U |

| Succession | |

| Contemporary | |

| Ice Lake (server) | |

Ice Lake (ICL) Client Configuration is Intel's successor to Cannon Lake, a 10 nm microarchitecture for mainstream workstations, desktops, and mobile devices.

Contents

Codenames

| Core | Abbrev | Description | Graphics | Target |

|---|---|---|---|---|

| Ice Lake Y | ICL-Y | Extremely low power | 2-in-1s detachable, tablets, and computer sticks | |

| Ice Lake U | ICL-U | Ultra-low Power | Light notebooks, portable All-in-Ones (AiOs), Minis, and conference room | |

| Ice Lake H | ICL-H | High-performance Graphics | Ultimate mobile performance, mobile workstations | |

| |

|

|

|

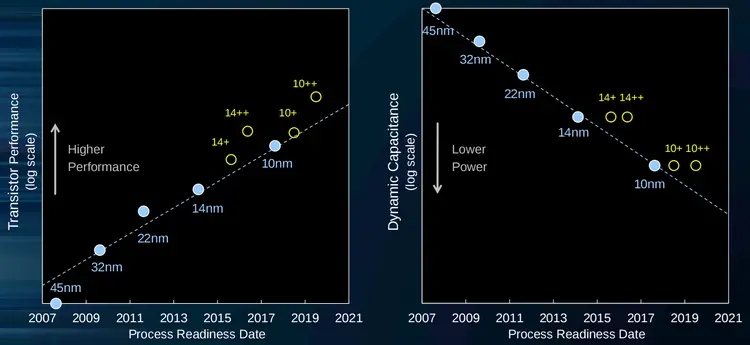

Process Technology

- See also: Cannon Lake § Process Technology

Ice Lake is fabricated on Intel's second-generation enhanced 10 nm process called "10 nm+". Versus the first generation 10nm which was used for Cannon Lake, 10nm+ features higher performance through higher drive current for the same power envelope. Intel says that Ice Lake is built on their learnings from their Cannon Lake products which were largely treated as a learning vehicle. Between Cannon Lake and Ice Lake, a number of changes were made in order to improve the process for their products. One such change was the addition of an extra metal layer (originally said to be 12, is now presumably 13 on Ice Lake) in order to improve the power delivery of the chip. Additionally, they have improved the threshold voltage of the transistors as well as their MIM cap among other changes.

Compiler support

Support for Ice Lake was added in LLVM Clang 6.0 and GCC 8.0.

| Compiler | Arch-Specific | Arch-Favorable |

|---|---|---|

| ICC | -march=icelake |

-mtune=icelake

|

| GCC | -march=icelake |

-mtune=icelake

|

| LLVM | -march=icelake |

-mtune=icelake

|

| Visual Studio | /? |

/tune:?

|

CPUID

| Core | Extended Family |

Family | Extended Model |

Model |

|---|---|---|---|---|

| U, Y | 0 | 0x6 | 0x7 | 0xE |

| Family 6 Model 126 | ||||

| ? | 0 | 0x6 | ? | ? |

| Family 6 Model ? | ||||

Architecture

Ice Lake comprises of Sunny Cove cores on the ring interconnect architecture along with Gen11 GPU, and an improved System Agent with a new display engine and I/O.

Key changes from Cannon Lake/Skylake

- Enhanced "10nm+" (from "10nm", 2nd gen)

- Core

- Sunny Cove core (from Palm Cove)

- See Sunny Cove for microarchitectural details and changes

- Sunny Cove core (from Palm Cove)

- Memory

- Graphics

- Display

- Gen 11.5 (from Gen9/Gen9.5)

- DisplayPort 1.4a with Display Stream Compression(DSC) (from DisplayPort 1.2)

- HDMI 2.0b (from HDMI 1.4)

- IPU

- 4th Gen IPU (from 3rd Gen in Skylake)

- More cameras support

- New concurrent image pipeline

- on-die MIPI interface

- New Integration

- New Gaussian Neural Accelerator 1.0 (Added in Cannon Lake but unclear to what extent)

- I/O

- Thunderbolt 3 over Type-C

- Package

- New Type3, Type4 packages

- New thin-film magnetic inductors

- New Type3, Type4 packages

This list is incomplete; you can help by expanding it.

New instructions

- See also: Sunny Cove § New Instructions

Ice Lake introduced a number of new instructions.

-

SHA- Hardware acceleration for SHA hashing operations -

CLWB- Force cache line write-back without flush -

RDPID- Read Processor ID -

AVX-512(originally introduced in Skylake (Server) but only now in client) - Additional AVX-512 extensions:

-

AVX512VPOPCNTDQ- AVX-512 Vector Population Count Doubleword and Quadword -

AVX512VNNI- AVX-512 Vector Neural Network Instructions -

AVX512GFNI- AVX-512 Galois Field New Instructions -

AVX512VAES- AVX-512 Vector AES -

AVX512VBMI2- AVX-512 Vector Bit Manipulation, Version 2 -

AVX512BITALG- AVX-512 Bit Algorithms -

AVX512VPCLMULQDQ- AVX-512 Vector Vector Carry-less Multiply

-

-

SSE_GFNI- SSE-based Galois Field New Instructions -

AVX_GFNI- AVX-based Galois Field New Instructions - Split Lock Detection - detection and cause an exception for split locks

- Fast Short REP MOV

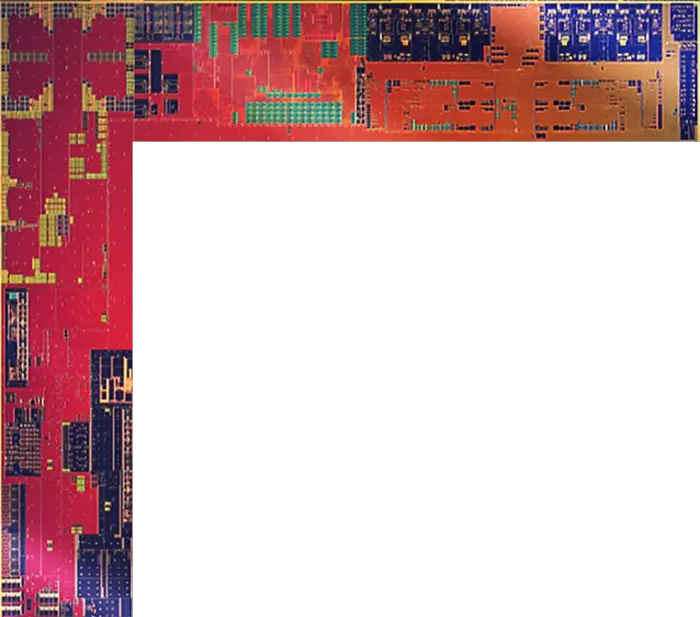

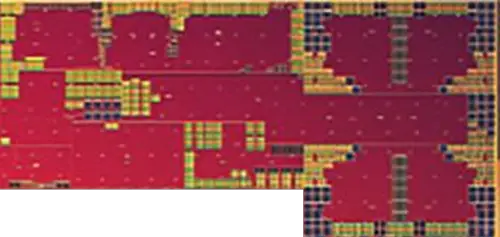

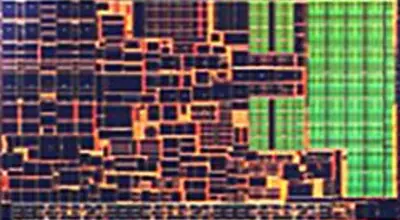

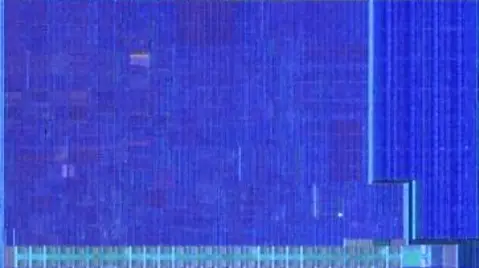

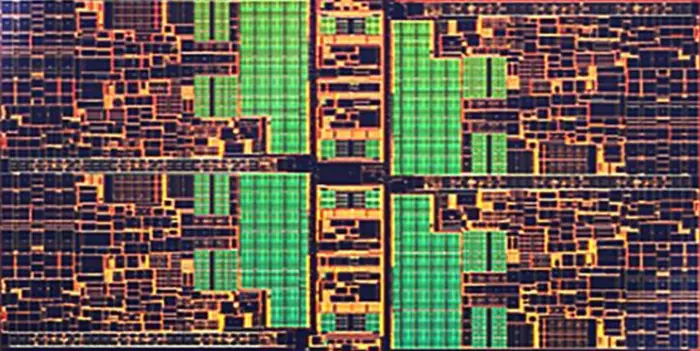

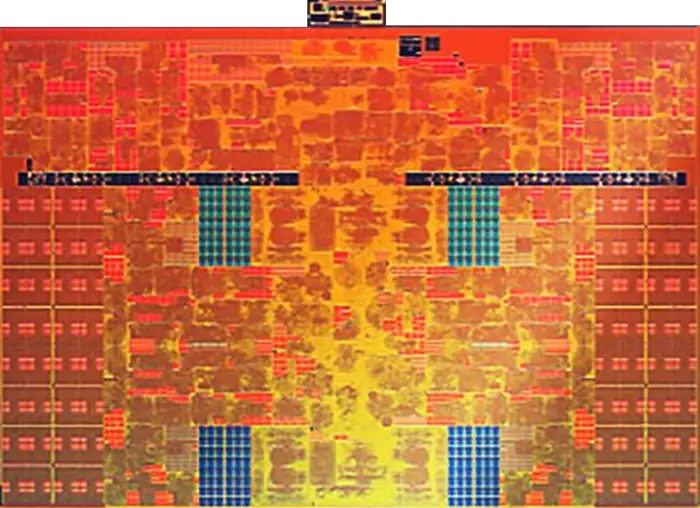

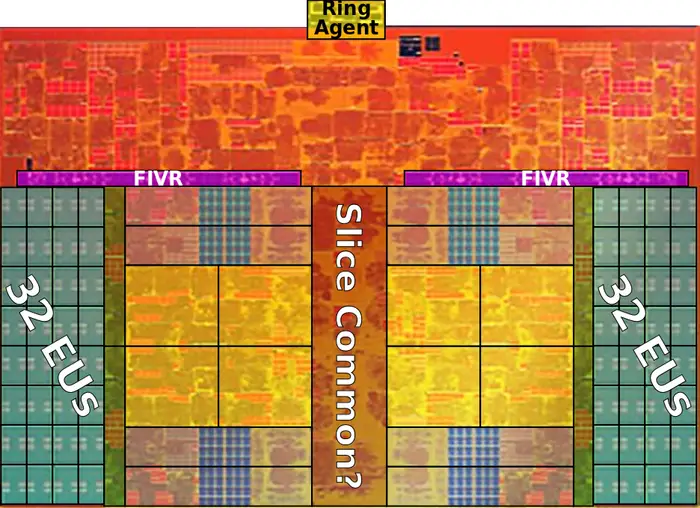

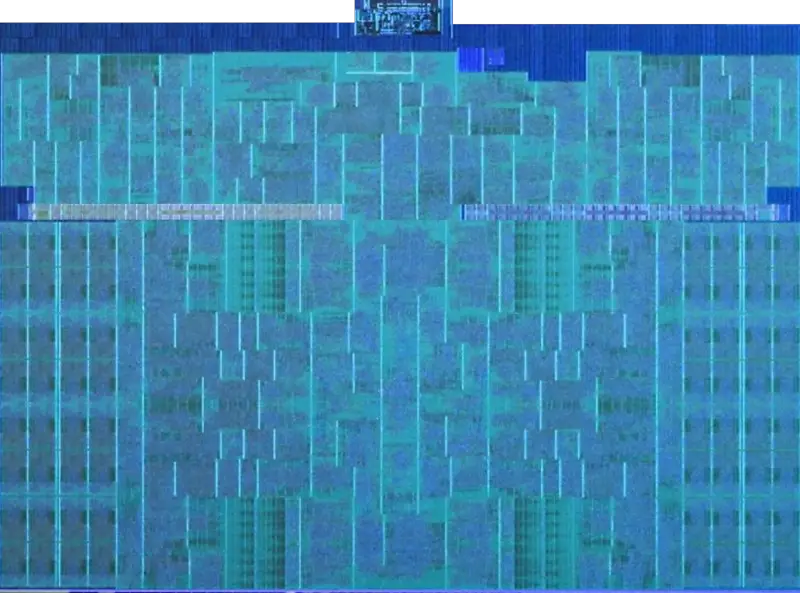

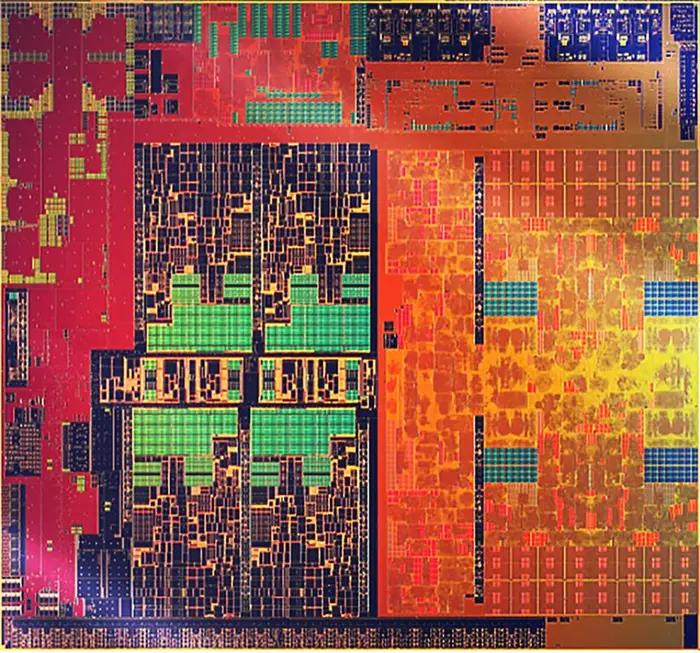

Block Diagram

Entire SoC Overview

Individual Core

See Sunny Cove § Block Diagram.

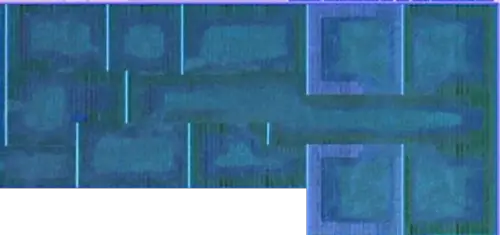

Gen11 Graphics

See Gen11 Graphics § Block Diagram.

Overview

The Ice Lake system on a chip is a 10-nanometer SoC that is aimed at the mainstream to premium mobile and the thin-and-light market. The microprocessor consists of five major components: CPU cores, LLC, ring interconnect, system agent, and Gen11 graphics. While a lot of what Ice Lake provides is inherited from the prior generations, Intel claims that every IP on Ice Lake has been enhanced in one way or another. A major enhancement in Ice Lake over the prior generation is the integration of up to four Sunny Cove cores which provide a significant uplift in IPC. Those cores also bring AVX-512 support for the client market. Those cores, along with the system agent and the GPU, are linked over Intel's ring interconnect. The chip is fed through a new integrated memory controller that supports quad-channel 32-bit LPDDR4X memory, providing bandwidths in the range of 50-60 GB/s. Ice Lake has a new integrated GPU which is based on their Gen11 microarchitecture which provides a large improvement in graphics performance.

The system architecture in Ice Lake has been redesigned. Intel added a new Gaussian Neural Accelerator (GNA) for the acceleration of inference applications. There is a new 4th-generation image processing unit (IPU). There is a new Thunderbolt 3 integration. Ice Lake has four Thunderbolt 3 ports. All four ports have the same capabilities and can be used simultaneously at full performance at up to 40 Gbps per port. Intel also upgraded the display engine to Gen11 with an improved display pipe that has a new Adaptive Sync and HDR-capable display pipes that support HDR 3 and DisplayPort 1.4, supporting error correction and compression.

Ice Lake chips integrate the PCH die on-package communicating over the on-package interconnect (OPI). The new PCH The PCH has an expanded I/O support for PCIe, USB, SATA, as well as audio DSP for load power voice processing. It also integrates WiFi 6+ CNVi.

On the platform level, there is a new integrated power delivery (FIVR) on both the PCH and the CPU which Intel says allows them to save on platform area by about 15% and it reduces the power delivery rails for the OEMs by roughly half.

Core

| This section is empty; you can help add the missing info by editing this page. |

Integration

GNA

Ice Lake introduced a new low-power neural processor called the Gaussian Neural Accelerator v1.0 (GNA) which is integrated on the SoC and runs at very low power even when the GPU and CPUs are turned off. The GNA can be used for long-running tasks (e.g., real-time meeting transcription). The GNA can operate while the remaining parts of the SoC are in idle in order to have minimal impact on performance.

IPU

Ice Lake incorporates 4th generation image processing unit (IPU). The IPU was first introduced with Skylake mobile SoCs (note that those were 3rd gen). The 4th Gen IPU found in Ice Lake introduces a number of new enhancements. It introduces new support for 4K video capture at 30fps. There is also new hardware support for better de-noising which supports up to 16 megapixels stills in low light conditions. In addition for support more camera simultaneously, the IPU incorporates a new concurrent image pipeline, supporting multiple different processing from the same camera stream, allowing a single camera to take the functionality of multiple sensors. A common example of that is devices with both IR and RGB cameras in the laptop bezel which can now be changed to a single camera. Intel says they are exposing more registers from the IPU to software in order to provide more flexibility for applications that make use of that for machine learning. It’s also worth noting that Intel integrated the MIPI interface onto the processor as well. Previously that was found on the chipset. The change significantly improves the latency, a required attribute needed for more advanced ML-specific applications. Some of those changes are designed to form the foundation for future generations of improvements.

Clock domains

Ice Lake is divided into a number of clock domains, each controlling the clock frequency of their respective unit in the processor. All clock domains are some multiple of the [virtual] bus clock (BCLK).

- BCLK - Bus/Base Clock - The system bus interface frequency (once upon a time referred to the actual FSB speed, it now serves as only a base clock reference for all other clock domains). The base clock is 100 MHz.

- Core Clock - The frequency at which the core and the L1/L2 caches operate at. (Frequency depends on the model and is represented as a multiple of BCLK).

- Ring Clock - The frequency at which the ring interconnect and LLC operate at. Data from/to the individual cores are read/written into the L3 at a rate of 32B/cycle operating at Ring Clock frequency.

- IGP Clock - The frequency at which the integrated graphics (Gen11 GPU) operates at. Data from/to the GPU are read/written into the LLC at a rate of 64B/cycle operating at this frequency as well.

- IPU - The frequency at which the image processing unit operates at

- MemClk - Memory Clock - The frequency at which the system DRAM operates at. DRAM data is transferred at a rate of 8B/cycle operating at MemClk frequency.

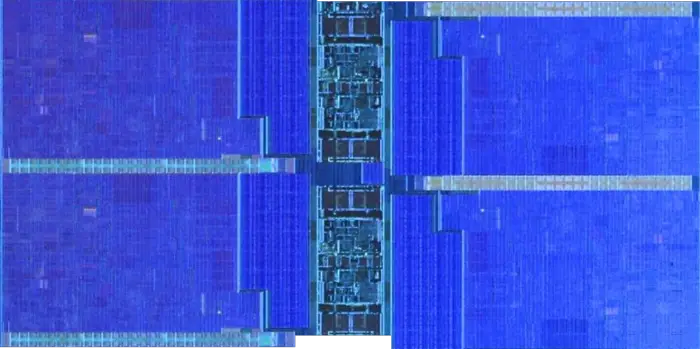

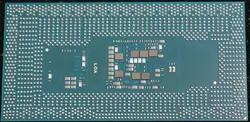

Packaging

Ice Lake comes in two packagings.

| Package | Type3 | Type4 |

|---|---|---|

| Core | Ice Lake U | Ice Lake Y |

| TDP | 15 W | 9 W |

| Dimensions | 50 x 25 x 1.3 mm | 26.5 x 18.5 x 1.0 mm |

| Balls | 1526 balls | 1377 balls |

| Ball Pitch | 0.65 mm | 0.43 mm |

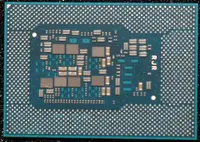

| Package (Front) |  |

|

| Package (Back) |  |

|

Thin-film magnetic inductor

Interestingly the new packages include a thin-film magnetic inductor array on the landing side. Those are said to have higher efficiency at lower power but also support the fully processor dynamic frequency range. They can be distinctly seen on the back of the chip.

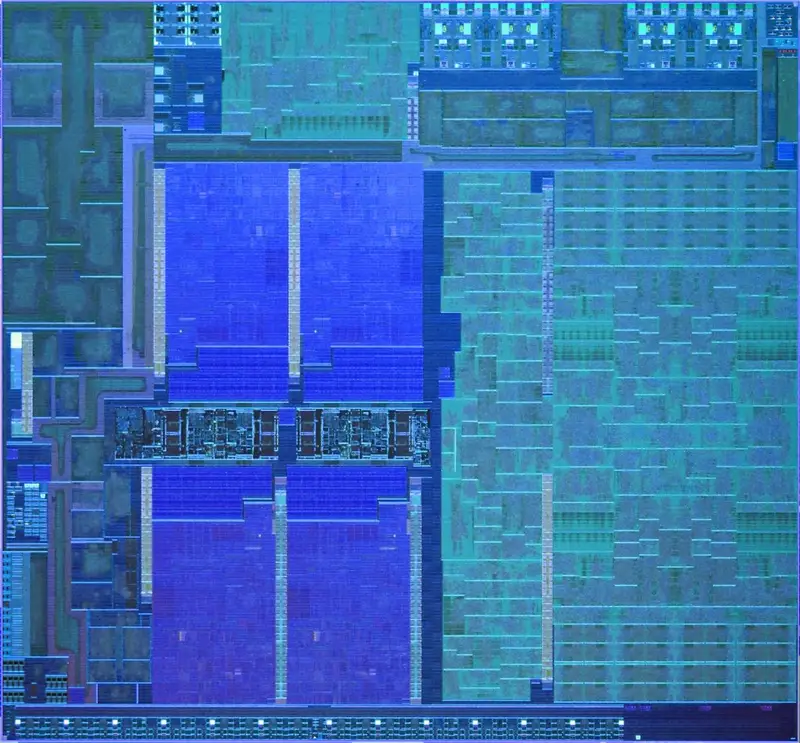

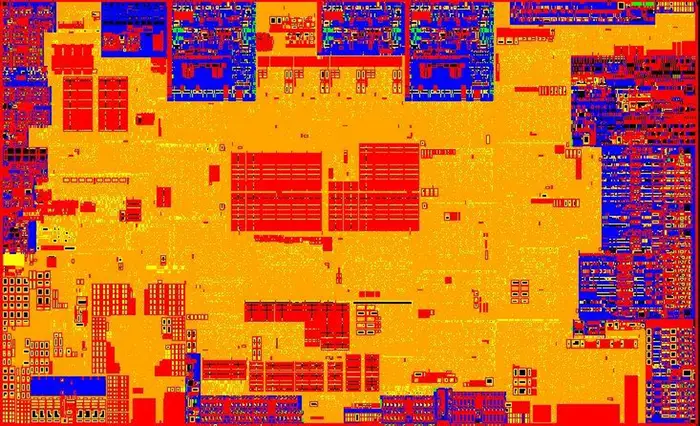

Die

System Agent

- System Agent

- 4th Gen IPU

- Gen11 Display

- Thunderbolt 3 over Type-C I/O subsystem

IPU

Display engine

Thunderbolt 3 I/O subsystem

Core

- See also: Sunny Cove § Die

- ~6.91 mm² die size

- ~3.5 mm x ~1.97 mm

Core group

- See also: Sunny Cove § Die

- ~30.73 mm² die size

- ~7.86 mm x ~3.91 mm

Integrated graphics

- Gen11 GPU

- 64 EUs

- ~41.1 mm² silicon area

- ~5.22 mm x ~7.86 mm

SoC

- 10 nm process

- ~122.52 mm² die size

- ~11.44 mm x ~10.71 mm

- 4 Sunny Cove big cores

- 64-EU Gen11 GPU

- 4th Gen IPU

PCH

- 14 nm process

- ~53.76 mm² die size

- ~5.69 mm x 9.45 mm

All Ice Lake Chips

| List of Ice Lake-based Processors | ||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Main processor | Turbo Boost | Memory | GPU | Features | ||||||||||||||||

| Model | Launched | Price | Family | Platform | Core | Cores | Threads | L3$ | TDP | Base | 1 Core | 2 Cores | 4 Cores | 6 Cores | Max Memory | Name | Base | Burst | TBT | HT |

| Count: 0 | ||||||||||||||||||||

Bibliography

- Intel 2018 Architecture Day.

- Intel. personal communication. 2019.

| codename | Ice Lake (client) + |

| core count | 2 + and 4 + |

| designer | Intel + |

| first launched | May 27, 2019 + |

| full page name | intel/microarchitectures/ice lake (client) + |

| instance of | microarchitecture + |

| instruction set architecture | x86-64 + |

| manufacturer | Intel + |

| microarchitecture type | CPU + |

| name | Ice Lake (client) + |

| pipeline stages (max) | 19 + |

| pipeline stages (min) | 14 + |

| process | 10 nm (0.01 μm, 1.0e-5 mm) + |