From WikiChip

Difference between revisions of "intel/microarchitectures/core (client)"

(→Overview) |

|||

| (8 intermediate revisions by 4 users not shown) | |||

| Line 7: | Line 7: | ||

|introduction=April, 2006 | |introduction=April, 2006 | ||

|phase-out=May, 2009 | |phase-out=May, 2009 | ||

| − | |isa | + | |isa=x86-64 |

| − | |||

| − | |||

|process=65 nm | |process=65 nm | ||

|predecessor=Modified Pentium M | |predecessor=Modified Pentium M | ||

| Line 25: | Line 23: | ||

== Overview == | == Overview == | ||

| − | When Core was introduced in 2006, Intel described it as a merger of both {{\\|P6}} and {{\\|NetBurst}}. When scrutinizing the details, it's fairly clear that little was actually borrowed from {{\\|NetBurst}}. In fact, it wasn't until Intel's entirely new microarchitecture {{\\|Sandy Bridge}} that a true merger presented itself. | + | * When Core was introduced in [[2006]], Intel described it as a merger of both {{\\|P6}} and {{\\|NetBurst}}. |

| + | :When scrutinizing the details, it's fairly clear that little was actually borrowed from {{\\|NetBurst}}. | ||

| + | :In fact, it wasn't until Intel's entirely new microarchitecture {{\\|Sandy Bridge}} that a true merger presented itself. | ||

{{expand section}} | {{expand section}} | ||

| + | |||

| + | |||

| + | === Intel Core Lines === | ||

| + | {{see also|Intel|intel/atom}} | ||

| + | {| class="wikitable mw-datatable" style="margin:0.2em auto; text-align:center; min-width:72em;" | ||

| + | |+Intel Core (+ Pentium 4) Roadmap | ||

| + | |- | ||

| + | ! rowspan="2" | Fab<br>process | ||

| + | ! rowspan="2" | Micro-<br>architecture | ||

| + | ! rowspan="2" | Code<br>names | ||

| + | ! rowspan="2" | Core<br>{{abbr|Gen|generation}} | ||

| + | ! rowspan="2" | Scalable<br>(Xeon)<br>{{abbr|Gen|generation}} | ||

| + | ! rowspan="2" | Release<br>date | ||

| + | ! colspan="5" | Processors | ||

| + | |- | ||

| + | ! Mobile | ||

| + | ! Desktop | ||

| + | ! Enthusiast/<br>Workstation | ||

| + | ! 1P/2P<br>Server | ||

| + | ! 4P/8P<br>Server | ||

| + | |- | ||

| + | | [[180 nm]] | ||

| + | ! rowspan="2" | [[NetBurst]] | ||

| + | | {{intel|Willamette|l=core}} | ||

| + | | colspan="2" rowspan="3" | — | ||

| + | | 2000-11 | ||

| + | | — | ||

| + | | {{intel|Willamette|l=core}} | ||

| + | | — | ||

| + | | Foster | ||

| + | | Foster MP | ||

| + | |- | ||

| + | | [[130 nm]]<hr>[[90 nm]] | ||

| + | | {{intel|Northwood|l=core}}<hr>{{intel|Prescott|l=arch}} | ||

| + | | 2002-01 | ||

| + | | Northwood <br>Mobile | ||

| + | | Northwood <hr>Prescott | ||

| + | | Northwood-XE <hr>Prescott 2M-XE | ||

| + | | Prestonia<br>Gallatin | ||

| + | | Gallatin | ||

| + | |- <!-- Pentium M (arch): Core: Banias, Dothan, Stealey, Canmore, Tolapai; Core: (Atom) Diamondville, Silverthorne --> | ||

| + | | [[130 nm]]<hr>[[90 nm]]<hr>[[90 nm]]<hr>[[65 nm]] | ||

| + | ! {{intel|Pentium M|l=arch}}<br>.<hr>.<br>{{intel|Pentium D|l=arch}}<!-- Pentium D: 90 nm Smithfield, 65 nm Presler --> | ||

| + | | {{intel|Banias|l=core}}<hr>{{intel|Dothan|l=core}}<hr>{{intel|Smithfield|l=core}}<hr>{{intel|Presler|l=core}} | ||

| + | | 2004-02 | ||

| + | | {{intel|Banias|l=core}}<hr>{{intel|Dothan|l=core}} | ||

| + | | {{intel|Smithfield|l=core}}<hr>{{intel|Presler|l=core}} | ||

| + | | Smithfield-XE<hr>Presler-XE | ||

| + | | Nocona<br>Irwindale<br>Paxville | ||

| + | | Potomac<br>Cranford<br>Paxville | ||

| + | |- | ||

| + | | rowspan="2" | [[65 nm]] | ||

| + | ! {{intel|Modified Pentium M|Modified <br>Pentium M|l=arch}} | ||

| + | | {{intel|Yonah|l=core}}<br>{{intel|Cedar Mill|l=core}} | ||

| + | | 1<br><small>(Yonah)</small> | ||

| + | | rowspan="10" | — | ||

| + | | 2006-01 | ||

| + | | Yonah | ||

| + | | Cedar Mill | ||

| + | | - | ||

| + | | Dempsey<br>Sossaman | ||

| + | | Tulsa <br>('''Xeon''') | ||

| + | |- | ||

| + | ! rowspan="2" | '''{{intel|core|Intel Core|l=arch}}''' | ||

| + | | {{intel|Merom|l=core}} | ||

| + | | rowspan="2" | 2 | ||

| + | | 2006-07 | ||

| + | | {{intel|Merom|l=core}}<br>Merom-L | ||

| + | | {{intel|Conroe|l=core}} | ||

| + | | {{intel|Kentsfield|l=core}} | ||

| + | | {{intel|Woodcrest|l=core}}<br>{{intel|Clovertown|l=core}} | ||

| + | | {{intel|Tigerton|l=core}} | ||

| + | |- | ||

| + | | rowspan="2" | [[45 nm]] | ||

| + | | [[Penryn]] | ||

| + | | 2007-11 | ||

| + | | {{intel|Penryn|l=arch}} | ||

| + | | {{intel|Wolfdale|l=core}} | ||

| + | | {{intel|Yorkfield|l=core}} | ||

| + | | {{intel|Harpertown|l=core}} | ||

| + | | {{intel|Dunnington|l=core}} | ||

| + | |- | ||

| + | ! rowspan="2" | {{intel|Nehalem|l=arch}} | ||

| + | | {{intel|Nehalem|l=arch}} | ||

| + | | rowspan="2" | 1 <br>(Core i) | ||

| + | | 2008-11 | ||

| + | | {{intel|Clarksfield|l=core}} | ||

| + | | {{intel|Lynnfield|l=core}} | ||

| + | | {{intel|Bloomfield|l=core}} | ||

| + | | {{intel|Gainestown|l=core}} | ||

| + | | {{intel|Beckton|l=core}} | ||

| + | |- | ||

| + | | rowspan="2" | [[32 nm]] | ||

| + | | {{intel|Westmere|l=arch}} | ||

| + | | 2010-01 | ||

| + | | {{intel|Arrandale|l=core}} | ||

| + | | {{intel|Clarkdale|l=core}} | ||

| + | | {{intel|Gulftown|l=core}} | ||

| + | | {{intel|Westmere EP|l=core}} | ||

| + | | {{intel|Westmere EX|l=core}} | ||

| + | |- | ||

| + | ! rowspan="2" | {{intel|Sandy Bridge|l=arch}} | ||

| + | | {{intel|Sandy Bridge|l=arch}} | ||

| + | | 2 | ||

| + | | 2011-01 | ||

| + | | {{intel|Sandy Bridge M|l=core}} | ||

| + | | {{intel|Sandy Bridge|l=arch}} | ||

| + | | {{intel|Sandy Bridge E|l=core}} | ||

| + | | {{intel|Sandy Bridge EP|l=core}} | ||

| + | | — | ||

| + | |- | ||

| + | | rowspan="3" | [[22 nm]] | ||

| + | | {{intel|Ivy Bridge|l=arch}} | ||

| + | | 3 | ||

| + | | 2012-04 | ||

| + | | {{intel|Ivy Bridge M|l=core}} | ||

| + | | {{intel|Ivy Bridge|l=arch}} | ||

| + | | {{intel|Ivy Bridge E|l=core}} | ||

| + | | {{intel|Ivy Bridge EP|l=core}} | ||

| + | | {{intel|Ivy Bridge EX|l=core}} | ||

| + | |- | ||

| + | ! rowspan="2" | {{intel|Haswell|l=arch}} | ||

| + | | [[Haswell]] | ||

| + | | rowspan="2" | 4 | ||

| + | | 2013-06 | ||

| + | | {{intel|Haswell H|l=core}}<br>{{intel|Haswell MB|l=core}}<br>{{intel|Haswell ULP|l=core}}<br>{{intel|Haswell ULX|l=core}} | ||

| + | | {{intel|Haswell DT|l=core}} | ||

| + | | {{intel|Haswell E|l=core}} | ||

| + | | {{intel|Haswell EP|l=core}} | ||

| + | | {{intel|Haswell EX|l=core}} | ||

| + | |- | ||

| + | | ''Devil's Canyon'' | ||

| + | | 2014-06 | ||

| + | | — | ||

| + | | Haswell DT | ||

| + | | colspan=3 | — | ||

| + | |- | ||

| + | | rowspan="10" | [[14 nm]] | ||

| + | ! {{intel|Broadwell|l=arch}} | ||

| + | | [[Broadwell]] | ||

| + | | 5 | ||

| + | | 2014-09 | ||

| + | | {{intel|Broadwell H|l=core}}<br>{{intel|Broadwell U|l=core}}<br>{{intel|Broadwell Y|l=core}} | ||

| + | | {{intel|Broadwell DT|l=core}}<br>''{{intel|Broadwell DE|l=core}}'' | ||

| + | | {{intel|Broadwell E|l=core}} | ||

| + | | {{intel|Broadwell EP|l=core}}<br>('''{{intel|Xeon E5}}''' v4) | ||

| + | | {{intel|Broadwell EX|l=core}}<br>('''{{intel|Xeon E7}}''' v4) | ||

| + | |- | ||

| + | ! {{intel|Skylake|l=arch}} | ||

| + | | [[Skylake]] | ||

| + | | 6 | ||

| + | | Xeon 1 | ||

| + | | 2015-08 | ||

| + | | {{intel|Skylake H|l=core}}<br>{{intel|Skylake U|l=core}}<br>{{intel|Skylake Y|l=core}} | ||

| + | | ''{{intel|Skylake DT|l=core}}''<br>{{intel|Skylake S|l=core}} | ||

| + | | {{intel|Skylake W|l=core}}<br>{{intel|Skylake X|l=core}} | ||

| + | | colspan="2" | {{intel|Skylake SP|l=core}}<br><small>(formerly Skylake-EP/EX)</small> <br>('''Xeon''' Gold, Platinum) | ||

| + | |- | ||

| + | ! {{intel|Kaby Lake|l=arch}} | ||

| + | | [[Kaby Lake]] | ||

| + | | 7 / 8 | ||

| + | | rowspan="4" | — | ||

| + | | 2016-10 | ||

| + | | {{intel|Kaby Lake G|l=core}}<br>{{intel|Kaby Lake H|l=core}}<br>{{intel|Kaby Lake U|l=core}}<br>{{intel|Kaby Lake Y|l=core}} | ||

| + | | {{intel|Kaby Lake S|l=core}} | ||

| + | | {{intel|Kaby Lake X|l=core}} | ||

| + | | colspan="2" | — | ||

| + | |- | ||

| + | ! {{intel|Coffee Lake|l=arch}} | ||

| + | | [[Coffee Lake]] | ||

| + | | 8 / 9 | ||

| + | | 2017-10 | ||

| + | | {{intel|Coffee Lake B|l=core}}<br>{{intel|Coffee Lake H|l=core}}<br>{{intel|Coffee Lake U|l=core}} | ||

| + | | {{intel|Coffee Lake S|l=core}} | ||

| + | | {{intel|Coffee Lake W|l=core}} | ||

| + | | [[Coffee Lake]]<br>('''{{intel|Xeon}}''' E) | ||

| + | | — | ||

| + | |- | ||

| + | ! {{intel|Whiskey Lake|l=arch}} | ||

| + | | [[Whiskey Lake]] | ||

| + | | 8 | ||

| + | | rowspan="2" | 2018-08 | ||

| + | | {{intel|Whiskey Lake U|l=core}} | ||

| + | | colspan="2" rowspan="2" | — | ||

| + | | colspan="2" rowspan="2" | — | ||

| + | |- | ||

| + | ! {{intel|Amber Lake|l=arch}} | ||

| + | | [[Amber Lake]] | ||

| + | | 8 / 10 | ||

| + | | {{intel|Amber Lake Y|l=core}} | ||

| + | |- | ||

| + | ! {{intel|Cascade Lake|l=arch}} | ||

| + | | [[Cascade Lake]] | ||

| + | | — | ||

| + | | Xeon 2 | ||

| + | | 2019-04 | ||

| + | | colspan="2" | — | ||

| + | | {{intel|Cascade Lake W|l=core}}<br>{{intel|Cascade Lake X|l=core}} | ||

| + | | colspan="2" | {{intel|Cascade Lake AP|l=core}}<br>{{intel|Cascade Lake SP|l=core}} ('''Xeon''') | ||

| + | |- | ||

| + | ! {{intel|Comet Lake|l=arch}} | ||

| + | | [[Comet Lake]] | ||

| + | | 10 | ||

| + | | — | ||

| + | | 2019-09 | ||

| + | | {{intel|Comet Lake H|l=core}}<br>{{intel|Comet Lake Y|l=core}}<br>{{intel|Comet Lake U|l=core}} | ||

| + | | {{intel|Comet Lake S|l=core}} | ||

| + | | {{intel|Comet Lake W|l=core}} | ||

| + | | colspan="2" | — | ||

| + | |- | ||

| + | ! {{intel|Cooper Lake|l=arch}} | ||

| + | | [[Cooper Lake]] | ||

| + | | — | ||

| + | | Xeon 3 | ||

| + | | 2020-06 | ||

| + | | colspan="4" | — | ||

| + | | {{intel|Cooper Lake SP|l=core}} | ||

| + | |- | ||

| + | ! {{intel|Rocket Lake|l=arch}} | ||

| + | | {{intel|Cypress Cove|l=core}} | ||

| + | | 11 | ||

| + | | rowspan=2 | — | ||

| + | | 2021-03 | ||

| + | | — | ||

| + | | {{intel|Rocket Lake SP|l=core}} | ||

| + | | {{intel|Rocket Lake W|l=core}} | ||

| + | | {{intel|Rocket Lake|l=arch}}<br>('''{{intel|Xeon}}''' E) | ||

| + | | — | ||

| + | |- | ||

| + | | rowspan=4 | [[10 nm]] | ||

| + | ! [[Cannon Lake]] | ||

| + | | [[Palm Cove]] | ||

| + | | 8 | ||

| + | | 2018-05 | ||

| + | | {{intel|Cannon Lake U|l=core}} | ||

| + | | colspan=2 | — | ||

| + | | colspan=2 | — | ||

| + | |- | ||

| + | ! [[Ice Lake]]<br><small>(client)</small><br><small>(server)</small> | ||

| + | | rowspan=2 | [[Sunny Cove]]<br>.<hr>.<br>+ 4x {{intel|Tremont|l=arch}} | ||

| + | | 10 | ||

| + | | Xeon 3 | ||

| + | | 2019-09<br><small>(client)</small><br>2021-04<br><small>(server)</small> | ||

| + | | {{intel|Ice Lake U|l=core}}<br>{{intel|Ice Lake Y|l=core}} | ||

| + | | — | ||

| + | | {{intel|Ice Lake W|l=core}} | ||

| + | | {{intel|Ice Lake SP|l=core}} <!-- + Cooper Lake --> | ||

| + | | — | ||

| + | |- | ||

| + | ! {{intel|Lakefield|l=arch}}<br><small>(hybrid)</small><br>({{intel|Foveros}}) | ||

| + | | — | ||

| + | | rowspan="3" | — | ||

| + | | 2020-06 | ||

| + | | {{intel|Lakefield|l=arch}} | ||

| + | | | ||

| + | | | ||

| + | | | ||

| + | | — | ||

| + | |- | ||

| + | ! {{intel|Tiger Lake|l=arch}} | ||

| + | | {{intel|Willow Cove|l=arch}} | ||

| + | | 11 | ||

| + | | 2020-09 | ||

| + | | Tiger Lake-H<br>Tiger Lake-H35<br>Tiger Lake-UP3<br>Tiger Lake-UP4 | ||

| + | | | ||

| + | | | ||

| + | | | ||

| + | | — | ||

| + | |- | ||

| + | | rowspan="4" | [[Intel]] [[7 nm]] | ||

| + | ! {{intel|Alder Lake|l=arch}}<br><small>(hybrid)</small> | ||

| + | | rowspan="2" | {{intel|Golden Cove|l=arch}} (P)<br>{{intel|Gracemont|l=arch}} (E) | ||

| + | | 12 | ||

| + | | 2021-11 <!-- ? "Sunny Cove" --> | ||

| + | | Alder Lake-H<br>Alder Lake-HX<br>Alder Lake-U<br>{{intel|Alder Lake M|l=core}} | ||

| + | | {{intel|Alder Lake S|l=core}} | ||

| + | | {{intel|Alder Lake P|l=core}} | ||

| + | | colspan=2 | — | ||

| + | |- | ||

| + | ! [[Sapphire Rapids]] | ||

| + | | — | ||

| + | | Xeon 4 | ||

| + | | 2023-01 | ||

| + | | colspan=2 | — | ||

| + | | Sapphire <br>Rapids-WS | ||

| + | | Sapphire <br>Rapids-SP/HBM<br>('''{{intel|Xeon}}''' Max) | ||

| + | | Sapphire <br>Rapids-SP | ||

| + | |- | ||

| + | ! {{intel|Raptor Lake|l=arch}}<br><small>(hybrid)</small> | ||

| + | | rowspan="2" | {{intel|Raptor Cove|l=arch}} (P)<br>{{intel|Gracemont|l=arch}} (E) | ||

| + | | 13 / 14 /<br>Series<br> 1 / 2 | ||

| + | | — | ||

| + | | 2022-10 | ||

| + | | Raptor Lake-HX<br>Raptor Lake-PX<br>Raptor Lake U | ||

| + | | Raptor Lake S | ||

| + | | Raptor Lake H<br>Raptor Lake P | ||

| + | | Raptor Lake<br>('''{{intel|Xeon}}''' E) | ||

| + | | rowspan=2 | — | ||

| + | |- | ||

| + | ! {{intel|Emerald Rapids|l=arch}} | ||

| + | | — | ||

| + | | Xeon 5 | ||

| + | | 2023-12 | ||

| + | | colspan="3" | — | ||

| + | | Emerald <br>Rapids-SP | ||

| + | |- | ||

| + | | [[Intel]] [[4 nm]] | ||

| + | ! {{intel|Meteor Lake|l=arch}}<br><small>(hybrid)</small> | ||

| + | | rowspan="2" | {{intel|Redwood Cove|l=arch}} (P)<br>{{intel|Crestmont|l=arch}} (E) | ||

| + | | Ultra <br>Series 1 | ||

| + | | — | ||

| + | | 2023-12 | ||

| + | | Meteor Lake-H<br>Meteor Lake-U | ||

| + | | colspan="2" | — | ||

| + | | colspan="2" | — | ||

| + | |- | ||

| + | | [[Intel]] [[3 nm]] | ||

| + | ! {{intel|Granite Rapids|l=arch}} | ||

| + | | — | ||

| + | | '''{{intel|Sierra Forest|Xeon 6|l=arch}}''' | ||

| + | | 2024-09 | ||

| + | | colspan="3" | — | ||

| + | | Granite Rapids-AP<br>Granite Rapids-SP | ||

| + | | — | ||

| + | |- | ||

| + | | rowspan="2" | TSMC N3B | ||

| + | ! {{intel|Lunar Lake|l=arch}}<br><small>(hybrid)</small> | ||

| + | | rowspan="2" | {{intel|Lion Cove|l=arch}} (P)<br>{{intel|Skymont|l=arch}} (E) | ||

| + | | Ultra<br>200V <!-- Core Ultra 200V --> | ||

| + | | rowspan="3" | — | ||

| + | | 2024-09 | ||

| + | | Lunar Lake-V | ||

| + | | colspan=2 | — | ||

| + | | colspan=2 | — | ||

| + | |- | ||

| + | ! {{intel|Arrow Lake|l=arch}}<br><small>(hybrid)</small> | ||

| + | | Ultra<br>Series 2 | ||

| + | | 2024-10<br><small>(desktop)</small><br>2025-01<br><small>(mobile)</small> | ||

| + | | Arrow Lake-H<br>Arrow Lake-HX<br>Arrow Lake-U | ||

| + | | Arrow Lake-S | ||

| + | | | ||

| + | | — | ||

| + | | — | ||

| + | |- | ||

| + | | rowspan="2" | [[Intel]] 18A | ||

| + | ! {{intel|Panther Lake|l=arch}}<br><small>(hybrid)</small> | ||

| + | | {{intel|Cougar Cove|l=arch}} (P)<br>{{intel|Darkmont|l=arch}} (E) <!-- Cougar Cove (P-cores), Darkmont (E-cores) --> | ||

| + | | Ultra <br>300 <!-- Core Ultra 300 --> | ||

| + | | 2025 | ||

| + | | Panther Lake-H<br>Panther Lake-HL<br>Panther Lake-U<br>Panther Lake-UL | ||

| + | | ? | ||

| + | | | ||

| + | | — | ||

| + | | — | ||

| + | |- | ||

| + | ! {{intel|Diamond Rapids|l=arch}} | ||

| + | | {{intel|Panther Cove X|l=arch}}<br>(''Mountain Stream'') <!-- Panther Cove X, Mountain Stream --> | ||

| + | | — | ||

| + | | ? | ||

| + | | 2025 | ||

| + | | — | ||

| + | | | ||

| + | | | ||

| + | | — | ||

| + | | — | ||

| + | |- | ||

| + | | rowspan="2" | TBA<br>(TSMC <br>2 nm or<br>Intel 18A) | ||

| + | ! {{intel|Nova Lake|l=arch}}<br><small>(hybrid)</small> | ||

| + | | {{intel|Coyote Cove|l=arch}} <!-- Coyote Cove (P), Arctic Wolf (E) --> | ||

| + | | | ||

| + | | — | ||

| + | | 2026 | ||

| + | | — | ||

| + | | TBA | ||

| + | | TBA | ||

| + | | — | ||

| + | | — | ||

| + | |- | ||

| + | ! {{intel|Razer Lake|l=arch}}<br><small>(hybrid)</small> | ||

| + | | | ||

| + | | | ||

| + | | — | ||

| + | | 2027 | ||

| + | | — | ||

| + | | TBA | ||

| + | | TBA | ||

| + | | — | ||

| + | | — | ||

| + | |- | ||

| + | |} | ||

| + | {{clear}} | ||

== Die Shot == | == Die Shot == | ||

Latest revision as of 20:00, 1 March 2025

| Edit Values | |

| Core µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | Intel |

| Manufacturer | Intel |

| Introduction | April, 2006 |

| Phase-out | May, 2009 |

| Process | 65 nm |

| Instructions | |

| ISA | x86-64 |

| Succession | |

Core was the microarchitecture for Intel's 65 nm process for desktops and servers as a successor to NetBurst. Core was replaced by the Penryn microarchitecture in late 2008.

Contents

Architecture[edit]

| This section is empty; you can help add the missing info by editing this page. |

Key changes from NetBurst[edit]

| This section is empty; you can help add the missing info by editing this page. |

Overview[edit]

- When scrutinizing the details, it's fairly clear that little was actually borrowed from NetBurst.

- In fact, it wasn't until Intel's entirely new microarchitecture Sandy Bridge that a true merger presented itself.

| This section requires expansion; you can help adding the missing info. |

Intel Core Lines[edit]

- See also: Intel and intel/atom

| Fab process |

Micro- architecture |

Code names |

Core Gen |

Scalable (Xeon) Gen |

Release date |

Processors | ||||

|---|---|---|---|---|---|---|---|---|---|---|

| Mobile | Desktop | Enthusiast/ Workstation |

1P/2P Server |

4P/8P Server | ||||||

| 180 nm | NetBurst | Willamette | — | 2000-11 | — | Willamette | — | Foster | Foster MP | |

| 130 nm 90 nm |

Northwood Prescott |

2002-01 | Northwood Mobile |

Northwood Prescott |

Northwood-XE Prescott 2M-XE |

Prestonia Gallatin |

Gallatin | |||

| 130 nm 90 nm 90 nm 65 nm |

Pentium M . . Pentium D |

Banias Dothan Smithfield Presler |

2004-02 | Banias Dothan |

Smithfield Presler |

Smithfield-XE Presler-XE |

Nocona Irwindale Paxville |

Potomac Cranford Paxville | ||

| 65 nm | Modified Pentium M |

Yonah Cedar Mill |

1 (Yonah) |

— | 2006-01 | Yonah | Cedar Mill | - | Dempsey Sossaman |

Tulsa (Xeon) |

| Intel Core | Merom | 2 | 2006-07 | Merom Merom-L |

Conroe | Kentsfield | Woodcrest Clovertown |

Tigerton | ||

| 45 nm | Penryn | 2007-11 | Penryn | Wolfdale | Yorkfield | Harpertown | Dunnington | |||

| Nehalem | Nehalem | 1 (Core i) |

2008-11 | Clarksfield | Lynnfield | Bloomfield | Gainestown | Beckton | ||

| 32 nm | Westmere | 2010-01 | Arrandale | Clarkdale | Gulftown | Westmere EP | Westmere EX | |||

| Sandy Bridge | Sandy Bridge | 2 | 2011-01 | Sandy Bridge M | Sandy Bridge | Sandy Bridge E | Sandy Bridge EP | — | ||

| 22 nm | Ivy Bridge | 3 | 2012-04 | Ivy Bridge M | Ivy Bridge | Ivy Bridge E | Ivy Bridge EP | Ivy Bridge EX | ||

| Haswell | Haswell | 4 | 2013-06 | Haswell H Haswell MB Haswell ULP Haswell ULX |

Haswell DT | Haswell E | Haswell EP | Haswell EX | ||

| Devil's Canyon | 2014-06 | — | Haswell DT | — | ||||||

| 14 nm | Broadwell | Broadwell | 5 | 2014-09 | Broadwell H Broadwell U Broadwell Y |

Broadwell DT Broadwell DE |

Broadwell E | Broadwell EP (Xeon E5 v4) |

Broadwell EX (Xeon E7 v4) | |

| Skylake | Skylake | 6 | Xeon 1 | 2015-08 | Skylake H Skylake U Skylake Y |

Skylake DT Skylake S |

Skylake W Skylake X |

Skylake SP (formerly Skylake-EP/EX) (Xeon Gold, Platinum) | ||

| Kaby Lake | Kaby Lake | 7 / 8 | — | 2016-10 | Kaby Lake G Kaby Lake H Kaby Lake U Kaby Lake Y |

Kaby Lake S | Kaby Lake X | — | ||

| Coffee Lake | Coffee Lake | 8 / 9 | 2017-10 | Coffee Lake B Coffee Lake H Coffee Lake U |

Coffee Lake S | Coffee Lake W | Coffee Lake (Xeon E) |

— | ||

| Whiskey Lake | Whiskey Lake | 8 | 2018-08 | Whiskey Lake U | — | — | ||||

| Amber Lake | Amber Lake | 8 / 10 | Amber Lake Y | |||||||

| Cascade Lake | Cascade Lake | — | Xeon 2 | 2019-04 | — | Cascade Lake W Cascade Lake X |

Cascade Lake AP Cascade Lake SP (Xeon) | |||

| Comet Lake | Comet Lake | 10 | — | 2019-09 | Comet Lake H Comet Lake Y Comet Lake U |

Comet Lake S | Comet Lake W | — | ||

| Cooper Lake | Cooper Lake | — | Xeon 3 | 2020-06 | — | Cooper Lake SP | ||||

| Rocket Lake | Cypress Cove | 11 | — | 2021-03 | — | Rocket Lake SP | Rocket Lake W | Rocket Lake (Xeon E) |

— | |

| 10 nm | Cannon Lake | Palm Cove | 8 | 2018-05 | Cannon Lake U | — | — | |||

| Ice Lake (client) (server) |

Sunny Cove . . + 4x Tremont |

10 | Xeon 3 | 2019-09 (client) 2021-04 (server) |

Ice Lake U Ice Lake Y |

— | Ice Lake W | Ice Lake SP | — | |

| Lakefield (hybrid) (Foveros) |

— | — | 2020-06 | Lakefield | — | |||||

| Tiger Lake | Willow Cove | 11 | 2020-09 | Tiger Lake-H Tiger Lake-H35 Tiger Lake-UP3 Tiger Lake-UP4 |

— | |||||

| Intel 7 nm | Alder Lake (hybrid) |

Golden Cove (P) Gracemont (E) |

12 | 2021-11 | Alder Lake-H Alder Lake-HX Alder Lake-U Alder Lake M |

Alder Lake S | Alder Lake P | — | ||

| Sapphire Rapids | — | Xeon 4 | 2023-01 | — | Sapphire Rapids-WS |

Sapphire Rapids-SP/HBM (Xeon Max) |

Sapphire Rapids-SP | |||

| Raptor Lake (hybrid) |

Raptor Cove (P) Gracemont (E) |

13 / 14 / Series 1 / 2 |

— | 2022-10 | Raptor Lake-HX Raptor Lake-PX Raptor Lake U |

Raptor Lake S | Raptor Lake H Raptor Lake P |

Raptor Lake (Xeon E) |

— | |

| Emerald Rapids | — | Xeon 5 | 2023-12 | — | Emerald Rapids-SP | |||||

| Intel 4 nm | Meteor Lake (hybrid) |

Redwood Cove (P) Crestmont (E) |

Ultra Series 1 |

— | 2023-12 | Meteor Lake-H Meteor Lake-U |

— | — | ||

| Intel 3 nm | Granite Rapids | — | Xeon 6 | 2024-09 | — | Granite Rapids-AP Granite Rapids-SP |

— | |||

| TSMC N3B | Lunar Lake (hybrid) |

Lion Cove (P) Skymont (E) |

Ultra 200V |

— | 2024-09 | Lunar Lake-V | — | — | ||

| Arrow Lake (hybrid) |

Ultra Series 2 |

2024-10 (desktop) 2025-01 (mobile) |

Arrow Lake-H Arrow Lake-HX Arrow Lake-U |

Arrow Lake-S | — | — | ||||

| Intel 18A | Panther Lake (hybrid) |

Cougar Cove (P) Darkmont (E) |

Ultra 300 |

2025 | Panther Lake-H Panther Lake-HL Panther Lake-U Panther Lake-UL |

? | — | — | ||

| Diamond Rapids | Panther Cove X (Mountain Stream) |

— | ? | 2025 | — | — | — | |||

| TBA (TSMC 2 nm or Intel 18A) |

Nova Lake (hybrid) |

Coyote Cove | — | 2026 | — | TBA | TBA | — | — | |

| Razer Lake (hybrid) |

— | 2027 | — | TBA | TBA | — | — | |||

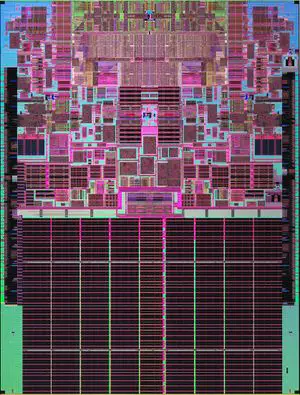

Die Shot[edit]

Dual-core Core[edit]

- Woodcrest

- 143 mm²

- 291,000,000 transistors

- 65 nm process

- 2 cores

Documents[edit]

- Intel® Processor Micro-architecture – Core®; Intel® Software College, 2006

- White Paper: Inside Intel® Core TM Microarchitecture, 2006

- Intel Multi-core Architecture and Implementations, March 7, 2006

- Intel® Core Microarchitecture, March 8, 2006

- Intel® Core Microarchitecture, IDF

- Core, Justin Rattner Senior Fellow, Chief Technology Officer, IDF

Facts about "Core - Microarchitectures - Intel"

| codename | Core + |

| designer | Intel + |

| first launched | April 2006 + |

| full page name | intel/microarchitectures/core (client) + |

| instance of | microarchitecture + |

| instruction set architecture | x86-64 + |

| manufacturer | Intel + |

| microarchitecture type | CPU + |

| name | Core + |

| phase-out | May 2009 + |

| process | 65 nm (0.065 μm, 6.5e-5 mm) + |