(.j) |

|||

| (19 intermediate revisions by 11 users not shown) | |||

| Line 1: | Line 1: | ||

| − | {{amd title|Socket AM4}}[[File:socket am4.svg|300px|right]] | + | {{amd title|Socket AM4}} |

| − | ''' | + | {{package |

| + | |name=Socket AM4 | ||

| + | |designer=AMD | ||

| + | |first launched=September 2016 | ||

| + | |market=Desktop | ||

| + | |microarch=Zen | ||

| + | |tdp=105 W | ||

| + | |package name=OPGA-1331 | ||

| + | |package type=Organic Micro Pin Grid Array | ||

| + | |package contacts=1331 | ||

| + | |package dimension=40 mm | ||

| + | |package dimension 2=40 mm | ||

| + | |package pitch=1 mm | ||

| + | |socket name=Socket AM4 | ||

| + | |socket type=PGA | ||

| + | |predecessor=Socket FM2+ | ||

| + | |predecessor link=amd/packages/socket fm2+ | ||

| + | |predecessor 2=Socket AM3+ | ||

| + | |predecessor 2 link=amd/packages/socket am3+ | ||

| + | |successor=Socket AM5 | ||

| + | |successor link=amd/packages/socket am5 | ||

| + | }} | ||

| + | '''AM4''' is a socket for [[AMD]]'s mainstream series of microprocessors, serving as a successor to {{\\|Socket FM2+}} and {{\\|Socket AM3+}}. It was superseded by {{\\|Socket AM5}}. | ||

| + | |||

| + | == Overview == | ||

| + | <!-- [[File:socket am4.svg|300px|right]] --> | ||

| + | Launching in September 2016, the '''AM4''' replaces a number of older AMD sockets including the {{\\|Socket FM2+}} and {{\\|Socket AM3+}} designed to unify all its mainstream processors from the low-end to the high-end in a single socket. At the time AMD stated the socket will feature prolong comparability life. | ||

| + | |||

| + | The AM4 accepts zero-insertion force '''µOPGA-1331'''-packaged microprocessors designed based on the {{amd|Excavator|l=arch}}, {{amd|Zen|l=arch}}, {{amd|Zen+|l=arch}}, {{amd|Zen 2|l=arch}}, and {{amd|Zen 3|l=arch}} microarchitectures, although the exact chips supported depends on the accompanying chipset. | ||

== Chipsets == | == Chipsets == | ||

{{amd socket am4 chipsets}} | {{amd socket am4 chipsets}} | ||

| + | |||

| + | === Support === | ||

| + | AM4 socket support for a particular microprocessor depends on the chipset compatibility. | ||

| + | |||

| + | {| class="wikitable" | ||

| + | ! colspan="8" | Socket AM4 Processor Support | ||

| + | |- | ||

| + | ! rowspan="2" | Chipset !! colspan="2" | {{amd|Zen|l=arch}} !! colspan="2" | {{amd|Zen+|l=arch}} || colspan="2" | {{amd|Zen 2|l=arch}} || {{amd|Zen 3|l=arch}} | ||

| + | |- | ||

| + | | '''Summit Ridge''' || '''Raven Ridge'''|| '''Pinnacle Ridge''' || '''Picasso'''|| '''Matisse'''|| '''Renoir'''|| '''Vermeer''' | ||

| + | |- | ||

| + | | A320 || colspan="4" {{tchk|yes}} ||* | ||

| + | |- | ||

| + | | A520 || colspan="4" {{tchk|no}} || colspan="3" {{tchk|yes}} | ||

| + | |- | ||

| + | | B350 || colspan="4" {{tchk|yes}} || * | ||

| + | |- | ||

| + | | B450 || colspan="6" {{tchk|yes}} || * | ||

| + | |- | ||

| + | | B550 || colspan="4" {{tchk|no}} || colspan="3" {{tchk|yes}} | ||

| + | |- | ||

| + | | X370 || colspan="4" {{tchk|yes}} || * | ||

| + | |- | ||

| + | | X470 || colspan="6" {{tchk|yes}} || * | ||

| + | |- | ||

| + | | X570 || colspan="2" {{tchk|no}} || colspan="5" {{tchk|yes}} | ||

| + | |} | ||

| + | * - Selective Beta BIOS update required | ||

== Processors using Socket AM4 == | == Processors using Socket AM4 == | ||

| − | <!-- NOTE: | + | <!-- NOTE: |

This table is generated automatically from the data in the actual articles. | This table is generated automatically from the data in the actual articles. | ||

If a microprocessor is missing from the list, an appropriate article for it needs to be | If a microprocessor is missing from the list, an appropriate article for it needs to be | ||

| Line 39: | Line 95: | ||

</table> | </table> | ||

{{comp table end}} | {{comp table end}} | ||

| + | |||

| + | == Photos == | ||

| + | <gallery widths="400px" heights="400px"> | ||

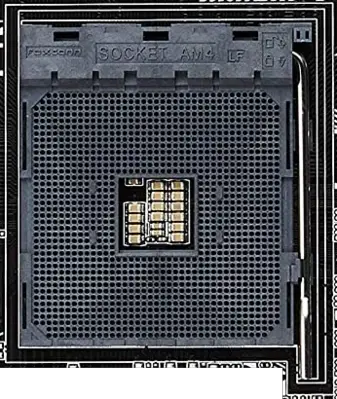

| + | File:socket mb am4.png|Socket AM4 | ||

| + | </gallery> | ||

| + | |||

| + | == Package Diagrams == | ||

| + | [[File:OPGA-1331 SR diag.svg]] | ||

| + | |||

| + | Approximate dimensions of the "{{amd|Summit Ridge|l=core}}" (≤ 8C, Zen, 14 nm, Feb. 2017) and "{{amd|Pinnacle Ridge|l=core}}" (≤ 8C, Zen+, 12 nm, April 2018) package. All dimensions in millimeters. | ||

| + | |||

| + | [[File:OPGA-1331 RR diag.svg]] | ||

| + | |||

| + | Approximate dimensions of the "{{amd|Raven Ridge|l=core}}" desktop package (≤ 4C/11CU, Zen, 14 nm, Oct. 2017). Mobile and embedded versions are available in a {{\\|FP5}} package. All dimensions in millimeters. | ||

| + | |||

| + | [[File:OPGA-1331 MTS diag.svg]] | ||

| + | |||

| + | Approximate dimensions of the "{{amd|Matisse|l=core}}" package (≤ 16C, Zen 2, 7/14 nm, July 2019). The left CCD is unpopulated in ≤ 8C models. All dimensions in millimeters. | ||

| + | |||

| + | == Socket Diagrams == | ||

| + | [[File:Socket AM4 FIT diag.svg]] | ||

| + | |||

| + | No data available. The diagram shows the dimensions of Foxconn Interconnect Technology Part No. PZ1331A-51ZZ*-1H. All dimensions in millimeters. | ||

| + | |||

| + | Socket drawing: https://www.fit-foxconn.com/Product/FileDownload?file=spec&path=%2FImages%2FProducts%2FSpec%2FPZ1331A-51ZZ0-1H_20181218103237.pdf&fileName=PZ1331A-51ZZ0-1H_20181218103237&fileType=pdf&fileClassID=2&productClass=Socket&productFamily=CPU%20Socket&productSeries=PGA%2FBGA&productNo=PZ1331A-51ZZ0-1H&version=7 | ||

| + | |||

| + | == Pin Map == | ||

| + | [[File:OPGA-1331 pinmap.svg|800px]] | ||

| + | |||

| + | AM4 pinout, top view. Click to flip and rotate. | ||

| + | |||

| + | <!-- | ||

| + | 48M_OSC,AR7,MA_DATA[15],F24,MB_DATA[34],AN36,P_ZVDDP,W8,VDDCR_CPU,AB9,VDDIO_MEM_S3,P29,VSS,G33,VSS,AF8 | ||

| + | AGPIO3,AT6,MA_DATA[16],J26,MB_DATA[35],AN39,P_ZVSS,W7,VDDCR_CPU,AB11,VDDIO_MEM_S3,P32,VSS,G35,VSS,AF10 | ||

| + | AGPIO4,AR6,MA_DATA[17],J27,MB_DATA[36],AK38,RESET_L,B16,VDDCR_CPU,AB13,VDDIO_MEM_S3,P35,VSS,G36,VSS,AF12 | ||

| + | AGPIO5/DEVSLP0,AP22,MA_DATA[18],G28,MB_DATA[37],AK36,RSMRST_L,AP5,VDDCR_CPU,AC2,VDDIO_MEM_S3,P38,VSS,G39,VSS,AF28 | ||

| + | AGPIO6,AN8,MA_DATA[19],H28,MB_DATA[38],AM39,RSVD,A5,VDDCR_CPU,AC10,VDDIO_MEM_S3,R28,VSS,H4,VSS,AF30 | ||

| + | AGPIO8,AP7,MA_DATA[20],H25,MB_DATA[39],AN38,RSVD,D28,VDDCR_CPU,AC12,VDDIO_MEM_S3,R31,VSS,H5,VSS,AG1 | ||

| + | AGPIO9/SGPIO0_DATAOUT,AN2,MA_DATA[21],G25,MB_DATA[40],AR36,RSVD,E19,VDDCR_CPU,AD7,VDDIO_MEM_S3,R34,VSS,H8,VSS,AG4 | ||

| + | AGPIO23/SGPIO0_LOAD,AN3,MA_DATA[22],E28,MB_DATA[41],AR37,RSVD,E22,VDDCR_CPU,AD9,VDDIO_MEM_S3,R37,VSS,H11,VSS,AG8 | ||

| + | AGPIO40/SGPIO0_DATAIN,AR4,MA_DATA[23],H27,MB_DATA[42],AU37,RSVD,E25,VDDCR_CPU,AD11,VDDIO_MEM_S3,T27,VSS,H14,VSS,AG9 | ||

| + | AGPIO86,AW17,MA_DATA[24],F29,MB_DATA[43],AV37,RSVD,G17,VDDCR_CPU,AD13,VDDIO_MEM_S3,T29,VSS,H17,VSS,AG11 | ||

| + | ALERT_L,D16,MA_DATA[25],J30,MB_DATA[44],AP37,RSVD,J36,VDDCR_CPU,AE3,VDDIO_MEM_S3,T33,VSS,H20,VSS,AG13 | ||

| + | AM4R1,AL8,MA_DATA[26],H31,MB_DATA[45],AP38,RSVD,J38,VDDCR_CPU,AE6,VDDIO_MEM_S3,T36,VSS,H23,VSS,AG15 | ||

| + | AZ_BITCLK,AW3,MA_DATA[27],F32,MB_DATA[46],AT36,RSVD,K34,VDDCR_CPU,AE10,VDDIO_MEM_S3,T39,VSS,H26,VSS,AG17 | ||

| + | AZ_RST_L,AU1,MA_DATA[28],J29,MB_DATA[47],AU38,RSVD,K38,VDDCR_CPU,AE12,VDDIO_MEM_S3,U28,VSS,H29,VSS,AG19 | ||

| + | AZ_SDIN0,AV3,MA_DATA[29],G29,MB_DATA[48],AW35,RSVD,R35,VDDCR_CPU,AF2,VDDIO_MEM_S3,U30,VSS,H32,VSS,AG21 | ||

| + | AZ_SDIN1,AU5,MA_DATA[30],E31,MB_DATA[49],AU35,RSVD,AB2,VDDCR_CPU,AF9,VDDIO_MEM_S3,U32,VSS,H35,VSS,AG23 | ||

| + | AZ_SDIN2,AV4,MA_DATA[31],G31,MB_DATA[50],AW32,RSVD,AB37,VDDCR_CPU,AF11,VDDIO_MEM_S3,U35,VSS,H38,VSS,AG25 | ||

| + | AZ_SDOUT,AU4,MA_DATA[32],AH34,MB_DATA[51],AU32,RSVD,AD3,VDDCR_CPU,AF13,VDDIO_MEM_S3,U38,VSS,J1,VSS,AG27 | ||

| + | AZ_SYNC,AU2,MA_DATA[33],AJ30,MB_DATA[52],AV36,RSVD,AH2,VDDCR_CPU,AG7,VDDIO_MEM_S3,V27,VSS,J4,VSS,AG28 | ||

| + | BLINK/AGPIO11,AT5,MA_DATA[34],AK30,MB_DATA[53],AW36,RSVD,AH35,VDDCR_CPU,AG10,VDDIO_MEM_S3,V29,VSS,J8,VSS,AG29 | ||

| + | CLK_REQ0_L/SATA_IS0_L/SATA_ZP0_L/AGPIO92,AT23,MA_DATA[35],AL34,MB_DATA[54],AW33,RSVD,AK34,VDDCR_CPU,AG12,VDDIO_MEM_S3,V31,VSS,J9,VSS,AG30 | ||

| + | CLK_REQ1_L/AGPIO115,AV24,MA_DATA[36],AH31,MB_DATA[55],AV33,RSVD,AL16,VDDCR_CPU,AG14,VDDIO_MEM_S3,V34,VSS,J11,VSS,AG31 | ||

| + | CLK_REQ2_L/AGPIO116,AT24,MA_DATA[37],AH32,MB_DATA[56],AW30,RSVD,AL17,VDDCR_CPU,AG16,VDDIO_MEM_S3,V37,VSS,J13,VSS,AG32 | ||

| + | CLK_REQ3_L/SATA_IS1_L/SATA_ZP1_L/EGPIO131,AL23,MA_DATA[38],AK33,MB_DATA[57],AV30,RSVD,AL18,VDDCR_CPU,AG18,VDDIO_MEM_S3,W28,VSS,J15,VSS,AH10 | ||

| + | CLK_REQG_L/OSCIN/EGPIO132,AR22,MA_DATA[39],AK32,MB_DATA[58],AW27,RSVD,AL19,VDDCR_CPU,AG20,VDDIO_MEM_S3,W33,VSS,J17,VSS,AH12 | ||

| + | CORETYPE[0],AM24,MA_DATA[40],AM34,MB_DATA[59],AW26,RSVD,AL20,VDDCR_CPU,AG22,VDDIO_MEM_S3,W34,VSS,J19,VSS,AH14 | ||

| + | CORETYPE[1],AN9,MA_DATA[41],AM33,MB_DATA[60],AV31,RSVD,AL21,VDDCR_CPU,AG24,VDDIO_MEM_S3,W36,VSS,J22,VSS,AH16 | ||

| + | DBRDY,E13,MA_DATA[42],AP31,MB_DATA[61],AU31,RSVD,AM12,VDDCR_CPU,AG26,VDDIO_MEM_S3,W39,VSS,J25,VSS,AH18 | ||

| + | DBREQ_L,D14,MA_DATA[43],AR33,MB_DATA[62],AV28,RSVD,AM16,VDDCR_CPU,AH3,VDDIO_MEM_S3,Y27,VSS,J28,VSS,AH20 | ||

| + | DP0_AUXN,H10,MA_DATA[44],AL32,MB_DATA[63],AV27,RSVD,AM17,VDDCR_CPU,AH6,VDDIO_MEM_S3,Y29,VSS,J31,VSS,AH22 | ||

| + | DP0_AUXP,G10,MA_DATA[45],AL31,MB_DM[0],C21,RSVD,AM21,VDDCR_CPU,AH9,VDDIO_MEM_S3,Y31,VSS,J34,VSS,AH24 | ||

| + | DP0_HPD,H9,MA_DATA[46],AP34,MB_DM[1],D26,RSVD,AN12,VDDCR_CPU,AH11,VDDIO_MEM_S3,Y32,VSS,J35,VSS,AH26 | ||

| + | DP0_TXN[0],C2,MA_DATA[47],AP32,MB_DM[2],A32,RSVD,AN15,VDDCR_CPU,AH13,VDDIO_MEM_S3,Y35,VSS,J37,VSS,AH28 | ||

| + | DP0_TXN[1],B3,MA_DATA[48],AR31,MB_DM[3],D37,RSVD,AN16,VDDCR_CPU,AH15,VDDIO_MEM_S3,Y38,VSS,K10,VSS,AH29 | ||

| + | DP0_TXN[2],A4,MA_DATA[49],AK29,MB_DM[4],AL38,RSVD,AN17,VDDCR_CPU,AH17,VDDIO_MEM_S3,AA28,VSS,K12,VSS,AH30 | ||

| + | DP0_TXN[3],C6,MA_DATA[50],AM28,MB_DM[5],AR39,RSVD,AN21,VDDCR_CPU,AH19,VDDIO_MEM_S3,AA34,VSS,K18,VSS,AH33 | ||

| + | DP0_TXP[0],D2,MA_DATA[51],AL28,MB_DM[6],AT35,RSVD,AP15,VDDCR_CPU,AH21,VDDIO_MEM_S3,AA37,VSS,K20,VSS,AJ5 | ||

| + | DP0_TXP[1],C3,MA_DATA[52],AM30,MB_DM[7],AW29,RSVD,AP16,VDDCR_CPU,AH23,VDDIO_MEM_S3,AB27,VSS,K21,VSS,AJ8 | ||

| + | DP0_TXP[2],B4,MA_DATA[53],AN30,MB_DM[8],F39,RSVD,AP17,VDDCR_CPU,AH25,VDDIO_MEM_S3,AB29,VSS,K22,VSS,AJ9 | ||

| + | DP0_TXP[3],C5,MA_DATA[54],AP28,MB_DQS_H[0],B22,RSVD,AP21,VDDCR_CPU,AH27,VDDIO_MEM_S3,AB31,VSS,K23,VSS,AJ11 | ||

| + | DP1_AUXN,G11,MA_DATA[55],AR28,MB_DQS_H[1],C27,RSVD,AR15,VDDCR_CPU,AJ2,VDDIO_MEM_S3,AB32,VSS,K26,VSS,AJ13 | ||

| + | DP1_AUXP,F11,MA_DATA[56],AK27,MB_DQS_H[2],C33,RSVD,AR16,VDDCR_CPU,AJ10,VDDIO_MEM_S3,AB33,VSS,K27,VSS,AJ23 | ||

| + | DP1_HPD,D10,MA_DATA[57],AK26,MB_DQS_H[3],B37,RSVD,AR18,VDDCR_CPU,AJ12,VDDIO_MEM_S3,AB36,VSS,K28,VSS,AJ25 | ||

| + | DP1_TXN[0],D5,MA_DATA[58],AP25,MB_DQS_H[4],AM37,RSVD,AR19,VDDCR_CPU,AJ14,VDDIO_MEM_S3,AB39,VSS,K29,VSS,AJ26 | ||

| + | DP1_TXN[1],D8,MA_DATA[59],AR25,MB_DQS_H[5],AT38,RSVD,AR20,VDDCR_CPU,AJ22,VDDIO_MEM_S3,AC28,VSS,K30,VSS,AJ27 | ||

| + | DP1_TXN[2],G8,MA_DATA[60],AN27,MB_DQS_H[6],AU34,RSVD,AR21,VDDCR_CPU,AJ24,VDDIO_MEM_S3,AC30,VSS,K33,VSS,AJ28 | ||

| + | DP1_TXN[3],F9,MA_DATA[61],AM27,MB_DQS_H[7],AU28,RSVD,AR24,VDDCR_CPU,AK7,VDDIO_MEM_S3,AC32,VSS,L4,VSS,AJ29 | ||

| + | DP1_TXP[0],D4,MA_DATA[62],AL25,MB_DQS_H[8],G38,RSVD,AT19,VDDCR_CPU,AK9,VDDIO_MEM_S3,AC35,VSS,L5,VSS,AJ32 | ||

| + | DP1_TXP[1],D7,MA_DATA[63],AM25,MB_DQS_L[0],A22,RSVD,AT25,VDDCR_CPU,AK11,VDDIO_MEM_S3,AC38,VSS,L8,VSS,AJ35 | ||

| + | DP1_TXP[2],F8,MA_DM[0],K19,MB_DQS_L[1],B27,RSVD,AT30,VDDCR_CPU,AK13,VDDIO_MEM_S3,AD27,VSS,L9,VSS,AJ36 | ||

| + | DP1_TXP[3],E9,MA_DM[1],J23,MB_DQS_L[2],C32,RSVD,AW24,VDDCR_CPU,AL3,VDDIO_MEM_S3,AD29,VSS,L11,VSS,AJ38 | ||

| + | DP2_AUXN,A11,MA_DM[2],G26,MB_DQS_L[3],A37,RTCCLK,AP8,VDDCR_CPU,AL6,VDDIO_MEM_S3,AD31,VSS,L13,VSS,AK1 | ||

| + | DP2_AUXP,A10,MA_DM[3],H30,MB_DQS_L[4],AM36,S0A3_GPIO/AGPIO10/SGPIO0_CLK,AR3,VDDCR_CPU,AL10,VDDIO_MEM_S3,AD34,VSS,L15,VSS,AK4 | ||

| + | DP2_HPD,E10,MA_DM[4],AJ31,MB_DQS_L[5],AT39,S5_MUX_CTRL/EGPIO42,AP4,VDDCR_CPU,AL12,VDDIO_MEM_S3,AD37,VSS,L17,VSS,AK10 | ||

| + | DP2_TXN[0],B7,MA_DM[5],AM31,MB_DQS_L[6],AV34,SATA_ACT_L/AGPIO130,AM22,VDDCR_CPU,AL14,VDDIO_MEM_S3,AE28,VSS,L19,VSS,AK12 | ||

| + | DP2_TXN[1],A8,MA_DM[6],AL29,MB_DQS_L[7],AU29,SATA_ZVDDP,AV7,VDDCR_CPU,AM2,VDDIO_MEM_S3,AE30,VSS,L21,VSS,AK14 | ||

| + | DP2_TXN[2],C9,MA_DM[7],AL26,MB_DQS_L[8],G37,SATA_ZVSS,AV6,VDDCR_CPU,AM8,VDDIO_MEM_S3,AE33,VSS,L25,VSS,AK22 | ||

| + | DP2_TXN[3],B10,MA_DM[8],G34,MB_EVENT_L,AA38,SCL0/I2C2_SCL/EGPIO113,AU25,VDDCR_CPU,AN7,VDDIO_MEM_S3,AE36,VSS,L27,VSS,AK25 | ||

| + | DP2_TXP[0],B6,MA_DQS_H[0],H19,MB_PAROUT,AB38,SCL1/I2C3_SCL/AGPIO19,AK3,VDDCR_CPU,AN10,VDDIO_MEM_S3,AE39,VSS,L28,VSS,AK28 | ||

| + | DP2_TXP[1],A7,MA_DQS_H[1],F23,MB_RAS_L_ADD[16],AD36,SDA0/I2C2_SDA/EGPIO114,AV25,VDDCR_CPU,AN13,VDDIO_MEM_S3,AF27,VSS,L29,VSS,AK31 | ||

| + | DP2_TXP[2],C8,MA_DQS_H[2],F27,MB_RESET_L,K35,SDA1/I2C3_SDA/AGPIO20,AK2,VDDCR_CPU,AP3,VDDIO_MEM_S3,AF29,VSS,L30,VSS,AK35 | ||

| + | DP2_TXP[3],B9,MA_DQS_H[3],F30,MB_WE_L_ADD[14],AD39,SERIRQ/AGPIO87,AW21,VDDCR_CPU,AP9,VDDIO_MEM_S3,AF32,VSS,L31,VSS,AK37 | ||

| + | DP_AUX_ZVSS,E12,MA_DQS_H[4],AJ33,MB_ZVDDIO_MEM_S3,Y36,SIC,B18,VDDCR_CPU,AP12,VDDIO_MEM_S3,AF35,VSS,M1,VSS,AL9 | ||

| + | DP_BLON,G13,MA_DQS_H[5],AN32,MB_ZVSS,AJ39,SID,C18,VDDCR_CPU,AR2,VDDIO_MEM_S3,AF38,VSS,M4,VSS,AL11 | ||

| + | DP_DIGON,H13,MA_DQS_H[6],AP29,P0A_ZVSS,V8,SLP_S3_L,AT2,VDDCR_CPU,AT4,VDDIO_MEM_S3,AG33,VSS,M8,VSS,AL24 | ||

| + | DP_STEREOSYNC,K14,MA_DQS_H[7],AP26,P0B_ZVSS,AT8,SLP_S5_L,AP2,VDDCR_CPU,AU3,VDDIO_MEM_S3,AG34,VSS,M10,VSS,AL27 | ||

| + | DP_VARY_BL,H12,MA_DQS_H[8],H34,PCIE_RST_L/EGPIO26,AL7,SPI_CLK/ESPI_CLK/EGPIO117,AW14,VDDCR_CPU,AU6,VDDIO_MEM_S3,AG35,VSS,M12,VSS,AL30 | ||

| + | DP_ZVSS,F12,MA_DQS_L[0],G19,PROCHOT_L,H15,SPI_CS1_L/EGPIO118,AT17,VDDCR_CPU,AU9,VDDIO_MEM_S3,AG37,VSS,M14,VSS,AL33 | ||

| + | EGPIO70,AT18,MA_DQS_L[1],G23,PWROK,E16,SPI_CS2_L/ESPI_CS_L/EGPIO119,AW15,VDDCR_CPU,AU12,VDDIO_MEM_S3,AH39,VSS,M16,VSS,AL35 | ||

| + | EGPIO95,AW11,MA_DQS_L[2],F26,PWR_BTN_L/AGPIO0,AN5,SPI_DI/ESPI_DAT1/EGPIO120,AU14,VDDCR_CPU,AU15,VDDIO_MEM_S3_SENSE,G14,VSS,M18,VSS,AL36 | ||

| + | EGPIO96,AV12,MA_DQS_L[3],E30,PWR_GOOD,AM3,SPI_DO/ESPI_DAT0/EGPIO121,AU16,VDDCR_CPU,AV5,VDDP,AM18,VSS,M20,VSS,AL39 | ||

| + | EGPIO97,AW12,MA_DQS_L[4],AJ34,P_GFX_RXN[0],F5,SPI_HOLD_L/ESPI_DAT3/EGPIO133,AV15,VDDCR_CPU,AV8,VDDP,AM19,VSS,M24,VSS,AM5 | ||

| + | EGPIO98,AU13,MA_DQS_L[5],AN33,P_GFX_RXN[1],G4,SPI_TPM_CS_L/AGPIO76,AU17,VDDCR_CPU,AV11,VDDP,AM20,VSS,M26,VSS,AM11 | ||

| + | EGPIO99,AV13,MA_DQS_L[6],AN29,P_GFX_RXN[2],H6,SPI_WP_L/ESPI_DAT2/EGPIO122,AV16,VDDCR_CPU,AV14,VDDP,AN18,VSS,M27,VSS,AM14 | ||

| + | EGPIO100,AT14,MA_DQS_L[7],AN26,P_GFX_RXN[3],J5,SPKR/AGPIO91,AW23,VDDCR_CPU_SENSE,F14,VDDP,AN19,VSS,M28,VSS,AM26 | ||

| + | ESPI_ALERT_L/LDRQ0_L/EGPIO108,AT15,MA_DQS_L[8],H33,P_GFX_RXN[4],K7,SVC,D17,VDDCR_SOC,B5,VDDP,AN20,VSS,N9,VSS,AM29 | ||

| + | ESPI_RESET_L/KBRST_L,AN24,MA_EVENT_L,W35,P_GFX_RXN[5],K4,SVD,C17,VDDCR_SOC,B8,VDDP,AP18,VSS,N11,VSS,AM32 | ||

| + | FANIN0/AGPIO84,AN23,MA_PAROUT,Y33,P_GFX_RXN[6],L6,SVT,A17,VDDCR_SOC,B11,VDDP,AP19,VSS,N13,VSS,AM35 | ||

| + | FANOUT0/AGPIO85,AP23,MA_RAS_L_ADD[16],AB34,P_GFX_RXN[7],M5,SYS_RESET_L/AGPIO1,AM4,VDDCR_SOC,B14,VDDP,AP20,VSS,N15,VSS,AM38 | ||

| + | GENINT1_L/AGPIO89,AV22,MA_RESET_L,L33,P_GFX_RXN[8],N7,TCK,C15,VDDCR_SOC,B17,VDDP_S5,AJ16,VSS,N17,VSS,AN1 | ||

| + | GENINT2_L/AGPIO90,AU23,MA_WE_L_ADD[14],AB35,P_GFX_RXN[9],N4,TDI,A14,VDDCR_SOC,B20,VDDP_S5,AJ17,VSS,N19,VSS,AN4 | ||

| + | GFX_CLKN,AF7,MA_ZVDDIO_MEM_S3,Y34,P_GFX_RXN[10],P6,TDO,C14,VDDCR_SOC,C4,VDDP_SENSE,AL22,VSS,N21,VSS,AN22 | ||

| + | GFX_CLKP,AF6,MA_ZVSS,AJ37,P_GFX_RXN[11],R5,TEST0,AM6,VDDCR_SOC,C7,VDD_18,AJ20,VSS,N23,VSS,AN25 | ||

| + | GPP_CLK0N,AG6,MB0_CKE[0],L37,P_GFX_RXN[12],T7,TEST1/TMS,AM7,VDDCR_SOC,C10,VDD_18,AK20,VSS,N25,VSS,AN28 | ||

| + | GPP_CLK0P,AG5,MB0_CKE[1],K37,P_GFX_RXN[13],T5,TEST2,AT3,VDDCR_SOC,C13,VDD_18_S5,AJ15,VSS,N27,VSS,AN31 | ||

| + | GPP_CLK1N,AH5,MB0_CS_L[0],AE37,P_GFX_RXN[14],U6,TEST4,L23,VDDCR_SOC,C16,VDD_18_S5,AK15,VSS,N29,VSS,AN34 | ||

| + | GPP_CLK1P,AH4,MB0_CS_L[1],AG39,P_GFX_RXN[15],V5,TEST5,M22,VDDCR_SOC,C19,VDD_33,AJ21,VSS,P4,VSS,AN35 | ||

| + | GPP_CLK2N,AH8,MB0_ODT[0],AF39,P_GFX_RXP[0],F6,TEST6,D13,VDDCR_SOC,D3,VDD_33,AK21,VSS,P5,VSS,AN37 | ||

| + | GPP_CLK2P,AH7,MB0_ODT[1],AH36,P_GFX_RXP[1],G5,TEST10,AB4,VDDCR_SOC,E2,VDD_33_S5,AJ19,VSS,P8,VSS,AP6 | ||

| + | GPP_CLK3N,AJ7,MB1_CKE[0],L39,P_GFX_RXP[2],H7,TEST11,A13,VDDCR_SOC,F7,VDD_33_S5,AK19,VSS,P10,VSS,AP24 | ||

| + | GPP_CLK3P,AJ6,MB1_CKE[1],L36,P_GFX_RXP[3],J6,TEST14,C12,VDDCR_SOC,F10,VSS,A3,VSS,P12,VSS,AP27 | ||

| + | LAD0/EGPIO104,AW20,MB1_CS_L[0],AE38,P_GFX_RXP[4],K8,TEST15,B12,VDDCR_SOC,F13,VSS,A6,VSS,R1,VSS,AP30 | ||

| + | LAD1/EGPIO105,AV21,MB1_CS_L[1],AG36,P_GFX_RXP[5],K5,TEST16,C11,VDDCR_SOC,F16,VSS,A9,VSS,R4,VSS,AP33 | ||

| + | LAD2/EGPIO106,AT21,MB1_ODT[0],AF37,P_GFX_RXP[6],L7,TEST17,D11,VDDCR_SOC,G3,VSS,A12,VSS,R8,VSS,AP35 | ||

| + | LAD3/EGPIO107,AT20,MB1_ODT[1],AH38,P_GFX_RXP[7],M6,TEST18,G16,VDDCR_SOC,G6,VSS,A15,VSS,R9,VSS,AP36 | ||

| + | LFRAME_L/EGPIO109,AW18,MB_ACT_L,M38,P_GFX_RXP[8],N8,TEST19,H16,VDDCR_SOC,G9,VSS,A18,VSS,R11,VSS,AP39 | ||

| + | LPCCLK0/EGPIO74,AU20,MB_ADD[0],AC36,P_GFX_RXP[9],N5,TEST28_H,E6,VDDCR_SOC,G12,VSS,A21,VSS,R13,VSS,AR5 | ||

| + | LPCCLK1/EGPIO75,AU19,MB_ADD[1],U36,P_GFX_RXP[10],P7,TEST28_L,E7,VDDCR_SOC,G15,VSS,A24,VSS,R27,VSS,AR8 | ||

| + | LPC_CLKRUN_L/AGPIO88,AV19,MB_ADD[2],U37,P_GFX_RXP[11],R6,TEST31,AA30,VDDCR_SOC,G18,VSS,A27,VSS,R29,VSS,AR11 | ||

| + | LPC_PD_L/AGPIO21,AV18,MB_ADD[3],T38,P_GFX_RXP[12],T8,TEST40,W30,VDDCR_SOC,H2,VSS,A30,VSS,T10,VSS,AR14 | ||

| + | LPC_PME_L/AGPIO22,AL2,MB_ADD[4],T37,P_GFX_RXP[13],T4,TEST41,A16,VDDCR_SOC,J7,VSS,A33,VSS,T12,VSS,AR17 | ||

| + | LPC_RST_L,AU22,MB_ADD[5],R39,P_GFX_RXP[14],U7,TEST46[13],AL4,VDDCR_SOC,J10,VSS,A36,VSS,T28,VSS,AR23 | ||

| + | MA0_CKE[0],M32,MB_ADD[6],R36,P_GFX_RXP[15],V6,TEST47,P28,VDDCR_SOC,J12,VSS,B19,VSS,T30,VSS,AR26 | ||

| + | MA0_CKE[1],M30,MB_ADD[7],P39,P_GFX_TXN[0],E1,THERMTRIP_L,A19,VDDCR_SOC,J14,VSS,B23,VSS,U4,VSS,AR27 | ||

| + | MA0_CS_L[0],AC33,MB_ADD[8],R38,P_GFX_TXN[1],F3,TMS,B15,VDDCR_SOC,J16,VSS,B26,VSS,U5,VSS,AR29 | ||

| + | MA0_CS_L[1],AE35,MB_ADD[9],P36,P_GFX_TXN[2],G2,TRST_L,B13,VDDCR_SOC,K3,VSS,B29,VSS,U8,VSS,AR30 | ||

| + | MA0_ODT[0],AD35,MB_ADD[10],AC39,P_GFX_TXN[3],H1,USB0_ZVSS,AJ3,VDDCR_SOC,K6,VSS,B32,VSS,U9,VSS,AR32 | ||

| + | MA0_ODT[1],AF31,MB_ADD[11],P37,P_GFX_TXN[4],J3,USB1_ZVSS,AN6,VDDCR_SOC,K9,VSS,B35,VSS,U11,VSS,AR34 | ||

| + | MA1_CKE[0],M33,MB_ADD[12],N38,P_GFX_TXN[5],K2,USB2_ZVSS,AK6,VDDCR_SOC,K11,VSS,C1,VSS,U13,VSS,AR35 | ||

| + | MA1_CKE[1],L34,MB_ADD[13],AG38,P_GFX_TXN[6],L1,USB3_ZVSS,AK5,VDDCR_SOC,K13,VSS,C22,VSS,U27,VSS,AR38 | ||

| + | MA1_CS_L[0],AC34,MB_ADD_17,AH37,P_GFX_TXN[7],M3,USB_HSD0N,AU8,VDDCR_SOC,K15,VSS,C25,VSS,U29,VSS,AT1 | ||

| + | MA1_CS_L[1],AE34,MB_ALERT_L,N37,P_GFX_TXN[8],N2,USB_HSD0P,AU7,VDDCR_SOC,L2,VSS,C28,VSS,U31,VSS,AT7 | ||

| + | MA1_ODT[0],AD33,MB_BANK[0],AD38,P_GFX_TXN[9],P1,USB_HSD1N,AW9,VDDCR_SOC,L10,VSS,C31,VSS,V1,VSS,AT10 | ||

| + | MA1_ODT[1],AF34,MB_BANK[1],AC37,P_GFX_TXN[10],R3,USB_HSD1P,AW8,VDDCR_SOC,L12,VSS,C34,VSS,V4,VSS,AT13 | ||

| + | MA_ACT_L,M35,MB_BG[0],M36,P_GFX_TXN[11],T2,USB_HSD2N,AU11,VDDCR_SOC,L14,VSS,C37,VSS,V7,VSS,AT16 | ||

| + | MA_ADD[0],AA32,MB_BG[1],M39,P_GFX_TXN[12],U1,USB_HSD2P,AU10,VDDCR_SOC,L16,VSS,D6,VSS,V10,VSS,AT22 | ||

| + | MA_ADD[1],T32,MB_CAS_L_ADD[15],AF36,P_GFX_TXN[13],V3,USB_HSD3N,AV10,VDDCR_SOC,L18,VSS,D9,VSS,V12,VSS,AT26 | ||

| + | MA_ADD[2],T35,MB_CHECK[0],F38,P_GFX_TXN[14],W2,USB_HSD3P,AV9,VDDCR_SOC,L20,VSS,D12,VSS,V28,VSS,AT27 | ||

| + | MA_ADD[3],T31,MB_CHECK[1],F36,P_GFX_TXN[15],Y1,USB_OC0_L/AGPIO16,AL1,VDDCR_SOC,L22,VSS,D15,VSS,V30,VSS,AT28 | ||

| + | MA_ADD[4],R30,MB_CHECK[2],H39,P_GFX_TXP[0],D1,USB_OC1_L/TDI/AGPIO17,AM1,VDDCR_SOC,L24,VSS,D18,VSS,W9,VSS,AT29 | ||

| + | MA_ADD[5],R33,MB_CHECK[3],J39,P_GFX_TXP[1],E3,USB_OC2_L/TCK/AGPIO18,AR1,VDDCR_SOC,L26,VSS,D19,VSS,W11,VSS,AT31 | ||

| + | MA_ADD[6],R32,MB_CHECK[4],E37,P_GFX_TXP[2],F2,USB_OC3_L/TDO/AGPIO24,AP1,VDDCR_SOC,M9,VSS,D21,VSS,W13,VSS,AT32 | ||

| + | MA_ADD[7],P34,MB_CHECK[5],E39,P_GFX_TXP[3],G1,USB_SS_0RXN,Y4,VDDCR_SOC,M11,VSS,D22,VSS,W27,VSS,AT33 | ||

| + | MA_ADD[8],P30,MB_CHECK[6],H36,P_GFX_TXP[4],H3,USB_SS_0RXP,Y3,VDDCR_SOC,M13,VSS,D23,VSS,W29,VSS,AT34 | ||

| + | MA_ADD[9],P31,MB_CHECK[7],H37,P_GFX_TXP[5],J2,USB_SS_0TXN,AF4,VDDCR_SOC,M15,VSS,D24,VSS,W31,VSS,AT37 | ||

| + | MA_ADD[10],AA36,MB_CLK_H[0],U39,P_GFX_TXP[6],K1,USB_SS_0TXP,AF3,VDDCR_SOC,M17,VSS,D25,VSS,Y5,VSS,AU18 | ||

| + | MA_ADD[11],P33,MB_CLK_H[1],V38,P_GFX_TXP[7],L3,USB_SS_1RXN,AA3,VDDCR_SOC,M19,VSS,D27,VSS,Y8,VSS,AU21 | ||

| + | MA_ADD[12],N35,MB_CLK_H[2],W37,P_GFX_TXP[8],M2,USB_SS_1RXP,AA2,VDDCR_SOC,M21,VSS,D29,VSS,Y10,VSS,AU24 | ||

| + | MA_ADD[13],AE32,MB_CLK_H[3],Y39,P_GFX_TXP[9],N1,USB_SS_1TXN,AC1,VDDCR_SOC,M23,VSS,D30,VSS,Y12,VSS,AU26 | ||

| + | MA_ADD_17,AF33,MB_CLK_L[0],V39,P_GFX_TXP[10],P3,USB_SS_1TXP,AB1,VDDCR_SOC,M25,VSS,D31,VSS,Y28,VSS,AU27 | ||

| + | MA_ALERT_L,N34,MB_CLK_L[1],W38,P_GFX_TXP[11],R2,USB_SS_2RXN,AE2,VDDCR_SOC,N10,VSS,D32,VSS,Y30,VSS,AU30 | ||

| + | MA_BANK[0],AA35,MB_CLK_L[2],Y37,P_GFX_TXP[12],T1,USB_SS_2RXP,AD2,VDDCR_SOC,N12,VSS,D33,VSS,AA1,VSS,AU33 | ||

| + | MA_BANK[1],AA33,MB_CLK_L[3],AA39,P_GFX_TXP[13],U3,USB_SS_2TXN,AC4,VDDCR_SOC,N14,VSS,D34,VSS,AA4,VSS,AU36 | ||

| + | MA_BG[0],N31,MB_DATA[0],D20,P_GFX_TXP[14],V2,USB_SS_2TXP,AC3,VDDCR_SOC,N16,VSS,D35,VSS,AA6,VSS,AU39 | ||

| + | MA_BG[1],N32,MB_DATA[1],B21,P_GFX_TXP[15],W1,USB_SS_3RXN,AF1,VDDCR_SOC,N18,VSS,D36,VSS,AA9,VSS,AV2 | ||

| + | MA_CAS_L_ADD[15],AD32,MB_DATA[2],B24,P_GPP_RXN[0],AT9,USB_SS_3RXP,AE1,VDDCR_SOC,N20,VSS,D39,VSS,AA11,VSS,AV17 | ||

| + | MA_CHECK[0],F33,MB_DATA[3],C24,P_GPP_RXN[1],AM10,USB_SS_3TXN,AG3,VDDCR_SOC,N22,VSS,E4,VSS,AA13,VSS,AV20 | ||

| + | MA_CHECK[1],G32,MB_DATA[4],A20,P_GPP_RXN[2]/SATA_RX0N,AP10,USB_SS_3TXP,AG2,VDDCR_SOC,N24,VSS,E5,VSS,AA27,VSS,AV23 | ||

| + | MA_CHECK[2],K31,MB_DATA[5],C20,P_GPP_RXN[3]/SATA_RX1N,AN11,USB_SS_ZVDDP,AK8,VDDCR_SOC,N26,VSS,E8,VSS,AA29,VSS,AV26 | ||

| + | MA_CHECK[3],K32,MB_DATA[6],A23,P_GPP_RXP[0],AR9,USB_SS_ZVSS,AJ4,VDDCR_SOC,P9,VSS,E11,VSS,AA31,VSS,AV29 | ||

| + | MA_CHECK[4],E33,MB_DATA[7],C23,P_GPP_RXP[1],AM9,USB_ZVSS,AT11,VDDCR_SOC,P11,VSS,E14,VSS,AB7,VSS,AV32 | ||

| + | MA_CHECK[5],E34,MB_DATA[8],A26,P_GPP_RXP[2]/SATA_RX0P,AR10,VDDBT_RTC_G,AL15,VDDCR_SOC,P13,VSS,E17,VSS,AB10,VSS,AV35 | ||

| + | MA_CHECK[6],J32,MB_DATA[9],C26,P_GPP_RXP[3]/SATA_RX1P,AP11,VDDCR_CPU,M7,VDDCR_SOC,R10,VSS,E20,VSS,AB12,VSS,AV38 | ||

| + | MA_CHECK[7],J33,MB_DATA[10],A29,P_GPP_TXN[0],AR12,VDDCR_CPU,N3,VDDCR_SOC,R12,VSS,E21,VSS,AB28,VSS,AW4 | ||

| + | MA_CLK_H[0],T34,MB_DATA[11],C29,P_GPP_TXN[1],AR13,VDDCR_CPU,N6,VDDCR_SOC,T11,VSS,E23,VSS,AB30,VSS,AW7 | ||

| + | MA_CLK_H[1],U33,MB_DATA[12],A25,P_GPP_TXN[2]/SATA_TX0N,AM13,VDDCR_CPU,P2,VDDCR_SOC,T13,VSS,E26,VSS,AC5,VSS,AW10 | ||

| + | MA_CLK_H[2],V35,MB_DATA[13],B25,P_GPP_TXN[3]/SATA_TX1N,AP14,VDDCR_CPU,R7,VDDCR_SOC,U12,VSS,E27,VSS,AC8,VSS,AW13 | ||

| + | MA_CLK_H[3],V32,MB_DATA[14],A28,P_GPP_TXP[0],AT12,VDDCR_CPU,T3,VDDCR_SOC,V13,VSS,E29,VSS,AC9,VSS,AW16 | ||

| + | MA_CLK_L[0],U34,MB_DATA[15],B28,P_GPP_TXP[1],AP13,VDDCR_CPU,T6,VDDCR_SOC_S5,AJ18,VSS,E32,VSS,AC11,VSS,AW19 | ||

| + | MA_CLK_L[1],V33,MB_DATA[16],A31,P_GPP_TXP[2]/SATA_TX0P,AL13,VDDCR_CPU,T9,VDDCR_SOC_S5,AK18,VSS,E35,VSS,AC13,VSS,AW22 | ||

| + | MA_CLK_L[2],V36,MB_DATA[17],B31,P_GPP_TXP[3]/SATA_TX1P,AN14,VDDCR_CPU,U2,VDDCR_SOC_SENSE,E15,VSS,E38,VSS,AC27,VSS,AW25 | ||

| + | MA_CLK_L[3],W32,MB_DATA[18],B34,P_HUB_RXN[0],AD8,VDDCR_CPU,U10,VDDIO_AUDIO,AM15,VSS,F1,VSS,AC29,VSS,AW28 | ||

| + | MA_DATA[0],E18,MB_DATA[19],C35,P_HUB_RXN[1],AA8,VDDCR_CPU,V9,VDDIO_MEM_S3,K36,VSS,F4,VSS,AC31,VSS,AW31 | ||

| + | MA_DATA[1],J18,MB_DATA[20],B30,P_HUB_RXN[2],Y7,VDDCR_CPU,V11,VDDIO_MEM_S3,K39,VSS,F17,VSS,AD1,VSS,AW34 | ||

| + | MA_DATA[2],J20,MB_DATA[21],C30,P_HUB_RXN[3],W5,VDDCR_CPU,W3,VDDIO_MEM_S3,L32,VSS,F19,VSS,AD4,VSS,AW37 | ||

| + | MA_DATA[3],H21,MB_DATA[22],B33,P_HUB_RXP[0],AE8,VDDCR_CPU,W6,VDDIO_MEM_S3,L35,VSS,F22,VSS,AD10,VSS_SENSE_A,F15 | ||

| + | MA_DATA[4],H18,MB_DATA[23],A34,P_HUB_RXP[1],AB8,VDDCR_CPU,W10,VDDIO_MEM_S3,L38,VSS,F25,VSS,AD12,VSS_SENSE_B,AM23 | ||

| + | MA_DATA[5],F18,MB_DATA[24],B36,P_HUB_RXP[2],Y6,VDDCR_CPU,W12,VDDIO_MEM_S3,M29,VSS,F28,VSS,AD28,WAKE_L/AGPIO2,AL5 | ||

| + | MA_DATA[6],G20,MB_DATA[25],E36,P_HUB_RXP[3],W4,VDDCR_CPU,Y2,VDDIO_MEM_S3,M31,VSS,F31,VSS,AD30,X32K_X1,AW5 | ||

| + | MA_DATA[7],F20,MB_DATA[26],C39,P_HUB_TXN[0],AE5,VDDCR_CPU,Y9,VDDIO_MEM_S3,M34,VSS,F34,VSS,AE7,X32K_X2,AW6 | ||

| + | MA_DATA[8],H22,MB_DATA[27],D38,P_HUB_TXN[1],AB5,VDDCR_CPU,Y11,VDDIO_MEM_S3,M37,VSS,F35,VSS,AE9,X48M_X1,AJ1 | ||

| + | MA_DATA[9],G22,MB_DATA[28],A35,P_HUB_TXN[2],AC7,VDDCR_CPU,Y13,VDDIO_MEM_S3,N28,VSS,F37,VSS,AE11,X48M_X2,AH1 | ||

| + | MA_DATA[10],E24,MB_DATA[29],C36,P_HUB_TXN[3],AD6,VDDCR_CPU,AA7,VDDIO_MEM_S3,N30,VSS,G7,VSS,AE13 | ||

| + | MA_DATA[11],J24,MB_DATA[30],B38,P_HUB_TXP[0],AE4,VDDCR_CPU,AA10,VDDIO_MEM_S3,N33,VSS,G21,VSS,AE27 | ||

| + | MA_DATA[12],F21,MB_DATA[31],C38,P_HUB_TXP[1],AA5,VDDCR_CPU,AA12,VDDIO_MEM_S3,N36,VSS,G24,VSS,AE29 | ||

| + | MA_DATA[13],J21,MB_DATA[32],AK39,P_HUB_TXP[2],AC6,VDDCR_CPU,AB3,VDDIO_MEM_S3,N39,VSS,G27,VSS,AE31 | ||

| + | MA_DATA[14],H24,MB_DATA[33],AL37,P_HUB_TXP[3],AD5,VDDCR_CPU,AB6,VDDIO_MEM_S3,P27,VSS,G30,VSS,AF5 | ||

| + | --> | ||

| + | |||

| + | === Pin Description === | ||

| + | {| class="wikitable sortable" | ||

| + | !Signal!!Description | ||

| + | |- | ||

| + | |MA/MB_ACT_L||DRAM Channel A/B Activation Command | ||

| + | |- | ||

| + | |MA/MB_ADD[13:0]||DRAM Column/Row Address | ||

| + | |- | ||

| + | |MA/MB_ADD_17||DRAM Column/Row Address 17 | ||

| + | |- | ||

| + | |MA/MB_ALERT_L||DRAM Alert (CRC error and Command/Address parity error) | ||

| + | |- | ||

| + | |MA/MB_BANK[1:0]||DRAM Bank Address | ||

| + | |- | ||

| + | |MA/MB_BG[1:0]||DRAM Bank Group | ||

| + | |- | ||

| + | |MA/MB_CAS_L_ADD[15]||DRAM Column Address Strobe or Column/Row Address 15 | ||

| + | |- | ||

| + | |MA/MB_CHECK[7:0]||DRAM ECC Check Bits | ||

| + | |- | ||

| + | |MA/MB_DATA[63:0]||DRAM Data Bus | ||

| + | |- | ||

| + | |MA/MB_DM[8:0]||DRAM Data Mask | ||

| + | |- | ||

| + | |MA/MB_DQS_H/L[8:0]||DRAM Differential Data Strobe | ||

| + | |- | ||

| + | |MA/MB_EVENT_L||DRAM Thermal Event Status | ||

| + | |- | ||

| + | |MA/MB_PAROUT||DRAM Command/Address Parity | ||

| + | |- | ||

| + | |MA/MB_RAS_L_ADD[16]||DRAM Row Address Strobe or Column/Row Address 16 | ||

| + | |- | ||

| + | |MA/MB_RESET_L||DRAM Reset | ||

| + | |- | ||

| + | |MA/MB_WE_L_ADD[14]||DRAM Write Enable or Column/Row Address 14 | ||

| + | |- | ||

| + | |MA/MB_ZVDDIO_MEM_S3|| | ||

| + | |- | ||

| + | |MA/MB_ZVSS||DRAM Interface Drive-Strength Auto-Compensation Resistor to VSS | ||

| + | |- | ||

| + | |MA0/MA1/MB0/MB1_CKE[1:0]||DRAM Channel A/B DIMM 0/1 Clock Enable | ||

| + | |- | ||

| + | |MA0/MA1/MB0/MB1_CLK_H/L[3:0]||DRAM Channel A/B DIMM 0/1 Differential Clock | ||

| + | |- | ||

| + | |MA0/MA1/MB0/MB1_CS_L[1:0]||DRAM Channel A/B DIMM 0/1 Chip Select | ||

| + | |- | ||

| + | |MA0/MA1/MB0/MB1_ODT[1:0]||DRAM Channel A/B DIMM 0/1 Enable Pin for On Die Termination | ||

| + | |- | ||

| + | |P_GFX_RXP/RXN[15:0]||PCIe {{abbr|GFX}} Receive Data Differential Pairs | ||

| + | |- | ||

| + | |P_GFX_TXP/TXN[15:0]||PCIe GFX Transmit Data Differential Pairs | ||

| + | |- | ||

| + | |P_GPP_RXP/RXN[3:0]||PCIe {{abbr|GPP}} Receive Data Differential Pairs | ||

| + | |- | ||

| + | |P_GPP_TXP/RXN[3:0]||PCIe GPP Transmit Data Differential Pairs | ||

| + | |- | ||

| + | |P_HUB_RXP/RXN[3:0]||PCIe Hub (chipset) Receive Data Differential Pairs | ||

| + | |- | ||

| + | |P_HUB_TXP/TXN[3:0]||PCIe Hub Transmit Data Differential Pairs | ||

| + | |- | ||

| + | |PCIE_RST_L||Reset signal for PCIe devices | ||

| + | |- | ||

| + | |P_ZVDDP|| | ||

| + | |- | ||

| + | |P_ZVSS|| | ||

| + | |- | ||

| + | |P0A/P0B_ZVSS||PCIe Drive-Strength Auto-Compensation Resistor to VSS | ||

| + | |- | ||

| + | |SATA_RX(0-1)P/N||SATA Receive Data Differential Pairs (alt. func. of P_GPP[2], P_GPP[3]) | ||

| + | |- | ||

| + | |SATA_TX(0-1)P/N||SATA Transmit Data Differential Pairs | ||

| + | |- | ||

| + | |SATA_ACT_L||SATA Channel Active (HD LED | ||

| + | |- | ||

| + | |SGPIO0_CLK||{{abbr|SGPIO}} Interface CLK Output; SGPIO supported on Socket AM4? | ||

| + | |- | ||

| + | |SGPIO0_DATAIN||SGPIO DATA Input | ||

| + | |- | ||

| + | |SGPIO0_DATAOUT||SGPIO DATA Output | ||

| + | |- | ||

| + | |SGPIO0_LOAD||SGPIO LOAD Output | ||

| + | |- | ||

| + | |SATA_IS(0-1)_L|| | ||

| + | |- | ||

| + | |SATA_ZP(0-1)_L||Zero Power SATA {{abbr|ODD}} | ||

| + | |- | ||

| + | |SATA_ZVDDP|| | ||

| + | |- | ||

| + | |SATA_ZVSS|| | ||

| + | |- | ||

| + | |DP0-DP2_TXP/TXN[3:0]||DisplayPort 0-2 Main Link Differential Transmitter Lane 0-3 | ||

| + | |- | ||

| + | |DP0-DP2_AUXP/AUXN||DisplayPort 0-2 Auxiliary Channel | ||

| + | |- | ||

| + | |DP0-DP2_HPD||DisplayPort 0-2 Hot Plug Detect Input | ||

| + | |- | ||

| + | |DP_BLON||Display Panel Backlight Enable | ||

| + | |- | ||

| + | |DP_DIGON||Display Panel Power Enable | ||

| + | |- | ||

| + | |DP_VARY_BL||Display Backlight Brightness Control | ||

| + | |- | ||

| + | |DP_STEREOSYNC||StereoSync output for shutter glasses | ||

| + | |- | ||

| + | |DP_AUX_ZVSS|| | ||

| + | |- | ||

| + | |DP_ZVSS|| | ||

| + | |- | ||

| + | |USB_HSD(0-3)P/N||USB Port 0-3 High Speed I/O Differential Pairs | ||

| + | |- | ||

| + | |USB_SS_(0-3)RXP/RXN||USB Port 0-3 Super Speed Receive Differential Pairs | ||

| + | |- | ||

| + | |USB_SS_(0-3)TXP/TXN||USB Port 0-3 Super Speed Transmit Differential Pairs | ||

| + | |- | ||

| + | |USB_OC(0-3)_L||USB Port 0-3 Over Current signal from USB connector | ||

| + | |- | ||

| + | |USB_SS_ZVDDP|| | ||

| + | |- | ||

| + | |USB_SS_ZVSS|| | ||

| + | |- | ||

| + | |USB_ZVSS|| | ||

| + | |- | ||

| + | |USB(0-3)_ZVSS||USB Port 0-3 Drive-Strength Auto-Compensation Resistor to VSS | ||

| + | |- | ||

| + | |AZ_BITCLK||[[wikipedia:Intel High Definition Audio|Azalia HD Audio]] Interface Bit Clock | ||

| + | |- | ||

| + | |AZ_RST_L||HDA Reset | ||

| + | |- | ||

| + | |AZ_SDIN(0-2)||HDA Serial Data Input from Codec 0-2 | ||

| + | |- | ||

| + | |AZ_SDOUT||HDA Serial Data Output to Codec | ||

| + | |- | ||

| + | |AZ_SYNC||HDA Sync Signal to Codec | ||

| + | |- | ||

| + | |SPKR||PC speaker/beeper PWM output | ||

| + | |- | ||

| + | |SPI_CLK||{{abbr|SPI}} Clock | ||

| + | |- | ||

| + | |SPI_DO||SPI Data Out or Data 0 for multi-I/O SPI/eSPI device | ||

| + | |- | ||

| + | |SPI_DI||SPI Data In or Data 1 | ||

| + | |- | ||

| + | |SPI_WP_L||SPI Write Protect or Data 2 | ||

| + | |- | ||

| + | |SPI_HOLD_L||SPI Hold Signal (asserted low to hold the SPI transaction) or Data 3 | ||

| + | |- | ||

| + | |SPI_TPM_CS_L||SPI Chip Select for {{abbr|TPM}} | ||

| + | |- | ||

| + | |SPI_CS1/CS2_L||SPI Chip Select | ||

| + | |- | ||

| + | |ESPI_CLK||{{abbr|ESPI}} Clock (alt. func. of SPI_CLK) | ||

| + | |- | ||

| + | |ESPI_DAT(0-3)||ESPI Data[0], Data[1:0], Data[3:0] (alt. func. of SPI_DO/DI/WP_L/HOLD_L) | ||

| + | |- | ||

| + | |ESPI_CS_L||ESPI Chip Select (SPI_CS2_L) | ||

| + | |- | ||

| + | |ESPI_ALERT_L||ESPI Alert Input (LDRQ0_L) | ||

| + | |- | ||

| + | |ESPI_RESET_L||ESPI Reset (KBRST_L) | ||

| + | |- | ||

| + | |LAD(0-3)||{{abbr|LPC}} Command/Address/Data | ||

| + | |- | ||

| + | |LDRQ0_L||Encoded DMA/Bus Master Request 0 | ||

| + | |- | ||

| + | |LFRAME_L||LPC Bus Frame | ||

| + | |- | ||

| + | |LPCCLK(0-1)||LPC 33 MHz Clock | ||

| + | |- | ||

| + | |LPC_CLKRUN_L||LPC CLKRUN Signal | ||

| + | |- | ||

| + | |LPC_PD_L||LPC Power Down | ||

| + | |- | ||

| + | |LPC_PME_L||LPC Power Management Event | ||

| + | |- | ||

| + | |LPC_RST_L||LPC Reset | ||

| + | |- | ||

| + | |SERIRQ||Serial IRQ for DMA | ||

| + | |- | ||

| + | |I2C(2-3)_SCL||{{abbr|I<sup>2</sup>C}} Port 2-3 Clock | ||

| + | |- | ||

| + | |I2C(2-3)_SDA||I<sup>2</sup>C Port 2-3 Data | ||

| + | |- | ||

| + | |SCL0||{{abbr|SMBus}} Port 0 Clock (alt. func. of I2C2) | ||

| + | |- | ||

| + | |SDA0||SMBus Port 0 Data | ||

| + | |- | ||

| + | |SCL1||SMBus Port 1 Clock (alt. func. of I2C3) | ||

| + | |- | ||

| + | |SDA1||SMBus Port 1 Data | ||

| + | |- | ||

| + | |AGPIO*||Advanced {{abbr|GPIO}} pin for interrupt, wake, or I/O | ||

| + | |- | ||

| + | |EGPIO*||Enhanced GPIO for I/O only | ||

| + | |- | ||

| + | |GENINT(1-2)_L||Generic Interrupt Request | ||

| + | |- | ||

| + | |GFX_CLKP/N||PCIe {{abbr|GFX}} 100 MHz Differential Reference Clock | ||

| + | |- | ||

| + | |GPP_CLK0(0-3)P/N||PCIe {{abbr|GPP}} 100 MHz Differential Reference Clock | ||

| + | |- | ||

| + | |CLK_REQG_L||PCIe GFX Clock Request | ||

| + | |- | ||

| + | |CLK_REQ(0-3)_L||PCIe GPP Clock Request | ||

| + | |- | ||

| + | |OSCIN||14 MHz Clock Input | ||

| + | |- | ||

| + | |X32K_X1/X2||32768 Hz Clock XTAL for the integrated {{abbr|RTC}} | ||

| + | |- | ||

| + | |X48M_X1/X2||48 MHz Clock XTAL for the integrated clock generator | ||

| + | |- | ||

| + | |RTCCLK||32768 Hz Real Time Clock output, for a device requiring an RTC clock | ||

| + | |- | ||

| + | |X48M_OSC||48 MHz clock output for devices requiring a single-ended OSC input | ||

| + | |- | ||

| + | |KBRST_L||Keyboard Controller Reset Input (warm reset) | ||

| + | |- | ||

| + | |PWR_BTN_L||Power Button; Requests sleep state or causes wake event | ||

| + | |- | ||

| + | |PWR_GOOD||Power Good Input; Asserted when all voltages and clock inputs are within specification | ||

| + | |- | ||

| + | |PWROK||Power OK; Asserted by the processor after all power planes are active, the system clock generators are powered up and run stably | ||

| + | |- | ||

| + | |RESET_L||Bidirectional signal that resets the processor when asserted; Normally controlled by an internal state machine but can also be asserted by a second external source | ||

| + | |- | ||

| + | |RSMRST_L||Resume Reset from motherboard; Asserted on power up, deasserted when S5 power supplies are within specification | ||

| + | |- | ||

| + | |S0A3_GPIO||S0A3 Indicator | ||

| + | |- | ||

| + | |SLP_S3/S5_L||S3/S5 Sleep State Power Plane Control Signal | ||

| + | |- | ||

| + | |SYS_RESET_L||System Reset Input (reset button) | ||

| + | |- | ||

| + | |WAKE_L||PCIe WAKE_L signal, wake system out of sleep state | ||

| + | |- | ||

| + | |BLINK||Blink LED S-state Indicator | ||

| + | |- | ||

| + | |FANIN0||Fan tachometer input | ||

| + | |- | ||

| + | |FANOUT0||Fan PWM output | ||

| + | |- | ||

| + | |ALERT_L||Programmable pin that can indicate different events, including a {{abbr|SB-TSI}} interrupt | ||

| + | |- | ||

| + | |PROCHOT_L||Asserted to force the processor into {{abbr|HTC}}-active state | ||

| + | |- | ||

| + | |SIC||Sideband Interface ({{abbr|SB-TSI}}) Clock | ||

| + | |- | ||

| + | |SID||Sideband Interface Data | ||

| + | |- | ||

| + | |THERMTRIP_L||{{x86|Thermal protection|Temperature Trip}} Input/Output | ||

| + | |- | ||

| + | |DBREQ_L||Debug Request input to JTAG controller | ||

| + | |- | ||

| + | |DBRDY|| | ||

| + | |- | ||

| + | |TCK||{{abbr|JTAG}} Clock | ||

| + | |- | ||

| + | |TDI||JTAG Data Input | ||

| + | |- | ||

| + | |TDO||JTAG Data Output | ||

| + | |- | ||

| + | |TMS||JTAG Mode Select | ||

| + | |- | ||

| + | |TRST_L||JTAG Reset | ||

| + | |- | ||

| + | |TEST*||Test Pins | ||

| + | |- | ||

| + | |SVC||Serial VID Interface Clock | ||

| + | |- | ||

| + | |SVD||Serial VID Interface Data | ||

| + | |- | ||

| + | |SVT||Serial VID Interface Telemetry | ||

| + | |- | ||

| + | |VDDIO_AUDIO||Azalia HD Audio power supply | ||

| + | |- | ||

| + | |VDDBT_RTC_G||Integrated Real Time Clock battery power supply | ||

| + | |- | ||

| + | |VDDCR_CPU||Core power supply | ||

| + | |- | ||

| + | |VDDCR_CPU_SENSE||VDDCR_CPU voltage monitor pin | ||

| + | |- | ||

| + | |VDDCR_SOC||Supply voltage for the Northbridge | ||

| + | |- | ||

| + | |VDDCR_SOC_SENSE||VDDCR_SOC voltage monitor pin | ||

| + | |- | ||

| + | |VDDCR_SOC_S5||Always on SOC power supply | ||

| + | |- | ||

| + | |VDDIO_MEM_S3||1.2 V DRAM supply voltage | ||

| + | |- | ||

| + | |VDDIO_MEM_S3_SENSE||VDDIO_MEM_S3 voltage monitor pin | ||

| + | |- | ||

| + | |VDDP|| | ||

| + | |- | ||

| + | |VDDP_SENSE||VDDP voltage monitor pin | ||

| + | |- | ||

| + | |VDDP_S5|| | ||

| + | |- | ||

| + | |VDD_18||1.8 V supply voltage | ||

| + | |- | ||

| + | |VDD_18_S5||Always on 1.8 V supply voltage | ||

| + | |- | ||

| + | |VDD_33||3.3 V supply voltage | ||

| + | |- | ||

| + | |VDD_33_S5||Always on 3.3 V supply voltage | ||

| + | |- | ||

| + | |VSS||Ground | ||

| + | |- | ||

| + | |VSS_SENSE_A||VSS sense pin for voltage regulator | ||

| + | |- | ||

| + | |VSS_SENSE_B||VSS sense pin for voltage regulator | ||

| + | |- | ||

| + | |{{vanchor|CORETYPE}}[1:0]||Processor Core Type Indicator | ||

| + | |- | ||

| + | |{{vanchor|AM4R1}}||Processor Family Revision Identifier | ||

| + | |- | ||

| + | |RSVD||Reserved | ||

| + | |} | ||

| + | |||

| + | == See also == | ||

| + | * {{\\|Socket AM3+}} | ||

| + | * {{\\|Socket AM5}} | ||

| + | * {{\\|Socket FM2+}} | ||

| + | * {{\\|Socket SP3}} | ||

| + | * {{\\|Socket TR4}} | ||

| + | * {{\\|Socket sTRX4}} | ||

| + | * {{\\|FP5|Package FP5}} | ||

| + | * {{\\|FP6|Package FP6}} | ||

| + | |||

| + | [[Category:amd]] | ||

Latest revision as of 00:58, 12 January 2024

| Edit Values | |

| Socket AM4 | |

| General Info | |

| Designer | AMD |

| Introduction | September 2016 (launched) |

| Market | Desktop |

| Microarchitecture | Zen |

| TDP | 105 W 105,000 mW 0.141 hp 0.105 kW |

| Package | |

| Name | OPGA-1331 |

| Type | Organic Micro Pin Grid Array |

| Contacts | 1331 |

| Dimension | 40 mm 4 cm × 40 mm1.575 in 4 cm 1.575 in |

| Pitch | 1 mm 0.0394 in |

| Socket | |

| Name | Socket AM4 |

| Type | PGA |

| Succession | |

AM4 is a socket for AMD's mainstream series of microprocessors, serving as a successor to Socket FM2+ and Socket AM3+. It was superseded by Socket AM5.

Contents

Overview[edit]

Launching in September 2016, the AM4 replaces a number of older AMD sockets including the Socket FM2+ and Socket AM3+ designed to unify all its mainstream processors from the low-end to the high-end in a single socket. At the time AMD stated the socket will feature prolong comparability life.

The AM4 accepts zero-insertion force µOPGA-1331-packaged microprocessors designed based on the Excavator, Zen, Zen+, Zen 2, and Zen 3 microarchitectures, although the exact chips supported depends on the accompanying chipset.

Chipsets[edit]

| Socket AM4 Platform [Edit] | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| Segment | Chipset | USB | SATA | SATAe | PCIe | RAID | Dual PCIe | Overclocking | ||

| 3.1 G1 | 3.1 G2 | 2.0 | ||||||||

| 500-series (Zen+, Zen 2, Zen 3) | ||||||||||

| Mainstream | B550 | 2 | 6 | 6 | 8 + 4x NVME | 0 | 16x Gen4 | 0,1,10 | ✔ | ✔ |

| Enthusiast | X570 | 0 | 8 | 4 | 14 + 4x NVME | 0 | 16x Gen4 | 0,1,10 | ||

| 400-series (Zen+) | ||||||||||

| Mainstream | B450 | 2 | 2 | 6 | 6 + 4x NVME | 1 | 6x Gen3 | 0,1,10 | ✘ | ✔ |

| Enthusiast | X470 | 6 | 2 | 6 | 10 + 4x NVME | 2 | 8x Gen3 | 0,1,10 | ✔ | |

| 300-series (Zen) | ||||||||||

| Small Form Factor | A300, B300 | 4 | 0 | 0 | 2 + 2x NVMe | 1 | 4x Gen3 | 0,1 | ✘ | |

| X300 | 4 | 0 | 0 | 2 + 2x NVMe | 1 | 4x Gen3 | 0,1 | ✔ | ||

| Entry-level | A320 | 6 | 1 | 6 | 4 + 2x NVMe | 2 | 4x Gen2 | 0,1,10 | ✘ | ✘ |

| Mainstream | B350 | 6 | 2 | 6 | 4 + 2x NVMe | 2 | 6x Gen2 | 0,1,10 | ✔ | |

| Enthusiast | X370 | 6 | 2 | 6 | 6 + 2x NVMe | 2 | 8x Gen2 | 0,1,10 | ✔ | |

Support[edit]

AM4 socket support for a particular microprocessor depends on the chipset compatibility.

| Socket AM4 Processor Support | |||||||

|---|---|---|---|---|---|---|---|

| Chipset | Zen | Zen+ | Zen 2 | Zen 3 | |||

| Summit Ridge | Raven Ridge | Pinnacle Ridge | Picasso | Matisse | Renoir | Vermeer | |

| A320 | ✔ | * | |||||

| A520 | ✘ | ✔ | |||||

| B350 | ✔ | * | |||||

| B450 | ✔ | * | |||||

| B550 | ✘ | ✔ | |||||

| X370 | ✔ | * | |||||

| X470 | ✔ | * | |||||

| X570 | ✘ | ✔ | |||||

* - Selective Beta BIOS update required

Processors using Socket AM4[edit]

| List of all Socket AM4-based Processors | |||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Model | Price | Process | Launched | µarch | Family | Core | C | T | Freq | Turbo | TDP | ||||||||

| 200GE | $ 55.00 € 49.50 £ 44.55 ¥ 5,683.15 | 14 nm 0.014 μm 1.4e-5 mm | 6 September 2018 | Zen | Athlon | Raven Ridge | 2 | 4 | 3.2 GHz 3,200 MHz 3,200,000 kHz | 35 W 35,000 mW 0.0469 hp 0.035 kW | |||||||||

| 220GE | $ 65.00 € 58.50 £ 52.65 ¥ 6,716.45 | 14 nm 0.014 μm 1.4e-5 mm | 21 December 2018 | Zen | Athlon | Raven Ridge | 2 | 4 | 3.4 GHz 3,400 MHz 3,400,000 kHz | 35 W 35,000 mW 0.0469 hp 0.035 kW | |||||||||

| 240GE | $ 75.00 € 67.50 £ 60.75 ¥ 7,749.75 | 14 nm 0.014 μm 1.4e-5 mm | 21 December 2018 | Zen | Athlon | Raven Ridge | 2 | 4 | 3.5 GHz 3,500 MHz 3,500,000 kHz | 35 W 35,000 mW 0.0469 hp 0.035 kW | |||||||||

| 3000G | $ 49.00 € 44.10 £ 39.69 ¥ 5,063.17 | 14 nm 0.014 μm 1.4e-5 mm | 20 November 2019 | Zen | Athlon | Dali Raven Ridge | 2 | 4 | 3.5 GHz 3,500 MHz 3,500,000 kHz | 35 W 35,000 mW 0.0469 hp 0.035 kW | |||||||||

| PRO 200GE | 14 nm 0.014 μm 1.4e-5 mm | 6 September 2018 | Zen | Athlon | Raven Ridge | 2 | 4 | 3.2 GHz 3,200 MHz 3,200,000 kHz | 35 W 35,000 mW 0.0469 hp 0.035 kW | ||||||||||

| PRO 300GE | 12 nm 0.012 μm 1.2e-5 mm | 30 September 2019 | Zen+ | Athlon | Picasso | 2 | 4 | 3.4 GHz 3,400 MHz 3,400,000 kHz | 35 W 35,000 mW 0.0469 hp 0.035 kW | ||||||||||

| 1200 | $ 109.00 € 98.10 £ 88.29 ¥ 11,262.97 | 14 nm 0.014 μm 1.4e-5 mm | 27 July 2017 | Zen | Ryzen 3 | Summit Ridge | 4 | 4 | 3.1 GHz 3,100 MHz 3,100,000 kHz | 3.4 GHz 3,400 MHz 3,400,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | ||||||||

| 1300X | $ 129.00 € 116.10 £ 104.49 ¥ 13,329.57 | 14 nm 0.014 μm 1.4e-5 mm | 27 July 2017 | Zen | Ryzen 3 | Summit Ridge | 4 | 4 | 3.5 GHz 3,500 MHz 3,500,000 kHz | 3.7 GHz 3,700 MHz 3,700,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | ||||||||

| 2200G | $ 99.00 € 89.10 £ 80.19 ¥ 10,229.67 | 14 nm 0.014 μm 1.4e-5 mm | 12 February 2018 | Zen | Ryzen 3 | Raven Ridge | 4 | 4 | 3.5 GHz 3,500 MHz 3,500,000 kHz | 3.7 GHz 3,700 MHz 3,700,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | ||||||||

| 2200GE | 14 nm 0.014 μm 1.4e-5 mm | 19 April 2018 | Zen | Ryzen 3 | Raven Ridge | 4 | 4 | 3.2 GHz 3,200 MHz 3,200,000 kHz | 3.6 GHz 3,600 MHz 3,600,000 kHz | 35 W 35,000 mW 0.0469 hp 0.035 kW | |||||||||

| 2300X | 12 nm 0.012 μm 1.2e-5 mm | 10 September 2018 | Zen+ | Ryzen 3 | Pinnacle Ridge | 4 | 4 | 3.5 GHz 3,500 MHz 3,500,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | ||||||||||

| 3200G | $ 99.00 € 89.10 £ 80.19 ¥ 10,229.67 | 12 nm 0.012 μm 1.2e-5 mm | 7 July 2019 | Zen+ | Ryzen 3 | Picasso | 4 | 4 | 3.6 GHz 3,600 MHz 3,600,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | |||||||||

| 4300G | 7 nm 0.007 μm 7.0e-6 mm | 21 July 2020 | Zen 2 | Ryzen 3 | Renoir | 4 | 8 | 3.8 GHz 3,800 MHz 3,800,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | ||||||||||

| 4300GE | 7 nm 0.007 μm 7.0e-6 mm | 21 July 2020 | Zen 2 | Ryzen 3 | Renoir | 4 | 8 | 3.5 GHz 3,500 MHz 3,500,000 kHz | 35 W 35,000 mW 0.0469 hp 0.035 kW | ||||||||||

| 5300G | 7 nm 0.007 μm 7.0e-6 mm | 13 April 2021 | Zen 3 | Ryzen 3 | Cezanne | 4 | 8 | 4 GHz 4,000 MHz 4,000,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | ||||||||||

| 5300GE | 7 nm 0.007 μm 7.0e-6 mm | 13 April 2021 | Zen 3 | Ryzen 3 | Cezanne | 4 | 8 | 3.6 GHz 3,600 MHz 3,600,000 kHz | 35 W 35,000 mW 0.0469 hp 0.035 kW | ||||||||||

| PRO 1200 | 14 nm 0.014 μm 1.4e-5 mm | Zen | Ryzen 3 | Summit Ridge | 4 | 4 | 3.1 GHz 3,100 MHz 3,100,000 kHz | 3.4 GHz 3,400 MHz 3,400,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | ||||||||||

| PRO 1300 | 14 nm 0.014 μm 1.4e-5 mm | Zen | Ryzen 3 | Summit Ridge | 4 | 4 | 3.5 GHz 3,500 MHz 3,500,000 kHz | 3.7 GHz 3,700 MHz 3,700,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | ||||||||||

| PRO 2200G | 14 nm 0.014 μm 1.4e-5 mm | 10 May 2018 | Zen | Ryzen 3 | Raven Ridge | 4 | 4 | 3.5 GHz 3,500 MHz 3,500,000 kHz | 3.7 GHz 3,700 MHz 3,700,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | |||||||||

| PRO 2200GE | 14 nm 0.014 μm 1.4e-5 mm | 10 May 2018 | Zen | Ryzen 3 | Raven Ridge | 4 | 4 | 3.2 GHz 3,200 MHz 3,200,000 kHz | 3.6 GHz 3,600 MHz 3,600,000 kHz | 35 W 35,000 mW 0.0469 hp 0.035 kW | |||||||||

| PRO 3200G | 12 nm 0.012 μm 1.2e-5 mm | 30 September 2019 | Zen+ | Ryzen 3 | Picasso | 4 | 4 | 3.6 GHz 3,600 MHz 3,600,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | ||||||||||

| PRO 3200GE | 12 nm 0.012 μm 1.2e-5 mm | 30 September 2019 | Zen+ | Ryzen 3 | Picasso | 4 | 4 | 3.3 GHz 3,300 MHz 3,300,000 kHz | 35 W 35,000 mW 0.0469 hp 0.035 kW | ||||||||||

| PRO 4350G | 7 nm 0.007 μm 7.0e-6 mm | 21 July 2020 | Zen 2 | Ryzen 3 | Renoir | 4 | 8 | 3.8 GHz 3,800 MHz 3,800,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | ||||||||||

| PRO 4350GE | 7 nm 0.007 μm 7.0e-6 mm | 21 July 2020 | Zen 2 | Ryzen 3 | Renoir | 4 | 8 | 3.5 GHz 3,500 MHz 3,500,000 kHz | 35 W 35,000 mW 0.0469 hp 0.035 kW | ||||||||||

| PRO 5350G | 7 nm 0.007 μm 7.0e-6 mm | 1 June 2021 | Zen 3 | Ryzen 3 | Cezanne | 4 | 8 | 4 GHz 4,000 MHz 4,000,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | ||||||||||

| PRO 5350GE | 7 nm 0.007 μm 7.0e-6 mm | 1 June 2021 | Zen 3 | Ryzen 3 | Cezanne | 4 | 8 | 3.6 GHz 3,600 MHz 3,600,000 kHz | 35 W 35,000 mW 0.0469 hp 0.035 kW | ||||||||||

| 1400 | $ 169.00 € 152.10 £ 136.89 ¥ 17,462.77 | 14 nm 0.014 μm 1.4e-5 mm | 11 April 2017 | Zen | Ryzen 5 | Summit Ridge | 4 | 8 | 3.2 GHz 3,200 MHz 3,200,000 kHz | 3.4 GHz 3,400 MHz 3,400,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | ||||||||

| 1500X | $ 189.00 € 170.10 £ 153.09 ¥ 19,529.37 | 14 nm 0.014 μm 1.4e-5 mm | 11 April 2017 | Zen | Ryzen 5 | Summit Ridge | 4 | 8 | 3.5 GHz 3,500 MHz 3,500,000 kHz | 3.7 GHz 3,700 MHz 3,700,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | ||||||||

| 1600 | $ 219.00 € 197.10 £ 177.39 ¥ 22,629.27 | 14 nm 0.014 μm 1.4e-5 mm | 11 April 2017 | Zen | Ryzen 5 | Summit Ridge | 6 | 12 | 3.2 GHz 3,200 MHz 3,200,000 kHz | 3.6 GHz 3,600 MHz 3,600,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | ||||||||

| 1600X | $ 249.00 € 224.10 £ 201.69 ¥ 25,729.17 | 14 nm 0.014 μm 1.4e-5 mm | 11 April 2017 | Zen | Ryzen 5 | Summit Ridge | 6 | 12 | 3.6 GHz 3,600 MHz 3,600,000 kHz | 4 GHz 4,000 MHz 4,000,000 kHz | 95 W 95,000 mW 0.127 hp 0.095 kW | ||||||||

| 2400G | $ 169.00 € 152.10 £ 136.89 ¥ 17,462.77 | 14 nm 0.014 μm 1.4e-5 mm | 12 February 2018 | Zen | Ryzen 5 | Raven Ridge | 4 | 8 | 3.6 GHz 3,600 MHz 3,600,000 kHz | 3.9 GHz 3,900 MHz 3,900,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | ||||||||

| 2400GE | 14 nm 0.014 μm 1.4e-5 mm | 19 April 2018 | Zen | Ryzen 5 | Raven Ridge | 4 | 8 | 3.2 GHz 3,200 MHz 3,200,000 kHz | 3.8 GHz 3,800 MHz 3,800,000 kHz | 35 W 35,000 mW 0.0469 hp 0.035 kW | |||||||||

| 2500X | 12 nm 0.012 μm 1.2e-5 mm | 10 September 2018 | Zen+ | Ryzen 5 | Pinnacle Ridge | 4 | 8 | 3.6 GHz 3,600 MHz 3,600,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | ||||||||||

| 2600 | $ 170.00 € 153.00 £ 137.70 ¥ 17,566.10 | 12 nm 0.012 μm 1.2e-5 mm | 19 April 2018 | Zen+ | Ryzen 5 | Pinnacle Ridge | 6 | 12 | 3.4 GHz 3,400 MHz 3,400,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | |||||||||

| 2600E | 12 nm 0.012 μm 1.2e-5 mm | 10 September 2018 | Zen+ | Ryzen 5 | Pinnacle Ridge | 6 | 12 | 3.1 GHz 3,100 MHz 3,100,000 kHz | 45 W 45,000 mW 0.0603 hp 0.045 kW | ||||||||||

| 2600X | $ 229.00 € 206.10 £ 185.49 ¥ 23,662.57 | 12 nm 0.012 μm 1.2e-5 mm | 19 April 2018 | Zen+ | Ryzen 5 | Pinnacle Ridge | 6 | 12 | 3.6 GHz 3,600 MHz 3,600,000 kHz | 95 W 95,000 mW 0.127 hp 0.095 kW | |||||||||

| 3400G | 12 nm 0.012 μm 1.2e-5 mm | 7 July 2019 | Zen+ | Ryzen 5 | Picasso | 4 | 8 | 3.7 GHz 3,700 MHz 3,700,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | ||||||||||

| 3500 | 7 nm 0.007 μm 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | Zen 2 | Ryzen 5 | Matisse | 6 | 6 | 3.6 GHz 3,600 MHz 3,600,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | |||||||||||

| 3500X | 7 nm 0.007 μm 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | Zen 2 | Ryzen 5 | Matisse | 6 | 6 | 3.6 GHz 3,600 MHz 3,600,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | |||||||||||

| 3600 | $ 199.00 € 179.10 £ 161.19 ¥ 20,562.67 | 7 nm 0.007 μm 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | 7 July 2019 | Zen 2 | Ryzen 5 | Matisse | 6 | 12 | 3.6 GHz 3,600 MHz 3,600,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | |||||||||

| 3600X | $ 249.00 € 224.10 £ 201.69 ¥ 25,729.17 | 7 nm 0.007 μm 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | 7 July 2019 | Zen 2 | Ryzen 5 | Matisse | 6 | 12 | 3.8 GHz 3,800 MHz 3,800,000 kHz | 95 W 95,000 mW 0.127 hp 0.095 kW | |||||||||

| 3600XT | $ 249.00 € 224.10 £ 201.69 ¥ 25,729.17 | 7 nm 0.007 μm 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | 7 July 2020 | Zen 2 | Ryzen 5 | Matisse | 6 | 12 | 3.8 GHz 3,800 MHz 3,800,000 kHz | 95 W 95,000 mW 0.127 hp 0.095 kW | |||||||||

| 4600G | 7 nm 0.007 μm 7.0e-6 mm | 21 July 2020 | Zen 2 | Ryzen 5 | Renoir | 6 | 12 | 3.7 GHz 3,700 MHz 3,700,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | ||||||||||

| 4600GE | 7 nm 0.007 μm 7.0e-6 mm | 21 July 2020 | Zen 2 | Ryzen 5 | Renoir | 6 | 12 | 3.3 GHz 3,300 MHz 3,300,000 kHz | 35 W 35,000 mW 0.0469 hp 0.035 kW | ||||||||||

| 5600G | $ 259.00 € 233.10 £ 209.79 ¥ 26,762.47 | 7 nm 0.007 μm 7.0e-6 mm | 13 April 2021 | Zen 3 | Ryzen 5 | Cezanne | 6 | 12 | 3.9 GHz 3,900 MHz 3,900,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | |||||||||

| 5600GE | 7 nm 0.007 μm 7.0e-6 mm | 13 April 2021 | Zen 3 | Ryzen 5 | Cezanne | 6 | 12 | 3.4 GHz 3,400 MHz 3,400,000 kHz | 35 W 35,000 mW 0.0469 hp 0.035 kW | ||||||||||

| 5600X | $ 299.00 € 269.10 £ 242.19 ¥ 30,895.67 | 7 nm 0.007 μm 12 nm7.0e-6 mm 0.012 μm 1.2e-5 mm | 5 November 2020 | Zen 3 | Ryzen 5 | Vermeer | 6 | 12 | 3.7 GHz 3,700 MHz 3,700,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | |||||||||

| PRO 1500 | 14 nm 0.014 μm 1.4e-5 mm | 29 June 2017 | Zen | Ryzen 5 | Summit Ridge | 4 | 8 | 3.5 GHz 3,500 MHz 3,500,000 kHz | 3.7 GHz 3,700 MHz 3,700,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | |||||||||

| PRO 1600 | 14 nm 0.014 μm 1.4e-5 mm | Zen | Ryzen 5 | Summit Ridge | 6 | 12 | 3.2 GHz 3,200 MHz 3,200,000 kHz | 3.6 GHz 3,600 MHz 3,600,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | ||||||||||

| PRO 2400G | $ 169.00 € 152.10 £ 136.89 ¥ 17,462.77 | 14 nm 0.014 μm 1.4e-5 mm | 10 May 2018 | Zen | Ryzen 5 | Raven Ridge | 4 | 8 | 3.6 GHz 3,600 MHz 3,600,000 kHz | 3.9 GHz 3,900 MHz 3,900,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | ||||||||

| Count: 93 | |||||||||||||||||||

Photos[edit]

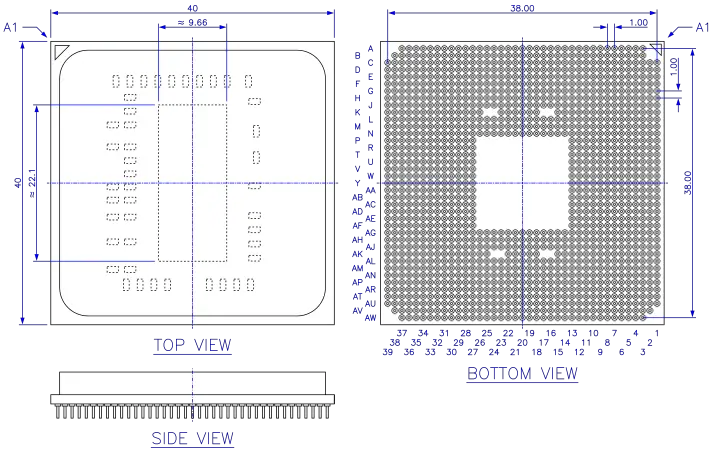

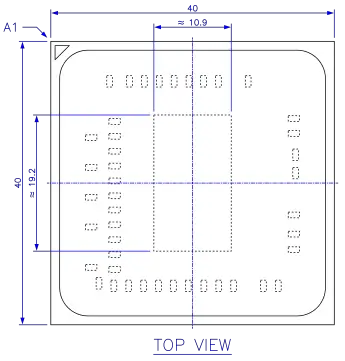

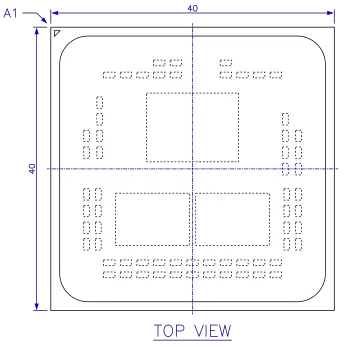

Package Diagrams[edit]

Approximate dimensions of the "Summit Ridge" (≤ 8C, Zen, 14 nm, Feb. 2017) and "Pinnacle Ridge" (≤ 8C, Zen+, 12 nm, April 2018) package. All dimensions in millimeters.

Approximate dimensions of the "Raven Ridge" desktop package (≤ 4C/11CU, Zen, 14 nm, Oct. 2017). Mobile and embedded versions are available in a FP5 package. All dimensions in millimeters.

Approximate dimensions of the "Matisse" package (≤ 16C, Zen 2, 7/14 nm, July 2019). The left CCD is unpopulated in ≤ 8C models. All dimensions in millimeters.

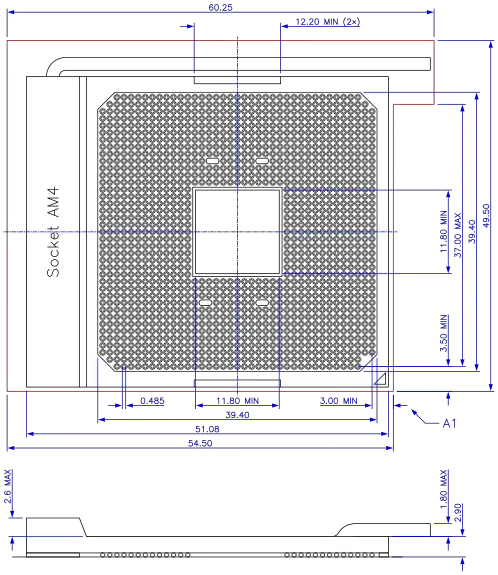

Socket Diagrams[edit]

No data available. The diagram shows the dimensions of Foxconn Interconnect Technology Part No. PZ1331A-51ZZ*-1H. All dimensions in millimeters.

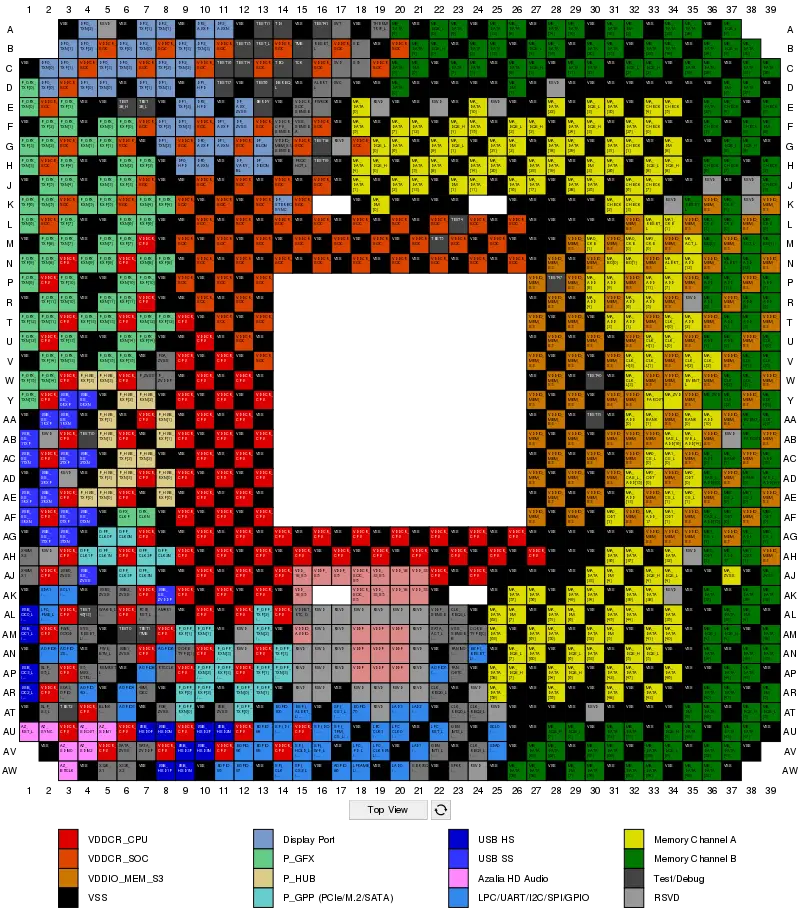

Pin Map[edit]

AM4 pinout, top view. Click to flip and rotate.

Pin Description[edit]

| Signal | Description |

|---|---|

| MA/MB_ACT_L | DRAM Channel A/B Activation Command |

| MA/MB_ADD[13:0] | DRAM Column/Row Address |

| MA/MB_ADD_17 | DRAM Column/Row Address 17 |

| MA/MB_ALERT_L | DRAM Alert (CRC error and Command/Address parity error) |

| MA/MB_BANK[1:0] | DRAM Bank Address |

| MA/MB_BG[1:0] | DRAM Bank Group |

| MA/MB_CAS_L_ADD[15] | DRAM Column Address Strobe or Column/Row Address 15 |

| MA/MB_CHECK[7:0] | DRAM ECC Check Bits |

| MA/MB_DATA[63:0] | DRAM Data Bus |

| MA/MB_DM[8:0] | DRAM Data Mask |

| MA/MB_DQS_H/L[8:0] | DRAM Differential Data Strobe |

| MA/MB_EVENT_L | DRAM Thermal Event Status |

| MA/MB_PAROUT | DRAM Command/Address Parity |

| MA/MB_RAS_L_ADD[16] | DRAM Row Address Strobe or Column/Row Address 16 |

| MA/MB_RESET_L | DRAM Reset |

| MA/MB_WE_L_ADD[14] | DRAM Write Enable or Column/Row Address 14 |

| MA/MB_ZVDDIO_MEM_S3 | |

| MA/MB_ZVSS | DRAM Interface Drive-Strength Auto-Compensation Resistor to VSS |

| MA0/MA1/MB0/MB1_CKE[1:0] | DRAM Channel A/B DIMM 0/1 Clock Enable |

| MA0/MA1/MB0/MB1_CLK_H/L[3:0] | DRAM Channel A/B DIMM 0/1 Differential Clock |

| MA0/MA1/MB0/MB1_CS_L[1:0] | DRAM Channel A/B DIMM 0/1 Chip Select |

| MA0/MA1/MB0/MB1_ODT[1:0] | DRAM Channel A/B DIMM 0/1 Enable Pin for On Die Termination |

| P_GFX_RXP/RXN[15:0] | PCIe GFX Receive Data Differential Pairs |

| P_GFX_TXP/TXN[15:0] | PCIe GFX Transmit Data Differential Pairs |

| P_GPP_RXP/RXN[3:0] | PCIe GPP Receive Data Differential Pairs |

| P_GPP_TXP/RXN[3:0] | PCIe GPP Transmit Data Differential Pairs |

| P_HUB_RXP/RXN[3:0] | PCIe Hub (chipset) Receive Data Differential Pairs |

| P_HUB_TXP/TXN[3:0] | PCIe Hub Transmit Data Differential Pairs |

| PCIE_RST_L | Reset signal for PCIe devices |

| P_ZVDDP | |

| P_ZVSS | |

| P0A/P0B_ZVSS | PCIe Drive-Strength Auto-Compensation Resistor to VSS |

| SATA_RX(0-1)P/N | SATA Receive Data Differential Pairs (alt. func. of P_GPP[2], P_GPP[3]) |

| SATA_TX(0-1)P/N | SATA Transmit Data Differential Pairs |

| SATA_ACT_L | SATA Channel Active (HD LED |

| SGPIO0_CLK | SGPIO Interface CLK Output; SGPIO supported on Socket AM4? |

| SGPIO0_DATAIN | SGPIO DATA Input |

| SGPIO0_DATAOUT | SGPIO DATA Output |

| SGPIO0_LOAD | SGPIO LOAD Output |

| SATA_IS(0-1)_L | |

| SATA_ZP(0-1)_L | Zero Power SATA ODD |

| SATA_ZVDDP | |

| SATA_ZVSS | |

| DP0-DP2_TXP/TXN[3:0] | DisplayPort 0-2 Main Link Differential Transmitter Lane 0-3 |

| DP0-DP2_AUXP/AUXN | DisplayPort 0-2 Auxiliary Channel |

| DP0-DP2_HPD | DisplayPort 0-2 Hot Plug Detect Input |

| DP_BLON | Display Panel Backlight Enable |

| DP_DIGON | Display Panel Power Enable |

| DP_VARY_BL | Display Backlight Brightness Control |

| DP_STEREOSYNC | StereoSync output for shutter glasses |

| DP_AUX_ZVSS | |

| DP_ZVSS | |

| USB_HSD(0-3)P/N | USB Port 0-3 High Speed I/O Differential Pairs |

| USB_SS_(0-3)RXP/RXN | USB Port 0-3 Super Speed Receive Differential Pairs |

| USB_SS_(0-3)TXP/TXN | USB Port 0-3 Super Speed Transmit Differential Pairs |

| USB_OC(0-3)_L | USB Port 0-3 Over Current signal from USB connector |

| USB_SS_ZVDDP | |

| USB_SS_ZVSS | |

| USB_ZVSS | |

| USB(0-3)_ZVSS | USB Port 0-3 Drive-Strength Auto-Compensation Resistor to VSS |

| AZ_BITCLK | Azalia HD Audio Interface Bit Clock |

| AZ_RST_L | HDA Reset |

| AZ_SDIN(0-2) | HDA Serial Data Input from Codec 0-2 |

| AZ_SDOUT | HDA Serial Data Output to Codec |

| AZ_SYNC | HDA Sync Signal to Codec |

| SPKR | PC speaker/beeper PWM output |

| SPI_CLK | SPI Clock |

| SPI_DO | SPI Data Out or Data 0 for multi-I/O SPI/eSPI device |

| SPI_DI | SPI Data In or Data 1 |

| SPI_WP_L | SPI Write Protect or Data 2 |

| SPI_HOLD_L | SPI Hold Signal (asserted low to hold the SPI transaction) or Data 3 |

| SPI_TPM_CS_L | SPI Chip Select for TPM |

| SPI_CS1/CS2_L | SPI Chip Select |

| ESPI_CLK | ESPI Clock (alt. func. of SPI_CLK) |

| ESPI_DAT(0-3) | ESPI Data[0], Data[1:0], Data[3:0] (alt. func. of SPI_DO/DI/WP_L/HOLD_L) |

| ESPI_CS_L | ESPI Chip Select (SPI_CS2_L) |

| ESPI_ALERT_L | ESPI Alert Input (LDRQ0_L) |

| ESPI_RESET_L | ESPI Reset (KBRST_L) |

| LAD(0-3) | LPC Command/Address/Data |

| LDRQ0_L | Encoded DMA/Bus Master Request 0 |

| LFRAME_L | LPC Bus Frame |

| LPCCLK(0-1) | LPC 33 MHz Clock |

| LPC_CLKRUN_L | LPC CLKRUN Signal |

| LPC_PD_L | LPC Power Down |

| LPC_PME_L | LPC Power Management Event |

| LPC_RST_L | LPC Reset |

| SERIRQ | Serial IRQ for DMA |

| I2C(2-3)_SCL | I2C Port 2-3 Clock |

| I2C(2-3)_SDA | I2C Port 2-3 Data |

| SCL0 | SMBus Port 0 Clock (alt. func. of I2C2) |

| SDA0 | SMBus Port 0 Data |

| SCL1 | SMBus Port 1 Clock (alt. func. of I2C3) |

| SDA1 | SMBus Port 1 Data |

| AGPIO* | Advanced GPIO pin for interrupt, wake, or I/O |

| EGPIO* | Enhanced GPIO for I/O only |

| GENINT(1-2)_L | Generic Interrupt Request |

| GFX_CLKP/N | PCIe GFX 100 MHz Differential Reference Clock |

| GPP_CLK0(0-3)P/N | PCIe GPP 100 MHz Differential Reference Clock |

| CLK_REQG_L | PCIe GFX Clock Request |

| CLK_REQ(0-3)_L | PCIe GPP Clock Request |

| OSCIN | 14 MHz Clock Input |

| X32K_X1/X2 | 32768 Hz Clock XTAL for the integrated RTC |

| X48M_X1/X2 | 48 MHz Clock XTAL for the integrated clock generator |

| RTCCLK | 32768 Hz Real Time Clock output, for a device requiring an RTC clock |

| X48M_OSC | 48 MHz clock output for devices requiring a single-ended OSC input |

| KBRST_L | Keyboard Controller Reset Input (warm reset) |

| PWR_BTN_L | Power Button; Requests sleep state or causes wake event |

| PWR_GOOD | Power Good Input; Asserted when all voltages and clock inputs are within specification |

| PWROK | Power OK; Asserted by the processor after all power planes are active, the system clock generators are powered up and run stably |

| RESET_L | Bidirectional signal that resets the processor when asserted; Normally controlled by an internal state machine but can also be asserted by a second external source |

| RSMRST_L | Resume Reset from motherboard; Asserted on power up, deasserted when S5 power supplies are within specification |

| S0A3_GPIO | S0A3 Indicator |

| SLP_S3/S5_L | S3/S5 Sleep State Power Plane Control Signal |

| SYS_RESET_L | System Reset Input (reset button) |

| WAKE_L | PCIe WAKE_L signal, wake system out of sleep state |

| BLINK | Blink LED S-state Indicator |

| FANIN0 | Fan tachometer input |

| FANOUT0 | Fan PWM output |

| ALERT_L | Programmable pin that can indicate different events, including a SB-TSI interrupt |

| PROCHOT_L | Asserted to force the processor into HTC-active state |

| SIC | Sideband Interface (SB-TSI) Clock |

| SID | Sideband Interface Data |

| THERMTRIP_L | Temperature Trip Input/Output |

| DBREQ_L | Debug Request input to JTAG controller |

| DBRDY | |

| TCK | JTAG Clock |

| TDI | JTAG Data Input |

| TDO | JTAG Data Output |

| TMS | JTAG Mode Select |

| TRST_L | JTAG Reset |

| TEST* | Test Pins |

| SVC | Serial VID Interface Clock |

| SVD | Serial VID Interface Data |

| SVT | Serial VID Interface Telemetry |

| VDDIO_AUDIO | Azalia HD Audio power supply |

| VDDBT_RTC_G | Integrated Real Time Clock battery power supply |

| VDDCR_CPU | Core power supply |

| VDDCR_CPU_SENSE | VDDCR_CPU voltage monitor pin |

| VDDCR_SOC | Supply voltage for the Northbridge |

| VDDCR_SOC_SENSE | VDDCR_SOC voltage monitor pin |

| VDDCR_SOC_S5 | Always on SOC power supply |

| VDDIO_MEM_S3 | 1.2 V DRAM supply voltage |

| VDDIO_MEM_S3_SENSE | VDDIO_MEM_S3 voltage monitor pin |

| VDDP | |

| VDDP_SENSE | VDDP voltage monitor pin |

| VDDP_S5 | |

| VDD_18 | 1.8 V supply voltage |

| VDD_18_S5 | Always on 1.8 V supply voltage |

| VDD_33 | 3.3 V supply voltage |

| VDD_33_S5 | Always on 3.3 V supply voltage |

| VSS | Ground |

| VSS_SENSE_A | VSS sense pin for voltage regulator |

| VSS_SENSE_B | VSS sense pin for voltage regulator |

| CORETYPE[1:0] | Processor Core Type Indicator |

| AM4R1 | Processor Family Revision Identifier |

| RSVD | Reserved |

See also[edit]

| designer | AMD + |

| first launched | September 2016 + |

| instance of | package + |

| market segment | Desktop + |

| microarchitecture | Zen + |

| name | Socket AM4 + |

| package | OPGA-1331 + |

| package contacts | 1,331 + |

| package length | 40 mm (4 cm, 1.575 in) + |

| package pitch | 1 mm (0.0394 in) + |

| package type | Organic Micro Pin Grid Array + |

| package width | 40 mm (4 cm, 1.575 in) + |

| socket | Socket AM4 + |

| tdp | 105 W (105,000 mW, 0.141 hp, 0.105 kW) + |