(Socket TR4) |

(→Pin Description) |

||

| (10 intermediate revisions by 3 users not shown) | |||

| Line 1: | Line 1: | ||

| − | {{amd title|Socket TR4 (sTR4)|package}} | + | {{amd title|Socket TR4 (SP3r2, sTR4)|package}} |

| − | {{package}} | + | {{package |

| − | '''Socket TR4''' | + | |name=Socket TR4 |

| + | |designer=AMD | ||

| + | |first announced=May 16, 2017 | ||

| + | |first launched=August 10, 2017 | ||

| + | |market=Desktop | ||

| + | |market 2=Workstation | ||

| + | |microarch=Zen | ||

| + | |microarch 2=Zen+ | ||

| + | |tdp=180 W | ||

| + | |tdp 2=250 W | ||

| + | |package name=TR4 | ||

| + | |package name 2=FCLGA-4094 | ||

| + | |package type=FC-OLGA | ||

| + | |package contacts=4094 | ||

| + | |package dimension=75.40 mm | ||

| + | |package dimension 2=58.50 mm | ||

| + | |package dimension 3=6.26 mm | ||

| + | |package pitch=0.87 mm | ||

| + | |package pitch 2=1.00 mm | ||

| + | |socket type=SM-LGA | ||

| + | |socket name=TR4 | ||

| + | |socket name 2=SP3r2 | ||

| + | |socket name 3=sTR4 | ||

| + | |successor=Socket sTRX4 | ||

| + | |successor link=amd/packages/socket strx4 | ||

| + | |successor 2=Socket sWRX8 | ||

| + | |successor 2 link=amd/packages/socket swrx8 | ||

| + | }} | ||

| + | '''Socket TR4''' a.k.a. '''Socket SP3r2''' and '''sTR4''' is a microprocessor socket designed by [[AMD]] for their first and second generation {{amd|Ryzen Threadripper}} high-end desktop processors. It was superseeded by {{\\|Socket sTRX4}}. Contemporary mainstream desktop processors use {{\\|Socket AM4}}, server processors {{\\|Socket SP3}}. | ||

| + | |||

| + | Socket TR4 is mechanically identical and almost pin-compatible to Socket SP3 and the sockets sTRX4 and sWRX8 also derived from it, but differs by the number of memory channels and I/O interfaces available: SP3 processors use [[DDR4]] {{abbr|RDIMM}}s on up to eight memory channels, sWRX8 processors {{abbr|UDIMM}}s or RDIMMs, while TR4 and sTRX4 processors support only UDIMMs on up to four memory channels. TR4 and sTRX4 omit four of eight PCIe interfaces present on Socket SP3 and sWRX8, but TR4 processors also pin out four additional USB ports, a {{abbr|HDA}} interface, and other client-oriented features which are not supported by the other infrastructures. | ||

| + | |||

| + | == Overview == | ||

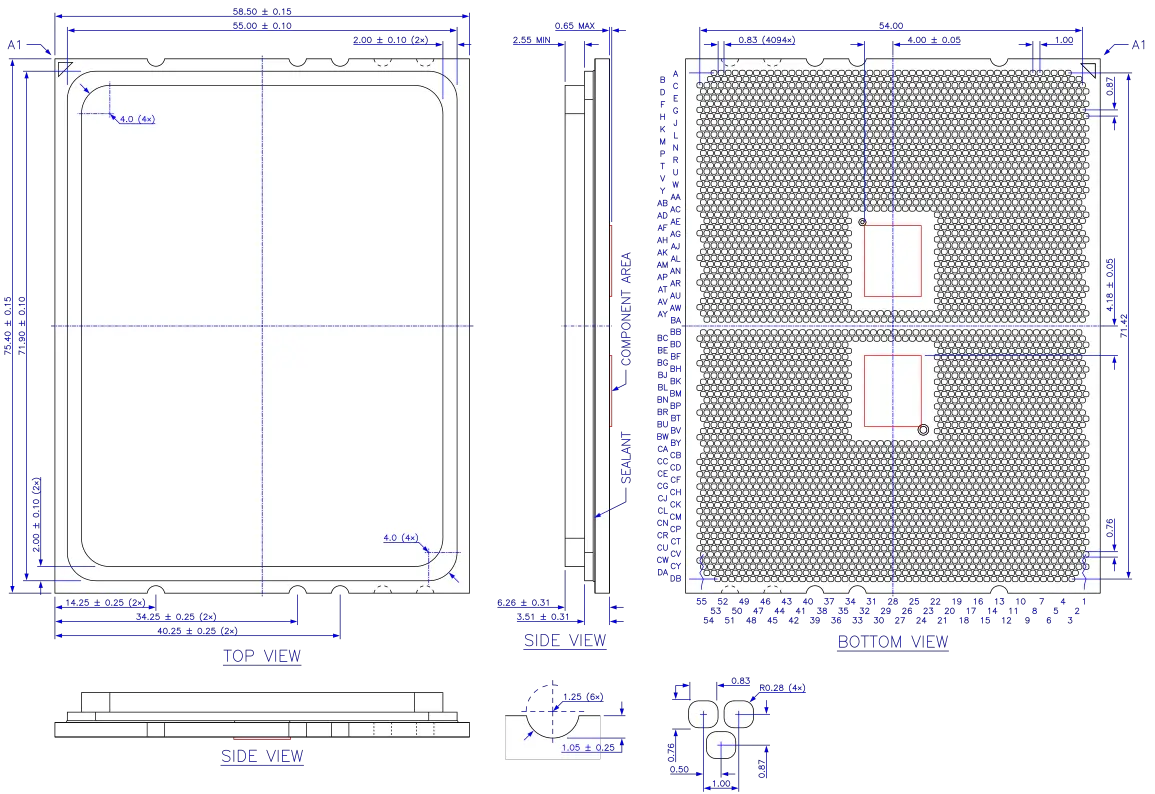

| + | Socket TR4 is a zero insertion force, screw actuated, [[wikipedia:Surface-mount technology|surface-mount]] [[land grid array]] socket for use with a 4094-contact, 1.00 mm × 0.87 mm interstitial pitch, organic land grid array CPU package. | ||

| + | |||

| + | It supports four channels of 72-bit [[DDR4]] memory with up to two DIMMs per channel, four 16-lane PCIe Gen 3 I/O interfaces, eight USB 3.1 Gen 1 ports, and up to 16 SATA Gen 3 ports. 8-layer motherboards are required to route these signals. | ||

| + | |||

| + | The following AMD processor families use Socket TR4: | ||

| + | {| class="wikitable" | ||

| + | ! || CPU Family || Microarch. || Process || Products | ||

| + | |- | ||

| + | |rowspan="2"|Type 0 | ||

| + | |rowspan="2"|{{amd|CPUID#Family 23 (17h)|Family 17h}} Models 00h–0Fh | ||

| + | |{{amd|Zen|l=arch}} | ||

| + | |[[GlobalFoundries]] [[14 nm]] (14LPP) | ||

| + | |{{amd|threadripper#1900-Series (Zen)|Threadripper 1900}} "{{amd|Whitehaven|l=core}}" (Model 01h) | ||

| + | |- | ||

| + | |{{amd|Zen+|l=arch}} | ||

| + | |[[GlobalFoundries]] [[12 nm]] (12LP) | ||

| + | |{{amd|threadripper#2900-Series (Zen+)|Threadripper 2900}} "{{amd|Colfax|l=core}}" (Model 08h) | ||

| + | |} | ||

| + | |||

| + | Codenames of AMD TR4 reference platforms ({{abbr|CRB}}s) are "Whitehaven", "Whitehaven OPS", and "Whitehaven {{abbr|DAP}}". | ||

| + | |||

| + | == Package Description == | ||

| + | The TR4 CPU package is lidded, has a 58.50 mm × 75.40 mm organic substrate with [[flip chip]] die attachment, and 4094 nickel and gold plated land pads. It ships with a carrier frame pre-installed. The carrier frame, made from an orange colored polycarbonate material, is a part of the package loading mechanism and remains on the package in the socket. | ||

| + | |||

| + | The package substrate has six keying notches along the short edges preventing it from being inserted 180 degrees rotated into the carrier frame or socket, or in an incompatible socket with mismatching keying features. Four additional positions are reserved for future models. However all sockets SP3, TR4, sTRX4, and sWRX8, and all processors for these sockets have the same keying. TR4 packages are electrically keyed by pin [[#SP3R1|SP3R2]] and Socket TR4 motherboards are not supposed to power up the socket if a SP3 or sWRX8 processor is installed.<!--AMD-55809 Sec 11.4--> To boot the processor they must also provide compatible firmware. | ||

| + | |||

| + | The lid a.k.a. integrated heat spreader has an internal support bar bisecting the dies in the package. [[wikipedia:Decoupling capacitor|Decoupling capacitors]] are placed under the lid around the chiplet periphery on the top side, and in two windows in the pad grid on the bottom side. TR4 packages use solder as {{abbr|TIM}} between the dies and the lid with <math>k</math> ≈ 62 W/(m⋅K).<!--AMD-55816--> A triangular symbol on both sides of the substrate marks the location of pin A1, with corresponding markings on the socket. | ||

| + | |||

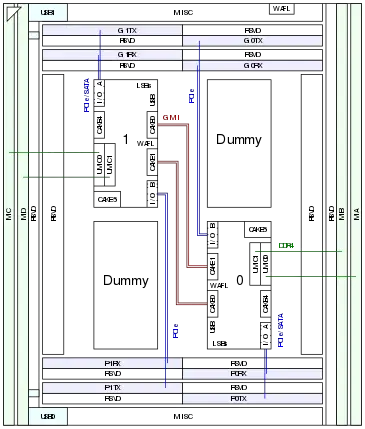

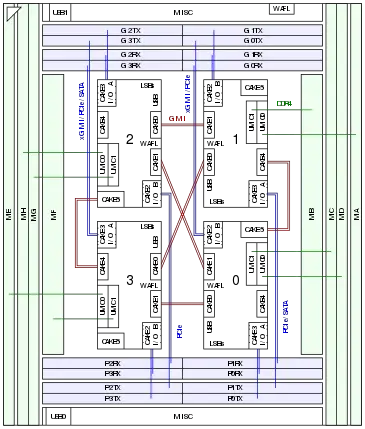

| + | TR4 is a [[multi-chip package]] integrating two identical dies and two dummies for mechanical stability. Each die contains eight CPU cores and implements one half of the processor's memory and I/O interfaces. Model 01h uses "Zeppelin" ZP-B1 dies, Model 08h "Pinnacle Ridge" PiR-B2 dies.<!--AMD-55449--> AMD used the same dies in various revisions for first generation EPYC server and embedded processors, and the first two generations of Ryzen desktop processors without {{abbr|iGPU}}; see {{amd|CPUID#Family 23 (17h)|CPU Family 17h}}. The dummies were shown to be patterned dies and are probably rejects. TR4 processors utilize customized, single-ended, 4:1 Serializer–Deserializer (SerDes) links on several package routing layers, 32 lanes wide in each direction, to connect the dies. The SerDes run at {{abbr|FCLK|Infinity Fabric clock}} so for instance a 1.33 GHz FCLK coupled to the bus clock of DDR4-2666 SDRAM gives a raw data rate of 5.33 GT/s per lane or 21.33 GB/s in each direction.<!--Beck2018, Naffziger2020, EPYC Tech Day 2017-06-20--> | ||

| + | |||

| + | Socket TR4 was derived from {{\\|Socket SP3}}, avoiding the expenses of designing and producing another socket for a small market segment. AMD actually designed a more compact dual-die {{abbr|BGA}} package {{\\|SP4}} for {{amd|epyc embedded#3000 Series (Zen)|EPYC 3000}} embedded processors. TR4 packages are not merely EPYC processors with two disabled dies, the signal routing is different. Only the four memory channels pinned out closest to the package edge, and only four of the eight PCIe interfaces are connected to the two active dies. The interfaces were renumbered to reflect this. Two, rather than just one, Data Fabric on-package links connect the dies. Since each die actually implements four USB ports and an audio controller some unused lands were repurposed to pin out these signals in addition to the four USB ports supported by Socket SP3. | ||

| + | |||

| + | {| style="text-align: center;" | ||

| + | | [[file:Socket TR4 routing.svg]] || || [[file:Socket SP3 Type-0 routing.svg]] | ||

| + | |- | ||

| + | | TR4 package top view, not to scale || || SP3 Type-0 package for comparison | ||

| + | |} | ||

| + | |||

| + | {{abbr|CAKE}}s extend the Data Fabric transport layer off-chip by connecting to a CAKE in another die. Their {{abbr|PCS}} interface drives a {{abbr|GMI}} (same socket) or {{abbr|xGMI}} (different socket) physical link. Each die has two 16-lane multi-function I/O interfaces. Type A supports the PCIe, SATA, and XGBE protocols, Type B only PCIe. CAKE2/CAKE3 and the I/O controllers share a 16-lane [[wikipedia:Physical_layer#PHY|PHY]] group. {{abbr|IF:CS}}0 and CS1 are the Data Fabric's interface to the memory controllers, {{abbr|UMC}}0 and UMC1 respectively. Not shown are the Control Fabric interfaces which use {{abbr|TWIX}} (same socket) or {{abbr|WAFL}} (different socket) physical links, USB signals (USB0 group from die 0, USB1 from die 1), and low speed busses. For details and the on-chip topology see AMD {{amd|Infinity Fabric}}. {{clear}} | ||

| + | |||

| + | Socket TR4 has four 16-lane multi-function I/O interfaces P0, P1, G0, and G1. All of these interfaces can be configured as PCIe link, some lanes alternatively as SATA link. The xGMI, S-Link, and XGBE protocols are not supported on this socket, nor is the WAFL interface. (xGMI and WAFL connect the Data and Control Fabrics of each processor on dual-socket server platforms. S-Link is a cache coherent link to {{abbr|CCIX}} memory expanders. XGBE is a backplane Ethernet link with data rates up to 10 Gbit/s.) | ||

| + | |||

| + | == Socket Description == | ||

| + | Socket TR4 (SP3r2) is mechanically identical to {{\\|Socket SP3#Socket Description|Socket SP3}}. | ||

| + | |||

| + | == Feature Summary == | ||

| + | * Lidded [[land grid array]] package, 75.40 mm × 58.50 mm | ||

| + | ** 4094 contacts in a 82 × 55 grid with 0.87 mm × 1.00 mm interstitial pitch | ||

| + | ** Organic substrate, [[flip chip]] die attachment | ||

| + | |||

| + | * 4 × 64/72 bit DDR4 SDRAM interface | ||

| + | ** Up to 1467 MHz, PC4-23466 (DDR4-2933), 93.87 GB/s total raw bandwidth, not overclocked | ||

| + | ** Up to 2 DIMMs/channel; {{abbr|SR}}/{{abbr|DR}} {{abbr|UDIMM}}s only | ||

| + | ** ECC support | ||

| + | ** Memory addressing up to ? GiB/channel | ||

| + | ** Max. total memory capacity 256 GiB using eight 32 GiB DIMMs | ||

| + | |||

| + | * Four multi-function I/O interfaces P0, P1, G0, G1 | ||

| + | :{| class="wikitable" style="text-align:center" | ||

| + | |Lane||15||14||13||12||11||10||9||8||7||6||5||4||3||2||1||0 | ||

| + | |- | ||

| + | |rowspan="5"|PCIe||colspan="16"|x16 | ||

| + | |- | ||

| + | |colspan="8"|x8||colspan="8"|x8 | ||

| + | |- | ||

| + | |colspan="4"|x4||colspan="4"|x4||colspan="4"|x4||colspan="4"|x4 | ||

| + | |- | ||

| + | |colspan="2"|x2||colspan="2"|x2||colspan="2"|x2||colspan="2"|x2||colspan="2"|x2||colspan="2"|x2||colspan="2"|x2||colspan="2"|x2 | ||

| + | |- | ||

| + | |x1||x1||x1||x1||x1||x1||x1||x1||x1||x1||x1||x1||x1||x1||x1||x1 | ||

| + | |- | ||

| + | |SATA||colspan="8"| ||7||6||5||4||3||2||1||0 | ||

| + | |- | ||

| + | | ||colspan="4"|PHY 4||colspan="4"|PHY 3||colspan="4"|PHY 2||colspan="2"|PHY 1||colspan="2"|PHY 0 | ||

| + | |} | ||

| + | :* PCIe Gen 1, 2, 3 (8 GT/s) protocol supported on all interfaces | ||

| + | :** 16 lanes, up to 8 ports per interface configurable x16, x8, x4, x2, x1 with power-of-two alignment (e.g. 1x4 + 4x1 + 1x8) | ||

| + | :** Max. 7 PCIe ports in each 8-lane subset (e.g. 0x8 + 8x1 is not possible) | ||

| + | :** Max. 7 PCIe ports per interface if any lane is configured as SATA port | ||

| + | :** Different PCIe generations supported on the ports in the same interface | ||

| + | :** Lane polarity inversion, per port lane reversal | ||

| + | :** Up to 60 PCIe lanes total (one x4 link reserved for chipset attachment) | ||

| + | |||

| + | :* SATA Gen 1, 2, 3 (6 Gb/s) protocol supported on the lower 8 lanes of P0 and G1 | ||

| + | :** P0: SATA00-07, G1: SATA10-17 | ||

| + | :** Up to 16 SATA ports total | ||

| + | |||

| + | :* Five {{abbr|PHY}} groups on each interface | ||

| + | :** Lanes sharing a PHY group must use the same protocol (PCIe, SATA) | ||

| + | |||

| + | * 8 × USB 1.1, 2.0, 3.1 Gen 1 (5 Gb/s) | ||

| + | |||

| + | * Low speed interfaces (some sharing pins): | ||

| + | ** {{abbr|HDA}} 1.0 | ||

| + | ** 2 × 4-wire or 4 × 2-wire {{abbr|UART}} modeled after the [[wikipedia:16550 UART|16550]] | ||

| + | ** {{abbr|LPC}} | ||

| + | ** 1/2/4-bit {{abbr|SPI/eSPI}} up to 100 MHz (SPI) and 66 MHz (eSPI) | ||

| + | ** 6 × {{abbr|I<sup>2</sup>C}} | ||

| + | ** 2 × {{abbr|SMBus}} | ||

| + | ** 2 × SATA {{abbr|DevSlp}} | ||

| + | ** 89 × {{abbr|GPIO}} | ||

| + | ** Sideband Interface ({{abbr|SB-TSI}}) | ||

| + | ** 2 × Serial VID Interface (SVI2) | ||

| + | ** {{abbr|JTAG}} | ||

| + | |||

| + | == Chipset == | ||

| + | TR4 processors are {{abbr|SoC}}s with an integrated controller hub so they do not require a chipset, but are paired with the AMD {{amd|X399}} chipset (AMD 300-Series) serving as I/O expander. | ||

| + | |||

| + | The chipset is attached with an x4 PCIe Gen 3 link and can provide the following additional interfaces: | ||

| + | * 8 lanes PCIe Gen 1, 2 (5 GT/s) | ||

| + | * 2 × SATA Express (two PCIe lanes or two SATA ports each) | ||

| + | * 4 × SATA Gen 1, 2, 3 (6 Gb/s) | ||

| + | * 2 × USB 1.1, 2.0, 3.1 Gen 2 (10 Gb/s) | ||

| + | * 6 × USB 1.1, 2.0, 3.1 Gen 1 (5 Gb/s) | ||

| + | * 6 × USB 1.1, 2.0 | ||

| + | |||

| + | == Processors using Socket TR4 == | ||

| + | <!-- NOTE: | ||

| + | This table is generated automatically from the data in the actual articles. | ||

| + | If a microprocessor is missing from the list, an appropriate article for it needs to be | ||

| + | created and tagged accordingly. | ||

| + | |||

| + | Missing a chip? please dump its name here: https://en.wikichip.org/wiki/WikiChip:wanted_chips | ||

| + | --> | ||

| + | {{comp table start}} | ||

| + | <table class="comptable sortable"> | ||

| + | {{comp table header|cols|Cores|Threads|L2$|L3$|Base|Turbo|Memory|{{abbr|TDP}}|Launched|Price|{{abbr|OPN}}}} | ||

| + | {{#ask: [[Category:microprocessor models by amd]] [[socket::~*TR4||~*SP3r2]] | ||

| + | |?full page name | ||

| + | |?model number | ||

| + | |?core count | ||

| + | |?thread count | ||

| + | |?l2$ size | ||

| + | |?l3$ size | ||

| + | |?base frequency#GHz | ||

| + | |?turbo frequency#GHz | ||

| + | |?supported memory type | ||

| + | |?tdp | ||

| + | |?first launched | ||

| + | |?release price | ||

| + | |?part number | ||

| + | |sort=model number | ||

| + | |format=template | ||

| + | |template=proc table 3 | ||

| + | |userparam=13 | ||

| + | |mainlabel=- | ||

| + | |valuesep=,<br/> | ||

| + | }} | ||

| + | {{comp table count|ask=[[Category:microprocessor models by amd]] [[socket::~*TR4||~*SP3r2]]}} | ||

| + | </table> | ||

| + | {{comp table end}} | ||

| + | |||

| + | == Photos == | ||

| + | {{empty section}} | ||

| + | |||

| + | == Package Diagrams == | ||

| + | <!-- :[[File:sp3-details.png|1000px]] --><!--AMD-55423-3.0 (public version) Fig 1--> | ||

| + | [[File:LGA-4094 SP3r2 diag.svg]] <!--based on AMD-55814-1.03 FDS SP3r2--> | ||

| + | |||

| + | TR4 package. All dimensions in millimeters. | ||

| + | |||

| + | == Socket Diagrams == | ||

| + | |||

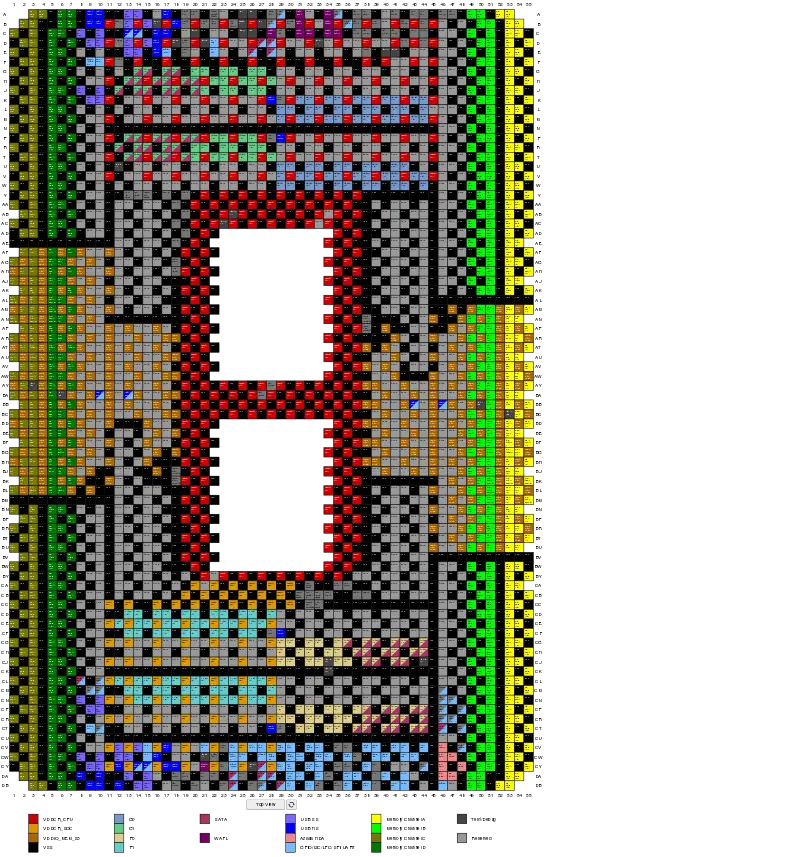

| + | == Pin Map == | ||

| + | [[File:Socket TR4 pinmap.svg|800px]] | ||

| + | |||

| + | Socket TR4 (SP3r2) pinout, top view. This is a preview, click for a larger image and other views. | ||

| + | |||

| + | <!-- | ||

| + | AGPIO3/WOL0,CY24,MB_DQS_L[4],CA49,RSVD,E37,RSVD,BK46,VDDCR_CPU,H27,VDDIO_MEM_S3_CD,AK11,VSS,AA37,VSS,BW45 | ||

| + | AGPIO4/WOL1,E17,MB_DQS_L[5],CG49,RSVD,E43,RSVD,BK48,VDDCR_CPU,H30,VDDIO_MEM_S3_CD,AL2,VSS,AA38,VSS,BW48 | ||

| + | AGPIO5/DEVSLP0/WOL2,DB24,MB_DQS_L[6],CN49,RSVD,E44,RSVD,BL12,VDDCR_CPU,H33,VDDIO_MEM_S3_CD,AL4,VSS,AA40,VSS,BW50 | ||

| + | AGPIO6/DEVSLP1/WOL3,DA24,MB_DQS_L[7],CW49,RSVD,E46,RSVD,BL13,VDDCR_CPU,H36,VDDIO_MEM_S3_CD,AL7,VSS,AA43,VSS,BW52 | ||

| + | AGPIO8,DB46,MB_DQS_L[8],AG51,RSVD,E47,RSVD,BL15,VDDCR_CPU,H39,VDDIO_MEM_S3_CD,AL9,VSS,AA45,VSS,BW55 | ||

| + | AGPIO9_0/SGPIO0_DATAOUT/MDIO1_SCL,DB29,MB_DQS_L[9],D50,RSVD,F41,RSVD,BL16,VDDCR_CPU,H42,VDDIO_MEM_S3_CD,AM1,VSS,AA48,VSS,BY1 | ||

| + | AGPIO23_0/SGPIO0_LOAD/MDIO1_SDA,CY27,MB_DQS_L[10],K50,RSVD,F42,RSVD,BL39,VDDCR_CPU,H45,VDDIO_MEM_S3_CD,AM4,VSS,AA50,VSS,BY4 | ||

| + | AGPIO40_0/SGPIO0_DATAIN/MDIO0_SDA,DA27,MB_DQS_L[11],T50,RSVD,F44,RSVD,BL41,VDDCR_CPU,K11,VDDIO_MEM_S3_CD,AM6,VSS,AA52,VSS,BY6 | ||

| + | ALERT_L,CY39,MB_DQS_L[12],AB50,RSVD,F46,RSVD,BL42,VDDCR_CPU,K15,VDDIO_MEM_S3_CD,AM8,VSS,AA55,VSS,BY8 | ||

| + | AZ_BITCLK,DA47,MB_DQS_L[13],CB51,RSVD,F48,RSVD,BL44,VDDCR_CPU,K18,VDDIO_MEM_S3_CD,AM11,VSS,AB4,VSS,BY11 | ||

| + | AZ_RST_L,CY46,MB_DQS_L[14],CH51,RSVD,G8,RSVD,BL46,VDDCR_CPU,K21,VDDIO_MEM_S3_CD,AN2,VSS,AB6,VSS,BY13 | ||

| + | AZ_SDIN0,CY48,MB_DQS_L[15],CP51,RSVD,G10,RSVD,BL47,VDDCR_CPU,K24,VDDIO_MEM_S3_CD,AN4,VSS,AB8,VSS,BY16 | ||

| + | AZ_SDIN1,CW46,MB_DQS_L[16],CY51,RSVD,G12,RSVD,BM12,VDDCR_CPU,K27,VDDIO_MEM_S3_CD,AN7,VSS,AB11,VSS,BY18 | ||

| + | AZ_SDIN2,CW47,MB_DQS_L[17],AH50,RSVD,G29,RSVD,BM14,VDDCR_CPU,K30,VDDIO_MEM_S3_CD,AN9,VSS,AB13,VSS,BY20 | ||

| + | AZ_SDOUT,CV46,MB_EVENT_L,BG51,RSVD,G30,RSVD,BM15,VDDCR_CPU,K33,VDDIO_MEM_S3_CD,AP4,VSS,AB16,VSS,BY24 | ||

| + | AZ_SYNC,DA46,MB_PAROUT,BG49,RSVD,G32,RSVD,BM17,VDDCR_CPU,K36,VDDIO_MEM_S3_CD,AP6,VSS,AB18,VSS,BY26 | ||

| + | BLINK/AGPIO11,CW36,MB_RAS_L_ADD[16],BK51,RSVD,G33,RSVD,BM40,VDDCR_CPU,K39,VDDIO_MEM_S3_CD,AP8,VSS,AB20,VSS,BY28 | ||

| + | CLK_REQ0_0_L/AGPIO92_0,CT48,MB_RESET_L,AM50,RSVD,G35,RSVD,BM41,VDDCR_CPU,K42,VDDIO_MEM_S3_CD,AP11,VSS,AB22,VSS,BY30 | ||

| + | CLK_REQ1_0_L/AGPIO115_0,CP48,MB_WE_L_ADD[14],BL51,RSVD,G36,RSVD,BM43,VDDCR_CPU,K45,VDDIO_MEM_S3_CD,AP13,VSS,AB26,VSS,BY32 | ||

| + | CLK_REQ1_1_L/EGPIO115_1,CM9,MB_ZVSS,BB51,RSVD,G38,RSVD,BM44,VDDCR_CPU,M11,VDDIO_MEM_S3_CD,AP16,VSS,AB28,VSS,BY34 | ||

| + | CLK_REQ2_0_L/AGPIO116_0,CR47,MC0_CKE[0],BK2,RSVD,G39,RSVD,BM46,VDDCR_CPU,M15,VDDIO_MEM_S3_CD,AR2,VSS,AB30,VSS,BY36 | ||

| + | CLK_REQ2_1_L/EGPIO116_1,CM10,MC0_CKE[1],BK3,RSVD,G41,RSVD,BM48,VDDCR_CPU,M18,VDDIO_MEM_S3_CD,AR4,VSS,AB32,VSS,BY39 | ||

| + | CLK_REQ3_0_L/EGPIO131_0,CP46,MC0_CLK_H[0],BA1,RSVD,G42,RSVD,BN8,VDDCR_CPU,M21,VDDIO_MEM_S3_CD,AR7,VSS,AB36,VSS,BY42 | ||

| + | CLK_REQ3_1_L/EGPIO131_1,CT10,MC0_CLK_H[1],AW1,RSVD,G44,RSVD,BN10,VDDCR_CPU,M24,VDDIO_MEM_S3_CD,AR9,VSS,AB38,VSS,BY45 | ||

| + | CLK_REQG_0_L/OSCIN/EGPIO132_0,CR46,MC0_CLK_L[0],AY2,RSVD,G46,RSVD,BN12,VDDCR_CPU,M27,VDDIO_MEM_S3_CD,AR11,VSS,AB39,VSS,BY47 | ||

| + | CLK_REQG_1_L/EGPIO132_1,CL10,MC0_CLK_L[1],AV2,RSVD,G47,RSVD,BN13,VDDCR_CPU,M30,VDDIO_MEM_S3_CD,AR14,VSS,AB42,VSS,BY49 | ||

| + | CORETYPE,C29,MC0_CS_L[0],AM3,RSVD,H9,RSVD,BN15,VDDCR_CPU,M33,VDDIO_MEM_S3_CD,AR17,VSS,AB45,VSS,BY52 | ||

| + | CPU_PRESENT_L,B24,MC0_CS_L[1],AH2,RSVD,H10,RSVD,BN16,VDDCR_CPU,M36,VDDIO_MEM_S3_CD,AR18,VSS,AB47,VSS,BY54 | ||

| + | DBREQ_L,B25,MC0_ODT[0],AL3,RSVD,H29,RSVD,BN39,VDDCR_CPU,M39,VDDIO_MEM_S3_CD,AT1,VSS,AB49,VSS,CA2 | ||

| + | EGPIO9_1/SGPIO1_DATAOUT/MDIO3_SCL,D28,MC0_ODT[1],AG1,RSVD,H31,RSVD,BN41,VDDCR_CPU,M42,VDDIO_MEM_S3_CD,AT4,VSS,AB52,VSS,CA4 | ||

| + | EGPIO23_1/SGPIO1_LOAD/MDIO3_SDA,E28,MC1_CKE[0],BJ3,RSVD,H32,RSVD,BN42,VDDCR_CPU,M45,VDDIO_MEM_S3_CD,AT6,VSS,AB54,VSS,CA7 | ||

| + | EGPIO40_1/SGPIO1_DATAIN/MDIO2_SDA,D27,MC1_CKE[1],BL1,RSVD,H34,RSVD,BN44,VDDCR_CPU,P11,VDDIO_MEM_S3_CD,AT8,VSS,AC2,VSS,CA9 | ||

| + | EGPIO42,CV21,MC1_CLK_H[0],AW3,RSVD,H35,RSVD,BN46,VDDCR_CPU,P15,VDDIO_MEM_S3_CD,AT11,VSS,AC4,VSS,CA11 | ||

| + | EGPIO70,CW25,MC1_CLK_H[1],AU1,RSVD,H37,RSVD,BN47,VDDCR_CPU,P18,VDDIO_MEM_S3_CD,AT13,VSS,AC7,VSS,CA14 | ||

| + | EGPIO92_1,CT9,MC1_CLK_L[0],AV3,RSVD,H38,RSVD,BP9,VDDCR_CPU,P21,VDDIO_MEM_S3_CD,AT16,VSS,AC9,VSS,CA17 | ||

| + | ESPI_ALERT_L/LDRQ0_L/EGPIO108,CW24,MC1_CLK_L[1],AT2,RSVD,H40,RSVD,BP10,VDDCR_CPU,P24,VDDIO_MEM_S3_CD,AU2,VSS,AC11,VSS,CA19 | ||

| + | ESPI_RESET_L/KBRST_L/AGPIO129,CY29,MC1_CS_L[0],AM2,RSVD,H41,RSVD,BP12,VDDCR_CPU,P27,VDDIO_MEM_S3_CD,AU4,VSS,AC14,VSS,CA23 | ||

| + | FANIN0/AGPIO84_0/NMI,CM46,MC1_CS_L[1],AJ1,RSVD,H43,RSVD,BP14,VDDCR_CPU,P30,VDDIO_MEM_S3_CD,AU7,VSS,AC17,VSS,CA25 | ||

| + | FANIN1/EGPIO84_1,F9,MC1_ODT[0],AK2,RSVD,H44,RSVD,BP15,VDDCR_CPU,P33,VDDIO_MEM_S3_CD,AU9,VSS,AC19,VSS,CA27 | ||

| + | FANOUT0/AGPIO85_0,CN47,MC1_ODT[1],AF2,RSVD,H46,RSVD,BP17,VDDCR_CPU,P36,VDDIO_MEM_S3_CD,AU11,VSS,AC21,VSS,CA29 | ||

| + | FANOUT1/EGPIO85_1,F10,MC_ACT_L,BH3,RSVD,H48,RSVD,BP40,VDDCR_CPU,P39,VDDIO_MEM_S3_CD,AU14,VSS,AC25,VSS,CA31 | ||

| + | FORCE_SELFREFRESH,A22,MC_ADD[0],AR1,RSVD,J29,RSVD,BP41,VDDCR_CPU,P42,VDDIO_MEM_S3_CD,AU17,VSS,AC27,VSS,CA33 | ||

| + | G0B_ZVSS,K29,MC_ADD[1],BC1,RSVD,J30,RSVD,BP43,VDDCR_CPU,P45,VDDIO_MEM_S3_CD,AU18,VSS,AC29,VSS,CA34 | ||

| + | G0_RXN[0],V29,MC_ADD[2],BB2,RSVD,J32,RSVD,BP44,VDDCR_CPU,T11,VDDIO_MEM_S3_CD,AV4,VSS,AC31,VSS,CA37 | ||

| + | G0_RXN[1],U29,MC_ADD[3],BB3,RSVD,J33,RSVD,BP46,VDDCR_CPU,T15,VDDIO_MEM_S3_CD,AV6,VSS,AC35,VSS,CA38 | ||

| + | G0_RXN[2],W30,MC_ADD[4],BC3,RSVD,J35,RSVD,BP48,VDDCR_CPU,T18,VDDIO_MEM_S3_CD,AV8,VSS,AC37,VSS,CA40 | ||

| + | G0_RXN[3],V32,MC_ADD[5],BD2,RSVD,J36,RSVD,BR8,VDDCR_CPU,T21,VDDIO_MEM_S3_CD,AV11,VSS,AC38,VSS,CA43 | ||

| + | G0_RXN[4],U32,MC_ADD[6],BE1,RSVD,J38,RSVD,BR10,VDDCR_CPU,T24,VDDIO_MEM_S3_CD,AV13,VSS,AC40,VSS,CA45 | ||

| + | G0_RXN[5],W33,MC_ADD[7],BE3,RSVD,J39,RSVD,BR12,VDDCR_CPU,T27,VDDIO_MEM_S3_CD,AV16,VSS,AC43,VSS,CA48 | ||

| + | G0_RXN[6],V35,MC_ADD[8],BD3,RSVD,J41,RSVD,BR13,VDDCR_CPU,T30,VDDIO_MEM_S3_CD,AW2,VSS,AC45,VSS,CA50 | ||

| + | G0_RXN[7],U35,MC_ADD[9],BG1,RSVD,J42,RSVD,BR15,VDDCR_CPU,T33,VDDIO_MEM_S3_CD,AW4,VSS,AC48,VSS,CA52 | ||

| + | G0_RXN[8],W36,MC_ADD[10],AR3,RSVD,J44,RSVD,BR16,VDDCR_CPU,T36,VDDIO_MEM_S3_CD,AW7,VSS,AC50,VSS,CB1 | ||

| + | G0_RXN[9],V38,MC_ADD[11],BF2,RSVD,J46,RSVD,BR39,VDDCR_CPU,T39,VDDIO_MEM_S3_CD,AW9,VSS,AC52,VSS,CB4 | ||

| + | G0_RXN[10],U38,MC_ADD[12],BF3,RSVD,J47,RSVD,BR41,VDDCR_CPU,T42,VDDIO_MEM_S3_CD,AW11,VSS,AC55,VSS,CB6 | ||

| + | G0_RXN[11],W39,MC_ADD[13],AK3,RSVD,K13,RSVD,BR42,VDDCR_CPU,T45,VDDIO_MEM_S3_CD,AW14,VSS,AD1,VSS,CB8 | ||

| + | G0_RXN[12],V41,MC_ADD_17,AJ3,RSVD,K14,RSVD,BR44,VDDCR_CPU,V11,VDDIO_MEM_S3_CD,AW17,VSS,AD4,VSS,CB11 | ||

| + | G0_RXN[13],U41,MC_ALERT_L,BG3,RSVD,K16,RSVD,BR46,VDDCR_CPU,V15,VDDIO_MEM_S3_CD,AW18,VSS,AD6,VSS,CB13 | ||

| + | G0_RXN[14],W42,MC_BANK[0],AP3,RSVD,K17,RSVD,BR47,VDDCR_CPU,V18,VDDIO_MEM_S3_CD,AY1,VSS,AD8,VSS,CB16 | ||

| + | G0_RXN[15],V44,MC_BANK[1],AP2,RSVD,K19,RSVD,BT9,VDDCR_CPU,V21,VDDIO_MEM_S3_CD,AY4,VSS,AD11,VSS,CB18 | ||

| + | G0_RXP[0],W29,MC_BG[0],BH2,RSVD,K20,RSVD,BT10,VDDCR_CPU,V24,VDDIO_MEM_S3_CD,AY6,VSS,AD13,VSS,CB20 | ||

| + | G0_RXP[1],U30,MC_BG[1],BJ1,RSVD,K22,RSVD,BT12,VDDCR_CPU,V27,VDDIO_MEM_S3_CD,AY8,VSS,AD16,VSS,CB22 | ||

| + | G0_RXP[2],V31,MC_CAS_L_ADD[15],AL1,RSVD,K23,RSVD,BT14,VDDCR_CPU,V30,VDDIO_MEM_S3_CD,AY11,VSS,AD18,VSS,CB24 | ||

| + | G0_RXP[3],W32,MC_CHECK[0],BV2,RSVD,K25,RSVD,BT15,VDDCR_CPU,V33,VDDIO_MEM_S3_CD,AY13,VSS,AD20,VSS,CB26 | ||

| + | G0_RXP[4],U33,MC_CHECK[1],BU1,RSVD,K26,RSVD,BT17,VDDCR_CPU,V36,VDDIO_MEM_S3_CD,AY16,VSS,AD22,VSS,CB28 | ||

| + | G0_RXP[5],V34,MC_CHECK[2],BP2,RSVD,K46,RSVD,BT40,VDDCR_CPU,V39,VDDIO_MEM_S3_CD,BA2,VSS,AD36,VSS,CB30 | ||

| + | G0_RXP[6],W35,MC_CHECK[3],BN1,RSVD,K48,RSVD,BT41,VDDCR_CPU,V42,VDDIO_MEM_S3_CD,BA4,VSS,AD38,VSS,CB35 | ||

| + | G0_RXP[7],U36,MC_CHECK[4],BV3,RSVD,L8,RSVD,BT43,VDDCR_CPU,V45,VDDIO_MEM_S3_CD,BA7,VSS,AD39,VSS,CB36 | ||

| + | G0_RXP[8],V37,MC_CHECK[5],BU3,RSVD,L10,RSVD,BT44,VDDCR_CPU,Y21,VDDIO_MEM_S3_CD,BA9,VSS,AD42,VSS,CB39 | ||

| + | G0_RXP[9],W38,MC_CHECK[6],BP3,RSVD,L12,RSVD,BT46,VDDCR_CPU,Y23,VDDIO_MEM_S3_CD,BA11,VSS,AD45,VSS,CB42 | ||

| + | G0_RXP[10],U39,MC_CHECK[7],BN3,RSVD,L14,RSVD,BT48,VDDCR_CPU,Y25,VDDIO_MEM_S3_CD,BA14,VSS,AD47,VSS,CB45 | ||

| + | G0_RXP[11],V40,MC_C[0],AF3,RSVD,L15,RSVD,BU8,VDDCR_CPU,Y27,VDDIO_MEM_S3_CD,BA17,VSS,AD49,VSS,CB47 | ||

| + | G0_RXP[12],W41,MC_C[1],AG3,RSVD,L17,RSVD,BU10,VDDCR_CPU,Y29,VDDIO_MEM_S3_CD,BA18,VSS,AD52,VSS,CB49 | ||

| + | G0_RXP[13],U42,MC_C[2],AH3,RSVD,L18,RSVD,BU12,VDDCR_CPU,Y31,VDDIO_MEM_S3_CD,BB4,VSS,AD54,VSS,CB52 | ||

| + | G0_RXP[14],V43,MC_DATA[0],DB3,RSVD,L20,RSVD,BU13,VDDCR_CPU,Y33,VDDIO_MEM_S3_CD,BB6,VSS,AE1,VSS,CB54 | ||

| + | G0_RXP[15],W44,MC_DATA[1],DA2,RSVD,L21,RSVD,BU15,VDDCR_CPU,Y35,VDDIO_MEM_S3_CD,BB8,VSS,AE2,VSS,CC2 | ||

| + | G0_TXN[0],L29,MC_DATA[2],CV2,RSVD,L23,RSVD,BU16,VDDCR_CPU,Y37,VDDIO_MEM_S3_CD,BB11,VSS,AE3,VSS,CC4 | ||

| + | G0_TXN[1],M31,MC_DATA[3],CU1,RSVD,L24,RSVD,BU39,VDDCR_CPU,AA20,VDDIO_MEM_S3_CD,BB13,VSS,AE4,VSS,CC7 | ||

| + | G0_TXN[2],K32,MC_DATA[4],DB4,RSVD,L26,RSVD,BU41,VDDCR_CPU,AA22,VDDIO_MEM_S3_CD,BB16,VSS,AE5,VSS,CC9 | ||

| + | G0_TXN[3],L32,MC_DATA[5],DA3,RSVD,L27,RSVD,BU42,VDDCR_CPU,AA24,VDDIO_MEM_S3_CD,BC2,VSS,AE6,VSS,CC12 | ||

| + | G0_TXN[4],M34,MC_DATA[6],CV3,RSVD,L45,RSVD,BU44,VDDCR_CPU,AA26,VDDIO_MEM_S3_CD,BC4,VSS,AE7,VSS,CC14 | ||

| + | G0_TXN[5],K35,MC_DATA[7],CU3,RSVD,L46,RSVD,BU46,VDDCR_CPU,AA28,VDDIO_MEM_S3_CD,BC7,VSS,AE8,VSS,CC15 | ||

| + | G0_TXN[6],L35,MC_DATA[8],CT2,RSVD,L47,RSVD,BU47,VDDCR_CPU,AA30,VDDIO_MEM_S3_CD,BC9,VSS,AE9,VSS,CC17 | ||

| + | G0_TXN[7],M37,MC_DATA[9],CR1,RSVD,M9,RSVD,BV9,VDDCR_CPU,AA32,VDDIO_MEM_S3_CD,BC11,VSS,AE10,VSS,CC19 | ||

| + | G0_TXN[8],K38,MC_DATA[10],CM2,RSVD,M10,RSVD,BV10,VDDCR_CPU,AA34,VDDIO_MEM_S3_CD,BC14,VSS,AE11,VSS,CC21 | ||

| + | G0_TXN[9],L38,MC_DATA[11],CL1,RSVD,M13,RSVD,BV12,VDDCR_CPU,AA36,VDDIO_MEM_S3_CD,BC17,VSS,AE14,VSS,CC23 | ||

| + | G0_TXN[10],M40,MC_DATA[12],CT3,RSVD,M14,RSVD,BV14,VDDCR_CPU,AB21,VDDIO_MEM_S3_CD,BC18,VSS,AE17,VSS,CC25 | ||

| + | G0_TXN[11],K41,MC_DATA[13],CR3,RSVD,M16,RSVD,BV15,VDDCR_CPU,AB23,VDDIO_MEM_S3_CD,BD1,VSS,AE19,VSS,CC27 | ||

| + | G0_TXN[12],L41,MC_DATA[14],CM3,RSVD,M17,RSVD,BV17,VDDCR_CPU,AB25,VDDIO_MEM_S3_CD,BD4,VSS,AE21,VSS,CC29 | ||

| + | G0_TXN[13],M43,MC_DATA[15],CL3,RSVD,M19,RSVD,BV40,VDDCR_CPU,AB27,VDDIO_MEM_S3_CD,BD6,VSS,AE35,VSS,CC31 | ||

| + | G0_TXN[14],K44,MC_DATA[16],CK2,RSVD,M20,RSVD,BV41,VDDCR_CPU,AB29,VDDIO_MEM_S3_CD,BD8,VSS,AE37,VSS,CC34 | ||

| + | G0_TXN[15],L44,MC_DATA[17],CJ1,RSVD,M22,RSVD,BV43,VDDCR_CPU,AB31,VDDIO_MEM_S3_CD,BD11,VSS,AE38,VSS,CC35 | ||

| + | G0_TXP[0],M29,MC_DATA[18],CF2,RSVD,M23,RSVD,BV44,VDDCR_CPU,AB33,VDDIO_MEM_S3_CD,BD15,VSS,AE40,VSS,CC36 | ||

| + | G0_TXP[1],L30,MC_DATA[19],CE1,RSVD,M25,RSVD,BW8,VDDCR_CPU,AB35,VDDIO_MEM_S3_CD,BE2,VSS,AE43,VSS,CC37 | ||

| + | G0_TXP[2],K31,MC_DATA[20],CK3,RSVD,M26,RSVD,BW10,VDDCR_CPU,AB37,VDDIO_MEM_S3_CD,BE4,VSS,AE45,VSS,CC38 | ||

| + | G0_TXP[3],M32,MC_DATA[21],CJ3,RSVD,M28,RSVD,BW12,VDDCR_CPU,AC20,VDDIO_MEM_S3_CD,BE7,VSS,AE48,VSS,CC39 | ||

| + | G0_TXP[4],L33,MC_DATA[22],CF3,RSVD,M46,RSVD,BW13,VDDCR_CPU,AC22,VDDIO_MEM_S3_CD,BE9,VSS,AE50,VSS,CC40 | ||

| + | G0_TXP[5],K34,MC_DATA[23],CE3,RSVD,M48,RSVD,BW15,VDDCR_CPU,AC24,VDDIO_MEM_S3_CD,BE16,VSS,AE52,VSS,CC41 | ||

| + | G0_TXP[6],M35,MC_DATA[24],CD2,RSVD,N8,RSVD,BW16,VDDCR_CPU,AC26,VDDIO_MEM_S3_CD,BE18,VSS,AF13,VSS,CC42 | ||

| + | G0_TXP[7],L36,MC_DATA[25],CC1,RSVD,N10,RSVD,BW39,VDDCR_CPU,AC28,VDDIO_MEM_S3_CD,BF4,VSS,AF16,VSS,CC43 | ||

| + | G0_TXP[8],K37,MC_DATA[26],BY2,RSVD,N46,RSVD,BW41,VDDCR_CPU,AC30,VDDIO_MEM_S3_CD,BF6,VSS,AF18,VSS,CC44 | ||

| + | G0_TXP[9],M38,MC_DATA[27],BW1,RSVD,N47,RSVD,BW42,VDDCR_CPU,AC32,VDDIO_MEM_S3_CD,BF8,VSS,AF20,VSS,CC45 | ||

| + | G0_TXP[10],L39,MC_DATA[28],CD3,RSVD,P9,RSVD,BW44,VDDCR_CPU,AC34,VDDIO_MEM_S3_CD,BF11,VSS,AF22,VSS,CC48 | ||

| + | G0_TXP[11],K40,MC_DATA[29],CC3,RSVD,P10,RSVD,BW46,VDDCR_CPU,AC36,VDDIO_MEM_S3_CD,BF15,VSS,AF36,VSS,CC50 | ||

| + | G0_TXP[12],M41,MC_DATA[30],BY3,RSVD,P31,RSVD,BW47,VDDCR_CPU,AD21,VDDIO_MEM_S3_CD,BG2,VSS,AF38,VSS,CC52 | ||

| + | G0_TXP[13],L42,MC_DATA[31],BW3,RSVD,P32,RSVD,BY9,VDDCR_CPU,AD35,VDDIO_MEM_S3_CD,BG4,VSS,AF39,VSS,CC55 | ||

| + | G0_TXP[14],K43,MC_DATA[32],AD3,RSVD,P34,RSVD,BY10,VDDCR_CPU,AD37,VDDIO_MEM_S3_CD,BG7,VSS,AF42,VSS,CD1 | ||

| + | G0_TXP[15],M44,MC_DATA[33],AC3,RSVD,P35,RSVD,BY12,VDDCR_CPU,AE20,VDDIO_MEM_S3_CD,BG9,VSS,AF45,VSS,CD4 | ||

| + | G1A_ZVSS,P28,MC_DATA[34],Y3,RSVD,P37,RSVD,BY14,VDDCR_CPU,AE34,VDDIO_MEM_S3_CD,BG16,VSS,AF47,VSS,CD6 | ||

| + | G1_RXN[0]/SATA10_RXN,R12,MC_DATA[35],W3,RSVD,P38,RSVD,BY15,VDDCR_CPU,AE36,VDDIO_MEM_S3_CD,BG18,VSS,AF49,VSS,CD8 | ||

| + | G1_RXN[1]/SATA11_RXN,P13,MC_DATA[36],AD2,RSVD,P40,RSVD,BY17,VDDCR_CPU,AF19,VDDIO_MEM_S3_CD,BH1,VSS,AF52,VSS,CD11 | ||

| + | G1_RXN[2]/SATA12_RXN,T14,MC_DATA[37],AC1,RSVD,P41,RSVD,BY19,VDDCR_CPU,AF21,VDDIO_MEM_S3_CD,BH4,VSS,AF54,VSS,CD12 | ||

| + | G1_RXN[3]/SATA13_RXN,R15,MC_DATA[38],Y2,RSVD,P43,RSVD,BY22,VDDCR_CPU,AF35,VDDIO_MEM_S3_CD,BH6,VSS,AG11,VSS,CD15 | ||

| + | G1_RXN[4]/SATA14_RXN/XGBE10_RXN,P16,MC_DATA[39],W1,RSVD,P44,RSVD,BY37,VDDCR_CPU,AF37,VDDIO_MEM_S3_CD,BH8,VSS,AG14,VSS,CD18 | ||

| + | G1_RXN[5]/SATA15_RXN/XGBE11_RXN,T17,MC_DATA[40],V3,RSVD,P46,RSVD,BY38,VDDCR_CPU,AG20,VDDIO_MEM_S3_CD,BH11,VSS,AG17,VSS,CD21 | ||

| + | G1_RXN[6]/SATA16_RXN/XGBE12_RXN,R18,MC_DATA[41],U3,RSVD,P48,RSVD,BY40,VDDCR_CPU,AG34,VDDIO_MEM_S3_CD,BH15,VSS,AG19,VSS,CD24 | ||

| + | G1_RXN[7]/SATA17_RXN/XGBE13_RXN,P19,MC_DATA[42],P3,RSVD,R8,RSVD,BY41,VDDCR_CPU,AG36,VDDIO_MEM_S3_CD,BJ2,VSS,AG21,VSS,CD27 | ||

| + | G1_RXN[8],T20,MC_DATA[43],N3,RSVD,R10,RSVD,BY43,VDDCR_CPU,AH19,VDDIO_MEM_S3_CD,BJ4,VSS,AG35,VSS,CD30 | ||

| + | G1_RXN[9],R21,MC_DATA[44],V2,RSVD,R29,RSVD,BY44,VDDCR_CPU,AH21,VDDIO_MEM_S3_CD,BJ7,VSS,AG37,VSS,CD33 | ||

| + | G1_RXN[10],P22,MC_DATA[45],U1,RSVD,R30,RSVD,BY46,VDDCR_CPU,AH35,VDDIO_MEM_S3_CD,BJ9,VSS,AG38,VSS,CD36 | ||

| + | G1_RXN[11],T23,MC_DATA[46],P2,RSVD,R32,RSVD,BY48,VDDCR_CPU,AH37,VDDIO_MEM_S3_CD,BJ16,VSS,AG40,VSS,CD39 | ||

| + | G1_RXN[12],R24,MC_DATA[47],N1,RSVD,R33,RSVD,CA8,VDDCR_CPU,AJ20,VDDIO_MEM_S3_CD,BK4,VSS,AG43,VSS,CD42 | ||

| + | G1_RXN[13],P25,MC_DATA[48],M3,RSVD,R35,RSVD,CA10,VDDCR_CPU,AJ34,VDDIO_MEM_S3_CD,BK6,VSS,AG45,VSS,CD45 | ||

| + | G1_RXN[14],T26,MC_DATA[49],L3,RSVD,R36,RSVD,CA12,VDDCR_CPU,AJ36,VDDIO_MEM_S3_CD,BK8,VSS,AG48,VSS,CD47 | ||

| + | G1_RXN[15],R27,MC_DATA[50],H3,RSVD,R38,RSVD,CA13,VDDCR_CPU,AK19,VDDIO_MEM_S3_CD,BK11,VSS,AG50,VSS,CD49 | ||

| + | G1_RXP[0]/SATA10_RXP,T13,MC_DATA[51],G3,RSVD,R39,RSVD,CA15,VDDCR_CPU,AK21,VDDIO_MEM_S3_CD,BL2,VSS,AG52,VSS,CD52 | ||

| + | G1_RXP[1]/SATA11_RXP,P14,MC_DATA[52],M2,RSVD,R41,RSVD,CA16,VDDCR_CPU,AK35,VDDIO_MEM_S3_CD,BL4,VSS,AG55,VSS,CD54 | ||

| + | G1_RXP[2]/SATA12_RXP,R14,MC_DATA[53],L1,RSVD,R42,RSVD,CA18,VDDCR_CPU,AK37,VDDIO_MEM_S3_CD,BL7,VSS,AH13,VSS,CE2 | ||

| + | G1_RXP[3]/SATA13_RXP,T16,MC_DATA[54],H2,RSVD,R44,RSVD,CA21,VDDCR_CPU,AL20,VDDIO_MEM_S3_CD,BL9,VSS,AH16,VSS,CE4 | ||

| + | G1_RXP[4]/SATA14_RXP/XGBE10_RXP,P17,MC_DATA[55],G1,RSVD,R46,RSVD,CA39,VDDCR_CPU,AL34,VDDIO_MEM_S3_CD_FB_H,BJ18,VSS,AH20,VSS,CE7 | ||

| + | G1_RXP[5]/SATA15_RXP/XGBE11_RXP,R17,MC_DATA[56],F3,RSVD,R47,RSVD,CA41,VDDCR_CPU,AL36,VDDIO_MEM_S3_CD_FB_L,BK18,VSS,AH22,VSS,CE9 | ||

| + | G1_RXP[6]/SATA16_RXP/XGBE12_RXP,T19,MC_DATA[57],E3,RSVD,T9,RSVD,CA42,VDDCR_CPU,AM19,VDD_18,Y17,VSS,AH36,VSS,CE31 | ||

| + | G1_RXP[7]/SATA17_RXP/XGBE13_RXP,P20,MC_DATA[58],A3,RSVD,T10,RSVD,CA44,VDDCR_CPU,AM21,VDD_18,Y19,VSS,AH38,VSS,CE34 | ||

| + | G1_RXP[8],R20,MC_DATA[59],A4,RSVD,T29,RSVD,CA46,VDDCR_CPU,AM35,VDD_18,AA18,VSS,AH39,VSS,CE37 | ||

| + | G1_RXP[9],T22,MC_DATA[60],F2,RSVD,T31,RSVD,CA47,VDDCR_CPU,AM37,VDD_18,AB19,VSS,AH42,VSS,CE40 | ||

| + | G1_RXP[10],P23,MC_DATA[61],E1,RSVD,T32,RSVD,CB9,VDDCR_CPU,AN20,VDD_18,AC18,VSS,AH45,VSS,CE43 | ||

| + | G1_RXP[11],R23,MC_DATA[62],B2,RSVD,T34,RSVD,CB10,VDDCR_CPU,AN34,VDD_18,AD19,VSS,AH47,VSS,CE45 | ||

| + | G1_RXP[12],T25,MC_DATA[63],B3,RSVD,T35,RSVD,CB12,VDDCR_CPU,AN36,VDD_18,AE18,VSS,AH49,VSS,CE48 | ||

| + | G1_RXP[13],P26,MC_DQS_H[0],CW1,RSVD,T37,RSVD,CB14,VDDCR_CPU,AP19,VDD_18_S5,AH18,VSS,AH52,VSS,CE50 | ||

| + | G1_RXP[14],R26,MC_DQS_H[1],CN1,RSVD,T38,RSVD,CB15,VDDCR_CPU,AP21,VDD_18_S5_SENSE,CB33,VSS,AH54,VSS,CE52 | ||

| + | G1_RXP[15],T28,MC_DQS_H[2],CG1,RSVD,T40,RSVD,CB17,VDDCR_CPU,AP35,VDD_18_SENSE,Y13,VSS,AJ11,VSS,CE55 | ||

| + | G1_TXN[0]/SATA10_TXN,H13,MC_DQS_H[3],CA1,RSVD,T41,RSVD,CB40,VDDCR_CPU,AP37,VDD_33,CB37,VSS,AJ14,VSS,CF1 | ||

| + | G1_TXN[1]/SATA11_TXN,J14,MC_DQS_H[4],AA3,RSVD,T43,RSVD,CB41,VDDCR_CPU,AR20,VDD_33,CB38,VSS,AJ17,VSS,CF4 | ||

| + | G1_TXN[2]/SATA12_TXN,G15,MC_DQS_H[5],R3,RSVD,T44,RSVD,CB43,VDDCR_CPU,AR34,VDD_33_S5,CA35,VSS,AJ18,VSS,CF6 | ||

| + | G1_TXN[3]/SATA13_TXN,H16,MC_DQS_H[6],J3,RSVD,T46,RSVD,CB44,VDDCR_CPU,AR36,VDD_33_S5,CA36,VSS,AJ19,VSS,CF8 | ||

| + | G1_TXN[4]/SATA14_TXN/XGBE10_TXN,J17,MC_DQS_H[7],C3,RSVD,T48,RSVD,CB46,VDDCR_CPU,AT19,VDD_33_S5_SENSE,CA32,VSS,AJ21,VSS,CF11 | ||

| + | G1_TXN[5]/SATA15_TXN/XGBE11_TXN,G18,MC_DQS_H[8],BR1,RSVD,U8,RSVD,CB48,VDDCR_CPU,AT21,VDD_33_SENSE,CC33,VSS,AJ35,VSS,CF12 | ||

| + | G1_TXN[6]/SATA16_TXN/XGBE12_TXN,H19,MC_DQS_H[9],CY3,RSVD,U10,RSVD,CC8,VDDCR_CPU,AT35,VSS,A5,VSS,AJ37,VSS,CF15 | ||

| + | G1_TXN[7]/SATA17_TXN/XGBE13_TXN,J20,MC_DQS_H[10],CP3,RSVD,U14,RSVD,CC10,VDDCR_CPU,AT37,VSS,A8,VSS,AJ38,VSS,CF18 | ||

| + | G1_TXN[8],G21,MC_DQS_H[11],CH3,RSVD,U15,RSVD,CC46,VDDCR_CPU,AU20,VSS,A11,VSS,AJ40,VSS,CF21 | ||

| + | G1_TXN[9],H22,MC_DQS_H[12],CB3,RSVD,U17,RSVD,CC47,VDDCR_CPU,AU34,VSS,A12,VSS,AJ43,VSS,CF24 | ||

| + | G1_TXN[10],J23,MC_DQS_H[13],AB2,RSVD,U18,RSVD,CD9,VDDCR_CPU,AU36,VSS,A15,VSS,AJ45,VSS,CF27 | ||

| + | G1_TXN[11],G24,MC_DQS_H[14],T2,RSVD,U20,RSVD,CD10,VDDCR_CPU,AV19,VSS,A18,VSS,AJ48,VSS,CF30 | ||

| + | G1_TXN[12],H25,MC_DQS_H[15],K2,RSVD,U21,RSVD,CD29,VDDCR_CPU,AV21,VSS,A21,VSS,AJ50,VSS,CF33 | ||

| + | G1_TXN[13],J26,MC_DQS_H[16],D2,RSVD,U23,RSVD,CD31,VDDCR_CPU,AV35,VSS,A24,VSS,AJ52,VSS,CF36 | ||

| + | G1_TXN[14],G27,MC_DQS_H[17],BT3,RSVD,U24,RSVD,CD32,VDDCR_CPU,AV37,VSS,A27,VSS,AK13,VSS,CF39 | ||

| + | G1_TXN[15],H28,MC_DQS_L[0],CY2,RSVD,U26,RSVD,CD34,VDDCR_CPU,AW20,VSS,A30,VSS,AK16,VSS,CF42 | ||

| + | G1_TXP[0]/SATA10_TXP,J12,MC_DQS_L[1],CP2,RSVD,U27,RSVD,CD35,VDDCR_CPU,AW34,VSS,A33,VSS,AK18,VSS,CF45 | ||

| + | G1_TXP[1]/SATA11_TXP,H14,MC_DQS_L[2],CH2,RSVD,U44,RSVD,CD37,VDDCR_CPU,AW36,VSS,A36,VSS,AK20,VSS,CF47 | ||

| + | G1_TXP[2]/SATA12_TXP,G14,MC_DQS_L[3],CB2,RSVD,U46,RSVD,CD38,VDDCR_CPU,AY19,VSS,A39,VSS,AK22,VSS,CF49 | ||

| + | G1_TXP[3]/SATA13_TXP,J15,MC_DQS_L[4],AB3,RSVD,U47,RSVD,CD40,VDDCR_CPU,AY21,VSS,A42,VSS,AK36,VSS,CF52 | ||

| + | G1_TXP[4]/SATA14_TXP/XGBE10_TXP,H17,MC_DQS_L[5],T3,RSVD,V9,RSVD,CD41,VDDCR_CPU,AY23,VSS,A45,VSS,AK38,VSS,CF54 | ||

| + | G1_TXP[5]/SATA15_TXP/XGBE11_TXP,G17,MC_DQS_L[6],K3,RSVD,V10,RSVD,CD43,VDDCR_CPU,AY25,VSS,A48,VSS,AK39,VSS,CG2 | ||

| + | G1_TXP[6]/SATA16_TXP/XGBE12_TXP,J18,MC_DQS_L[7],D3,RSVD,V13,RSVD,CD44,VDDCR_CPU,AY27,VSS,A51,VSS,AK42,VSS,CG4 | ||

| + | G1_TXP[7]/SATA17_TXP/XGBE13_TXP,H20,MC_DQS_L[8],BT2,RSVD,V14,RSVD,CD46,VDDCR_CPU,AY29,VSS,B4,VSS,AK45,VSS,CG7 | ||

| + | G1_TXP[8],G20,MC_DQS_L[9],CW3,RSVD,V16,RSVD,CD48,VDDCR_CPU,AY31,VSS,B5,VSS,AK47,VSS,CG9 | ||

| + | G1_TXP[9],J21,MC_DQS_L[10],CN3,RSVD,V17,RSVD,CE8,VDDCR_CPU,AY33,VSS,B8,VSS,AK49,VSS,CG31 | ||

| + | G1_TXP[10],H23,MC_DQS_L[11],CG3,RSVD,V19,RSVD,CE10,VDDCR_CPU,AY35,VSS,B47,VSS,AK52,VSS,CG34 | ||

| + | G1_TXP[11],G23,MC_DQS_L[12],CA3,RSVD,V20,RSVD,CE29,VDDCR_CPU,AY37,VSS,B49,VSS,AK54,VSS,CG37 | ||

| + | G1_TXP[12],J24,MC_DQS_L[13],AA1,RSVD,V22,RSVD,CE30,VDDCR_CPU,BA20,VSS,B52,VSS,AL11,VSS,CG40 | ||

| + | G1_TXP[13],H26,MC_DQS_L[14],R1,RSVD,V23,RSVD,CE32,VDDCR_CPU,BA22,VSS,C2,VSS,AL14,VSS,CG43 | ||

| + | G1_TXP[14],G26,MC_DQS_L[15],J1,RSVD,V25,RSVD,CE33,VDDCR_CPU,BA24,VSS,C4,VSS,AL17,VSS,CG45 | ||

| + | G1_TXP[15],J27,MC_DQS_L[16],C1,RSVD,V26,RSVD,CE35,VDDCR_CPU,BA26,VSS,C7,VSS,AL18,VSS,CG48 | ||

| + | GENINT1_L/AGPIO89,CY44,MC_DQS_L[17],BR3,RSVD,V28,RSVD,CE36,VDDCR_CPU,BA28,VSS,C9,VSS,AL19,VSS,CG50 | ||

| + | GENINT2_L/AGPIO90,CN46,MC_EVENT_L,AU3,RSVD,V46,RSVD,CE38,VDDCR_CPU,BA30,VSS,C11,VSS,AL21,VSS,CG52 | ||

| + | GFX_CLK00N,DB18,MC_PAROUT,AT3,RSVD,V48,RSVD,CE39,VDDCR_CPU,BA32,VSS,C12,VSS,AL35,VSS,CG55 | ||

| + | GFX_CLK00P,DA18,MC_RAS_L_ADD[16],AN1,RSVD,W8,RSVD,CE41,VDDCR_CPU,BA34,VSS,C15,VSS,AL37,VSS,CH1 | ||

| + | GFX_CLK10N,C38,MC_RESET_L,BL3,RSVD,W10,RSVD,CE42,VDDCR_CPU,BA36,VSS,C18,VSS,AL38,VSS,CH4 | ||

| + | GFX_CLK10P,C37,MC_WE_L_ADD[14],AN3,RSVD,W12,RSVD,CE44,VDDCR_CPU,BB19,VSS,C21,VSS,AL40,VSS,CH6 | ||

| + | GFX_CLK11N,A37,MC_ZVSS,BA3,RSVD,W14,RSVD,CE46,VDDCR_CPU,BB21,VSS,C24,VSS,AL43,VSS,CH8 | ||

| + | GFX_CLK11P,B37,MD0_CKE[0],BK5,RSVD,W15,RSVD,CE47,VDDCR_CPU,BB23,VSS,C27,VSS,AL45,VSS,CH11 | ||

| + | GPP_CLK00N,AY28,MD0_CKE[1],BL5,RSVD,W17,RSVD,CF9,VDDCR_CPU,BB25,VSS,C30,VSS,AL46,VSS,CH12 | ||

| + | GPP_CLK00P,BA27,MD0_CLK_H[0],AY5,RSVD,W18,RSVD,CF10,VDDCR_CPU,BB27,VSS,C33,VSS,AL47,VSS,CH15 | ||

| + | GPP_CLK01N,DB20,MD0_CLK_H[1],AY7,RSVD,W20,RSVD,CF31,VDDCR_CPU,BB29,VSS,C36,VSS,AL48,VSS,CH18 | ||

| + | GPP_CLK01P,DA19,MD0_CLK_L[0],AW5,RSVD,W21,RSVD,CF32,VDDCR_CPU,BB31,VSS,C39,VSS,AL49,VSS,CH21 | ||

| + | GPP_CLK02N,CY36,MD0_CLK_L[1],AW6,RSVD,W23,RSVD,CF34,VDDCR_CPU,BB33,VSS,C42,VSS,AL50,VSS,CH24 | ||

| + | GPP_CLK02P,CY35,MD0_CS_L[0],AM7,RSVD,W24,RSVD,CF35,VDDCR_CPU,BB35,VSS,C45,VSS,AL51,VSS,CH27 | ||

| + | GPP_CLK03N,DB35,MD0_CS_L[1],AJ6,RSVD,W26,RSVD,CF37,VDDCR_CPU,BB37,VSS,C48,VSS,AL52,VSS,CH30 | ||

| + | GPP_CLK03P,DA34,MD0_ODT[0],AK5,RSVD,W27,RSVD,CF38,VDDCR_CPU,BC20,VSS,C50,VSS,AL53,VSS,CH33 | ||

| + | GPP_CLK11N,A46,MD0_ODT[1],AG5,RSVD,W46,RSVD,CF40,VDDCR_CPU,BC22,VSS,C52,VSS,AL54,VSS,CH36 | ||

| + | GPP_CLK11P,A47,MD1_CKE[0],BJ6,RSVD,W47,RSVD,CF41,VDDCR_CPU,BC24,VSS,C55,VSS,AL55,VSS,CH39 | ||

| + | GPP_CLK12N,C41,MD1_CKE[1],BK7,RSVD,Y9,RSVD,CF43,VDDCR_CPU,BC26,VSS,D1,VSS,AM13,VSS,CH42 | ||

| + | GPP_CLK12P,C40,MD1_CLK_H[0],AV5,RSVD,Y10,RSVD,CF44,VDDCR_CPU,BC28,VSS,D4,VSS,AM16,VSS,CH45 | ||

| + | GPP_CLK13N,B42,MD1_CLK_H[1],AV7,RSVD,Y46,RSVD,CF46,VDDCR_CPU,BC30,VSS,D6,VSS,AM18,VSS,CH47 | ||

| + | GPP_CLK13P,A41,MD1_CLK_L[0],AU5,RSVD,Y48,RSVD,CF48,VDDCR_CPU,BC32,VSS,D8,VSS,AM20,VSS,CH49 | ||

| + | I2C0_SCL/EGPIO145/HP_SCL,DA40,MD1_CLK_L[1],AU6,RSVD,AA8,RSVD,CG8,VDDCR_CPU,BC34,VSS,D47,VSS,AM22,VSS,CH52 | ||

| + | I2C0_SDA/EGPIO146/HP_SDA,DB41,MD1_CS_L[0],AN6,RSVD,AA10,RSVD,CG10,VDDCR_CPU,BC36,VSS,D49,VSS,AM36,VSS,CH54 | ||

| + | I2C1_SCL/EGPIO147/SFP_SCL,E22,MD1_CS_L[1],AJ5,RSVD,AA12,RSVD,CG12,VDDCR_CPU,BD19,VSS,D52,VSS,AM38,VSS,CJ2 | ||

| + | I2C1_SDA/EGPIO148/SFP_SDA,D22,MD1_ODT[0],AL6,RSVD,AA13,RSVD,CG14,VDDCR_CPU,BD21,VSS,D54,VSS,AM39,VSS,CJ4 | ||

| + | I2C4_SCL/EGPIO149,CW43,MD1_ODT[1],AG6,RSVD,AA15,RSVD,CG15,VDDCR_CPU,BD35,VSS,E2,VSS,AM42,VSS,CJ7 | ||

| + | I2C4_SDA/EGPIO150,CV44,MD_ACT_L,BJ5,RSVD,AA16,RSVD,CG17,VDDCR_CPU,BD37,VSS,E4,VSS,AM45,VSS,CJ9 | ||

| + | I2C5_SCL/EGPIO151,CV42,MD_ADD[0],AR5,RSVD,AA39,RSVD,CG18,VDDCR_CPU,BE20,VSS,E7,VSS,AM46,VSS,CJ31 | ||

| + | I2C5_SDA/EGPIO152,CW42,MD_ADD[1],BB7,RSVD,AA41,RSVD,CG20,VDDCR_CPU,BE34,VSS,E9,VSS,AM48,VSS,CJ37 | ||

| + | LAD0/EGPIO104,CV29,MD_ADD[2],BB5,RSVD,AA42,RSVD,CG21,VDDCR_CPU,BE36,VSS,E11,VSS,AN11,VSS,CJ40 | ||

| + | LAD1/EGPIO105,CW30,MD_ADD[3],BC5,RSVD,AA44,RSVD,CG23,VDDCR_CPU,BF19,VSS,E12,VSS,AN12,VSS,CJ43 | ||

| + | LAD2/EGPIO106,CV32,MD_ADD[4],BC6,RSVD,AA46,RSVD,CG24,VDDCR_CPU,BF21,VSS,E15,VSS,AN13,VSS,CJ45 | ||

| + | LAD3/EGPIO107,CW28,MD_ADD[5],BD5,RSVD,AA47,RSVD,CG26,VDDCR_CPU,BF35,VSS,E18,VSS,AN14,VSS,CJ48 | ||

| + | LFRAME_L/EGPIO109,CW27,MD_ADD[6],BD7,RSVD,AB9,RSVD,CG27,VDDCR_CPU,BF37,VSS,E21,VSS,AN15,VSS,CJ50 | ||

| + | LPCCLK0/EGPIO74,CV30,MD_ADD[7],BE6,RSVD,AB10,RSVD,CG46,VDDCR_CPU,BG20,VSS,E24,VSS,AN16,VSS,CJ52 | ||

| + | LPCCLK1/EGPIO75,CV33,MD_ADD[8],BE5,RSVD,AB12,RSVD,CG47,VDDCR_CPU,BG34,VSS,E27,VSS,AN17,VSS,CJ55 | ||

| + | LPC_CLKRUN_L/AGPIO88,CW31,MD_ADD[9],BF7,RSVD,AB14,RSVD,CH9,VDDCR_CPU,BG36,VSS,E30,VSS,AN18,VSS,CK1 | ||

| + | LPC_PD_L/AGPIO21,CV27,MD_ADD[10],AP5,RSVD,AB15,RSVD,CH10,VDDCR_CPU,BH19,VSS,E33,VSS,AN19,VSS,CK4 | ||

| + | LPC_PME_L/AGPIO22,CV26,MD_ADD[11],BF5,RSVD,AB17,RSVD,CH13,VDDCR_CPU,BH21,VSS,E36,VSS,AN21,VSS,CK6 | ||

| + | LPC_RST_L,CV24,MD_ADD[12],BG5,RSVD,AB34,RSVD,CH14,VDDCR_CPU,BH35,VSS,E39,VSS,AN35,VSS,CK8 | ||

| + | LPC_SMI_L/NMI_SYNC_FLOOD_L/AGPIO86,CW34,MD_ADD[13],AK7,RSVD,AB40,RSVD,CH16,VDDCR_CPU,BH37,VSS,E42,VSS,AN37,VSS,CK11 | ||

| + | MA0_CKE[0],AN54,MD_ADD_17,AH5,RSVD,AB41,RSVD,CH17,VDDCR_CPU,BJ20,VSS,E45,VSS,AN39,VSS,CK12 | ||

| + | MA0_CKE[1],AN53,MD_ALERT_L,BG6,RSVD,AB43,RSVD,CH19,VDDCR_CPU,BJ34,VSS,E48,VSS,AN40,VSS,CK13 | ||

| + | MA0_CLK_H[0],BB55,MD_BANK[0],AP7,RSVD,AB44,RSVD,CH20,VDDCR_CPU,BJ36,VSS,E50,VSS,AN41,VSS,CK14 | ||

| + | MA0_CLK_H[1],BD55,MD_BANK[1],AR6,RSVD,AB46,RSVD,CH22,VDDCR_CPU,BK19,VSS,E52,VSS,AN43,VSS,CK15 | ||

| + | MA0_CLK_L[0],BC54,MD_BG[0],BH5,RSVD,AB48,RSVD,CH23,VDDCR_CPU,BK21,VSS,E55,VSS,AN46,VSS,CK16 | ||

| + | MA0_CLK_L[1],BE54,MD_BG[1],BH7,RSVD,AC8,RSVD,CH25,VDDCR_CPU,BK35,VSS,F1,VSS,AN47,VSS,CK17 | ||

| + | MA0_CS_L[0],BL53,MD_CAS_L_ADD[15],AL5,RSVD,AC10,RSVD,CH26,VDDCR_CPU,BK37,VSS,F4,VSS,AP18,VSS,CK18 | ||

| + | MA0_CS_L[1],BR54,MD_CHECK[0],BU6,RSVD,AC12,RSVD,CH28,VDDCR_CPU,BL20,VSS,F6,VSS,AP20,VSS,CK19 | ||

| + | MA0_ODT[0],BM53,MD_CHECK[1],BU5,RSVD,AC13,RSVD,CH46,VDDCR_CPU,BL34,VSS,F8,VSS,AP22,VSS,CK20 | ||

| + | MA0_ODT[1],BT55,MD_CHECK[2],BN6,RSVD,AC15,RSVD,CH48,VDDCR_CPU,BL36,VSS,F13,VSS,AP36,VSS,CK21 | ||

| + | MA1_CKE[0],AP53,MD_CHECK[3],BN5,RSVD,AC16,RSVD,CJ8,VDDCR_CPU,BM19,VSS,F15,VSS,AP39,VSS,CK22 | ||

| + | MA1_CKE[1],AM55,MD_CHECK[4],BV7,RSVD,AC33,RSVD,CJ10,VDDCR_CPU,BM21,VSS,F16,VSS,AP41,VSS,CK23 | ||

| + | MA1_CLK_H[0],BD53,MD_CHECK[5],BV5,RSVD,AC39,RSVD,CJ12,VDDCR_CPU,BM35,VSS,F18,VSS,AP42,VSS,CK24 | ||

| + | MA1_CLK_H[1],BF55,MD_CHECK[6],BP7,RSVD,AC41,RSVD,CJ14,VDDCR_CPU,BM37,VSS,F19,VSS,AP45,VSS,CK25 | ||

| + | MA1_CLK_L[0],BE53,MD_CHECK[7],BP5,RSVD,AC42,RSVD,CJ15,VDDCR_CPU,BN20,VSS,F21,VSS,AP46,VSS,CK26 | ||

| + | MA1_CLK_L[1],BG54,MD_C[0],AF7,RSVD,AC44,RSVD,CJ17,VDDCR_CPU,BN34,VSS,F22,VSS,AR19,VSS,CK27 | ||

| + | MA1_CS_L[0],BL54,MD_C[1],AF5,RSVD,AC46,RSVD,CJ18,VDDCR_CPU,BN36,VSS,F24,VSS,AR21,VSS,CK28 | ||

| + | MA1_CS_L[1],BP55,MD_C[2],AH7,RSVD,AC47,RSVD,CJ20,VDDCR_CPU,BP19,VSS,F25,VSS,AR35,VSS,CK29 | ||

| + | MA1_ODT[0],BN54,MD_DATA[0],DB6,RSVD,AD9,RSVD,CJ21,VDDCR_CPU,BP21,VSS,F27,VSS,AR37,VSS,CK30 | ||

| + | MA1_ODT[1],BU54,MD_DATA[1],DA5,RSVD,AD10,RSVD,CJ23,VDDCR_CPU,BP35,VSS,F28,VSS,AR38,VSS,CK31 | ||

| + | MA_ACT_L,AR53,MD_DATA[2],CU6,RSVD,AD12,RSVD,CJ24,VDDCR_CPU,BP37,VSS,F30,VSS,AR39,VSS,CK32 | ||

| + | MA_ADD[0],BH55,MD_DATA[3],CU5,RSVD,AD14,RSVD,CJ26,VDDCR_CPU,BR20,VSS,F31,VSS,AR40,VSS,CK33 | ||

| + | MA_ADD[1],AY55,MD_DATA[4],DB7,RSVD,AD15,RSVD,CJ27,VDDCR_CPU,BR34,VSS,F33,VSS,AR43,VSS,CK35 | ||

| + | MA_ADD[2],BA54,MD_DATA[5],DA6,RSVD,AD17,RSVD,CJ46,VDDCR_CPU,BR36,VSS,F34,VSS,AT18,VSS,CK36 | ||

| + | MA_ADD[3],BA53,MD_DATA[6],CV7,RSVD,AD40,RSVD,CJ47,VDDCR_CPU,BT19,VSS,F36,VSS,AT20,VSS,CK37 | ||

| + | MA_ADD[4],AY53,MD_DATA[7],CV5,RSVD,AD41,RSVD,CK9,VDDCR_CPU,BT21,VSS,F37,VSS,AT22,VSS,CK38 | ||

| + | MA_ADD[5],AW54,MD_DATA[8],CR6,RSVD,AD43,RSVD,CK10,VDDCR_CPU,BT35,VSS,F39,VSS,AT36,VSS,CK39 | ||

| + | MA_ADD[6],AV55,MD_DATA[9],CR5,RSVD,AD44,RSVD,CK46,VDDCR_CPU,BT37,VSS,F47,VSS,AT39,VSS,CK40 | ||

| + | MA_ADD[7],AV53,MD_DATA[10],CL6,RSVD,AD46,RSVD,CK48,VDDCR_CPU,BU20,VSS,F49,VSS,AT42,VSS,CK41 | ||

| + | MA_ADD[8],AW53,MD_DATA[11],CL5,RSVD,AD48,RSVD,CL29,VDDCR_CPU,BU34,VSS,F52,VSS,AT45,VSS,CK42 | ||

| + | MA_ADD[9],AT55,MD_DATA[12],CT7,RSVD,AE12,RSVD,CL30,VDDCR_CPU,BU36,VSS,F54,VSS,AU19,VSS,CK43 | ||

| + | MA_ADD[10],BH53,MD_DATA[13],CT5,RSVD,AE13,RSVD,CL32,VDDCR_CPU,BV19,VSS,G2,VSS,AU21,VSS,CK44 | ||

| + | MA_ADD[11],AU54,MD_DATA[14],CM7,RSVD,AE15,RSVD,CL33,VDDCR_CPU,BV21,VSS,G4,VSS,AU35,VSS,CK45 | ||

| + | MA_ADD[12],AU53,MD_DATA[15],CM5,RSVD,AE16,RSVD,CL35,VDDCR_CPU,BV35,VSS,G7,VSS,AU37,VSS,CK47 | ||

| + | MA_ADD[13],BN53,MD_DATA[16],CJ6,RSVD,AE39,RSVD,CL36,VDDCR_CPU,BV37,VSS,G9,VSS,AU38,VSS,CK49 | ||

| + | MA_ADD_17,BP53,MD_DATA[17],CJ5,RSVD,AE41,RSVD,CL38,VDDCR_CPU,BW20,VSS,G11,VSS,AU43,VSS,CK52 | ||

| + | MA_ALERT_L,AT53,MD_DATA[18],CE6,RSVD,AE42,RSVD,CL39,VDDCR_CPU,BW34,VSS,G13,VSS,AV18,VSS,CK54 | ||

| + | MA_BANK[0],BJ53,MD_DATA[19],CE5,RSVD,AE44,RSVD,CL41,VDDCR_CPU,BW36,VSS,G16,VSS,AV20,VSS,CL2 | ||

| + | MA_BANK[1],BJ54,MD_DATA[20],CK7,RSVD,AE46,RSVD,CL42,VDDCR_CPU,BY21,VSS,G19,VSS,AV22,VSS,CL4 | ||

| + | MA_BG[0],AR54,MD_DATA[21],CK5,RSVD,AE47,RSVD,CL44,VDDCR_CPU,BY23,VSS,G22,VSS,AV36,VSS,CL7 | ||

| + | MA_BG[1],AP55,MD_DATA[22],CF7,RSVD,AF9,RSVD,CL46,VDDCR_CPU,BY25,VSS,G25,VSS,AV42,VSS,CL9 | ||

| + | MA_CAS_L_ADD[15],BM55,MD_DATA[23],CF5,RSVD,AF10,RSVD,CL47,VDDCR_CPU,BY27,VSS,G28,VSS,AV45,VSS,CL31 | ||

| + | MA_CHECK[0],AE54,MD_DATA[24],CC6,RSVD,AF12,RSVD,CM29,VDDCR_CPU,BY29,VSS,G31,VSS,AW19,VSS,CL34 | ||

| + | MA_CHECK[1],AF55,MD_DATA[25],CC5,RSVD,AF14,RSVD,CM31,VDDCR_CPU,BY31,VSS,G34,VSS,AW21,VSS,CL37 | ||

| + | MA_CHECK[2],AJ54,MD_DATA[26],BW6,RSVD,AF15,RSVD,CM32,VDDCR_CPU,BY33,VSS,G37,VSS,AW35,VSS,CL40 | ||

| + | MA_CHECK[3],AK55,MD_DATA[27],BW5,RSVD,AF17,RSVD,CM34,VDDCR_CPU,BY35,VSS,G40,VSS,AW37,VSS,CL43 | ||

| + | MA_CHECK[4],AE53,MD_DATA[28],CD7,RSVD,AF40,RSVD,CM35,VDDCR_CPU_SENSE,Y15,VSS,G43,VSS,AW38,VSS,CL45 | ||

| + | MA_CHECK[5],AF53,MD_DATA[29],CD5,RSVD,AF41,RSVD,CM37,VDDCR_SOC,CA20,VSS,G45,VSS,AW42,VSS,CL48 | ||

| + | MA_CHECK[6],AJ53,MD_DATA[30],BY7,RSVD,AF43,RSVD,CM38,VDDCR_SOC,CA22,VSS,G48,VSS,AW43,VSS,CL50 | ||

| + | MA_CHECK[7],AK53,MD_DATA[31],BY5,RSVD,AF44,RSVD,CM40,VDDCR_SOC,CA24,VSS,G50,VSS,AW44,VSS,CL52 | ||

| + | MA_C[0],BU53,MD_DATA[32],AC5,RSVD,AF46,RSVD,CM41,VDDCR_SOC,CA26,VSS,G52,VSS,AY18,VSS,CL55 | ||

| + | MA_C[1],BT53,MD_DATA[33],AC6,RSVD,AF48,RSVD,CM43,VDDCR_SOC,CA28,VSS,G55,VSS,AY20,VSS,CM1 | ||

| + | MA_C[2],BR53,MD_DATA[34],W5,RSVD,AG8,RSVD,CM44,VDDCR_SOC,CB19,VSS,H1,VSS,AY22,VSS,CM4 | ||

| + | MA_DATA[0],A53,MD_DATA[35],W6,RSVD,AG10,RSVD,CM48,VDDCR_SOC,CB21,VSS,H4,VSS,AY24,VSS,CM6 | ||

| + | MA_DATA[1],B54,MD_DATA[36],AD5,RSVD,AG12,RSVD,CN12,VDDCR_SOC,CB23,VSS,H6,VSS,AY26,VSS,CM8 | ||

| + | MA_DATA[2],E54,MD_DATA[37],AD7,RSVD,AG13,RSVD,CN29,VDDCR_SOC,CB25,VSS,H8,VSS,AY30,VSS,CM11 | ||

| + | MA_DATA[3],F55,MD_DATA[38],Y5,RSVD,AG15,RSVD,CN30,VDDCR_SOC,CB27,VSS,H12,VSS,AY32,VSS,CM12 | ||

| + | MA_DATA[4],A52,MD_DATA[39],Y7,RSVD,AG16,RSVD,CN32,VDDCR_SOC,CC11,VSS,H47,VSS,AY34,VSS,CM15 | ||

| + | MA_DATA[5],B53,MD_DATA[40],U5,RSVD,AG39,RSVD,CN33,VDDCR_SOC,CC13,VSS,H49,VSS,AY36,VSS,CM18 | ||

| + | MA_DATA[6],E53,MD_DATA[41],U6,RSVD,AG41,RSVD,CN35,VDDCR_SOC,CC16,VSS,H52,VSS,BA19,VSS,CM21 | ||

| + | MA_DATA[7],F53,MD_DATA[42],N5,RSVD,AG42,RSVD,CN36,VDDCR_SOC,CC18,VSS,H54,VSS,BA21,VSS,CM24 | ||

| + | MA_DATA[8],G54,MD_DATA[43],N6,RSVD,AG44,RSVD,CN38,VDDCR_SOC,CC20,VSS,J2,VSS,BA23,VSS,CM27 | ||

| + | MA_DATA[9],H55,MD_DATA[44],V5,RSVD,AG46,RSVD,CN39,VDDCR_SOC,CC22,VSS,J4,VSS,BA25,VSS,CM30 | ||

| + | MA_DATA[10],L54,MD_DATA[45],V7,RSVD,AG47,RSVD,CN41,VDDCR_SOC,CC24,VSS,J7,VSS,BA29,VSS,CM33 | ||

| + | MA_DATA[11],M55,MD_DATA[46],P5,RSVD,AH9,RSVD,CN42,VDDCR_SOC,CC26,VSS,J9,VSS,BA31,VSS,CM36 | ||

| + | MA_DATA[12],G53,MD_DATA[47],P7,RSVD,AH10,RSVD,CN44,VDDCR_SOC,CC28,VSS,J11,VSS,BA33,VSS,CM39 | ||

| + | MA_DATA[13],H53,MD_DATA[48],L5,RSVD,AH12,RSVD,CP13,VDDCR_SOC,CE11,VSS,J13,VSS,BA35,VSS,CM42 | ||

| + | MA_DATA[14],L53,MD_DATA[49],L6,RSVD,AH14,RSVD,CP14,VDDCR_SOC,CE13,VSS,J16,VSS,BA37,VSS,CM45 | ||

| + | MA_DATA[15],M53,MD_DATA[50],G5,RSVD,AH15,RSVD,CP16,VDDCR_SOC,CE16,VSS,J19,VSS,BA38,VSS,CM47 | ||

| + | MA_DATA[16],N54,MD_DATA[51],G6,RSVD,AH17,RSVD,CP17,VDDCR_SOC,CE19,VSS,J22,VSS,BB18,VSS,CM49 | ||

| + | MA_DATA[17],P55,MD_DATA[52],M5,RSVD,AH40,RSVD,CP19,VDDCR_SOC,CE22,VSS,J25,VSS,BB20,VSS,CM52 | ||

| + | MA_DATA[18],U54,MD_DATA[53],M7,RSVD,AH41,RSVD,CP20,VDDCR_SOC,CE25,VSS,J28,VSS,BB22,VSS,CM54 | ||

| + | MA_DATA[19],V55,MD_DATA[54],H5,RSVD,AH43,RSVD,CP22,VDDCR_SOC,CE28,VSS,J31,VSS,BB24,VSS,CN2 | ||

| + | MA_DATA[20],N53,MD_DATA[55],H7,RSVD,AH44,RSVD,CP23,VDDCR_SOC,CG11,VSS,J34,VSS,BB26,VSS,CN4 | ||

| + | MA_DATA[21],P53,MD_DATA[56],E5,RSVD,AH46,RSVD,CP25,VDDCR_SOC,CG13,VSS,J37,VSS,BB28,VSS,CN7 | ||

| + | MA_DATA[22],U53,MD_DATA[57],E6,RSVD,AH48,RSVD,CP26,VDDCR_SOC,CG16,VSS,J40,VSS,BB30,VSS,CN9 | ||

| + | MA_DATA[23],V53,MD_DATA[58],B7,RSVD,AJ8,RSVD,CP28,VDDCR_SOC,CG19,VSS,J43,VSS,BB32,VSS,CN31 | ||

| + | MA_DATA[24],W54,MD_DATA[59],A7,RSVD,AJ10,RSVD,CR8,VDDCR_SOC,CG22,VSS,J45,VSS,BB34,VSS,CN34 | ||

| + | MA_DATA[25],Y55,MD_DATA[60],F5,RSVD,AJ12,RSVD,CR10,VDDCR_SOC,CG25,VSS,J48,VSS,BB36,VSS,CN37 | ||

| + | MA_DATA[26],AC54,MD_DATA[61],F7,RSVD,AJ13,RSVD,CR12,VDDCR_SOC,CG28,VSS,J50,VSS,BC19,VSS,CN40 | ||

| + | MA_DATA[27],AD55,MD_DATA[62],B6,RSVD,AJ15,RSVD,CR14,VDDCR_SOC,CJ11,VSS,J52,VSS,BC21,VSS,CN43 | ||

| + | MA_DATA[28],W53,MD_DATA[63],A6,RSVD,AJ16,RSVD,CR15,VDDCR_SOC,CJ13,VSS,J55,VSS,BC23,VSS,CN45 | ||

| + | MA_DATA[29],Y53,MD_DQS_H[0],CW5,RSVD,AJ39,RSVD,CR17,VDDCR_SOC,CJ16,VSS,K1,VSS,BC25,VSS,CN48 | ||

| + | MA_DATA[30],AC53,MD_DQS_H[1],CN5,RSVD,AJ41,RSVD,CR18,VDDCR_SOC,CJ19,VSS,K4,VSS,BC27,VSS,CN50 | ||

| + | MA_DATA[31],AD53,MD_DQS_H[2],CG5,RSVD,AJ42,RSVD,CR20,VDDCR_SOC,CJ22,VSS,K6,VSS,BC29,VSS,CN52 | ||

| + | MA_DATA[32],BW53,MD_DQS_H[3],CA5,RSVD,AJ44,RSVD,CR21,VDDCR_SOC,CJ25,VSS,K8,VSS,BC31,VSS,CN55 | ||

| + | MA_DATA[33],BY53,MD_DQS_H[4],AA6,RSVD,AJ46,RSVD,CR23,VDDCR_SOC,CJ28,VSS,K12,VSS,BC33,VSS,CP1 | ||

| + | MA_DATA[34],CC53,MD_DQS_H[5],R6,RSVD,AJ47,RSVD,CR24,VDDCR_SOC,CL11,VSS,K47,VSS,BC35,VSS,CP4 | ||

| + | MA_DATA[35],CD53,MD_DQS_H[6],J6,RSVD,AK9,RSVD,CR26,VDDCR_SOC,CL13,VSS,K49,VSS,BC37,VSS,CP6 | ||

| + | MA_DATA[36],BW54,MD_DQS_H[7],C6,RSVD,AK10,RSVD,CR27,VDDCR_SOC,CL16,VSS,K52,VSS,BC38,VSS,CP8 | ||

| + | MA_DATA[37],BY55,MD_DQS_H[8],BR5,RSVD,AK12,RSVD,CT13,VDDCR_SOC,CL19,VSS,K54,VSS,BD12,VSS,CP11 | ||

| + | MA_DATA[38],CC54,MD_DQS_H[9],CY7,RSVD,AK14,RSVD,CT14,VDDCR_SOC,CL22,VSS,L2,VSS,BD13,VSS,CP12 | ||

| + | MA_DATA[39],CD55,MD_DQS_H[10],CP7,RSVD,AK15,RSVD,CT16,VDDCR_SOC,CL25,VSS,L4,VSS,BD14,VSS,CP15 | ||

| + | MA_DATA[40],CE53,MD_DQS_H[11],CH7,RSVD,AK17,RSVD,CT17,VDDCR_SOC,CL28,VSS,L7,VSS,BD18,VSS,CP18 | ||

| + | MA_DATA[41],CF53,MD_DQS_H[12],CB7,RSVD,AK40,RSVD,CT19,VDDCR_SOC,CN11,VSS,L9,VSS,BD20,VSS,CP21 | ||

| + | MA_DATA[42],CJ53,MD_DQS_H[13],AB5,RSVD,AK41,RSVD,CT20,VDDCR_SOC,CN13,VSS,L11,VSS,BD22,VSS,CP24 | ||

| + | MA_DATA[43],CK53,MD_DQS_H[14],T5,RSVD,AK43,RSVD,CT22,VDDCR_SOC,CN16,VSS,L13,VSS,BD36,VSS,CP27 | ||

| + | MA_DATA[44],CE54,MD_DQS_H[15],K5,RSVD,AK44,RSVD,CT23,VDDCR_SOC,CN19,VSS,L16,VSS,BE11,VSS,CP30 | ||

| + | MA_DATA[45],CF55,MD_DQS_H[16],D5,RSVD,AK46,RSVD,CT25,VDDCR_SOC,CN22,VSS,L19,VSS,BE14,VSS,CP33 | ||

| + | MA_DATA[46],CJ54,MD_DQS_H[17],BT7,RSVD,AK48,RSVD,CT26,VDDCR_SOC,CN25,VSS,L22,VSS,BE19,VSS,CP36 | ||

| + | MA_DATA[47],CK55,MD_DQS_L[0],CY5,RSVD,AL8,RSVD,CU8,VDDCR_SOC,CN28,VSS,L25,VSS,BE21,VSS,CP39 | ||

| + | MA_DATA[48],CL53,MD_DQS_L[1],CP5,RSVD,AL10,RSVD,CU10,VDDCR_SOC,CR11,VSS,L28,VSS,BE35,VSS,CP42 | ||

| + | MA_DATA[49],CM53,MD_DQS_L[2],CH5,RSVD,AL12,RSVD,CU46,VDDCR_SOC,CR13,VSS,L31,VSS,BE37,VSS,CP45 | ||

| + | MA_DATA[50],CR53,MD_DQS_L[3],CB5,RSVD,AL13,RSVD,CU47,VDDCR_SOC,CR16,VSS,L34,VSS,BE38,VSS,CP47 | ||

| + | MA_DATA[51],CT53,MD_DQS_L[4],AB7,RSVD,AL15,RSVD,CV9,VDDCR_SOC,CR19,VSS,L37,VSS,BF13,VSS,CP49 | ||

| + | MA_DATA[52],CL54,MD_DQS_L[5],T7,RSVD,AL16,RSVD,CV10,VDDCR_SOC,CR22,VSS,L40,VSS,BF18,VSS,CP52 | ||

| + | MA_DATA[53],CM55,MD_DQS_L[6],K7,RSVD,AL39,RSVD,CV20,VDDCR_SOC,CR25,VSS,L43,VSS,BF20,VSS,CP54 | ||

| + | MA_DATA[54],CR54,MD_DQS_L[7],D7,RSVD,AL41,RSVD,CW19,VDDCR_SOC,CR28,VSS,L48,VSS,BF22,VSS,CR2 | ||

| + | MA_DATA[55],CT55,MD_DQS_L[8],BT5,RSVD,AL42,RSVD,CY20,VDDCR_SOC,CV11,VSS,L50,VSS,BF36,VSS,CR4 | ||

| + | MA_DATA[56],CU53,MD_DQS_L[9],CW6,RSVD,AL44,RSVD,CY41,VDDCR_SOC,CV13,VSS,L52,VSS,BG11,VSS,CR7 | ||

| + | MA_DATA[57],CV53,MD_DQS_L[10],CN6,RSVD,AM9,RSVD,CY42,VDDCR_SOC,CV16,VSS,L55,VSS,BG14,VSS,CR9 | ||

| + | MA_DATA[58],DB53,MD_DQS_L[11],CG6,RSVD,AM10,RSVD,DA43,VDDCR_SOC,CV19,VSS,M1,VSS,BG17,VSS,CR31 | ||

| + | MA_DATA[59],DB52,MD_DQS_L[12],CA6,RSVD,AM12,RSVD,DB17,VDDCR_SOC,CV22,VSS,M4,VSS,BG19,VSS,CR34 | ||

| + | MA_DATA[60],CU54,MD_DQS_L[13],AA5,RSVD,AM14,RSVD,DB21,VDDCR_SOC,CV25,VSS,M6,VSS,BG21,VSS,CR37 | ||

| + | MA_DATA[61],CV55,MD_DQS_L[14],R5,RSVD,AM15,RSVD,DB44,VDDCR_SOC,CV28,VSS,M8,VSS,BG35,VSS,CR40 | ||

| + | MA_DATA[62],DA54,MD_DQS_L[15],J5,RSVD,AM17,RSVD,DB47,VDDCR_SOC,CY11,VSS,M12,VSS,BG37,VSS,CR43 | ||

| + | MA_DATA[63],DA53,MD_DQS_L[16],C5,RSVD,AM40,RSVD1,CW18,VDDCR_SOC,CY13,VSS,M47,VSS,BG38,VSS,CR45 | ||

| + | MA_DQS_H[0],D55,MD_DQS_L[17],BR6,RSVD,AM41,RSVD2,DA16,VDDCR_SOC,CY16,VSS,M49,VSS,BH13,VSS,CR48 | ||

| + | MA_DQS_H[1],K55,MD_EVENT_L,AT5,RSVD,AM43,RSVD3,CV18,VDDCR_SOC,CY19,VSS,M52,VSS,BH16,VSS,CR50 | ||

| + | MA_DQS_H[2],T55,MD_PAROUT,AT7,RSVD,AM44,RTCCLK,E38,VDDCR_SOC,CY22,VSS,M54,VSS,BH17,VSS,CR52 | ||

| + | MA_DQS_H[3],AB55,MD_RAS_L_ADD[16],AN5,RSVD,AN8,S0A3_GPIO_0/AGPIO10_0/SGPIO0_CLK/MDIO0_SCL,DA28,VDDCR_SOC,CY25,VSS,N2,VSS,BH18,VSS,CR55 | ||

| + | MA_DQS_H[4],CB53,MD_RESET_L,BL6,RSVD,AN10,S0A3_GPIO_1/EGPIO10_1/SGPIO1_CLK/MDIO2_SCL,E26,VDDCR_SOC,CY28,VSS,N4,VSS,BH20,VSS,CT1 | ||

| + | MA_DQS_H[5],CH53,MD_WE_L_ADD[14],AM5,RSVD,AN42,SATA_ACT_0_L/AGPIO130_0,CT46,VDDCR_SOC_S5,CA30,VSS,N7,VSS,BH22,VSS,CT4 | ||

| + | MA_DQS_H[6],CP53,MD_ZVSS,BA5,RSVD,AN44,SATA_ACT_1_L/EGPIO130_1,CL8,VDDCR_SOC_S5,CB29,VSS,N9,VSS,BH36,VSS,CT6 | ||

| + | MA_DQS_H[7],CY53,NV_SAVE_L,A38,RSVD,AP9,SA[0],D42,VDDCR_SOC_S5,CC30,VSS,N11,VSS,BJ10,VSS,CT8 | ||

| + | MA_DQS_H[8],AH55,P0A_ZVSS,CT29,RSVD,AP10,SA[1],C43,VDDCR_SOC_S5_SENSE,CC32,VSS,N12,VSS,BJ11,VSS,CT11 | ||

| + | MA_DQS_H[9],C53,P0_RXN[0]/SATA00_RXN,CG44,RSVD,AP12,SA[2],D44,VDDCR_SOC_SENSE,CB31,VSS,N13,VSS,BJ14,VSS,CT12 | ||

| + | MA_DQS_H[10],J53,P0_RXN[1]/SATA01_RXN,CH43,RSVD,AP14,SCL0/I2C2_SCL/EGPIO113/SPD_SCL,DA42,VDDIO_AUDIO,AG18,VSS,N14,VSS,BJ15,VSS,CT15 | ||

| + | MA_DQS_H[11],R53,P0_RXN[2]/SATA02_RXN,CJ42,RSVD,AP15,SCL1/I2C3_SCL/AGPIO19/BMC_SCL,CW15,VDDIO_MEM_S3_AB,AM47,VSS,N15,VSS,BJ17,VSS,CT18 | ||

| + | MA_DQS_H[12],AA53,P0_RXN[3]/SATA03_RXN,CG41,RSVD,AP17,SDA0/I2C2_SDA/EGPIO114/SPD_SDA,DB42,VDDIO_MEM_S3_AB,AM49,VSS,N16,VSS,BJ19,VSS,CT21 | ||

| + | MA_DQS_H[13],CA54,P0_RXN[4]/SATA04_RXN/XGBE00_RXN,CH40,RSVD,AP43,SDA1/I2C3_SDA/AGPIO20/BMC_SDA,CV15,VDDIO_MEM_S3_AB,AM52,VSS,N17,VSS,BJ21,VSS,CT24 | ||

| + | MA_DQS_H[14],CG54,P0_RXN[5]/SATA05_RXN/XGBE01_RXN,CJ39,RSVD,AP44,SERIRQ/AGPIO87,CW33,VDDIO_MEM_S3_AB,AM54,VSS,N18,VSS,BJ35,VSS,CT27 | ||

| + | MA_DQS_H[15],CN54,P0_RXN[6]/SATA06_RXN/XGBE02_RXN,CG38,RSVD,AP48,SIC,DA39,VDDIO_MEM_S3_AB,AN45,VSS,N19,VSS,BJ37,VSS,CT30 | ||

| + | MA_DQS_H[16],CW54,P0_RXN[7]/SATA07_RXN/XGBE03_RXN,CH37,RSVD,AR8,SID,DB39,VDDIO_MEM_S3_AB,AN48,VSS,N20,VSS,BJ38,VSS,CT33 | ||

| + | MA_DQS_H[17],AG53,P0_RXN[8],CJ36,RSVD,AR10,SLP_S3_L,DA21,VDDIO_MEM_S3_AB,AN50,VSS,N21,VSS,BK9,VSS,CT36 | ||

| + | MA_DQS_L[0],C54,P0_RXN[9],CG35,RSVD,AR12,SLP_S5_L,CY23,VDDIO_MEM_S3_AB,AN52,VSS,N22,VSS,BK10,VSS,CT39 | ||

| + | MA_DQS_L[1],J54,P0_RXN[10],CH34,RSVD,AR13,SP3R1,C44,VDDIO_MEM_S3_AB,AP40,VSS,N23,VSS,BK13,VSS,CT42 | ||

| + | MA_DQS_L[2],R54,P0_RXN[11],CJ33,RSVD,AR15,SP3R2,F12,VDDIO_MEM_S3_AB,AP47,VSS,N24,VSS,BK15,VSS,CT45 | ||

| + | MA_DQS_L[3],AA54,P0_RXN[12],CG32,RSVD,AR16,SPI_CLK/ESPI_CLK,DB30,VDDIO_MEM_S3_AB,AP49,VSS,N25,VSS,BK16,VSS,CT47 | ||

| + | MA_DQS_L[4],CA53,P0_RXN[13],CH31,RSVD,AR42,SPI_CS1_L/EGPIO118,DB32,VDDIO_MEM_S3_AB,AP52,VSS,N26,VSS,BK17,VSS,CT49 | ||

| + | MA_DQS_L[5],CG53,P0_RXN[14],CJ30,RSVD,AR44,SPI_CS2_L/ESPI_CS_L/EGPIO119,DA33,VDDIO_MEM_S3_AB,AP54,VSS,N27,VSS,BK20,VSS,CT52 | ||

| + | MA_DQS_L[6],CN53,P0_RXN[15],CG29,RSVD,AR46,SPI_DI/ESPI_DAT1,DA30,VDDIO_MEM_S3_AB,AR41,VSS,N28,VSS,BK22,VSS,CT54 | ||

| + | MA_DQS_L[7],CW53,P0_RXP[0]/SATA00_RXP,CH44,RSVD,AR47,SPI_DO/ESPI_DAT0,CY32,VDDIO_MEM_S3_AB,AR45,VSS,N29,VSS,BK36,VSS,CU2 | ||

| + | MA_DQS_L[8],AG54,P0_RXP[1]/SATA01_RXP,CG42,RSVD,AT9,SPI_HOLD_L/ESPI_DAT3/EGPIO133,CY33,VDDIO_MEM_S3_AB,AR48,VSS,N30,VSS,BK38,VSS,CU4 | ||

| + | MA_DQS_L[9],D53,P0_RXP[2]/SATA02_RXP,CJ41,RSVD,AT10,SPI_TPM_CS_L/AGPIO76/PSP_ROM_CS_L,CY30,VDDIO_MEM_S3_AB,AR50,VSS,N31,VSS,BK39,VSS,CU7 | ||

| + | MA_DQS_L[10],K53,P0_RXP[3]/SATA03_RXP,CH41,RSVD,AT12,SPI_WP_L/ESPI_DAT2/EGPIO122,DA31,VDDIO_MEM_S3_AB,AR52,VSS,N32,VSS,BK40,VSS,CU9 | ||

| + | MA_DQS_L[11],T53,P0_RXP[4]/SATA04_RXP/XGBE00_RXP,CG39,RSVD,AT14,SPKR/AGPIO91,CV48,VDDIO_MEM_S3_AB,AR55,VSS,N33,VSS,BK41,VSS,CU11 | ||

| + | MA_DQS_L[12],AB53,P0_RXP[5]/SATA05_RXP/XGBE01_RXP,CJ38,RSVD,AT15,SVC_CPU,A44,VDDIO_MEM_S3_AB,AT38,VSS,N34,VSS,BK42,VSS,CU12 | ||

| + | MA_DQS_L[13],CB55,P0_RXP[6]/SATA06_RXP/XGBE02_RXP,CH38,RSVD,AT17,SVC_SOC,CV35,VDDIO_MEM_S3_AB,AT40,VSS,N35,VSS,BK43,VSS,CU13 | ||

| + | MA_DQS_L[14],CH55,P0_RXP[7]/SATA07_RXP/XGBE03_RXP,CG36,RSVD,AT41,SVD_CPU,B44,VDDIO_MEM_S3_AB,AT47,VSS,N36,VSS,BK44,VSS,CU14 | ||

| + | MA_DQS_L[15],CP55,P0_RXP[8],CJ35,RSVD,AT43,SVD_SOC,CV36,VDDIO_MEM_S3_AB,AT49,VSS,N37,VSS,BK45,VSS,CU15 | ||

| + | MA_DQS_L[16],CY55,P0_RXP[9],CH35,RSVD,AT44,SVT_CPU,A43,VDDIO_MEM_S3_AB,AT52,VSS,N38,VSS,BL8,VSS,CU16 | ||

| + | MA_DQS_L[17],AH53,P0_RXP[10],CG33,RSVD,AT46,SVT_SOC,CW37,VDDIO_MEM_S3_AB,AT54,VSS,N39,VSS,BL10,VSS,CU17 | ||

| + | MA_EVENT_L,BF53,P0_RXP[11],CJ32,RSVD,AT48,SYS_RESET_L/AGPIO1,A35,VDDIO_MEM_S3_AB,AU41,VSS,N40,VSS,BL11,VSS,CU18 | ||

| + | MA_PAROUT,BG53,P0_RXP[12],CH32,RSVD,AU8,TCK,B27,VDDIO_MEM_S3_AB,AU45,VSS,N41,VSS,BL14,VSS,CU19 | ||

| + | MA_RAS_L_ADD[16],BK55,P0_RXP[13],CG30,RSVD,AU10,TDI,A25,VDDIO_MEM_S3_AB,AU48,VSS,N42,VSS,BL17,VSS,CU20 | ||

| + | MA_RESET_L,AM53,P0_RXP[14],CJ29,RSVD,AU12,TDO,A26,VDDIO_MEM_S3_AB,AU50,VSS,N43,VSS,BL18,VSS,CU21 | ||

| + | MA_WE_L_ADD[14],BK53,P0_RXP[15],CH29,RSVD,AU13,TEST4[0],CK34,VDDIO_MEM_S3_AB,AU52,VSS,N44,VSS,BL19,VSS,CU22 | ||

| + | MA_ZVSS,BB53,P0_TXN[0]/SATA00_TXN,CP44,RSVD,AU15,TEST4[1],AC23,VDDIO_MEM_S3_AB,AV38,VSS,N45,VSS,BL21,VSS,CU23 | ||

| + | MB0_CKE[0],AN51,P0_TXN[1]/SATA01_TXN,CT43,RSVD,AU16,TEST5[0],CJ34,VDDIO_MEM_S3_AB,AV40,VSS,N48,VSS,BL35,VSS,CU24 | ||

| + | MB0_CKE[1],AM51,P0_TXN[2]/SATA02_TXN,CR42,RSVD,AU39,TEST5[1],AB24,VDDIO_MEM_S3_AB,AV47,VSS,N50,VSS,BL37,VSS,CU25 | ||

| + | MB0_CLK_H[0],BC51,P0_TXN[3]/SATA03_TXN,CP41,RSVD,AU40,TEST6[0],CJ44,VDDIO_MEM_S3_AB,AV49,VSS,N52,VSS,BL38,VSS,CU26 | ||

| + | MB0_CLK_H[1],BC49,P0_TXN[4]/SATA04_TXN/XGBE00_TXN,CT40,RSVD,AU42,TEST6[1],U12,VDDIO_MEM_S3_AB,AV52,VSS,N55,VSS,BL40,VSS,CU27 | ||

| + | MB0_CLK_L[0],BD51,P0_TXN[5]/SATA05_TXN/XGBE01_TXN,CR39,RSVD,AU44,TEST14,E40,VDDIO_MEM_S3_AB,AV54,VSS,P1,VSS,BL43,VSS,CU28 | ||

| + | MB0_CLK_L[1],BD50,P0_TXN[6]/SATA06_TXN/XGBE02_TXN,CP38,RSVD,AU46,TEST15,E41,VDDIO_MEM_S3_AB,AW41,VSS,P4,VSS,BM1,VSS,CU29 | ||

| + | MB0_CS_L[0],BL49,P0_TXN[7]/SATA07_TXN/XGBE03_TXN,CT37,RSVD,AU47,TEST16,D21,VDDIO_MEM_S3_AB,AW45,VSS,P6,VSS,BM2,VSS,CU30 | ||

| + | MB0_CS_L[1],BP50,P0_TXN[8],CR36,RSVD,AV9,TEST17,C20,VDDIO_MEM_S3_AB,AW48,VSS,P8,VSS,BM3,VSS,CU31 | ||

| + | MB0_ODT[0],BN51,P0_TXN[9],CP35,RSVD,AV10,TEST31,D33,VDDIO_MEM_S3_AB,AW50,VSS,P12,VSS,BM4,VSS,CU32 | ||

| + | MB0_ODT[1],BT51,P0_TXN[10],CT34,RSVD,AV12,TEST40A,BC53,VDDIO_MEM_S3_AB,AW52,VSS,P47,VSS,BM5,VSS,CU33 | ||

| + | MB1_CKE[0],AP50,P0_TXN[11],CR33,RSVD,AV14,TEST40B,BB50,VDDIO_MEM_S3_AB,AW55,VSS,P49,VSS,BM6,VSS,CU34 | ||

| + | MB1_CKE[1],AN49,P0_TXN[12],CP32,RSVD,AV15,TEST40C,AY3,VDDIO_MEM_S3_AB,AY38,VSS,P52,VSS,BM7,VSS,CU35 | ||

| + | MB1_CLK_H[0],BE51,P0_TXN[13],CT31,RSVD,AV17,TEST40D,BA6,VDDIO_MEM_S3_AB,AY39,VSS,P54,VSS,BM8,VSS,CU36 | ||

| + | MB1_CLK_H[1],BE49,P0_TXN[14],CR30,RSVD,AV39,TEST41[0],CY26,VDDIO_MEM_S3_AB,AY42,VSS,R2,VSS,BM9,VSS,CU37 | ||

| + | MB1_CLK_L[0],BF51,P0_TXN[15],CP29,RSVD,AV41,TEST41[1],B16,VDDIO_MEM_S3_AB,AY45,VSS,R4,VSS,BM10,VSS,CU38 | ||

| + | MB1_CLK_L[1],BF50,P0_TXP[0]/SATA00_TXP,CR44,RSVD,AV43,TEST47[0],D18,VDDIO_MEM_S3_AB,AY47,VSS,R7,VSS,BM11,VSS,CU39 | ||

| + | MB1_CS_L[0],BK50,P0_TXP[1]/SATA01_TXP,CT44,RSVD,AV44,TEST47[1],CW21,VDDIO_MEM_S3_AB,AY49,VSS,R9,VSS,BM13,VSS,CU40 | ||

| + | MB1_CS_L[1],BP51,P0_TXP[2]/SATA02_TXP,CP43,RSVD,AV46,THERMTRIP_L,A28,VDDIO_MEM_S3_AB,AY52,VSS,R11,VSS,BM16,VSS,CU41 | ||

| + | MB1_ODT[0],BM50,P0_TXP[3]/SATA03_TXP,CR41,RSVD,AV48,TMS,C26,VDDIO_MEM_S3_AB,AY54,VSS,R13,VSS,BM18,VSS,CU42 | ||

| + | MB1_ODT[1],BT50,P0_TXP[4]/SATA04_TXP/XGBE00_TXP,CT41,RSVD,AW8,TRST_L,C25,VDDIO_MEM_S3_AB,BA40,VSS,R16,VSS,BM20,VSS,CU43 | ||

| + | MB_ACT_L,AP51,P0_TXP[5]/SATA05_TXP/XGBE01_TXP,CP40,RSVD,AW10,UART0_CTS_L/UART2_RXD/EGPIO135,CV41,VDDIO_MEM_S3_AB,BA43,VSS,R19,VSS,BM22,VSS,CU44 | ||

| + | MB_ADD[0],BH51,P0_TXP[6]/SATA06_TXP/XGBE02_TXP,CR38,RSVD,AW12,UART0_INTR/AGPIO139,CV38,VDDIO_MEM_S3_AB,BA45,VSS,R22,VSS,BM36,VSS,CU45 | ||

| + | MB_ADD[1],BA49,P0_TXP[7]/SATA07_TXP/XGBE03_TXP,CT38,RSVD,AW13,UART0_RTS_L/UART2_TXD/EGPIO137,CW40,VDDIO_MEM_S3_AB,BA48,VSS,R25,VSS,BM38,VSS,CU48 | ||

| + | MB_ADD[2],BA51,P0_TXP[8],CP37,RSVD,AW15,UART0_RXD/EGPIO136,CV39,VDDIO_MEM_S3_AB,BA50,VSS,R28,VSS,BM39,VSS,CU50 | ||

| + | MB_ADD[3],AY51,P0_TXP[9],CR35,RSVD,AW16,UART0_TXD/EGPIO138,CW39,VDDIO_MEM_S3_AB,BA52,VSS,R31,VSS,BM42,VSS,CU52 | ||

| + | MB_ADD[4],AY50,P0_TXP[10],CT35,RSVD,AW39,UART1_CTS_L/UART3_TXD/EGPIO140,CY38,VDDIO_MEM_S3_AB,BB38,VSS,R34,VSS,BM45,VSS,CU55 | ||

| + | MB_ADD[5],AW51,P0_TXP[11],CP34,RSVD,AW40,UART1_INTR/AGPIO144,DA36,VDDIO_MEM_S3_AB,BB39,VSS,R37,VSS,BN2,VSS,CV1 | ||

| + | MB_ADD[6],AW49,P0_TXP[12],CR32,RSVD,AW46,UART1_RTS_L/UART3_RXD/EGPIO142,DB38,VDDIO_MEM_S3_AB,BB42,VSS,R40,VSS,BN4,VSS,CV4 | ||

| + | MB_ADD[7],AV50,P0_TXP[13],CT32,RSVD,AW47,UART1_RXD/EGPIO141,DB36,VDDIO_MEM_S3_AB,BB45,VSS,R43,VSS,BN7,VSS,CV6 | ||

| + | MB_ADD[8],AV51,P0_TXP[14],CP31,RSVD,AY9,UART1_TXD/EGPIO143,DA37,VDDIO_MEM_S3_AB,BB47,VSS,R45,VSS,BN9,VSS,CV8 | ||

| + | MB_ADD[9],AU49,P0_TXP[15],CR29,RSVD,AY10,USB_0_0_ZVSS,DB12,VDDIO_MEM_S3_AB,BB49,VSS,R48,VSS,BN11,VSS,CV31 | ||

| + | MB_ADD[10],BJ51,P1B_ZVSS,CF28,RSVD,AY12,USB_0_1_ZVSS,CY12,VDDIO_MEM_S3_AB,BB52,VSS,R50,VSS,BN14,VSS,CV34 | ||

| + | MB_ADD[11],AU51,P1_RXN[0],CD28,RSVD,AY14,USB_0_2_ZVSS,CT28,VDDIO_MEM_S3_AB,BB54,VSS,R52,VSS,BN17,VSS,CV37 | ||

| + | MB_ADD[12],AT51,P1_RXN[1],CE26,RSVD,AY15,USB_0_3_ZVSS,CF29,VDDIO_MEM_S3_AB,BC40,VSS,R55,VSS,BN18,VSS,CV40 | ||

| + | MB_ADD[13],BN49,P1_RXN[2],CF26,RSVD,AY17,USB_0_HSD0N,CY18,VDDIO_MEM_S3_AB,BC43,VSS,T1,VSS,BN19,VSS,CV43 | ||

| + | MB_ADD_17,BR51,P1_RXN[3],CD25,RSVD,AY40,USB_0_HSD0P,CY17,VDDIO_MEM_S3_AB,BC45,VSS,T4,VSS,BN21,VSS,CV45 | ||

| + | MB_ALERT_L,AT50,P1_RXN[4],CE23,RSVD,AY41,USB_0_HSD1N,CV17,VDDIO_MEM_S3_AB,BC48,VSS,T6,VSS,BN35,VSS,CV47 | ||

| + | MB_BANK[0],BJ49,P1_RXN[5],CF23,RSVD,AY43,USB_0_HSD1P,CW16,VDDIO_MEM_S3_AB,BC50,VSS,T8,VSS,BN37,VSS,CV49 | ||

| + | MB_BANK[1],BH50,P1_RXN[6],CD22,RSVD,AY44,USB_0_HSD2N,DB10,VDDIO_MEM_S3_AB,BC52,VSS,T12,VSS,BN38,VSS,CV52 | ||

| + | MB_BG[0],AR51,P1_RXN[7],CE20,RSVD,AY46,USB_0_HSD2P,DA10,VDDIO_MEM_S3_AB,BC55,VSS,T47,VSS,BN40,VSS,CV54 | ||

| + | MB_BG[1],AR49,P1_RXN[8],CF20,RSVD,AY48,USB_0_HSD3N,DB9,VDDIO_MEM_S3_AB,BD38,VSS,T49,VSS,BN43,VSS,CW2 | ||

| + | MB_CAS_L_ADD[15],BM51,P1_RXN[9],CD19,RSVD,BA8,USB_0_HSD3P,DA8,VDDIO_MEM_S3_AB,BD39,VSS,T52,VSS,BP4,VSS,CW4 | ||

| + | MB_CHECK[0],AF50,P1_RXN[10],CE17,RSVD,BA12,USB_0_OC0_L/AGPIO16_0,CY15,VDDIO_MEM_S3_AB,BD42,VSS,T54,VSS,BP6,VSS,CW7 | ||

| + | MB_CHECK[1],AF51,P1_RXN[11],CF17,RSVD,BA15,USB_0_OC1_L/AGPIO17_0,CY14,VDDIO_MEM_S3_AB,BD45,VSS,U2,VSS,BP8,VSS,CW9 | ||

| + | MB_CHECK[2],AK50,P1_RXN[12],CD16,RSVD,BA16,USB_0_OC2_L/AGPIO18_0,BB46,VDDIO_MEM_S3_AB,BD47,VSS,U4,VSS,BP11,VSS,CW11 | ||

| + | MB_CHECK[3],AK51,P1_RXN[13],CE14,RSVD,BA39,USB_0_OC3_L/AGPIO24_0,BB43,VDDIO_MEM_S3_AB,BD49,VSS,U7,VSS,BP13,VSS,CW14 | ||

| + | MB_CHECK[4],AE49,P1_RXN[14],CF14,RSVD,BA41,USB_0_SS_0RXN,DB15,VDDIO_MEM_S3_AB,BD52,VSS,U9,VSS,BP16,VSS,CW17 | ||

| + | MB_CHECK[5],AE51,P1_RXN[15],CD13,RSVD,BA42,USB_0_SS_0RXP,DA15,VDDIO_MEM_S3_AB,BD54,VSS,U11,VSS,BP18,VSS,CW20 | ||

| + | MB_CHECK[6],AJ49,P1_RXP[0],CE27,RSVD,BA44,USB_0_SS_0TXN,CV14,VDDIO_MEM_S3_AB,BE40,VSS,U13,VSS,BP20,VSS,CW23 | ||

| + | MB_CHECK[7],AJ51,P1_RXP[1],CD26,RSVD,BA46,USB_0_SS_0TXP,CW13,VDDIO_MEM_S3_AB,BE43,VSS,U16,VSS,BP22,VSS,CW26 | ||

| + | MB_C[0],BU49,P1_RXP[2],CF25,RSVD,BA47,USB_0_SS_1RXN,DB14,VDDIO_MEM_S3_AB,BE45,VSS,U19,VSS,BP36,VSS,CW29 | ||

| + | MB_C[1],BU51,P1_RXP[3],CE24,RSVD,BB9,USB_0_SS_1RXP,DA13,VDDIO_MEM_S3_AB,BE48,VSS,U22,VSS,BP38,VSS,CW32 | ||

| + | MB_C[2],BR49,P1_RXP[4],CD23,RSVD,BB10,USB_0_SS_1TXN,CW12,VDDIO_MEM_S3_AB,BE50,VSS,U25,VSS,BP39,VSS,CW35 | ||

| + | MB_DATA[0],A50,P1_RXP[5],CF22,RSVD,BB12,USB_0_SS_1TXP,CV12,VDDIO_MEM_S3_AB,BE52,VSS,U28,VSS,BP42,VSS,CW38 | ||

| + | MB_DATA[1],B51,P1_RXP[6],CE21,RSVD,BB14,USB_0_SS_2RXN,CN10,VDDIO_MEM_S3_AB,BF38,VSS,U31,VSS,BP45,VSS,CW41 | ||

| + | MB_DATA[2],F50,P1_RXP[7],CD20,RSVD,BB15,USB_0_SS_2RXP,CP10,VDDIO_MEM_S3_AB,BF39,VSS,U34,VSS,BR2,VSS,CW44 | ||

| + | MB_DATA[3],F51,P1_RXP[8],CF19,RSVD,BB17,USB_0_SS_2TXN,CY10,VDDIO_MEM_S3_AB,BF42,VSS,U37,VSS,BR4,VSS,CW45 | ||

| + | MB_DATA[4],A49,P1_RXP[9],CE18,RSVD,BB40,USB_0_SS_2TXP,CW10,VDDIO_MEM_S3_AB,BF45,VSS,U40,VSS,BR7,VSS,CW48 | ||

| + | MB_DATA[5],B50,P1_RXP[10],CD17,RSVD,BB41,USB_0_SS_3RXN,CN8,VDDIO_MEM_S3_AB,BF47,VSS,U43,VSS,BR9,VSS,CW50 | ||

| + | MB_DATA[6],E49,P1_RXP[11],CF16,RSVD,BB44,USB_0_SS_3RXP,CP9,VDDIO_MEM_S3_AB,BF49,VSS,U45,VSS,BR11,VSS,CW52 | ||

| + | MB_DATA[7],E51,P1_RXP[12],CE15,RSVD,BB48,USB_0_SS_3TXN,CY9,VDDIO_MEM_S3_AB,BF52,VSS,U48,VSS,BR14,VSS,CW55 | ||

| + | MB_DATA[8],H50,P1_RXP[13],CD14,RSVD,BC8,USB_0_SS_3TXP,CW8,VDDIO_MEM_S3_AB,BF54,VSS,U50,VSS,BR17,VSS,CY1 | ||

| + | MB_DATA[9],H51,P1_RXP[14],CF13,RSVD,BC10,USB_1_0_ZVSS,D16,VDDIO_MEM_S3_AB,BG40,VSS,U52,VSS,BR18,VSS,CY4 | ||

| + | MB_DATA[10],M50,P1_RXP[15],CE12,RSVD,BC12,USB_1_1_ZVSS,E16,VDDIO_MEM_S3_AB,BG43,VSS,U55,VSS,BR19,VSS,CY6 | ||

| + | MB_DATA[11],M51,P1_TXN[0],CL27,RSVD,BC13,USB_1_2_ZVSS,K28,VDDIO_MEM_S3_AB,BG45,VSS,V1,VSS,BR21,VSS,CY8 | ||

| + | MB_DATA[12],G49,P1_TXN[1],CN26,RSVD,BC15,USB_1_3_ZVSS,P29,VDDIO_MEM_S3_AB,BG48,VSS,V4,VSS,BR35,VSS,CY31 | ||

| + | MB_DATA[13],G51,P1_TXN[2],CM26,RSVD,BC16,USB_1_HSD0N,C17,VDDIO_MEM_S3_AB,BG50,VSS,V6,VSS,BR37,VSS,CY34 | ||

| + | MB_DATA[14],L49,P1_TXN[3],CL24,RSVD,BC39,USB_1_HSD0P,C16,VDDIO_MEM_S3_AB,BG52,VSS,V8,VSS,BR38,VSS,CY37 | ||

| + | MB_DATA[15],L51,P1_TXN[4],CN23,RSVD,BC41,USB_1_HSD1N,B18,VDDIO_MEM_S3_AB,BG55,VSS,V12,VSS,BR40,VSS,CY40 | ||

| + | MB_DATA[16],P50,P1_TXN[5],CM23,RSVD,BC42,USB_1_HSD1P,A17,VDDIO_MEM_S3_AB,BH38,VSS,V47,VSS,BR43,VSS,CY43 | ||

| + | MB_DATA[17],P51,P1_TXN[6],CL21,RSVD,BC44,USB_1_HSD2N,A10,VDDIO_MEM_S3_AB,BH39,VSS,V49,VSS,BT1,VSS,CY45 | ||

| + | MB_DATA[18],V50,P1_TXN[7],CN20,RSVD,BC46,USB_1_HSD2P,B10,VDDIO_MEM_S3_AB,BH42,VSS,V52,VSS,BT4,VSS,CY47 | ||

| + | MB_DATA[19],V51,P1_TXN[8],CM20,RSVD,BC47,USB_1_HSD3N,A9,VDDIO_MEM_S3_AB,BH45,VSS,V54,VSS,BT6,VSS,CY49 | ||

| + | MB_DATA[20],N49,P1_TXN[9],CL18,RSVD,BD9,USB_1_HSD3P,B9,VDDIO_MEM_S3_AB,BH47,VSS,W2,VSS,BT8,VSS,CY52 | ||

| + | MB_DATA[21],N51,P1_TXN[10],CN17,RSVD,BD10,USB_1_OC0_L/EGPIO16_1,C13,VDDIO_MEM_S3_AB,BH49,VSS,W4,VSS,BT11,VSS,CY54 | ||

| + | MB_DATA[22],U49,P1_TXN[11],CM17,RSVD,BD16,USB_1_OC1_L/EGPIO17_1,C14,VDDIO_MEM_S3_AB,BH52,VSS,W7,VSS,BT13,VSS,DA4 | ||

| + | MB_DATA[23],U51,P1_TXN[12],CL15,RSVD,BD17,USB_1_OC2_L/EGPIO18_1,BA10,VDDIO_MEM_S3_AB,BH54,VSS,W9,VSS,BT16,VSS,DA7 | ||

| + | MB_DATA[24],Y50,P1_TXN[13],CN14,RSVD,BD40,USB_1_OC3_L/EGPIO24_1,BA13,VDDIO_MEM_S3_AB,BJ40,VSS,W11,VSS,BT18,VSS,DA9 | ||

| + | MB_DATA[25],Y51,P1_TXN[14],CM14,RSVD,BD41,USB_1_SS_0RXN,E13,VDDIO_MEM_S3_AB,BJ43,VSS,W13,VSS,BT20,VSS,DA11 | ||

| + | MB_DATA[26],AD50,P1_TXN[15],CL12,RSVD,BD43,USB_1_SS_0RXP,D13,VDDIO_MEM_S3_AB,BJ45,VSS,W16,VSS,BT22,VSS,DA12 | ||

| + | MB_DATA[27],AD51,P1_TXP[0],CM28,RSVD,BD44,USB_1_SS_0TXN,A13,VDDIO_MEM_S3_AB,BJ48,VSS,W19,VSS,BT36,VSS,DA14 | ||

| + | MB_DATA[28],W49,P1_TXP[1],CN27,RSVD,BD46,USB_1_SS_0TXP,B13,VDDIO_MEM_S3_AB,BJ50,VSS,W22,VSS,BT38,VSS,DA17 | ||

| + | MB_DATA[29],W51,P1_TXP[2],CL26,RSVD,BD48,USB_1_SS_1RXN,D15,VDDIO_MEM_S3_AB,BJ52,VSS,W25,VSS,BT39,VSS,DA20 | ||

| + | MB_DATA[30],AC49,P1_TXP[3],CM25,RSVD,BE8,USB_1_SS_1RXP,E14,VDDIO_MEM_S3_AB,BK47,VSS,W28,VSS,BT42,VSS,DA23 | ||

| + | MB_DATA[31],AC51,P1_TXP[4],CN24,RSVD,BE10,USB_1_SS_1TXN,B15,VDDIO_MEM_S3_AB,BK49,VSS,W31,VSS,BT45,VSS,DA26 | ||

| + | MB_DATA[32],BY51,P1_TXP[5],CL23,RSVD,BE12,USB_1_SS_1TXP,A14,VDDIO_MEM_S3_AB,BK52,VSS,W34,VSS,BU2,VSS,DA29 | ||

| + | MB_DATA[33],BY50,P1_TXP[6],CM22,RSVD,BE13,USB_1_SS_2RXN,K9,VDDIO_MEM_S3_AB,BK54,VSS,W37,VSS,BU4,VSS,DA32 | ||

| + | MB_DATA[34],CD51,P1_TXP[7],CN21,RSVD,BE15,USB_1_SS_2RXP,J8,VDDIO_MEM_S3_AB,BL45,VSS,W40,VSS,BU7,VSS,DA35 | ||

| + | MB_DATA[35],CD50,P1_TXP[8],CL20,RSVD,BE17,USB_1_SS_2TXN,C8,VDDIO_MEM_S3_AB,BL48,VSS,W43,VSS,BU9,VSS,DA38 | ||

| + | MB_DATA[36],BW51,P1_TXP[9],CM19,RSVD,BE39,USB_1_SS_2TXP,D9,VDDIO_MEM_S3_AB,BL50,VSS,W45,VSS,BU11,VSS,DA41 | ||

| + | MB_DATA[37],BW49,P1_TXP[10],CN18,RSVD,BE41,USB_1_SS_3RXN,K10,VDDIO_MEM_S3_AB,BL52,VSS,W48,VSS,BU14,VSS,DA44 | ||

| + | MB_DATA[38],CC51,P1_TXP[11],CL17,RSVD,BE42,USB_1_SS_3RXP,J10,VDDIO_MEM_S3_AB,BL55,VSS,W50,VSS,BU17,VSS,DA45 | ||

| + | MB_DATA[39],CC49,P1_TXP[12],CM16,RSVD,BE44,USB_1_SS_3TXN,C10,VDDIO_MEM_S3_AB,BM47,VSS,W52,VSS,BU18,VSS,DA48 | ||

| + | MB_DATA[40],CF51,P1_TXP[13],CN15,RSVD,BE46,USB_1_SS_3TXP,D10,VDDIO_MEM_S3_AB,BM49,VSS,W55,VSS,BU19,VSS,DA51 | ||

| + | MB_DATA[41],CF50,P1_TXP[14],CL14,RSVD,BE47,VDDBT_RTC_G,CB34,VDDIO_MEM_S3_AB,BM52,VSS,Y1,VSS,BU21,VSS,DA52 | ||

| + | MB_DATA[42],CK51,P1_TXP[15],CM13,RSVD,BF9,VDDCR_CPU,B11,VDDIO_MEM_S3_AB,BM54,VSS,Y4,VSS,BU35,VSS,DB5 | ||

| + | MB_DATA[43],CK50,PCIE_RST0_L/EGPIO26_0,DB27,RSVD,BF10,VDDCR_CPU,B14,VDDIO_MEM_S3_AB,BN45,VSS,Y6,VSS,BU37,VSS,DB8 | ||

| + | MB_DATA[44],CE51,PCIE_RST1_L/EGPIO26_1,B28,RSVD,BF12,VDDCR_CPU,B17,VDDIO_MEM_S3_AB,BN48,VSS,Y8,VSS,BU38,VSS,DB11 | ||

| + | MB_DATA[45],CE49,PROCHOT_L,B22,RSVD,BF14,VDDCR_CPU,B20,VDDIO_MEM_S3_AB,BN50,VSS,Y11,VSS,BU40,VSS,DB13 | ||

| + | MB_DATA[46],CJ51,PWRGD_OUT,B30,RSVD,BF16,VDDCR_CPU,B23,VDDIO_MEM_S3_AB,BN52,VSS,Y12,VSS,BU43,VSS,DB16 | ||

| + | MB_DATA[47],CJ49,PWROK,D12,RSVD,BF17,VDDCR_CPU,B26,VDDIO_MEM_S3_AB,BP47,VSS,Y16,VSS,BV4,VSS,DB19 | ||

| + | MB_DATA[48],CM51,PWR_BTN_L/AGPIO0,A29,RSVD,BF40,VDDCR_CPU,B29,VDDIO_MEM_S3_AB,BP49,VSS,Y18,VSS,BV6,VSS,DB22 | ||

| + | MB_DATA[49],CM50,PWR_GOOD,DB33,RSVD,BF41,VDDCR_CPU,B32,VDDIO_MEM_S3_AB,BP52,VSS,Y20,VSS,BV8,VSS,DB25 | ||

| + | MB_DATA[50],CT51,RESET_L,B12,RSVD,BF43,VDDCR_CPU,B35,VDDIO_MEM_S3_AB,BP54,VSS,Y22,VSS,BV11,VSS,DB28 | ||

| + | MB_DATA[51],CT50,RSMRST_L,B39,RSVD,BF44,VDDCR_CPU,B38,VDDIO_MEM_S3_AB,BR45,VSS,Y24,VSS,BV13,VSS,DB31 | ||

| + | MB_DATA[52],CL51,RSVD,A16,RSVD,BF46,VDDCR_CPU,B41,VDDIO_MEM_S3_AB,BR48,VSS,Y26,VSS,BV16,VSS,DB34 | ||

| + | MB_DATA[53],CL49,RSVD,A23,RSVD,BF48,VDDCR_CPU,B43,VDDIO_MEM_S3_AB,BR50,VSS,Y28,VSS,BV18,VSS,DB37 | ||

| + | MB_DATA[54],CR51,RSVD,A32,RSVD,BG8,VDDCR_CPU,B45,VDDIO_MEM_S3_AB,BR52,VSS,Y30,VSS,BV20,VSS,DB40 | ||

| + | MB_DATA[55],CR49,RSVD,A40,RSVD,BG10,VDDCR_CPU,D11,VDDIO_MEM_S3_AB,BR55,VSS,Y32,VSS,BV22,VSS,DB43 | ||

| + | MB_DATA[56],CV51,RSVD,B33,RSVD,BG12,VDDCR_CPU,D14,VDDIO_MEM_S3_AB,BT47,VSS,Y34,VSS,BV36,VSS,DB45 | ||

| + | MB_DATA[57],CV50,RSVD,B40,RSVD,BG13,VDDCR_CPU,D17,VDDIO_MEM_S3_AB,BT49,VSS,Y36,VSS,BV38,VSS,DB48 | ||

| + | MB_DATA[58],DA49,RSVD,B46,RSVD,BG15,VDDCR_CPU,D20,VDDIO_MEM_S3_AB,BT52,VSS,Y38,VSS,BV39,VSS,DB51 | ||

| + | MB_DATA[59],DB49,RSVD,B48,RSVD,BG39,VDDCR_CPU,D23,VDDIO_MEM_S3_AB,BT54,VSS,Y39,VSS,BV42,VSS_SENSE_A,Y14 | ||

| + | MB_DATA[60],CU51,RSVD,C19,RSVD,BG41,VDDCR_CPU,D26,VDDIO_MEM_S3_AB,BU45,VSS,Y40,VSS,BV45,VSS_SENSE_B,CB32 | ||

| + | MB_DATA[61],CU49,RSVD,C22,RSVD,BG42,VDDCR_CPU,D29,VDDIO_MEM_S3_AB,BU48,VSS,Y41,VSS,BV46,WAFL0_ZVSS,CY21 | ||

| + | MB_DATA[62],DA50,RSVD,C23,RSVD,BG44,VDDCR_CPU,D32,VDDIO_MEM_S3_AB,BU50,VSS,Y42,VSS,BV47,WAFL1_ZVSS,C28 | ||

| + | MB_DATA[63],DB50,RSVD,C46,RSVD,BG46,VDDCR_CPU,D35,VDDIO_MEM_S3_AB,BU52,VSS,Y43,VSS,BV48,WAFL_RXN[0],B34 | ||

| + | MB_DQS_H[0],D51,RSVD,C47,RSVD,BG47,VDDCR_CPU,D38,VDDIO_MEM_S3_AB_FB_H,AP38,VSS,Y44,VSS,BV49,WAFL_RXN[1],C34 | ||

| + | MB_DQS_H[1],K51,RSVD,D24,RSVD,BH9,VDDCR_CPU,D41,VDDIO_MEM_S3_AB_FB_L,AN38,VSS,Y45,VSS,BV50,WAFL_RXP[0],A34 | ||

| + | MB_DQS_H[2],T51,RSVD,D25,RSVD,BH10,VDDCR_CPU,D43,VDDIO_MEM_S3_CD,AF4,VSS,Y47,VSS,BV51,WAFL_RXP[1],C35 | ||

| + | MB_DQS_H[3],AB51,RSVD,D30,RSVD,BH12,VDDCR_CPU,D45,VDDIO_MEM_S3_CD,AF6,VSS,Y49,VSS,BV52,WAFL_TXN[0],C32 | ||

| + | MB_DQS_H[4],CB50,RSVD,D31,RSVD,BH14,VDDCR_CPU,F11,VDDIO_MEM_S3_CD,AF8,VSS,Y52,VSS,BV53,WAFL_TXN[1],A31 | ||

| + | MB_DQS_H[5],CH50,RSVD,D34,RSVD,BH40,VDDCR_CPU,F14,VDDIO_MEM_S3_CD,AF11,VSS,Y54,VSS,BV54,WAFL_TXP[0],C31 | ||

| + | MB_DQS_H[6],CP50,RSVD,D36,RSVD,BH41,VDDCR_CPU,F17,VDDIO_MEM_S3_CD,AG2,VSS,AA2,VSS,BV55,WAFL_TXP[1],B31 | ||

| + | MB_DQS_H[7],CY50,RSVD,D37,RSVD,BH43,VDDCR_CPU,F20,VDDIO_MEM_S3_CD,AG4,VSS,AA4,VSS,BW2,WAKE_L/AGPIO2,B36 | ||

| + | MB_DQS_H[8],AH51,RSVD,D39,RSVD,BH44,VDDCR_CPU,F23,VDDIO_MEM_S3_CD,AG7,VSS,AA7,VSS,BW4,X32K_X1,DA25 | ||

| + | MB_DQS_H[9],C49,RSVD,D40,RSVD,BH46,VDDCR_CPU,F26,VDDIO_MEM_S3_CD,AG9,VSS,AA9,VSS,BW7,X32K_X2,DB26 | ||

| + | MB_DQS_H[10],J49,RSVD,D46,RSVD,BH48,VDDCR_CPU,F29,VDDIO_MEM_S3_CD,AH1,VSS,AA11,VSS,BW9,X48M_X1,DA22 | ||

| + | MB_DQS_H[11],R49,RSVD,D48,RSVD,BJ8,VDDCR_CPU,F32,VDDIO_MEM_S3_CD,AH4,VSS,AA14,VSS,BW11,X48M_X2,DB23 | ||

| + | MB_DQS_H[12],AA49,RSVD,E8,RSVD,BJ12,VDDCR_CPU,F35,VDDIO_MEM_S3_CD,AH6,VSS,AA17,VSS,BW14,X156M_H[0],CW22 | ||

| + | MB_DQS_H[13],CA51,RSVD,E10,RSVD,BJ13,VDDCR_CPU,F38,VDDIO_MEM_S3_CD,AH8,VSS,AA19,VSS,BW17,X156M_H[1],D19 | ||

| + | MB_DQS_H[14],CG51,RSVD,E20,RSVD,BJ39,VDDCR_CPU,F40,VDDIO_MEM_S3_CD,AH11,VSS,AA21,VSS,BW18,X156M_L[0],CV23 | ||

| + | MB_DQS_H[15],CN51,RSVD,E23,RSVD,BJ41,VDDCR_CPU,F43,VDDIO_MEM_S3_CD,AJ2,VSS,AA23,VSS,BW19,X156M_L[1],E19 | ||

| + | MB_DQS_H[16],CW51,RSVD,E25,RSVD,BJ42,VDDCR_CPU,F45,VDDIO_MEM_S3_CD,AJ4,VSS,AA25,VSS,BW21,XTRIG_L[4],B21 | ||

| + | MB_DQS_H[17],AG49,RSVD,E29,RSVD,BJ44,VDDCR_CPU,H11,VDDIO_MEM_S3_CD,AJ7,VSS,AA27,VSS,BW35,XTRIG_L[5],A20 | ||

| + | MB_DQS_L[0],C51,RSVD,E31,RSVD,BJ46,VDDCR_CPU,H15,VDDIO_MEM_S3_CD,AJ9,VSS,AA29,VSS,BW37,XTRIG_L[6],A19 | ||

| + | MB_DQS_L[1],J51,RSVD,E32,RSVD,BJ47,VDDCR_CPU,H18,VDDIO_MEM_S3_CD,AK4,VSS,AA31,VSS,BW38,XTRIG_L[7],B19 | ||

| + | MB_DQS_L[2],R51,RSVD,E34,RSVD,BK12,VDDCR_CPU,H21,VDDIO_MEM_S3_CD,AK6,VSS,AA33,VSS,BW40 | ||

| + | MB_DQS_L[3],AA51,RSVD,E35,RSVD,BK14,VDDCR_CPU,H24,VDDIO_MEM_S3_CD,AK8,VSS,AA35,VSS,BW43 | ||

| + | --> | ||

| + | |||

| + | === Pin Description === | ||

| + | {| class="wikitable sortable" | ||

| + | !Signal!!Type!!Description | ||

| + | |- | ||

| + | |MA-MD_ACT_L||O-IOMEM-S||DRAM Channel A-D Activation Command | ||

| + | |- | ||

| + | |MA-MD_ADD[13:0]||O-IOMEM-S||DRAM Column/Row Address | ||

| + | |- | ||

| + | |MA-MD_ADD_17||O-IOMEM-S||DRAM Column/Row Address 17 | ||

| + | |- | ||

| + | |MA-MD_ALERT_L||I-IOMEM-S||DRAM Alert (CRC error and Command/Address parity error) | ||

| + | |- | ||

| + | |MA-MD_BANK[1:0]||O-IOMEM-S||DRAM Bank Address | ||

| + | |- | ||

| + | |MA-MD_BG[1:0]||O-IOMEM-S||DRAM Bank Group | ||

| + | |- | ||

| + | |MA-MD_CAS_L_ADD[15]||O-IOMEM-S||DRAM Column Address Strobe or Column/Row Address 15 | ||

| + | |- | ||

| + | |MA-MD_CHECK[7:0]||B-IOMEM-S||DRAM ECC Check Bits | ||

| + | |- | ||

| + | |MA-MD_C[2:0]||O-IOMEM-S||DRAM Chip ID Signals | ||

| + | |- | ||

| + | |MA-MD_DATA[63:0]||B-IOMEM-S||DRAM Data Bus | ||

| + | |- | ||

| + | |MA-MD_DQS_H/L[8:0]||B-IOMEM-S||DRAM Differential Data Strobe | ||

| + | |- | ||

| + | |MA-MD_DQS_H[17:9]||B-IOMEM-S||DRAM Differential Data Strobe for RDIMMs, DM[8:0] Data Mask output for UDIMMs; <br>RDIMMs not supported on Socket TR4 | ||

| + | |- | ||

| + | |MA-MD_DQS_L[17:9]||B-IOMEM-S||DRAM Differential Data Strobe for RDIMMs, not connected for UDIMMs | ||

| + | |- | ||

| + | |MA-MD_EVENT_L||I-IOMEM-S||DRAM Thermal Event | ||

| + | |- | ||

| + | |MA-MD_PAROUT||O-IOMEM-S||DRAM Command and Address Parity | ||

| + | |- | ||

| + | |MA-MD_RAS_L_ADD[16]||O-IOMEM-S||DRAM Row Address Strobe or Column/Row Address 16 | ||

| + | |- | ||

| + | |MA-MD_RESET_L||O-IOMEM-S||DRAM Reset | ||

| + | |- | ||

| + | |MA-MD_WE_L_ADD[14]||O-IOMEM-S||DRAM Write Enable or Column/Row Address 14 | ||

| + | |- | ||

| + | |MA-MD_ZVSS||A||DRAM Interface Drive-Strength Auto-Compensation Resistor to VSS | ||

| + | |- | ||

| + | |MA0-MD0_CKE[1:0]<br/>MA1-MD1_CKE[1:0]||O-IOMEM-S||DRAM Channel A-D DIMM 0-1 Clock Enable | ||

| + | |- | ||

| + | |MA0-MD0_CLK_H/L[1:0]<br/>MA1-MD1_CLK_H/L[1:0]||O-IOMEM-D||DRAM Channel A-D DIMM 0-1 Differential Clock | ||

| + | |- | ||

| + | |MA0-MD0_CS_L[1:0]<br/>MA1-MD1_CS_L[1:0]||O-IOMEM-S||DRAM Channel A-D DIMM 0-1 Chip Select | ||

| + | |- | ||

| + | |MA0-MD0_ODT[1:0]<br/>MA1-MD1_ODT[1:0]||O-IOMEM-S||DRAM Channel A-D DIMM 0-1 Enable Pin for On Die Termination | ||

| + | |- | ||

| + | |FORCE_SELFREFRESH||I-IO33-S||NVDIMM Force Self-Refresh; NVDIMMs not supported on Socket TR4 | ||

| + | |- | ||

| + | |NV_SAVE_L||O-IO18-S||NVDIMM SAVE Signal | ||

| + | |- | ||