(Corrected spelling mistake: changed "own" to "down") |

|||

| (16 intermediate revisions by 4 users not shown) | |||

| Line 1: | Line 1: | ||

{{intel title|Bonnell|arch}} | {{intel title|Bonnell|arch}} | ||

{{microarchitecture | {{microarchitecture | ||

| − | | atype | + | |atype=CPU |

| − | | name | + | |name=Bonnell |

| − | | designer | + | |designer=Intel |

| − | | manufacturer | + | |manufacturer=Intel |

| − | | introduction | + | |introduction=March 2, 2008 |

| − | | phase-out | + | |phase-out=2011 |

| − | | process | + | |process=45 nm |

| − | | cores | + | |cores=1 |

| − | | cores 2 | + | |cores 2=2 |

| − | + | |type=Superscalar | |

| − | + | |oooe=No | |

| − | | type | + | |speculative=Yes |

| − | | | + | |renaming=No |

| − | | speculative | + | |stages min=16 |

| − | | renaming | + | |stages max=19 |

| − | + | |isa=x86-64 | |

| − | + | |extension=MOVBE | |

| − | | stages min | + | |extension 2=MMX |

| − | | stages max | + | |extension 3=SSE |

| − | | | + | |extension 4=SSE2 |

| − | + | |extension 5=SSE3 | |

| − | + | |extension 6=SSSE3 | |

| − | + | |l1i=32 KiB | |

| − | | extension | + | |l1i per=Core |

| − | | extension 2 | + | |l1i desc=8-way set associative |

| − | | extension 3 | + | |l1d=24 KiB |

| − | | extension 4 | + | |l1d per=Core |

| − | | extension 5 | + | |l1d desc=6-way set associative |

| − | | extension 6 | + | |l2=512 KiB |

| − | + | |l2 per=Core | |

| − | + | |l2 desc=8-way set associative | |

| − | | l1i | + | |core name=Silverthorne |

| − | | l1i per | + | |core name 2=Diamondville |

| − | | l1i desc | + | |core name 3=Lincroft |

| − | | l1d | + | |core name 4=Pineview |

| − | | l1d per | + | |core name 5=Tunnel Creek |

| − | | l1d desc | + | |core name 6=Stellarton |

| − | | l2 | + | |core name 7=Sodaville |

| − | | l2 per | + | |core name 8=Groveland |

| − | | l2 desc | + | |successor=Saltwell |

| − | + | |successor link=intel/microarchitectures/saltwell | |

| − | + | |pipeline=Yes | |

| − | | core name | + | |OoOE=No |

| − | | core name 2 | + | |issues=2 |

| − | | core name 3 | + | |inst=Yes |

| − | | core name 4 | + | |cache=Yes |

| − | | core name 5 | + | |core names=Yes |

| − | | core name 6 | + | |succession=Yes |

| − | | core name 7 | ||

| − | | core name 8 | ||

| − | |||

| − | |||

| − | |||

| − | | successor | ||

| − | | successor link | ||

}} | }} | ||

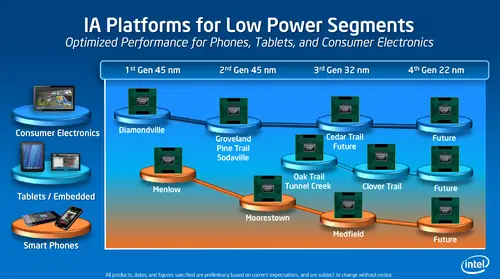

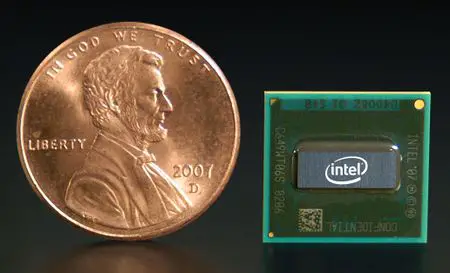

'''Bonnell''' was a [[microarchitecture]] for [[Intel]]'s [[45 nm]] ultra-low voltage [[microprocessor]]s first introduced in 2008 for their then-new {{intel|Atom}} family. Bonnell, which was named after the highest point in [[wikipedia:Austin, Texas|Austin]] - [[wikipedia:Mount Bonnell|Mount Bonnell]], was Intel's first x86-compatible [[microarchitecture]] designed to target the ultra-low power market. | '''Bonnell''' was a [[microarchitecture]] for [[Intel]]'s [[45 nm]] ultra-low voltage [[microprocessor]]s first introduced in 2008 for their then-new {{intel|Atom}} family. Bonnell, which was named after the highest point in [[wikipedia:Austin, Texas|Austin]] - [[wikipedia:Mount Bonnell|Mount Bonnell]], was Intel's first x86-compatible [[microarchitecture]] designed to target the ultra-low power market. | ||

| Line 109: | Line 102: | ||

== Brands == | == Brands == | ||

| − | Intel sold | + | Intel sold Bonnell-based processors under the '''{{intel|Atom}}''' brand. Additionally, manufacturers were allowed to use the '''Centrino Atom''' brand if the system consist of a Bonnell-based processor, the chipset, wireless capabilities ([[WiFi]], [[3G]], [[WiMAX]]), is battery powered, and had a screen size of up to 6". |

{| class="wikitable" | {| class="wikitable" | ||

| Line 156: | Line 149: | ||

|} | |} | ||

{{clear}} | {{clear}} | ||

| + | |||

| + | == Compatibility == | ||

| + | |||

| + | {| class="wikitable" | ||

| + | ! Vendor !! OS !! Version !! Notes | ||

| + | |- | ||

| + | | rowspan="4" | [[Microsoft]] || rowspan="4" | Windows || style="background-color: #d6ffd8;" | Windows XP Embedded SP2 || Support | ||

| + | |- | ||

| + | | style="background-color: #d6ffd8;" | Windows Embedded CE 6.0 || Support | ||

| + | |- | ||

| + | | style="background-color: #d6ffd8;" | Windows 7 || Support | ||

| + | |- | ||

| + | | style="background-color: #d6ffd8;" | Windows Embedded Standard 7 || Support | ||

| + | |- | ||

| + | | rowspan="2" | Linux || rowspan="2" | Linux || style="background-color: #d6ffd8;" | Kernel 2.4/2.6? || Initial Support | ||

| + | |- | ||

| + | | style="background-color: #d6ffd8;" | MeeGo 1 || Support | ||

| + | |} | ||

== Compiler support == | == Compiler support == | ||

| Line 260: | Line 271: | ||

=== Overview === | === Overview === | ||

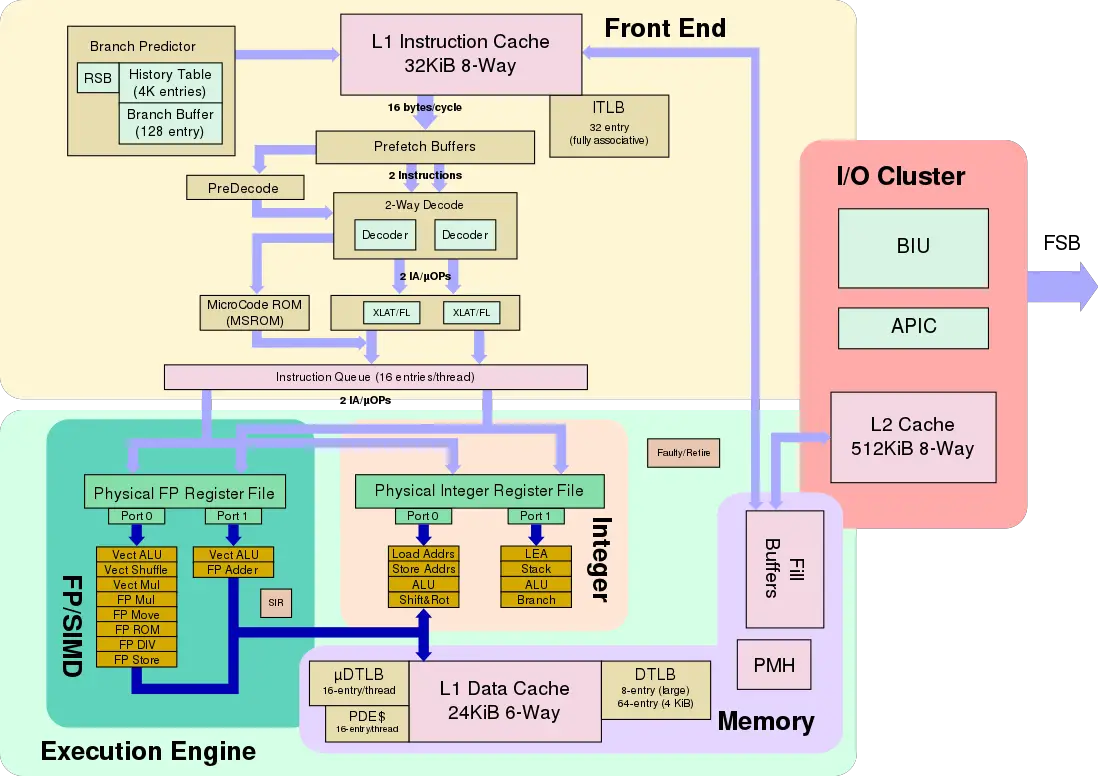

| − | Bonnell's architecture shares very little in common with other Intel designs. To achieve the strict ultra-low power objects, Bonnell features a very slimmed | + | Bonnell's architecture shares very little in common with other Intel designs. To achieve the strict ultra-low power objects, Bonnell features a very slimmed down design discarding many high-performance techniques used by Intel's high-performance architectures such as aggressive [[speculative execution]], [[out-of-order]] execution, and µop transformation. |

| + | |||

| + | Part of the design requirement was that Bonnell retain full [[x86]] compatibility, up to the latest extension - at one tenth of the power consumption of the {{\\|Pentium M}}. This meant any software is now 100% compatible but it forced engineers to deal with all the baggage the architecture brought along. The decision to offer full compatibility brought its own set of benefits such as access to the largest software code base in the world, including the ability to run any other [[x86]] operating system unmodified. At the same time it forced the design team to resort to other means of reducing power. | ||

| − | + | Up to Bonnell, all of Intel's existing architectures put very low priority on power efficiency (note that this has significantly changed since the introduction of {{\\|Sandy Bridge}}). High-performance, high-throughput, complex designs are simply inadequate for the kind of power goals required out of Bonnell, even if they were trimmed down. It was decided that Bonnell would be designed from the scratch with power goals in mind. For those reasons Bonnell resembles the {{\\|P5}} microarchitecture. | |

| − | |||

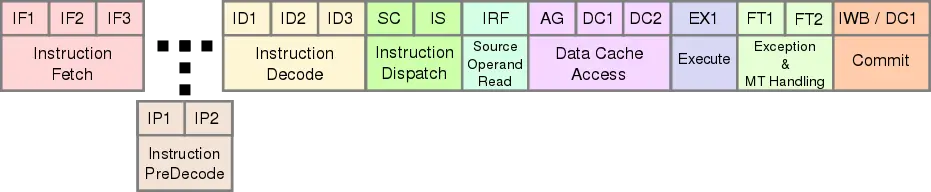

=== Pipeline === | === Pipeline === | ||

Much like the original {{\\|P5}} microarchitecture, Bonnell consists of an [[in-order]] [[dual-issue]] pipeline. The pipeline is shown below. Note the pipeline is duplicated for dual-issue execution. | Much like the original {{\\|P5}} microarchitecture, Bonnell consists of an [[in-order]] [[dual-issue]] pipeline. The pipeline is shown below. Note the pipeline is duplicated for dual-issue execution. | ||

| Line 272: | Line 284: | ||

| − | Unlike {{\\|P5}}, which only had 5 stages, Bonnell has 16 to 19 stages | + | Unlike {{\\|P5}}, which only had 5 stages, Bonnell has 16 to 19 pipeline stages. The longer pipeline allows a more even spreading of heat across the chip with more units. This also allows a higher clock rate. |

==== Front End ==== | ==== Front End ==== | ||

| − | Bonnell's front end is very simple when compared to Intel's high-performance architectures. [[Out-of-order execution]] (OoOE) that is found ubiquitously in all HPC architectures was rejected. Bonnell's power and area constraints simply couldn't allow for the complex logic needed to support that capability. The [[Instruction Fetch]] consists of 3 stages capable going through up to 16 bytes per cycle. Like fetch, the [[Instruction Decode]] is also 3 stages capable of decording instructions with up to 3 prefixes each cycle (considerably longer for more complex instructions). | + | Bonnell's front end is very simple when compared to Intel's high-performance architectures. [[Out-of-order execution]] (OoOE) that is found ubiquitously in all HPC architectures was rejected. Bonnell's power and area constraints simply couldn't allow for the complex logic needed to support that capability. The [[Instruction Fetch]] consists of 3 stages, capable of going through up to 16 bytes per cycle. Like fetch, the [[Instruction Decode]] is also 3 stages, capable of decording instructions with up to 3 prefixes each cycle (considerably longer for more complex instructions). |

Bonnell is a departure from all modern x86 architectures with respect to decoding (including those developed by [[AMD]] and [[VIA]] and every Intel architecture since {{\\|P6}}). Whereas modern architectures transform complex [[x86]] instructions into a more easily digestible µop form, Bonnell does almost no such transformations. The pipeline is tailored to execute regular x86 instructions as single atomic operations consisting of a single destination register and up to three source-registers (typical load-operate-store format). Most instructions actually correspond very closely to the original x86 instructions. This design choice results in lower complexity but at the cost of performance reduction. Bonnell has two identical decoders capable of decoding complex x86 instructions. Being variable length instruction architecture introduces an additional layer of complexity. To assist the decoders, Bonnell implements predecoders that determine instruction boundaries and mark them using a single-bit marker. Two cycles are allocated for predecoding as well as L1 storage. Boundary marks are also stored in the L1 eliminating the need to preform needlessly redundant predecoding. Repeated operations are retrieved pre-marked eliminating two cycles. Bonnel has a 36 KiB L1 instruction cache consisting of 32 KiB instruction cache and 4 KiB instruction boundary mark cache. All instructions (coming from both cache or predecode) must undergo full decode. It's worthwhile noting that Intel states Bonnell is a 16-stage pipeline because for the most part, after a cache hit you'll have 16 stages. This is also true in some cases where the processor can simultaneously decode the next instruction. However, in the cases where you get a miss, it will cost 3 additional stages to catch up and locate the boundary for that instruction for a total of 19 stages. | Bonnell is a departure from all modern x86 architectures with respect to decoding (including those developed by [[AMD]] and [[VIA]] and every Intel architecture since {{\\|P6}}). Whereas modern architectures transform complex [[x86]] instructions into a more easily digestible µop form, Bonnell does almost no such transformations. The pipeline is tailored to execute regular x86 instructions as single atomic operations consisting of a single destination register and up to three source-registers (typical load-operate-store format). Most instructions actually correspond very closely to the original x86 instructions. This design choice results in lower complexity but at the cost of performance reduction. Bonnell has two identical decoders capable of decoding complex x86 instructions. Being variable length instruction architecture introduces an additional layer of complexity. To assist the decoders, Bonnell implements predecoders that determine instruction boundaries and mark them using a single-bit marker. Two cycles are allocated for predecoding as well as L1 storage. Boundary marks are also stored in the L1 eliminating the need to preform needlessly redundant predecoding. Repeated operations are retrieved pre-marked eliminating two cycles. Bonnel has a 36 KiB L1 instruction cache consisting of 32 KiB instruction cache and 4 KiB instruction boundary mark cache. All instructions (coming from both cache or predecode) must undergo full decode. It's worthwhile noting that Intel states Bonnell is a 16-stage pipeline because for the most part, after a cache hit you'll have 16 stages. This is also true in some cases where the processor can simultaneously decode the next instruction. However, in the cases where you get a miss, it will cost 3 additional stages to catch up and locate the boundary for that instruction for a total of 19 stages. | ||

| Line 363: | Line 375: | ||

=== Modularity === | === Modularity === | ||

Bonnell is a highly modular architecture with almost all features disableable via built-in fuses allowing for many [[binning]] variation. Both virtualization support (VT-x/d) and {{intel|Hyper-Threading}} may be disabled to cut on power. Bonnell implements both AGTL+ and CMOS transceiver logic for the [[front-side bus]] signaling with either one capable of being fused off. CMOS signaling allows for lower power but cannot reach the high bug speeds that AGTL+ can. This may or maybe not be a restriction that system designers might face. | Bonnell is a highly modular architecture with almost all features disableable via built-in fuses allowing for many [[binning]] variation. Both virtualization support (VT-x/d) and {{intel|Hyper-Threading}} may be disabled to cut on power. Bonnell implements both AGTL+ and CMOS transceiver logic for the [[front-side bus]] signaling with either one capable of being fused off. CMOS signaling allows for lower power but cannot reach the high bug speeds that AGTL+ can. This may or maybe not be a restriction that system designers might face. | ||

| + | |||

| + | == Second Generation Enhancements == | ||

| + | [[File:lincroft goals.png|left|200px]] | ||

| + | [[File:bonnell system board size goals.png|right|300px]] | ||

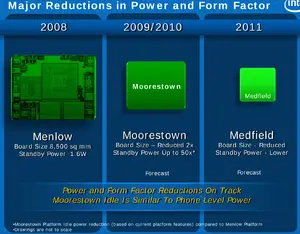

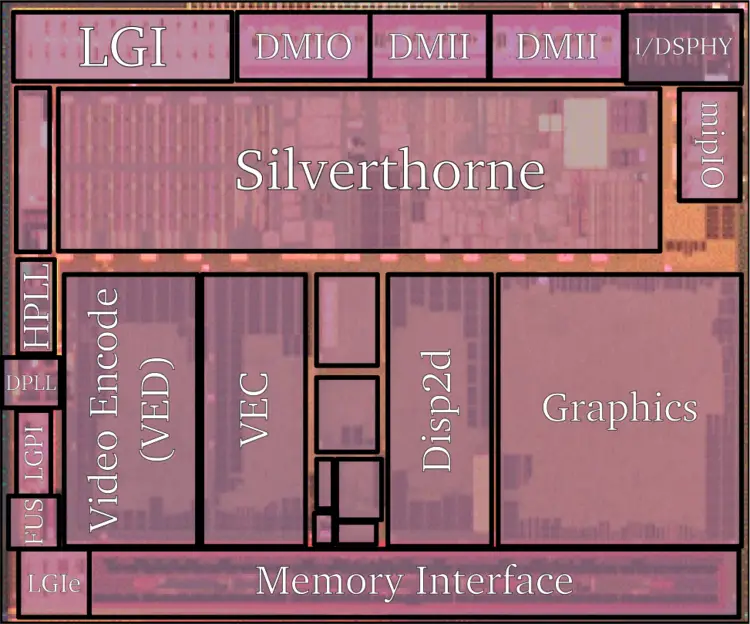

| + | With the introduction of {{intel|Lincroft|l=core}}, Intel has made substantial improvements the overall platform. The {{intel|Silverthorne|l=core}}-based systems had a great core in terms of power and performance, but they were drugged behind when was combined with far less efficient chipset and system design. These deficiencies were addressed in the second generation of Bonnell-based models. | ||

| + | |||

| + | The first variant was {{intel|Lincroft|l=core}} which set out to reduce the original system standby power of 1.6 W down to 32 mW (a 50x reduction) while reducing the overall board size by 2x. To achieve those goals Intel turned to higher integration, moving [[integrated graphics|Graphics]], CPU core, Video Acceleration, [[Display Controller]], and [[Memory Controller]] all in a single [[system on a chip]]. Those components were previously incorporated on the [[130 nm process]] chipset. This leaves the {{intel|Langwell|l=chipset}} chipset with just the low-power [[southbridge]] functionalities. The new chipset is also manufactured on a considerably better [[65 nm process]] | ||

| + | |||

| + | === Performance Features === | ||

| + | To address the higher performance goals, Intel introduced a number of new features into Lincroft including '''Bus Turbo Mode''' and '''Burst Mode'''. | ||

| + | |||

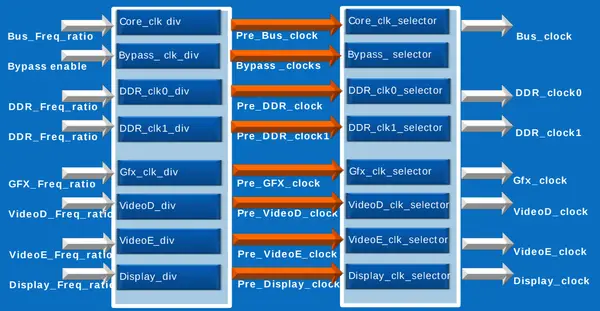

| + | ==== Clock Domains ==== | ||

| + | Each of {{intel|Lincroft|l=core}}'s multimedia engines are assigned a specific clock ratios and using a farm of clock dividers and clock selectors the appropriate clocks get generated to the individual multimedia engines. The complex clocking architecture implemented in Lincroft was designed to allow greater flexibility and a wider range of devices. This is done by simply tweaking the appropriate ratios for each engine based on the desired performance and power goals. | ||

| + | |||

| + | [[File:lincroft clock domains.png|600px]] | ||

| + | |||

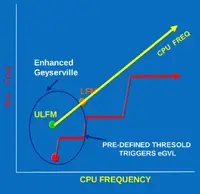

| + | ==== Bus Turbo Mode & Burst Mode ==== | ||

| + | Intel also introduced '''Burst Turbo Mode''', a feature designed to reduce memory latency by dynamically increasing bus frequencies in sync with CPU bursts. At pre-defined CPU frequencies, the bus gets dynamically overclocked to reduce the bottlenecking that might occur. This is implemented directly in hardware using the [[clock dividers]] (see [[#Clock Domains|§ Clock Domains]]) without the need to re-clock the PLLs. | ||

| + | |||

| + | Another feature that was introduced was '''Burst Mode''', the ability for the CPU to opportunistically take advantage of the thermal headroom on the T<sub>junction</sub> and T<sub>skin</sub> by temporarily increasing the CPU frequency. Upon violation of T<sub>junction</sub>/T<sub>skin</sub>, the system throttles down back to recovery points (LFM [[c-state]]). | ||

| + | |||

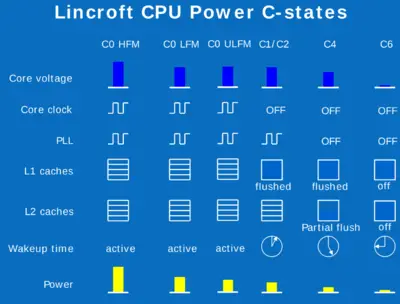

| + | === Low-power features === | ||

| + | In order to further reduce power Intel introduced a number of new features: | ||

| + | |||

| + | * Low power architecture features | ||

| + | ** [[MIPI-DSI]] | ||

| + | ** [[LP-DDR1]] | ||

| + | ** Integrated Hardware accelerators for Video Encode/Code | ||

| + | * Enhanced Geyserville for ULFM | ||

| + | * Extended CPU Power [[C-States]] | ||

| + | * Distributed [[Power Gating]] | ||

| + | |||

| + | ==== Enhanced Geyserville (eGVL) ==== | ||

| + | [[File:lincroft new egvl mode.png|right|200px]] | ||

| + | '''Enhanced Geyserville''' is a new mode that allows the CPU to run below LFM at V<sub>min</sub>. This enables linear saving of average power during instances where the CPU is idle while in C0 [[C-State]] (cV²F, note that leakage is mostly a constant due to V=V<sub>min</sub> the entire time). Equivalent, the bus frequency is also down-clocked at predefined frequencies (see [[#Bus Turbo Mode & Burst Mode|§ Bus Turbo Mode]]). The additional ultra low-power mode is exposed as a [[P-State]] to the [[operating system]]. | ||

| + | |||

| + | Below is the C-State chart with the additional Ultra-low LFM state added, enabling further decrease in average power consumption. | ||

| + | |||

| + | [[File:lincroft extended c-states.png|400px]] | ||

| + | |||

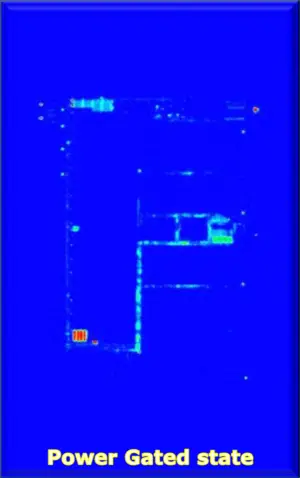

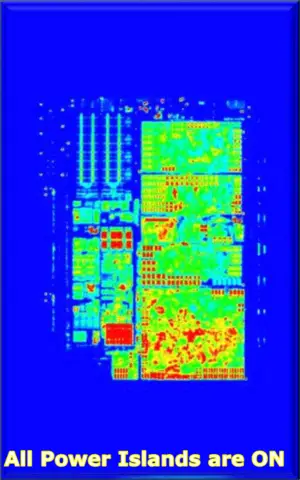

| + | ==== Extensive power-gating ==== | ||

| + | Lincroft introduces an extensive system of power-gating. The entire SoC is divided up into multiple physical power islands. Each island can be individually controlled through a distributed power-gating system. Lincroft allows for a fine-grained management of power through both hardware and software to be able to disable areas of the chip that are not being actively utilized. | ||

| + | |||

| + | |||

| + | <div style="display: inline-block;"> | ||

| + | <div style="float: left; margin: 10px;">[[File:lincroft all off.png|300px]]</div> | ||

| + | <div style="float: left; margin: 10px;">[[File:lincroft all on.png|300px]]</div> | ||

| + | </div> | ||

== Die == | == Die == | ||

| Line 447: | Line 507: | ||

== Cores == | == Cores == | ||

| − | === First | + | Bonnell has lived through a number of iterations unlike the mainstream variants which followed a {{intel|tick-tock|far more ambitious development cycle}}. Products based on Bonnell can more or less be split into two generations: |

| − | First generation of Bonnell-based microprocessors introduced 2 cores: '''{{intel|Silverthorne|l=core}}''' for ultra-mobile PCs and mobile Internet devices (MIDs) and '''{{intel|Diamondville}}''' for ultra cheap notebooks and desktops. | + | |

| − | + | * '''First Generation''' - initial Bonnell processor models. Those relied on a number of external chipset chips for the I/O, graphics, and various other system features. | |

| − | {{ | + | * '''Second Generation''' - considerably higher integration was introduced. The original CPU was not incorporated along with many of its peripheral on a single chip to create a [[System on a Chip]]. |

| − | + | ||

| − | + | === First generation === | |

| − | {{ | + | First generation of Bonnell-based microprocessors introduced 2 cores: '''{{intel|Silverthorne|l=core}}''' for ultra-mobile PCs and mobile Internet devices (MIDs) and '''{{intel|Diamondville}}''' for ultra cheap notebooks and desktops. |

| − | '''Diamondville''' was the codename for the series of ultra cheap notebooks and desktops introduced in 2008. Diamondville is very much a soldered-on-motherboard derivative of {{intel|Silverthorne|l=core}} with faster FSB (operating at 533 MHz - 667 MHz). The dual-core version is | + | |

| + | * '''{{intel|Silverthorne|l=core}}''' was the codename for a series of Mobile Internet Devices (MIDs) introduced in 2008. These processors had 1 core and 2 threads with a FSB operating at 400 MHz-533 MHz. Those models were branded as {{intel|Atom}} MIDs and went along with the {{intel|poulsbo|l=chipset}} chipset. | ||

| + | * '''{{intel|Diamondville|l=core}}''' was the codename for the series of ultra cheap notebooks and desktops introduced in 2008. Diamondville is very much a soldered-on-motherboard derivative of {{intel|Silverthorne|l=core}} with faster FSB (operating at 533 MHz - 667 MHz). The dual-core version is a [[Multi Chip Module]] (MCM) Silverthorne variant operating on the same [[FSB]]. | ||

| + | |||

=== Second Generation === | === Second Generation === | ||

First generation of Bonnell-based microprocessors while being low power had to work with the older [[90 nm process]] {{intel|945GSE}} chipset and {{intel|82801GBM}} I/O controller with a TDP of almost 9.5 watts - almost 4 times that of the processor itself. Second generation Bonnell-based microprocessors aimed to address this issue by integrating a memory controller and GPU on-chip. This drastically reduced power consumption and cost. | First generation of Bonnell-based microprocessors while being low power had to work with the older [[90 nm process]] {{intel|945GSE}} chipset and {{intel|82801GBM}} I/O controller with a TDP of almost 9.5 watts - almost 4 times that of the processor itself. Second generation Bonnell-based microprocessors aimed to address this issue by integrating a memory controller and GPU on-chip. This drastically reduced power consumption and cost. | ||

| − | + | ||

| − | {{ | + | * '''{{intel|Lincroft|l=core}}''' is the codename for Bonnell-based Silverthorne's successor. Lincroft integrates on-die the graphics and memory controller. Lincroft effectively replaces the original Silverthorne offering 2x reduction in average circuit board size and up to 50x standby power reduction vs Menlow equivalent. Lincroft also introduces a 2x reduction in the overall active power consumption of the system. |

| − | + | ||

==== Pineview ==== | ==== Pineview ==== | ||

{{main|intel/pineview|l1=Pineview}} | {{main|intel/pineview|l1=Pineview}} | ||

| Line 488: | Line 551: | ||

<table class="comptable sortable tc13 tc14 tc15 tc16 tc17 tc18 tc19 tc20 tc21 tc22"> | <table class="comptable sortable tc13 tc14 tc15 tc16 tc17 tc18 tc19 tc20 tc21 tc22"> | ||

<tr class="comptable-header"><th> </th><th colspan="20">List of Bonnell-based Processors</th></tr> | <tr class="comptable-header"><th> </th><th colspan="20">List of Bonnell-based Processors</th></tr> | ||

| − | <tr class="comptable-header"><th> </th><th colspan=" | + | <tr class="comptable-header"><th> </th><th colspan="9">Main processor</th><th colspan="2">Bus</th><th colspan="2">[[IGP]]</th><th colspan="4">Features</th></tr> |

| − | {{comp table header 1|cols=Price, Core, Launched, C, T, Freq, TDP, SDP, Speed, Rate, Package, {{intel|Hyper-Threading|HT}}, VT-x, {{intel|EIST}}}} | + | {{comp table header 1|cols=Price, Core, Launched, C, T, Freq, Burst, TDP, SDP, Speed, Rate, Name, Frequency, Package, {{intel|Hyper-Threading|HT}}, VT-x, {{intel|EIST}}}} |

{{#ask: [[Category:microprocessor models by intel]] [[instance of::microprocessor]] [[microarchitecture::Bonnell]] | {{#ask: [[Category:microprocessor models by intel]] [[instance of::microprocessor]] [[microarchitecture::Bonnell]] | ||

|?full page name | |?full page name | ||

| Line 499: | Line 562: | ||

|?thread count | |?thread count | ||

|?base frequency#GHz | |?base frequency#GHz | ||

| − | |?tdp# | + | |?turbo frequency (1 core)#GHz |

| + | |?tdp#mW | ||

|?sdp#mW | |?sdp#mW | ||

|?bus speed | |?bus speed | ||

|?bus rate | |?bus rate | ||

| + | |?integrated gpu | ||

| + | |?integrated gpu base frequency | ||

|?package | |?package | ||

|?has simultaneous multithreading | |?has simultaneous multithreading | ||

| Line 509: | Line 575: | ||

|format=template | |format=template | ||

|template=proc table 3 | |template=proc table 3 | ||

| − | |userparam= | + | |userparam=19:17 |

|mainlabel=- | |mainlabel=- | ||

}} | }} | ||

| Line 543: | Line 609: | ||

* Corporation, Intel. "Intel 64 and IA-32 architectures optimization reference manual." (2009). | * Corporation, Intel. "Intel 64 and IA-32 architectures optimization reference manual." (2009). | ||

* Beavers, Brad. "The story behind the Intel Atom processor success." IEEE Design & Test of Computers 26.2 (2009). | * Beavers, Brad. "The story behind the Intel Atom processor success." IEEE Design & Test of Computers 26.2 (2009). | ||

| + | |||

| + | == See also == | ||

| + | * Marvell's {{marvell|Sheeva PJ1|l=arch}} | ||

| + | * ARM's {{arm|ARM11|l=arch}} | ||

Latest revision as of 19:29, 23 May 2019

| Edit Values | |

| Bonnell µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | Intel |

| Manufacturer | Intel |

| Introduction | March 2, 2008 |

| Phase-out | 2011 |

| Process | 45 nm |

| Core Configs | 1, 2 |

| Pipeline | |

| Type | Superscalar |

| OoOE | No |

| Speculative | Yes |

| Reg Renaming | No |

| Stages | 16-19 |

| Instructions | |

| ISA | x86-64 |

| Extensions | MOVBE, MMX, SSE, SSE2, SSE3, SSSE3 |

| Cache | |

| L1I Cache | 32 KiB/Core 8-way set associative |

| L1D Cache | 24 KiB/Core 6-way set associative |

| L2 Cache | 512 KiB/Core 8-way set associative |

| Cores | |

| Core Names | Silverthorne, Diamondville, Lincroft, Pineview, Tunnel Creek, Stellarton, Sodaville, Groveland |

| Succession | |

Bonnell was a microarchitecture for Intel's 45 nm ultra-low voltage microprocessors first introduced in 2008 for their then-new Atom family. Bonnell, which was named after the highest point in Austin - Mount Bonnell, was Intel's first x86-compatible microarchitecture designed to target the ultra-low power market.

Bonnell (project Silverthorne then) was designed by a then-new low-power design team Intel created at their Texas Development Center in Austin in 2004 along with a new chipset (Poulsbo) design team. The design team was led by Elinora Yoeli. While Yoeli previously worked at her native country, Bonnell was a US design and was unconnected to any of Intel's projects worked on by the Israel Design Center in Haifa. Previously Yoeli led the Israeli team in the development of Pentium M.

Contents

Codenames[edit]

| Platform | Chipset | Core | Target |

|---|---|---|---|

| Menlow | Poulsbo | Silverthorne | MIDs |

| Menlow | Poulsbo | Diamondville | Nettops |

| Moorestown | Langwell | Lincroft | MIDs |

| Pine Trail | Tiger Point | Pineview | Nettops |

| Queens Bay | Topcliff | Tunnel Creek | Embedded |

| Queens Bay | Topcliff | Stellarton | Embedded + Altera FPGA |

| Sodaville | CE | ||

| Groveland | CE | ||

| Elk Rock | CE |

Generation successor[edit]

| First Generation | Second Generation | Third Generation | ||

|---|---|---|---|---|

| Silverthorne | → | Lincroft | ||

| Diamondville | → | Pineview | ||

| Tunnel Creek | ||||

| Stellarton | ||||

| Sodaville | → | Groveland |

Brands[edit]

Intel sold Bonnell-based processors under the Atom brand. Additionally, manufacturers were allowed to use the Centrino Atom brand if the system consist of a Bonnell-based processor, the chipset, wireless capabilities (WiFi, 3G, WiMAX), is battery powered, and had a screen size of up to 6".

|

|

|

Release Dates[edit]

The Atom family was officially announced on March 2, 2008 under the Intel Atom and Intel Centrino Atom brands. Bonnell was first introduced on April 2nd 2008 during the Intel Developers Forum in Shanghai.

Process Technology[edit]

| 45 nm Manufacturing Fabs | |

|---|---|

| Fab | Location |

| D1D | Hillsboro, Oregon |

| Fab 32 | Chandler, Arizona |

| Fab 28 | Kiryat Gat, Israel |

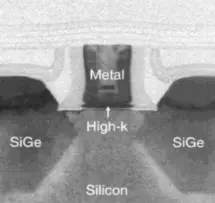

Bonell is designed to be manufactured using a 45 nm process. Intel's 45 nm process is the first high-volume manufacturing process to introduce High-k + metal gate transistors.

| Bonnell | |

|---|---|

| 45 nm | |

| Gate Pitch | 180 nm |

| Interconnect Pitch | 160 nm |

| SRAM bit cell (HD) | 0.346 µm² |

| SRAM bit cell (LP) | 0.3816 µm² |

Compatibility[edit]

| Vendor | OS | Version | Notes |

|---|---|---|---|

| Microsoft | Windows | Windows XP Embedded SP2 | Support |

| Windows Embedded CE 6.0 | Support | ||

| Windows 7 | Support | ||

| Windows Embedded Standard 7 | Support | ||

| Linux | Linux | Kernel 2.4/2.6? | Initial Support |

| MeeGo 1 | Support |

Compiler support[edit]

| Compiler | Arch-Specific | Arch-Favorable |

|---|---|---|

| GCC | -march=bonnell |

-mtune=bonnell

|

| LLVM | -march=bonnell |

-mtune=bonnell

|

| Visual Studio | /arch:SSE3

|

Architecture[edit]

Bonnell features a brand new architecture not based on any previous Intel design. The architecture was specifically designed for ultra-mobile PCs (UMPCs), mobile internet devices (MID), and other embedded devices. Bonnell's primary goals were:

- Reduce power consumption,

- while staying fully x86-compatible,

- at acceptable performance

Performance/Power new rule: +1% performance for at most +1% power consumption.

In additional to full-x86 compatibility and power requirements, Bonnell was also required to maintain 100% compatibility with Intel's Core architecture (specficially the then-new Core 2 Duo processors.

Architecture[edit]

- Strictly ultra-low power

- 45 nm process, 9 metal layers, CMOS

- 500 mW to 2 W TDP

- Average 220 mW

- Idle under 80 mW

- 533 MT/s dual mode (GTL & CMOS) FSB

- In-order

- 2-issue decode

- Simple 2-way SMT

- Instruction Queue of 32 entries (16 entries/thread)

- FP Register File (per thread)

- Integer Register File (per thread)

- Private L1 cache for each core

- Shared L2 cache for the entire chip

The number of functional units were kept to minimum to cut on power consumption.

- 2 address generation units (AGUs)

- 2 Integer ALUs (1 for jumps, 1 for shifts)

- 2 FP ALUs (1 adder, 1 for others)

- No Integer multiplier & divider (shared with FP ALU instead)

Block Diagram[edit]

Memory Hierarchy[edit]

- Cache

- Hardware prefetchers

- C6 cache

- 10.5 KiB array to hold the architectural state during deep power down state

- 1-read, 1-write ported

- L1 Instruction Cache

- 36 KiB

- 32 KiB Instruction + 4 KiB Boundary Mark

- 8-way set associative

- 1 read and 1 write port

- 8 transistors (instead of 6) to reduce voltage

- 1-bit pairty (but no ECC)

- 36 KiB

- L1 Data Cache

- 24 KiB

- 6-way set associative

- 1 read and 1 write port

- 8 transistors (instead of 6) to reduce voltage

- 1-bit pairty (but no ECC)

- Per core

- 24 KiB

- L2 Cache:

- 512 KiB 8-way set associative

- ECC support

- Shrinkable from 512 KiB to 128 KiB (2-way)

- 64-bit cache line

- Per core

- Tag/LRU/State bit

- All in one array

- Tag + data = 4.5 KiB + 17.5 KiB

- L3 Cache:

- No level 3 cache

- RAM

- Maximum of 2 GiB, 4 GiB, and 8 GiB

Note that the L1 cache for data and instructions were originally both 32 KiB (8-way), however due to power restrictions, the L1d$ was later reduced to 24 KiB.

- TLB

- ITLB

- 32-entry

- fully associative

- DTLB

- 4 KiB PAges

- 64-entry TLB

- 4-way set associative

- 16-entry micro-TLB

- fully associative

- duplicated for each thread

- 16-entry PDE cache

- fully associative

- 64-entry TLB

- Large Pages

- 8 entries, 4-way set associative

- 4 KiB PAges

- ITLB

Overview[edit]

Bonnell's architecture shares very little in common with other Intel designs. To achieve the strict ultra-low power objects, Bonnell features a very slimmed down design discarding many high-performance techniques used by Intel's high-performance architectures such as aggressive speculative execution, out-of-order execution, and µop transformation.

Part of the design requirement was that Bonnell retain full x86 compatibility, up to the latest extension - at one tenth of the power consumption of the Pentium M. This meant any software is now 100% compatible but it forced engineers to deal with all the baggage the architecture brought along. The decision to offer full compatibility brought its own set of benefits such as access to the largest software code base in the world, including the ability to run any other x86 operating system unmodified. At the same time it forced the design team to resort to other means of reducing power.

Up to Bonnell, all of Intel's existing architectures put very low priority on power efficiency (note that this has significantly changed since the introduction of Sandy Bridge). High-performance, high-throughput, complex designs are simply inadequate for the kind of power goals required out of Bonnell, even if they were trimmed down. It was decided that Bonnell would be designed from the scratch with power goals in mind. For those reasons Bonnell resembles the P5 microarchitecture.

Pipeline[edit]

Much like the original P5 microarchitecture, Bonnell consists of an in-order dual-issue pipeline. The pipeline is shown below. Note the pipeline is duplicated for dual-issue execution.

Unlike P5, which only had 5 stages, Bonnell has 16 to 19 pipeline stages. The longer pipeline allows a more even spreading of heat across the chip with more units. This also allows a higher clock rate.

Front End[edit]

Bonnell's front end is very simple when compared to Intel's high-performance architectures. Out-of-order execution (OoOE) that is found ubiquitously in all HPC architectures was rejected. Bonnell's power and area constraints simply couldn't allow for the complex logic needed to support that capability. The Instruction Fetch consists of 3 stages, capable of going through up to 16 bytes per cycle. Like fetch, the Instruction Decode is also 3 stages, capable of decording instructions with up to 3 prefixes each cycle (considerably longer for more complex instructions).

Bonnell is a departure from all modern x86 architectures with respect to decoding (including those developed by AMD and VIA and every Intel architecture since P6). Whereas modern architectures transform complex x86 instructions into a more easily digestible µop form, Bonnell does almost no such transformations. The pipeline is tailored to execute regular x86 instructions as single atomic operations consisting of a single destination register and up to three source-registers (typical load-operate-store format). Most instructions actually correspond very closely to the original x86 instructions. This design choice results in lower complexity but at the cost of performance reduction. Bonnell has two identical decoders capable of decoding complex x86 instructions. Being variable length instruction architecture introduces an additional layer of complexity. To assist the decoders, Bonnell implements predecoders that determine instruction boundaries and mark them using a single-bit marker. Two cycles are allocated for predecoding as well as L1 storage. Boundary marks are also stored in the L1 eliminating the need to preform needlessly redundant predecoding. Repeated operations are retrieved pre-marked eliminating two cycles. Bonnel has a 36 KiB L1 instruction cache consisting of 32 KiB instruction cache and 4 KiB instruction boundary mark cache. All instructions (coming from both cache or predecode) must undergo full decode. It's worthwhile noting that Intel states Bonnell is a 16-stage pipeline because for the most part, after a cache hit you'll have 16 stages. This is also true in some cases where the processor can simultaneously decode the next instruction. However, in the cases where you get a miss, it will cost 3 additional stages to catch up and locate the boundary for that instruction for a total of 19 stages.

Some x86 instructions are simply too complex to handle directly. Those selected few get diverted into the micro-code sequencer ROM (MSROM) for decoding producing much more sane RISCish instructions at the cost of 2 additional cycles. Intel estimates that only 5% of common software require instructions to be split up. Only decoder0 can request transfer to use the MSROM. All instructions longer than 8 bytes or instructions having more than three prefixes will result in a MSROM transfer unconditionally. Those instructions will experience two cycles of delay. The inability to execute things out-of-order eliminates lots of optimization opportunities at this stage. One thing Bonnell can do is lockstep instructions that can be execute simultaneously such as in the case of instructions that performance a memory access along an arithmetic operation. In those instances Bonnell will issue the instruction as if it were two separate instructions executing simultaneously. In addition, only one x87 instruction can be decoded per cycle.

Because Bonnell has support for Hyper-Threading, Intel's brand name for their own simultaneous multithreading technology, a number of modifications had to be done. The prefetch buffer and the instruction queue have been duplicated for each thread.

Branch predictor[edit]

No aggressive speculative execution is done in Bonnell, however it does implements a light-weight Gshare branch predictor consisting of a two-level adaptive predictor with a 12-bit global history table. The pattern history table has 4096 entries and is competitively shared between threads. The branch buffer target has 128 entries (4-way by 32 sets). While unconditional jumps are not recorded in the table, always-taken and never-taken jumps do.

The branch-misprediction penalty is 11 to 13 cycles. Some of the rare or complex x86 instructions will detour into a microcode sequencer for decoding, necessitating two additional clock cycles. Additionally there is a roughly 7 cycle penalty for correctly predicted branches but no target can be predicted because of a missing branch target buffer (BTB) entry. Bonnell return stack buffer is 8-entry deep.

Back End[edit]

Each cycle two instructions are dispatched in-order. The scheduler can take a pair of instructions from a single thread or across threads. Bonnell in-order back-end resembles a traditional early 90s design featuring a dual ALU, a dual FPU and a dual AGU. Similarly to the front-end, in order to accommodate simultaneous multithreading, the Bonnell design team chose to duplicate both the floating-point and integer register files. The duplication of the register files allows Bonnell to perform context switching on each stage by maintaining duplicate states for each thread. The decision to duplicate this logic directly results in more transistors and larger area of the silicon. Overall implementing SMT still required less power and less die area than the other heavyweight alternatives (i.e., out-of-order and larger superscaler). Nonetheless the total register file area accounts for 50% of the entire core's die area which was single-handedly an important contributor to the overall chip power consumption.

FP/SIMD execution Cluster[edit]

| SIMD/FP Execution Cluster Ports | |

|---|---|

| Port 0 | Port 1 |

| SIMD ALU (128-bit / 64-bit int) |

SIMD ALU (128-bit) |

| Shuffle unit (128-bit / 64-bit int) |

FP Adder |

| SIMD/FP multiply unit (128-bit / 64-bit int) | |

| Divide unit (support IMUL, IDIV) | |

In the further pursuit of power saving specialized execution units were minimized as much as possible. Bonnell's floating point & SIMD execution cluster does most of the heavy lifting. It features a 128 bit SIMD integer path containing 2 SIMD ALUs and 1 shuffle unit. Bonnell's SIMD integer multiplier and floating point divider are also responsible for the scalar integer multiply and integer divider operations. Additionally the cluster includes a 64 bit FP & SIMD integer multipliers and a 128 bit FP adder.

Additionally, this cluster contains a Safe Instruction Recognition (SIR) unit responsible for supporing out-of-order commits. The idea behind the SIR unit is fairly simple, when conditions are met (i.e, when there are no inter-dependency between varying latency instructions) the two instructions will execute simultaneously allowing the shorter latency instruction to execute and finish before a possibly longer latency floating point operation ends. This algorithm reduces needless stalls that plagues traditional in-order pipelines.

Integer Execution Cluster[edit]

| SIMD/FP Execution Cluster Ports | |

|---|---|

| Port 0 | Port 1 |

| Load/Store | Jump unite and LEA |

| ALU0 | ALU1 |

| Shift/Rotate unit | Bit processing unit |

The integer execution cluster contains two ALUs, a shifter, and a jump execution unit capable of performing single-cycle 64 bit integer operations. The Integer cluster has store-forwarding support allowing for a 0-cycle latency effective load-to-use.

Memory Subsystem[edit]

Bonnell has two address generation units (AGUs). For data, there is 24 KiB write-back L1 cache with a 2-level DTLB hierarchy, hardware page walker, and an integer store-to-load forwarding support. Additionally, there is a rather large 512 KiB L2 cache with inline ECC and hardware pre-fetchers. The tag, LRU, and the state bits are all stored in a single array to minimize area. The tag and data consist of 8 4.5 KiB tag sub arrays and 32 17.5 KiB data sub-arrays made of 256 cells on the bit line and 136 cells on the write line.

As a power-saving feature, the L2 cache can be configured down to 2-way dynamically (i.e. programmatically) for applications that do not require the full performance. Doing so reduces the power and downsizes the cache to 128 KiB. Additionally, for less demanding tasks, the Bonnell power gates unused ways. It's interesting to note that the design team placed the TAG blocks at the bottom of the DATA arrays allowing, in theory, to expend the L2 to 1 MiB should they want to.

I/O Bus[edit]

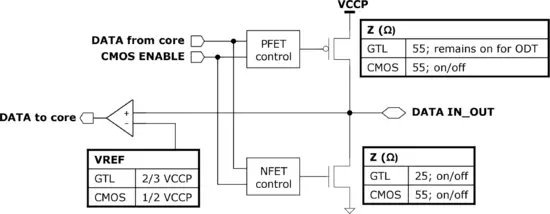

- Main article: Front-Side Bus

Traditionally, Intel has been using AGTL+ transceivers (Advanced Gunning Transceiver Logic) for their front-side bus communication. With bonnell (and the chipset) Intel also introduced a CMOS signaling logic mode. CMOS has the advantage of only drawing power during transition. The switch to CMOS saves 200-500 mW at the cost of worse latency and slower bus which ranges from 400 to 533 MHz. Bonnell's intended applications is not heavy processing machine, the lower bus speed was likely a worthy compromise.

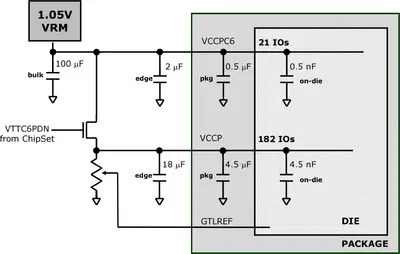

Bonnell implements both mode, so designers who prefer the faster bus can opt for the traditional AGTL+ transceivers while those who seek low power can opt for the CMOS implementation. Intel offers both types by simply fusing the appropriate circuitry. This is done by reprogramming the NFET control pull-down and the PFET control accordingly, activating or deactivating the resistor and switching the voltage.

Note that during deep sleep, the design team designed the power rails using two power planes. To further save power, only keeping 21 pins are kept alive, reducing the average power by another 10% while killing off 182 of the other I/O which are not necessary for that state.

Features[edit]

Multithreading[edit]

Bonnell supports Intel's Hyper-Threading, their marketing term for their own implementation of simultaneous multithreading. The notion of implementing simultaneous multithreading on such a low-power architecture might seem unusual at first. In fact, it's one of only a handful of ultra-low power architectures to support such feature. Intel justified this design choice by demonstrating that performance enjoys an uplift of anywhere from 30% to 50% while worsening power consumption by up to 20% (with an average of 30% performance increase for 15% more power). The toll on the die area was a mere 8%.

In the front-end, the prefetch buffer and the instruction queue have been duplicated for each thread, everything else is competitively shared between the threads. In the back-end, only the integer and floating register files are duplicated, everything else is competitively shared as well. Note that both threads compete over the L1 instruction and data caches as well as the L2 and the TLBs with the exception of a 16-entry micro-TLB that's duplicated for each thread.

Low-power features[edit]

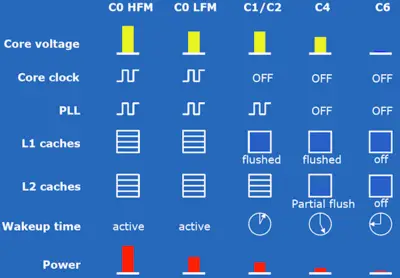

Bonnell implements a number of features to enhance battery life including several lower power states (C-states). Bonnell is capable of achieving 2 GHz core frequency at 1 V and can go down all the way to 600 MHz at 0.75 V though down-dialing the core phase-lock-loop (PLL) ratio. Bonnell supports up to C6 C-state where more power saving is achieving with higher C-state which in term means more components (i.e., features) are turned off.

• C-0 state, the processor can operate at its highest frequency (in high-frequency mode (HFM)) and in its lowest frequency (low frequency mode (LFM)).

• C-1 state, the core is power-gated and the L1 caches are flushed, yielding lower dynamic power; exit latency is sub-1µs

• C-4 state, the PPLs are shut down down as well, exit latency is in the order of 30 µs

• C-6 state, the state of the machine is kept alive in a 10.5 KiB register file (SRAM kept at VCC of 0.3 V) with the core power is completely shut off; exit latency in the order of 100 µs

Intel estimates C-6 residency to be between 80% and 90% resulting in an average power in the order of 220 mW. Likewise Idle power, which is dominated by leakage power of the functional units, is below 80 mW.

Modularity[edit]

Bonnell is a highly modular architecture with almost all features disableable via built-in fuses allowing for many binning variation. Both virtualization support (VT-x/d) and Hyper-Threading may be disabled to cut on power. Bonnell implements both AGTL+ and CMOS transceiver logic for the front-side bus signaling with either one capable of being fused off. CMOS signaling allows for lower power but cannot reach the high bug speeds that AGTL+ can. This may or maybe not be a restriction that system designers might face.

Second Generation Enhancements[edit]

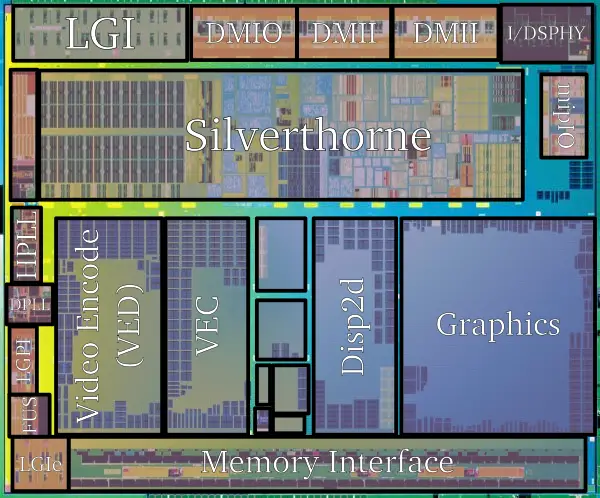

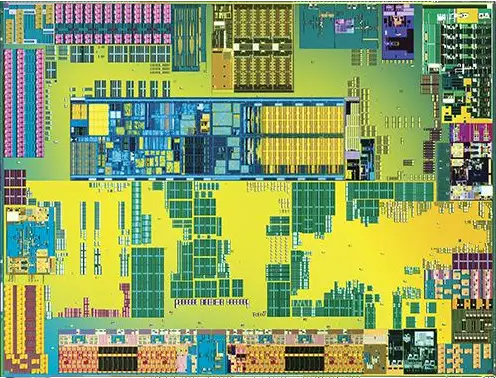

With the introduction of Lincroft, Intel has made substantial improvements the overall platform. The Silverthorne-based systems had a great core in terms of power and performance, but they were drugged behind when was combined with far less efficient chipset and system design. These deficiencies were addressed in the second generation of Bonnell-based models.

The first variant was Lincroft which set out to reduce the original system standby power of 1.6 W down to 32 mW (a 50x reduction) while reducing the overall board size by 2x. To achieve those goals Intel turned to higher integration, moving Graphics, CPU core, Video Acceleration, Display Controller, and Memory Controller all in a single system on a chip. Those components were previously incorporated on the 130 nm process chipset. This leaves the Langwell chipset with just the low-power southbridge functionalities. The new chipset is also manufactured on a considerably better 65 nm process

Performance Features[edit]

To address the higher performance goals, Intel introduced a number of new features into Lincroft including Bus Turbo Mode and Burst Mode.

Clock Domains[edit]

Each of Lincroft's multimedia engines are assigned a specific clock ratios and using a farm of clock dividers and clock selectors the appropriate clocks get generated to the individual multimedia engines. The complex clocking architecture implemented in Lincroft was designed to allow greater flexibility and a wider range of devices. This is done by simply tweaking the appropriate ratios for each engine based on the desired performance and power goals.

Bus Turbo Mode & Burst Mode[edit]

Intel also introduced Burst Turbo Mode, a feature designed to reduce memory latency by dynamically increasing bus frequencies in sync with CPU bursts. At pre-defined CPU frequencies, the bus gets dynamically overclocked to reduce the bottlenecking that might occur. This is implemented directly in hardware using the clock dividers (see § Clock Domains) without the need to re-clock the PLLs.

Another feature that was introduced was Burst Mode, the ability for the CPU to opportunistically take advantage of the thermal headroom on the Tjunction and Tskin by temporarily increasing the CPU frequency. Upon violation of Tjunction/Tskin, the system throttles down back to recovery points (LFM c-state).

Low-power features[edit]

In order to further reduce power Intel introduced a number of new features:

- Low power architecture features

- Enhanced Geyserville for ULFM

- Extended CPU Power C-States

- Distributed Power Gating

Enhanced Geyserville (eGVL)[edit]

Enhanced Geyserville is a new mode that allows the CPU to run below LFM at Vmin. This enables linear saving of average power during instances where the CPU is idle while in C0 C-State (cV²F, note that leakage is mostly a constant due to V=Vmin the entire time). Equivalent, the bus frequency is also down-clocked at predefined frequencies (see § Bus Turbo Mode). The additional ultra low-power mode is exposed as a P-State to the operating system.

Below is the C-State chart with the additional Ultra-low LFM state added, enabling further decrease in average power consumption.

Extensive power-gating[edit]

Lincroft introduces an extensive system of power-gating. The entire SoC is divided up into multiple physical power islands. Each island can be individually controlled through a distributed power-gating system. Lincroft allows for a fine-grained management of power through both hardware and software to be able to disable areas of the chip that are not being actively utilized.

Die[edit]

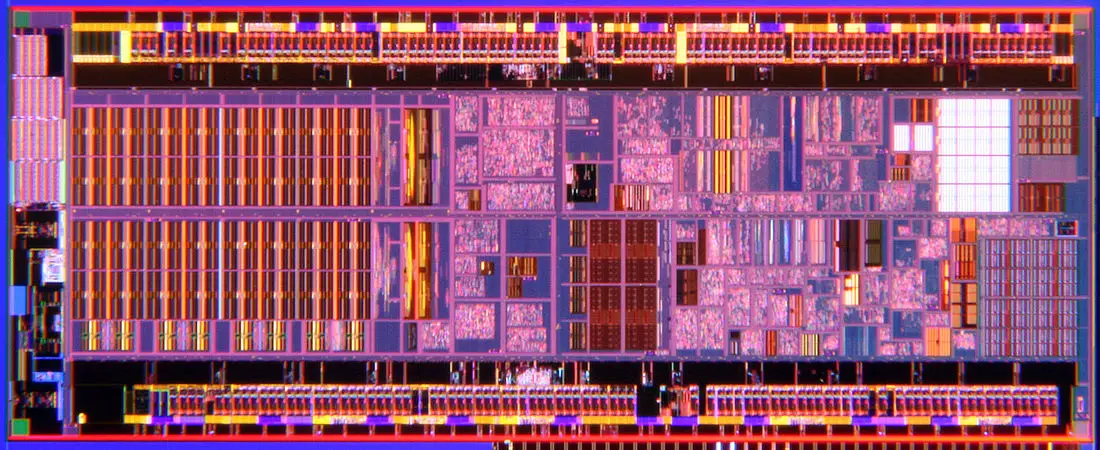

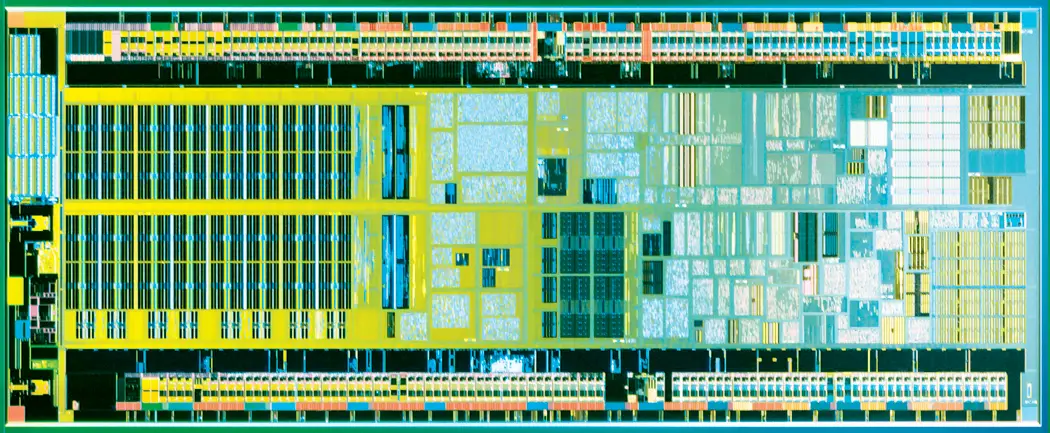

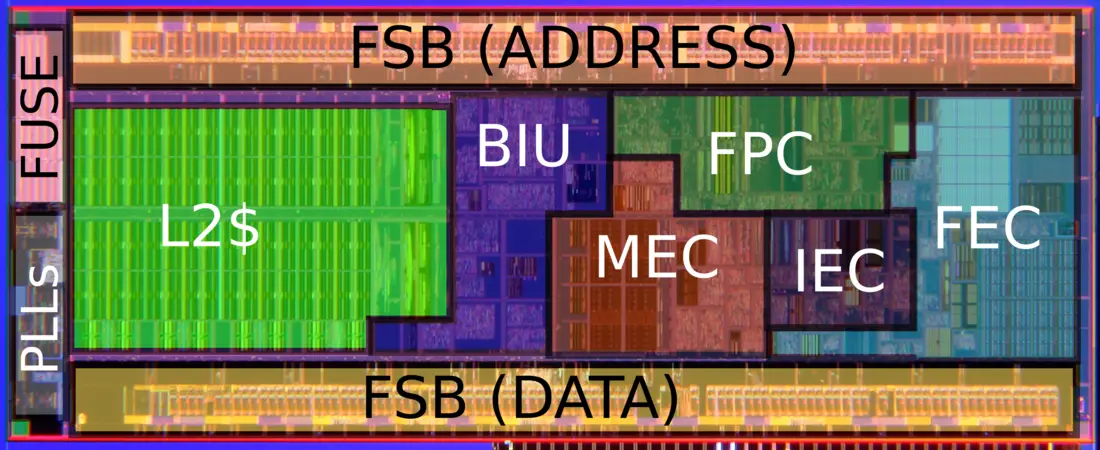

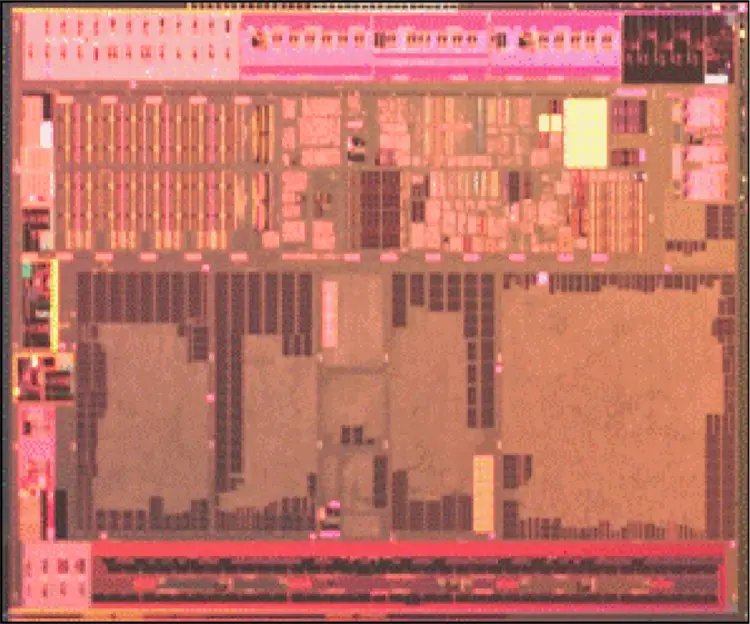

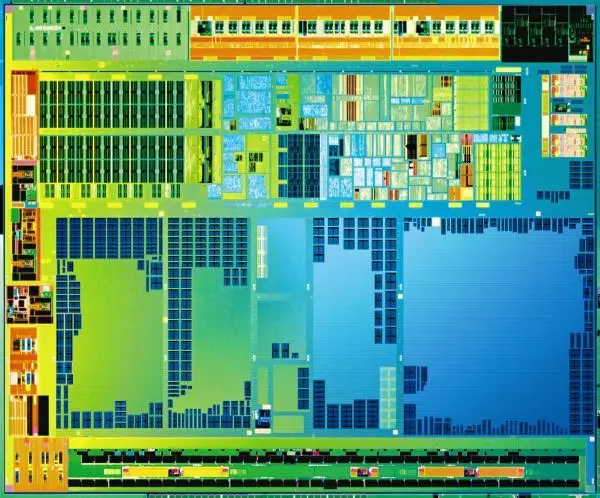

Silverthorne[edit]

- 45 nm process

- 9 metal layers

- 47,212,207 transistors

- 3.1 mm x 7.8 mm

- 24.18 mm² die size

- packaged in a Halide-Free 441 ball, 14 mm x 13 mm µFCBGA

Function Unit Blocks (FUBs):

- BIC/BIU - Bus Interface Cluster/Unit

- MEC - Memory Cluster Execution & L1d$

- FPC - FP/SIMD execution Cluster

- IEC - Integer Execution Cluster

- FEC - Front-End Cluster & L1i$

- FSB - Front Side Bus

Physical layout[edit]

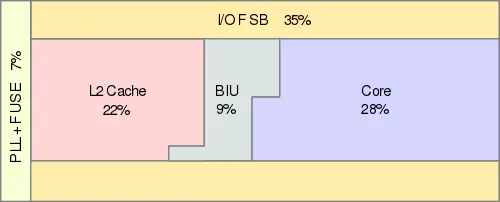

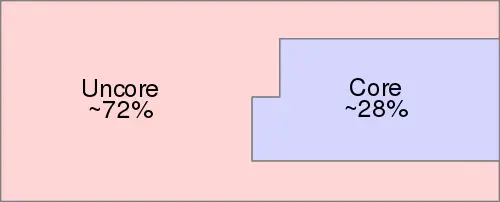

The Atom design team was considerably smaller than Intel's typical design teams which forced them to work in a slightly different way. The design team used a methodology they described as a "sea of Functional Unit Block" (FUBs) where by all cluster hierarchies (including unit-level hierarchies) are flattened at the chip level. This development methodology allowed for faster iteration. The various FUB designs were divided among the team members allowing them to handle the design in a more manageable way. All in all, Bonnell's physical database consisted of 205 unique FUBs interlinked via 41,000 FUB-to-FUB interconnects. Bonnell is manufactured on Intel's 45 nm process. 91% of the FUBs using pre-characterized standard cells (45% structured data-path and 46% fully synthesized random logic blocks) with only the remaining 9% being full-custom blocks. The unusually high utilization of standard cells (at least for Intel) is likely due to the limited resources given to the Bonnell design team.

| Type | Unique | Instances |

|---|---|---|

| Random Logic Synthesized | 92 | 92 |

| Structured Data Paths | 88 | 140 |

| L2 sub-arrays | 2 | 40 |

| Custom | 18 | 19 |

| Repeater Station | - | 317 |

| Total | 200 | 608 |

| Cluster | Transistor Count |

|---|---|

| Core | 13,828,574 |

| Uncore | 2,738,951 |

| L2 & L2 tag | 30,644,682 |

| Total | 47,212,207 |

Lincroft[edit]

Moorestown Platform[edit]

- 45 nm process

- 140,000,000

- Die size 7.34 mm × 8.89 mm

- Size area 65.2526 mm²

Oak Trail Platform[edit]

Cores[edit]

Bonnell has lived through a number of iterations unlike the mainstream variants which followed a far more ambitious development cycle. Products based on Bonnell can more or less be split into two generations:

- First Generation - initial Bonnell processor models. Those relied on a number of external chipset chips for the I/O, graphics, and various other system features.

- Second Generation - considerably higher integration was introduced. The original CPU was not incorporated along with many of its peripheral on a single chip to create a System on a Chip.

First generation[edit]

First generation of Bonnell-based microprocessors introduced 2 cores: Silverthorne for ultra-mobile PCs and mobile Internet devices (MIDs) and Diamondville for ultra cheap notebooks and desktops.

- Silverthorne was the codename for a series of Mobile Internet Devices (MIDs) introduced in 2008. These processors had 1 core and 2 threads with a FSB operating at 400 MHz-533 MHz. Those models were branded as Atom MIDs and went along with the poulsbo chipset.

- Diamondville was the codename for the series of ultra cheap notebooks and desktops introduced in 2008. Diamondville is very much a soldered-on-motherboard derivative of Silverthorne with faster FSB (operating at 533 MHz - 667 MHz). The dual-core version is a Multi Chip Module (MCM) Silverthorne variant operating on the same FSB.

Second Generation[edit]

First generation of Bonnell-based microprocessors while being low power had to work with the older 90 nm process 945GSE chipset and 82801GBM I/O controller with a TDP of almost 9.5 watts - almost 4 times that of the processor itself. Second generation Bonnell-based microprocessors aimed to address this issue by integrating a memory controller and GPU on-chip. This drastically reduced power consumption and cost.

- Lincroft is the codename for Bonnell-based Silverthorne's successor. Lincroft integrates on-die the graphics and memory controller. Lincroft effectively replaces the original Silverthorne offering 2x reduction in average circuit board size and up to 50x standby power reduction vs Menlow equivalent. Lincroft also introduces a 2x reduction in the overall active power consumption of the system.

Pineview[edit]

- Main article: Pineview

Pineview was the codename for second generate Bonnell-based processors which integrated a memory controller, Direct Media Interface (DMI) link, and the GMA 3150 GPU. Pineview is the successor for Diamondville, targeting the same ultra cheap desktops, nettops and netbooks.

Tunnel Creek[edit]

- Main article: Tunnel Creek

Tunnel Creek was the codename for a series of MPUs for embedded applications.

Stellarton[edit]

- Main article: Stellarton

Stellarton was the codename for a series of MPUs for embedded applications. Stellarton is the Tunnel Creek core packaged with an Altera FPGA.

Sodaville[edit]

- Main article: Sodaville

Sodaville is the codename for a series of consumer electronics system on a chip (e.g. set-top box).

Groveland[edit]

- Main article: Groveland

Groveland is the codename for a series of consumer electronics MPUs (e.g. smart TVs).

All Bonnell Chips[edit]

| List of Bonnell-based Processors | ||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Main processor | Bus | IGP | Features | |||||||||||||||||

| Model | Price | Core | Launched | C | T | Freq | Burst | TDP | SDP | Speed | Rate | Name | Frequency | Package | HT | VT-x | EIST | |||

| 230 | $ 29.00 € 26.10 £ 23.49 ¥ 2,996.57 | Diamondville | 3 June 2008 | 1 | 2 | 1.6 GHz 1,599.99 MHz 1,599,990 kHz | 4,000 mW 4 W 0.00536 hp 0.004 kW | 133.33 MHz 0.133 GHz 133,330 kHz | 533.33 MT/s 0.533 GT/s 533,330 kT/s | FCBGA-437 | ✔ | ✘ | ✘ | |||||||

| 330 | $ 43.00 € 38.70 £ 34.83 ¥ 4,443.19 | Diamondville | 21 September 2008 | 2 | 4 | 1.6 GHz 1,599.99 MHz 1,599,990 kHz | 8,000 mW 8 W 0.0107 hp 0.008 kW | 133.33 MHz 0.133 GHz 133,330 kHz | 533.33 MT/s 0.533 GT/s 533,330 kT/s | FCBGA-437 | ✔ | ✘ | ✘ | |||||||

| N270 | $ 44.00 € 39.60 £ 35.64 ¥ 4,546.52 | Diamondville | 3 June 2008 | 1 | 2 | 1.6 GHz 1,599.99 MHz 1,599,990 kHz | 2,500 mW 2.5 W 0.00335 hp 0.0025 kW | 133.33 MHz 0.133 GHz 133,330 kHz | 533.33 MT/s 0.533 GT/s 533,330 kT/s | FCBGA-437 | ✔ | ✘ | ✔ | |||||||

| N280 | Diamondville | 7 February 2009 | 1 | 2 | 1.667 GHz 1,666.66 MHz 1,666,660 kHz | 2,500 mW 2.5 W 0.00335 hp 0.0025 kW | 166.66 MHz 0.167 GHz 166,660 kHz | 666.66 MT/s 0.667 GT/s 666,660 kT/s | FCBGA-437 | ✔ | ✘ | ✔ | ||||||||

| Z500 | $ 45.00 € 40.50 £ 36.45 ¥ 4,649.85 | Silverthorne | 2 April 2008 | 1 | 2 | 0.8 GHz 800 MHz 800,000 kHz | 650 mW 0.65 W 8.7165e-4 hp 6.5e-4 kW | 960 mW 0.96 W 0.00129 hp 9.6e-4 kW | 100 MHz 0.1 GHz 100,000 kHz | 400 MT/s 0.4 GT/s 400,000 kT/s | FCBGA-441 | ✔ | ✘ | ✔ | ||||||

| Z510 | $ 45.00 € 40.50 £ 36.45 ¥ 4,649.85 | Silverthorne | 2 April 2008 | 1 | 1 | 1.1 GHz 1,100 MHz 1,100,000 kHz | 2,000 mW 2 W 0.00268 hp 0.002 kW | 960 mW 0.96 W 0.00129 hp 9.6e-4 kW | 100 MHz 0.1 GHz 100,000 kHz | 400 MT/s 0.4 GT/s 400,000 kT/s | FCBGA-441 | ✘ | ✘ | ✔ | ||||||

| Z510P | Silverthorne | 2 March 2009 | 1 | 2 | 1.1 GHz 1,100 MHz 1,100,000 kHz | 2,000 mW 2 W 0.00268 hp 0.002 kW | 100 MHz 0.1 GHz 100,000 kHz | 400 MT/s 0.4 GT/s 400,000 kT/s | FCBGA-437 | ✔ | ✘ | ✔ | ||||||||

| Z510PT | Silverthorne | 2 March 2009 | 1 | 2 | 1.1 GHz 1,100 MHz 1,100,000 kHz | 2,000 mW 2 W 0.00268 hp 0.002 kW | 100 MHz 0.1 GHz 100,000 kHz | 400 MT/s 0.4 GT/s 400,000 kT/s | FCBGA-437 | ✔ | ✘ | ✔ | ||||||||

| Z515 | Silverthorne | 8 April 2009 | 1 | 2 | 1.2 GHz 1,200 MHz 1,200,000 kHz | 650 mW 0.65 W 8.7165e-4 hp 6.5e-4 kW | 100 MHz 0.1 GHz 100,000 kHz | 400 MT/s 0.4 GT/s 400,000 kT/s | FCBGA-441 | ✔ | ✘ | ✔ | ||||||||

| Z520 | $ 65.00 € 58.50 £ 52.65 ¥ 6,716.45 | Silverthorne | 2 April 2008 | 1 | 2 | 1.333 GHz 1,333.33 MHz 1,333,330 kHz | 2,000 mW 2 W 0.00268 hp 0.002 kW | 960 mW 0.96 W 0.00129 hp 9.6e-4 kW | 133.33 MHz 0.133 GHz 133,330 kHz | 533.33 MT/s 0.533 GT/s 533,330 kT/s | FCBGA-441 | ✔ | ✔ | ✔ | ||||||

| Z520PT | Silverthorne | 2 March 2009 | 1 | 2 | 1.333 GHz 1,333.33 MHz 1,333,330 kHz | 2,000 mW 2 W 0.00268 hp 0.002 kW | 133.33 MHz 0.133 GHz 133,330 kHz | 533.33 MT/s 0.533 GT/s 533,330 kT/s | FCBGA-437 | ✔ | ✘ | ✔ | ||||||||

| Z530 | $ 95.00 € 85.50 £ 76.95 ¥ 9,816.35 | Silverthorne | 2 April 2008 | 1 | 2 | 1.6 GHz 1,599.99 MHz 1,599,990 kHz | 2,200 mW 2.2 W 0.00295 hp 0.0022 kW | 133.33 MHz 0.133 GHz 133,330 kHz | 533.33 MT/s 0.533 GT/s 533,330 kT/s | FCBGA-441 | ✔ | ✔ | ✔ | |||||||

| Z530P | Silverthorne | 2 March 2009 | 1 | 2 | 1.6 GHz 1,599.99 MHz 1,599,990 kHz | 2,000 mW 2 W 0.00268 hp 0.002 kW | 133.33 MHz 0.133 GHz 133,330 kHz | 533.33 MT/s 0.533 GT/s 533,330 kT/s | FCBGA-437 | ✔ | ✔ | ✔ | ||||||||

| Z540 | $ 160.00 € 144.00 £ 129.60 ¥ 16,532.80 | Silverthorne | 2 April 2008 | 1 | 2 | 1.867 GHz 1,866.66 MHz 1,866,660 kHz | 2,400 mW 2.4 W 0.00322 hp 0.0024 kW | 960 mW 0.96 W 0.00129 hp 9.6e-4 kW | 133.33 MHz 0.133 GHz 133,330 kHz | 533.33 MT/s 0.533 GT/s 533,330 kT/s | FCBGA-441 | ✔ | ✔ | ✔ | ||||||

| Z550 | Silverthorne | 8 April 2009 | 1 | 2 | 2 GHz 1,999.99 MHz 1,999,990 kHz | 2,400 mW 2.4 W 0.00322 hp 0.0024 kW | 133.33 MHz 0.133 GHz 133,330 kHz | 533.33 MT/s 0.533 GT/s 533,330 kT/s | FCBGA-441 | ✔ | ✔ | ✔ | ||||||||

| Z560 | Silverthorne | June 2010 | 1 | 2 | 2.133 GHz 2,133.33 MHz 2,133,330 kHz | 2,500 mW 2.5 W 0.00335 hp 0.0025 kW | 133.33 MHz 0.133 GHz 133,330 kHz | 533.33 MT/s 0.533 GT/s 533,330 kT/s | FCBGA-441 | ✔ | ✔ | ✔ | ||||||||

| Z600 | Lincroft | 4 May 2010 | 1 | 2 | 0.8 GHz 800 MHz 800,000 kHz | 1.2 GHz 1,200 MHz 1,200,000 kHz | 1,300 mW 1.3 W 0.00174 hp 0.0013 kW | 100 MHz 0.1 GHz 100,000 kHz | 400 MT/s 0.4 GT/s 400,000 kT/s | PowerVR SGX535 | 200 MHz 0.2 GHz 200,000 KHz | FCBGA-518 | ✔ | ✘ | ✔ | |||||

| Z605 | Lincroft | 4 May 2010 | 1 | 2 | 1 GHz 1,000 MHz 1,000,000 kHz | 2,200 mW 2.2 W 0.00295 hp 0.0022 kW | 100 MHz 0.1 GHz 100,000 kHz | 400 MT/s 0.4 GT/s 400,000 kT/s | PowerVR SGX535 | 400 MHz 0.4 GHz 400,000 KHz | FCBGA-518 | ✔ | ✘ | ✔ | ||||||

| Z610 | Lincroft | 4 May 2010 | 1 | 2 | 0.8 GHz 800 MHz 800,000 kHz | 1.2 GHz 1,200 MHz 1,200,000 kHz | 1,300 mW 1.3 W 0.00174 hp 0.0013 kW | 100 MHz 0.1 GHz 100,000 kHz | 400 MT/s 0.4 GT/s 400,000 kT/s | PowerVR SGX535 | 400 MHz 0.4 GHz 400,000 KHz | FCBGA-518 | ✔ | ✘ | ✔ | |||||

| Z612 | Lincroft | 4 May 2010 | 1 | 2 | 0.9 GHz 900 MHz 900,000 kHz | 1.5 GHz 1,500 MHz 1,500,000 kHz | 1,300 mW 1.3 W 0.00174 hp 0.0013 kW | 100 MHz 0.1 GHz 100,000 kHz | 400 MT/s 0.4 GT/s 400,000 kT/s | PowerVR SGX535 | 400 MHz 0.4 GHz 400,000 KHz | FCBGA-518 | ✔ | ✘ | ✔ | |||||

| Z615 | Lincroft | 4 May 2010 | 1 | 2 | 1.2 GHz 1,200 MHz 1,200,000 kHz | 1.6 GHz 1,600 MHz 1,600,000 kHz | 2,200 mW 2.2 W 0.00295 hp 0.0022 kW | 100 MHz 0.1 GHz 100,000 kHz | 400 MT/s 0.4 GT/s 400,000 kT/s | PowerVR SGX535 | 400 MHz 0.4 GHz 400,000 KHz | FCBGA-518 | ✔ | ✘ | ✔ | |||||

| Z620 | Lincroft | 4 May 2010 | 1 | 2 | 0.9 GHz 900 MHz 900,000 kHz | 1.6 GHz 1,600 MHz 1,600,000 kHz | 1,300 mW 1.3 W 0.00174 hp 0.0013 kW | 100 MHz 0.1 GHz 100,000 kHz | 400 MT/s 0.4 GT/s 400,000 kT/s | PowerVR SGX535 | 400 MHz 0.4 GHz 400,000 KHz | FCBGA-518 | ✔ | ✘ | ✔ | |||||

| Z625 | Lincroft | 4 May 2010 | 1 | 2 | 1.5 GHz 1,500 MHz 1,500,000 kHz | 1.9 GHz 1,900 MHz 1,900,000 kHz | 2,200 mW 2.2 W 0.00295 hp 0.0022 kW | 100 MHz 0.1 GHz 100,000 kHz | 400 MT/s 0.4 GT/s 400,000 kT/s | PowerVR SGX535 | 400 MHz 0.4 GHz 400,000 KHz | FCBGA-518 | ✔ | ✘ | ✔ | |||||

| Z650 | Lincroft | 11 April 2011 | 1 | 2 | 1.2 GHz 1,200 MHz 1,200,000 kHz | 3,000 mW 3 W 0.00402 hp 0.003 kW | 100 MHz 0.1 GHz 100,000 kHz | 400 MT/s 0.4 GT/s 400,000 kT/s | PowerVR SGX535 | 400 MHz 0.4 GHz 400,000 KHz | FCBGA-518 | ✔ | ✘ | ✔ | ||||||

| Z670 | $ 75.00 € 67.50 £ 60.75 ¥ 7,749.75 | Lincroft | 11 April 2011 | 1 | 2 | 1.5 GHz 1,500 MHz 1,500,000 kHz | 3,000 mW 3 W 0.00402 hp 0.003 kW | 100 MHz 0.1 GHz 100,000 kHz | 400 MT/s 0.4 GT/s 400,000 kT/s | PowerVR SGX535 | 400 MHz 0.4 GHz 400,000 KHz | FCBGA-518 | ✔ | ✘ | ✔ | |||||

| Count: 25 | ||||||||||||||||||||

Documents[edit]

- Menlow Platform presentation

- Nettops 2008 platform

Artwork[edit]

Silverthorne die on a Tukwila (Itanium) wafer comparison

References[edit]

- Some information was obtained directly from Intel

- Gerosa, Gianfranco, et al. "A sub-2 W low power IA processor for mobile internet devices in 45 nm high-k metal gate CMOS." IEEE Journal of Solid-State Circuits 44.1 (2009): 73-82.

- Gerosa, Gianfranco, et al. "A sub-1W to 2W low-power IA processor for mobile internet devices and ultra-mobile PCs in 45nm hi-κ metal gate CMOS." Solid-State Circuits Conference, 2008. ISSCC 2008. Digest of Technical Papers. IEEE International. IEEE, 2008.

- Taufique, Mohammed H., et al. "A 512-KB level-2 cache design in 45-nm for low power IA processor silverthorne." Custom Integrated Circuits Conference, 2008. CICC 2008. IEEE. IEEE, 2008.

- Wang, Perry H., et al. "Intel® atom™ processor core made FPGA-synthesizable." Proceedings of the ACM/SIGDA international symposium on Field programmable gate arrays. ACM, 2009.

- Corporation, Intel. "Intel 64 and IA-32 architectures optimization reference manual." (2009).

- Beavers, Brad. "The story behind the Intel Atom processor success." IEEE Design & Test of Computers 26.2 (2009).

See also[edit]

- Marvell's Sheeva PJ1

- ARM's ARM11

| codename | Bonnell + |

| core count | 1 + and 2 + |

| designer | Intel + |

| first launched | March 2, 2008 + |

| full page name | intel/microarchitectures/bonnell + |

| instance of | microarchitecture + |

| instruction set architecture | x86-64 + |

| manufacturer | Intel + |

| microarchitecture type | CPU + |

| name | Bonnell + |

| phase-out | 2011 + |

| pipeline stages (max) | 19 + |

| pipeline stages (min) | 16 + |

| process | 45 nm (0.045 μm, 4.5e-5 mm) + |