From WikiChip

Difference between revisions of "amd/packages/ft1"

(Created page with "{{amd title|Package FT1}} {{package |name=FT1 |designer=AMD |market=Mobile |first launched=January 4, 2011 |microarch=Bobcat |tdp=18 W |package name=FT1 |package type=Organic...") |

(Corrected pitch, added more features.) |

||

| Line 12: | Line 12: | ||

|package dimension=19.0 mm | |package dimension=19.0 mm | ||

|package dimension 2=19.0 mm | |package dimension 2=19.0 mm | ||

| − | |package pitch=0.8- | + | |package pitch=0.8-1.0 mm |

}} | }} | ||

| − | '''FT1''' was a BGA-413 package for low power [[AMD]] microprocessors with integrated | + | '''FT1''' was a BGA-413 package for low power [[AMD]] microprocessors with integrated graphics targeting the thin client, embedded and tablet market, the successor to the {{\\|ASB2}} package. Its counterparts for the mainstream mobile and desktop markets are {{\\|Socket FS1}} and {{\\|Socket FM1}}, respectively. FT1 was superseded by the {{\\|FT3}} package. |

| − | graphics targeting the client, embedded and tablet market, the successor to the {{\\|ASB2}} package. | + | |

| − | Its counterparts for the mainstream mobile and desktop markets are | + | Package FT1 was used in AMD's "Brazos" platform for ultrathin notebooks. All processors in the FT1 package are members of AMD's Family 14h with CPU cores based on the {{amd|Bobcat|l=arch}} microarchitecture, and were manufactured on a 40 nm SOI process. |

| − | {{\\|Socket FS1}} and {{\\|Socket FM1}}, respectively. FT1 was superseded by the {{\\|FT3}} package. | ||

| − | |||

| − | |||

=== Features === | === Features === | ||

| − | * 413-pin lidless micro ball grid array package, 0.8- | + | * 413-pin lidless micro ball grid array package, 0.8-1.0 mm multi-pitch, 19 × 19 mm, organic substrate |

| − | + | ||

| − | * 64 bit DDR3 SDRAM interface up to 667 MHz, PC3-10600 (DDR3-1333), 10.7 | + | * 64 bit DDR3 SDRAM interface up to 667 MHz, PC3-10600 (DDR3-1333), 10.7 GB/s |

| + | ** Up to 2 UDIMMs or SODIMMs, no ECC support | ||

| + | |||

| + | * PCIe Gen 1.0 and 2.0 (5 GT/s) | ||

| + | ** Configurable x4 General Purpose Ports (4x1, 2x2, 1x2 + 2x1, 1x4) | ||

| + | ** x4 Unified Media Interface to FCH | ||

| + | |||

| + | * Two independent display controllers | ||

| + | ** Up to 2 × DisplayPort/eDP 1.1a up to 2560 × 1600 at 60 Hz, 30 bpp | ||

| + | ** 2 × Single link DVI up to 1920 × 1200 at 60 Hz, 24 bpp | ||

| + | ** 1 × Single link LVDS up to 1440 × 900 or 1400 × 1050 at 60 Hz, 18 bpp | ||

| + | ** 1 × HDMI up to 1920 × 1080 at 60 Hz, 36 bpp | ||

| + | ** 1 × VGA/DAC | ||

| + | ** 1 × DVO | ||

== Chipsets == | == Chipsets == | ||

| − | * AMD A50M | + | * AMD FCH A50M/A55E, codename "Hudson" |

== Processors using package FT1 == | == Processors using package FT1 == | ||

| Line 79: | Line 89: | ||

:[[File:BGA-413 pn.svg|800px]] | :[[File:BGA-413 pn.svg|800px]] | ||

| − | BGA-413 package | + | BGA-413 package ball numbers. |

== Pin Map == | == Pin Map == | ||

| Line 213: | Line 223: | ||

== References == | == References == | ||

* "FT1 Processor Functional Data Sheet", AMD Publ. #44444, Rev. 2.05, November 2010 | * "FT1 Processor Functional Data Sheet", AMD Publ. #44444, Rev. 2.05, November 2010 | ||

| − | * "BIOS and Kernel Developer’s Guide (BKDG) for AMD Family 14h Models 00h-0Fh Processors", AMD Publ. 43170, Rev. 3.13, February 17, 2012 | + | * "BIOS and Kernel Developer’s Guide (BKDG) for AMD Family 14h Models 00h-0Fh Processors", AMD Publ. #43170, Rev. 3.13, February 17, 2012 |

| − | * "Revision Guide for AMD Family 14h Models 00h-0Fh Processors", AMD Publ. #47534, Rev. 3.18, February 2013 | + | * "Revision Guide for AMD Family 14h Models 00h-0Fh Processors", AMD Publ. #47534, Rev. 3.18, February 26, 2013 |

== See also == | == See also == | ||

| − | * {{\\|ASB2}} | + | * {{\\|ASB2|Package ASB2}} |

| − | * {{\\|FT3}} | + | * {{\\|FT3|Package FT3}} |

* {{\\|Socket FS1}} | * {{\\|Socket FS1}} | ||

* {{\\|Socket FM1}} | * {{\\|Socket FM1}} | ||

[[Category:amd]] | [[Category:amd]] | ||

Revision as of 10:12, 5 September 2020

| Edit Values | |

| FT1 | |

| General Info | |

| Designer | AMD |

| Introduction | January 4, 2011 (launched) |

| Market | Mobile |

| Microarchitecture | Bobcat |

| TDP | 18 W 18,000 mW 0.0241 hp 0.018 kW |

| Package | |

| Name | FT1 |

| Type | Organic Micro Ball Grid Array |

| Contacts | 413 |

| Dimension | 19.0 mm 1.9 cm × 19.0 mm0.748 in 1.9 cm 0.748 in |

| Pitch | 0.8-1.0 mm "-1.0mm" is not declared as a valid unit of measurement for this property. |

FT1 was a BGA-413 package for low power AMD microprocessors with integrated graphics targeting the thin client, embedded and tablet market, the successor to the ASB2 package. Its counterparts for the mainstream mobile and desktop markets are Socket FS1 and Socket FM1, respectively. FT1 was superseded by the FT3 package.

Package FT1 was used in AMD's "Brazos" platform for ultrathin notebooks. All processors in the FT1 package are members of AMD's Family 14h with CPU cores based on the Bobcat microarchitecture, and were manufactured on a 40 nm SOI process.

Contents

Features

- 413-pin lidless micro ball grid array package, 0.8-1.0 mm multi-pitch, 19 × 19 mm, organic substrate

- 64 bit DDR3 SDRAM interface up to 667 MHz, PC3-10600 (DDR3-1333), 10.7 GB/s

- Up to 2 UDIMMs or SODIMMs, no ECC support

- PCIe Gen 1.0 and 2.0 (5 GT/s)

- Configurable x4 General Purpose Ports (4x1, 2x2, 1x2 + 2x1, 1x4)

- x4 Unified Media Interface to FCH

- Two independent display controllers

- Up to 2 × DisplayPort/eDP 1.1a up to 2560 × 1600 at 60 Hz, 30 bpp

- 2 × Single link DVI up to 1920 × 1200 at 60 Hz, 24 bpp

- 1 × Single link LVDS up to 1440 × 900 or 1400 × 1050 at 60 Hz, 18 bpp

- 1 × HDMI up to 1920 × 1080 at 60 Hz, 36 bpp

- 1 × VGA/DAC

- 1 × DVO

Chipsets

- AMD FCH A50M/A55E, codename "Hudson"

Processors using package FT1

- AMD C-Series codename "Ontario"

- AMD E-Series "Zacate"

- AMD G-Series

- AMD Z-Series "Desna"

| List of all FT1-based Processors | |||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Model | Price | Process | Launched | µarch | Family | Core | C | T | Freq | Turbo | TDP | ||||||||

| T16R | 40 nm 0.04 μm 4.0e-5 mm | June 2012 | Bobcat | Embedded G-Series | eBrazos | 1 | 1 | 0.615 GHz 615 MHz 615,000 kHz | 4.5 W 4,500 mW 0.00603 hp 0.0045 kW | ||||||||||

| T24L | 40 nm 0.04 μm 4.0e-5 mm | 1 March 2011 | Bobcat | Embedded G-Series | eBrazos | 1 | 1 | 1 GHz 1,000 MHz 1,000,000 kHz | 5 W 5,000 mW 0.00671 hp 0.005 kW | ||||||||||

| T30L | 40 nm 0.04 μm 4.0e-5 mm | 1 March 2011 | Bobcat | Embedded G-Series | eBrazos | 1 | 1 | 1.4 GHz 1,400 MHz 1,400,000 kHz | 18 W 18,000 mW 0.0241 hp 0.018 kW | ||||||||||

| T40E | 40 nm 0.04 μm 4.0e-5 mm | 23 May 2011 | Bobcat | Embedded G-Series | eBrazos | 2 | 2 | 1 GHz 1,000 MHz 1,000,000 kHz | 6.4 W 6,400 mW 0.00858 hp 0.0064 kW | ||||||||||

| T40N | 40 nm 0.04 μm 4.0e-5 mm | 19 January 2011 | Bobcat | Embedded G-Series | eBrazos | 2 | 2 | 1 GHz 1,000 MHz 1,000,000 kHz | 18 W 18,000 mW 0.0241 hp 0.018 kW | ||||||||||

| T40R | 40 nm 0.04 μm 4.0e-5 mm | 23 May 2011 | Bobcat | Embedded G-Series | eBrazos | 1 | 1 | 1 GHz 1,000 MHz 1,000,000 kHz | 5.5 W 5,500 mW 0.00738 hp 0.0055 kW | ||||||||||

| T44R | 40 nm 0.04 μm 4.0e-5 mm | 19 January 2011 | Bobcat | Embedded G-Series | eBrazos | 1 | 1 | 1.2 GHz 1,200 MHz 1,200,000 kHz | 9 W 9,000 mW 0.0121 hp 0.009 kW | ||||||||||

| T48E | 40 nm 0.04 μm 4.0e-5 mm | 2012 | Bobcat | Embedded G-Series | eBrazos | 2 | 2 | 1.4 GHz 1,400 MHz 1,400,000 kHz | 18 W 18,000 mW 0.0241 hp 0.018 kW | ||||||||||

| T48L | 40 nm 0.04 μm 4.0e-5 mm | 1 March 2011 | Bobcat | Embedded G-Series | eBrazos | 2 | 2 | 1.4 GHz 1,400 MHz 1,400,000 kHz | 18 W 18,000 mW 0.0241 hp 0.018 kW | ||||||||||

| T48N | 40 nm 0.04 μm 4.0e-5 mm | 19 January 2011 | Bobcat | Embedded G-Series | eBrazos | 2 | 2 | 1.4 GHz 1,400 MHz 1,400,000 kHz | 18 W 18,000 mW 0.0241 hp 0.018 kW | ||||||||||

| T52R | 40 nm 0.04 μm 4.0e-5 mm | 19 January 2011 | Bobcat | Embedded G-Series | eBrazos | 1 | 1 | 1.5 GHz 1,500 MHz 1,500,000 kHz | 18 W 18,000 mW 0.0241 hp 0.018 kW | ||||||||||

| T56E | 40 nm 0.04 μm 4.0e-5 mm | 2012 | Bobcat | Embedded G-Series | eBrazos | 2 | 2 | 1.65 GHz 1,650 MHz 1,650,000 kHz | 18 W 18,000 mW 0.0241 hp 0.018 kW | ||||||||||

| T56N | 40 nm 0.04 μm 4.0e-5 mm | 19 January 2011 | Bobcat | Embedded G-Series | eBrazos | 2 | 2 | 1.65 GHz 1,650 MHz 1,650,000 kHz | 18 W 18,000 mW 0.0241 hp 0.018 kW | ||||||||||

| Count: 13 | |||||||||||||||||||

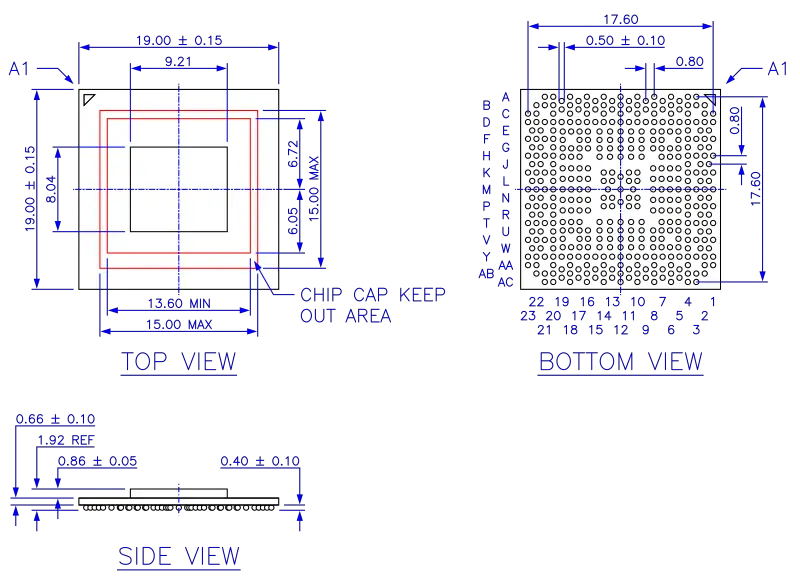

Package Diagram

All dimensions in millimeters.

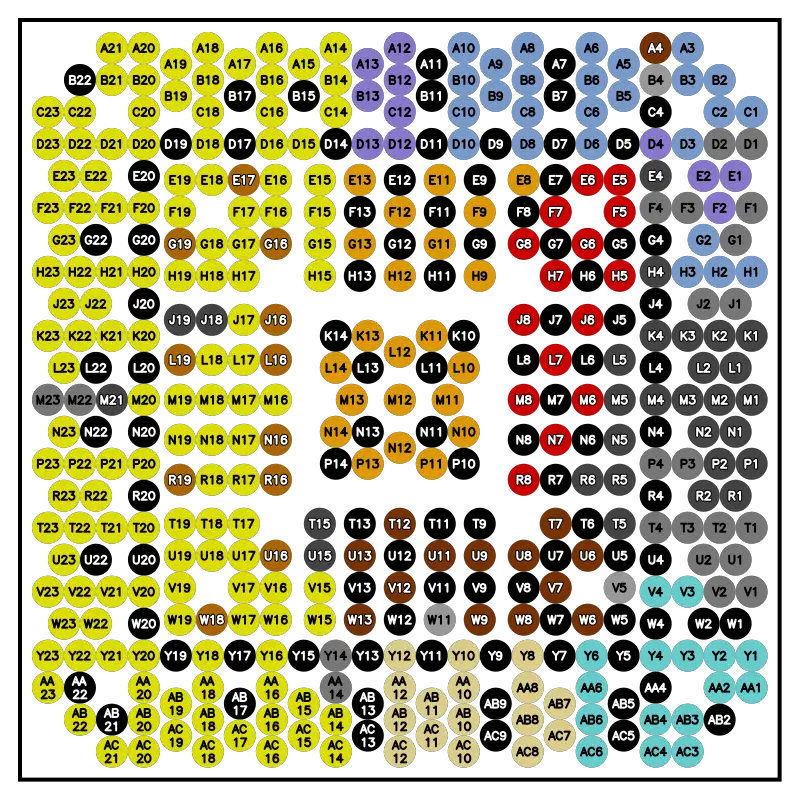

BGA-413 package ball numbers.

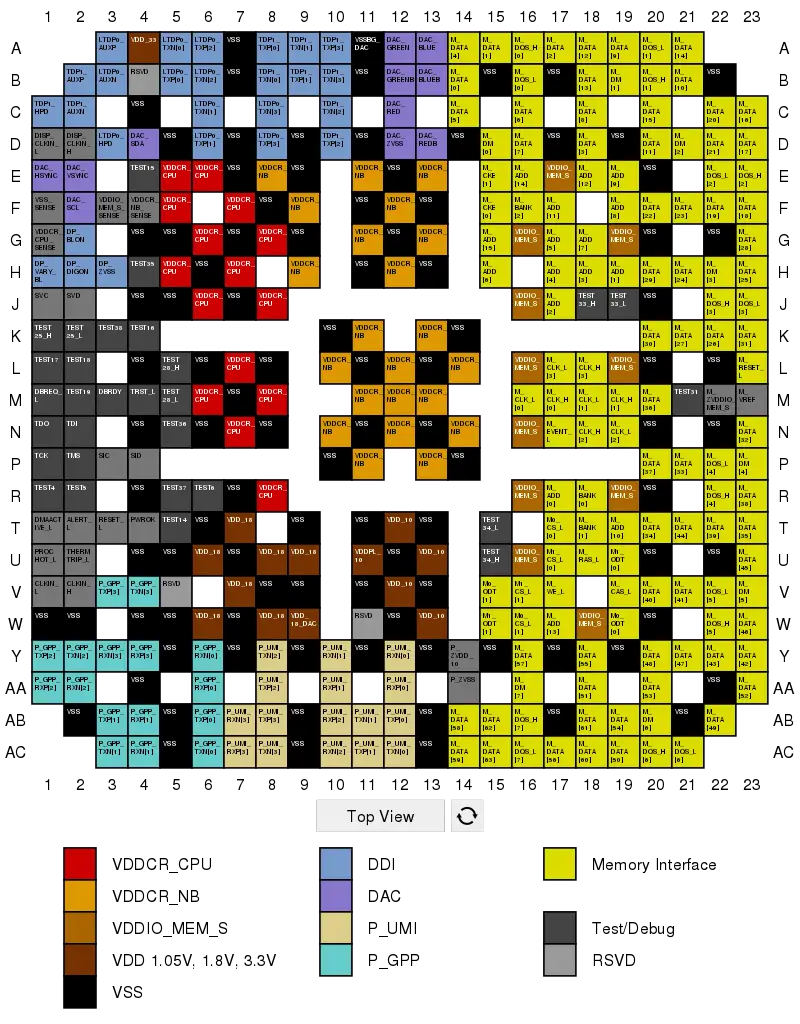

Pin Map

Pin Description

| Signal | Description |

|---|---|

| ALERT_L | Programmable pin that can indicate different events, including a SB-TSI interrupt |

| CLKIN_H/L | 100 MHz PLL Differential Reference Clock |

| DAC_BLUE, DAC_BLUEB | Blue for Video Monitor Output |

| DAC_GREEN, DAC_GREENB | Green for Video Monitor Output |

| DAC_HSYNC, DAC_VSYNC | Display Horizontal, Vertical Sync |

| DAC_RED, DAC_REDB | Red for Video Monitor Output |

| DAC_SCL, DAC_SDA | I2C Clock, Data for Display (to video monitor) |

| DAC_ZVSS | Compensation Resistor to DAC Ground Pin |

| DBREQ_L/DBRDY | Debug Request/Ready |

| DISP_CLKIN_H/L | 100 MHz Display Controller Reference Clock |

| DMAACTIVE_L | Indicated System DMA Activity |

| DP_BLON | Display Panel Backlight Enable |

| DP_DIGON | Display Panel Power Enable |

| DP_VARY_BL | Display Backlight Brightness Control |

| DP_ZVSS | Compensation Resistor to VSS |

| LTDP0/TDP1_AUXP/N | DisplayPort Auxiliary Channel |

| LTDP0/TDP1_HPD | DisplayPort Hot Plug Detect |

| LTDP0/TDP1_TXP/N[3:0] | DisplayPort Differential Transmitter |

| M0_CS_L[1:0], M1_CS_L[1:0] | DRAM Chip Selects |

| M0_ODT[1:0], M1_ODT[1:0] | DRAM Enable Pin for On Die Termination |

| M_ADD[15:0] | DRAM Column/Row Address |

| M_BANK[2:0] | DRAM Bank Address |

| M_CAS_L | DRAM Column Address Strobe |

| M_CKE[1:0] | DRAM Clock Enable |

| M_CLK_H/L[3:0] | DRAM Differential Clock |

| M_DATA[63:0] | DRAM Interface Data Bus |

| M_DM[7:0] | DRAM Data Mask |

| M_DQS_H/L[7:0] | DRAM Differential Data Strobe |

| M_EVENT_L | DRAM Thermal Event |

| M_RAS_L | DRAM Row Address Strobe |

| M_RESET_L | DRAM Reset Pin for Suspend-to-RAM Power Management Mode |

| M_VREF | Memory Interface Voltage Reference |

| M_WE_L | DRAM Write Enable |

| M_ZVDDIO_MEM_S | Compensation Resistor to VDDIO |

| PROCHOT_L | Processor in HTC-active state input/output |

| PWROK | Voltages and CLKIN have reached specified operation |

| P_GPP_TX/RXP/N[3:0] | General Purpose External PCIe Transmit/Receive Data Differential Pairs |

| P_UMI_TX/RXP/N[3:0] | Unified Media Interface Transmit/Receive Data Differential Pairs |

| P_ZVDD_10 | Compensation Resistor to P_VDD_10 Power Supply |

| P_ZVSS | Compensation Resistor to VSS |

| RESET_L | Processor Reset |

| RSVD | Reserved |

| SIC, SID | Sideband Temperature Sensor Interface Clock, Data |

| SVC, SVD | Serial VID Interface Clock, Data |

| TCK, TDI, TDO, TMS, TRST_L | JTAG interface |

| TEST* | Test signal |

| THERMTRIP_L | Thermal Sensor Trip output |

| VDDCR_CPU_SENSE | VDDCR_CPU Voltage Monitor Pin |

| VDDCR_CPU | Core Power Supply |

| VDDCR_NB_SENSE | VDDCR_NB Voltage Monitor Pin |

| VDDCR_NB | Northbridge Power Supply |

| VDDIO_MEM_S_SENSE | VDDIO_MEM_S Voltage Monitor Pin |

| VDDIO_MEM_S | DDR SDRAM I/O Ring Power Supply |

| VDDPL_10 | 1.05 V Supply Pin for System PLL |

| VDD_10 | 1.05 V Supply Pins |

| VDD_18_DAC | 1.8 V Supply Pin for DAC |

| VDD_18 | 1.8 V Supply Pins |

| VDD_33 | 3.3 V Supply Pin |

| VSSBG_DAC | DAC Ground |

| VSS_SENSE | VSS Voltage Monitor Pin |

| VSS | Ground |

References

- "FT1 Processor Functional Data Sheet", AMD Publ. #44444, Rev. 2.05, November 2010

- "BIOS and Kernel Developer’s Guide (BKDG) for AMD Family 14h Models 00h-0Fh Processors", AMD Publ. #43170, Rev. 3.13, February 17, 2012

- "Revision Guide for AMD Family 14h Models 00h-0Fh Processors", AMD Publ. #47534, Rev. 3.18, February 26, 2013

See also

Facts about "Package FT1 - AMD"

| designer | AMD + |

| first launched | January 4, 2011 + |

| instance of | package + |

| market segment | Mobile + |

| microarchitecture | Bobcat + |

| name | FT1 + |

| package | FT1 + |

| package contacts | 413 + |

| package length | 19 mm (1.9 cm, 0.748 in) + |

| package type | Organic Micro Ball Grid Array + |

| package width | 19 mm (1.9 cm, 0.748 in) + |

| tdp | 18 W (18,000 mW, 0.0241 hp, 0.018 kW) + |