m (Bot: moving all {{mpu}} to {{chip}}) |

|||

| Line 58: | Line 58: | ||

|package 1 height=5.1 mm | |package 1 height=5.1 mm | ||

}} | }} | ||

| − | The '''Intel 4004''' was released by [[Intel Corporation]] in [[1971]] and was the first commercially available [[microprocessor]]. The 4004 was a [[4-bit architecture|4-bit CPU]], designed for use in the [[Busicom]] 141-PF printing calculator<ref>[http://www.intel.com/content/www/us/en/history/museum-story-of-intel-4004.html The Story of the Intel® 4004]</ref> | + | The '''Intel 4004''' was released by [[Intel Corporation]] in [[1971]] and was the first commercially available [[microprocessor]]. The 4004 was a [[4-bit architecture|4-bit CPU]], designed for use in the [[Busicom]] 141-PF printing calculator.<ref>[http://www.intel.com/content/www/us/en/history/museum-story-of-intel-4004.html The Story of the Intel® 4004]</ref> The chip, which is clocked at 740 KHz, employs a 10µm<ref>[http://www.intel.com/Assets/PDF/DataSheet/4004_datasheet.pdf 4004 Datasheet]</ref> process silicon-gate, capable of executing 92,000 instructions per second. The chip was capable of accessing 4KB of [[program memory]] and 640 bytes of RAM. The 4004 was part of the [[Intel MCS-4]] system. |

The microprocessor had a limited architecture, such as: only a 3-levels deep [[stack]], a complex memory access scheme, and no [[interrupt]] support. In [[1974]] Intel released an enhanced version of the chip called the [[Intel 4040|4040]]. | The microprocessor had a limited architecture, such as: only a 3-levels deep [[stack]], a complex memory access scheme, and no [[interrupt]] support. In [[1974]] Intel released an enhanced version of the chip called the [[Intel 4040|4040]]. | ||

| + | |||

| + | It began as the "Busicom Project", a joint development by America's Intel and Japan's [[Busicom]],<ref name="shima"/><ref name="ieee"/> with initial design concepts by Busicom's [[wikipedia:Masatoshi Shima|Masatoshi Shima]] and [[Sharp Corporation|Sharp]]'s [[wikipedia:Tadashi Sasaki (engineer)|Tadashi Sasaki]] in 1968,<ref name=tout1/><ref name="sasaki"/><ref name="shima"/> before being designed by Intel's Marcian Hoff and Federico Faggin and Busicom's Shima from 1969 to April 1970;<ref name="shima"/><ref name="ieee"/><ref name="faggin"/> it was completed under Faggin's leadership, with Shima's assistance, in January 1971. The first commercial sale of the fully operational 4004 occurred in March 1971 to Busicom, for the [[Busicom|Busicom 141-PF]] calculator, for which it was originally designed and built as a custom chip.<ref name="faggin">Faggin, F. (1992). "The Birth of the Microprocessor". ''Byte'', pp. 145–150, March 1992.</ref> | ||

== Variations == | == Variations == | ||

| Line 132: | Line 134: | ||

== Designers == | == Designers == | ||

| − | Lead designers for the 4004 | + | Lead designers for the 4004: |

| + | |||

| + | * [[designer::Masatoshi Shima]] | ||

| + | * [[designer::Tadashi Sasaki]] | ||

* [[designer::Ted Hoff]] | * [[designer::Ted Hoff]] | ||

* [[designer::Federico Faggin]] | * [[designer::Federico Faggin]] | ||

* [[designer::Stan Mazor]] | * [[designer::Stan Mazor]] | ||

| − | |||

== Die Shot == | == Die Shot == | ||

| Line 144: | Line 148: | ||

* 12 mm² die | * 12 mm² die | ||

[[File:4004 die shot.png]] | [[File:4004 die shot.png]] | ||

| + | |||

| + | == History and production == | ||

| + | [[File:KL National INS4004.jpg|thumb|National Semiconductor was a second source manufacturer of the 4004, under their part number INS4004.<ref>http://www.cpu-world.com/CPUs/4004/index.html Intel 4004 microprocessor family, retrieved 2011 Dec 14</ref>]] | ||

| + | |||

| + | ===1968=== | ||

| + | The origins of the 4004 date back to the the "Busicom Project",<ref name="ieee">Federico Faggin, [http://ieeexplore.ieee.org/stamp/stamp.jsp?arnumber=4776530 The Making of the First Microprocessor], ''IEEE Solid-State Circuits Magazine'', Winter 2009, IEEE Xplore</ref> which began at Japanese calculator company [[Busicom]] in April 1968, when engineer [[wikipedia:Masatoshi Shima|Masatoshi Shima]] was tasked with designing a special-purpose LSI chipset, along with his supervisor Tadashi Tanba, for use in the [[Busicom|Busicom 141-PF]] desktop calculator with integrated printer.<ref name=tout1/><ref name="shima">[https://web-beta.archive.org/web/20081219113410/http://www.ieee.org/portal/cms_docs_iportals/iportals/aboutus/history_center/oral_history/pdfs/Shima197.pdf Masatoshi Shima], IEEE</ref> His initial design consisted of seven LSI chips, including a three-chip CPU.<ref name="ieee"/> His design included arithmetic units (adders), multiplier units, registers, read-only memory (ROM), and a macro-instruction set to control a decimal computer system.<ref name=tout1/> Busicom then wanted a general-purpose LSI chipset, for not only desktop calculators, but also other equipment such as an automated teller machine (ATM), cash register and billing machine. Shima thus began work on a general-purpose LSI chipset in late 1968.<ref name="shima"/> | ||

| + | |||

| + | [[Sharp Corporation|Sharp]] engineer [[wikipedia:Tadashi Sasaki (engineer)|Tadashi Sasaki]] was also involved with its development, and conceived of a single-chip CPU in 1968, when he discussed the concept at a brainstorming meeting that was held in Japan. Sasaki attributes the basic invention to break the calculator chipset into four parts with ROM (4001), RAM (4002), shift registers (4003) and CPU (4004) to an unnamed woman, a software engineering researcher from [[wikipedia:Nara Women's University|Nara Women's College]], who was present at the meeting. Sasaki then had his first meeting with Robert Noyce from [[Intel]] in 1968, and presented the woman's four-division chipset concept to Intel and Busicom.<ref name="sasaki">William Aspray (1994-05-25), [http://www.ieeeghn.org/wiki/index.php/Oral-History:Tadashi_Sasaki Oral-History: Tadashi Sasaki], ''Interview #211 for the Center for the History of Electrical Engineering'', The Institute of Electrical and Electronics Engineers, Inc. Accessed 2013-01-02.</ref> | ||

| + | |||

| + | ===1969=== | ||

| + | Busicom approached the American company [[Intel]] for manufacturing help in 1969. Intel, which was more of a memory company back then, had facilities to manufacture the high density [[silicon gate]] [[MOSFET#Metal–oxide–semiconductor structure|MOS]] chip Busicom required.<ref name="shima"/> | ||

| + | |||

| + | Shima went to Intel in June 1969 to present his design proposal. Due to Intel lacking logic engineers to understand the logic schematics or circuit engineers to convert them, Intel asked Shima to simplify the logic.<ref name="shima"/> Intel wanted a single-chip CPU design,<ref name="shima"/> influenced by Sharp's Tadashi Sasaki who presented the concept to Busicom and Intel in 1968.<ref name="sasaki"/> The single-chip microprocessor design was then formulated by Intel's Marcian "Ted" Hoff in 1969,<ref name="ieee"/> simplifying Shima's initial design down to four chips, including a single-chip CPU.<ref name="ieee"/> Hoff, head of Intel's Application Research Department, contributed to the architectural proposal for Busicom. When asked where he got his ideas for the architecture, Hoff related that Plessey, "a British tractor company",<ref>Possibly he had confused the Plessey name with that of Massey Ferguson, makers of agricultural machinery.</ref> had donated a minicomputer to Stanford, and he had "played with it some" while he was there. | ||

| + | |||

| + | Due to Hoff's formulation lacking key details, Shima came up with his own ideas to find solutions for its implementation. Shima was responsible for adding a 10-bit static shift register to make it useful as a printer's buffer and keyboard interface, many improvements in the instruction set, making the RAM organization suitable for a calculator, the memory address information transfer, the key program in an area of performance and program capacity, the functional specification, decimal computer idea, software, desktop calculator logic, real-time I/O control, and data exchange instruction between the accumulator and general purpose register. Hoff and Shima eventually realized the [[4-bit]] microprocessor concept together, with the help of Intel's Stanley Mazor to interpret the ideas of Shima and Hoff.<ref name="shima"/> The specifications of the four chips were developed over a period of a few months in 1969, between an Intel team led by Hoff and a Busicom team led by Shima.<ref name="ieee"/> | ||

| + | |||

| + | Intel made further modifications to the design. Serial memories required more components, and would use 40 pins, a packaging standard different from Intel’s own 16-pin standard, and so it was proposed that an updated design produced with standard 16-pin DIP packaging and reduced instruction set be developed,<ref name=tout1>Nigel Tout, [http://www.vintagecalculators.com/html/busicom_141-pf_and_intel_4004.html The Busicom 141-PF calculator and the Intel 4004 microprocessor], accessed November 15, 2009</ref> using a newly developed dynamic RAM (DRAM) memory chip. This resulted in the 4004 architecture, which is part of a family of chips, including ROM, DRAM, and serial-to-parallel shift register chips. The 4004 was subsequently designed using silicon gate technology and built of approximately 2,300 transistors.<ref name="funfacts">[http://www.intel.com/about/companyinfo/museum/exhibits/4004/facts.htm Intel 4004 Fun Facts], Intel, accessed 2011-07-06</ref> | ||

| + | |||

| + | In late 1969, Shima returned to Japan.<ref name="shima"/> After that, Intel had done no further work on the project until early 1970.<ref name="shima"/><ref name="ieee"/> | ||

| + | |||

| + | ===1970=== | ||

| + | Shima returned to Intel in early 1970, and found that no further work had been done on the 4004 since he left, and that Hoff had moved on to other projects.<ref name="shima"/> Only a week before Shima had returned to Intel,<ref name="shima"/> Federico Faggin had joined Intel and become the project leader.<ref name="ieee"/> After Shima explained the project to Faggin, they worked together to design the 4004.<ref name="shima"/> | ||

| + | |||

| + | Faggin, the sole chip designer among the engineers on the MCS-4 project, was the only one with experience in metal-oxide semiconductor (MOS) random logic and circuit design. He also had the crucial knowledge of the new silicon gate process technology with self-aligned gates, which he had created at [[Fairchild Semiconductor|Fairchild]] in 1968. At Fairchild in 1968, Faggin also designed and manufactured the first commercial IC using SGT, the Fairchild 3708.<ref>[http://www.intel4004.com/papers.htm ''Earliest Published Papers''], retrieved 2012 Jan 16</ref> As soon as he joined the Intel MOS Department, he created a new random logic design methodology based on silicon gate, and contributed many technology and circuit design inventions that enabled their single chip microprocessor to become a reality. His methodology set the design style for all the early Intel microprocessors and later for the Zilog Z80. He also led the MCS-4 project and was responsible for its successful outcome (1970–1971).<ref name="intel4004"/> Shima designed the logic<ref name="shima"/> and the Busicom calculator firmware, and assisted Faggin during the first six months of the implementation. The manager of Intel's MOS Design Department was Leslie L. Vadász.<ref name="intel4004">[http://www.intel4004.com/qa4004.htm The Intel4004], Intel4004.com, accessed 2008-03-15</ref> At the time of the MCS-4 development, Vadasz's attention was completely focused on the mainstream business of semiconductor memories and he left the leadership and the management of the MCS-4 project to Faggin. | ||

| + | |||

| + | Thus, the chief designers of the chip were Faggin who created the design methodology and the silicon-based chip design, Hoff who formulated the architecture before moving on to other projects, and Shima who produced the initial Busicom design and then assisted in the development of the final Intel design.<ref name=tout1/> | ||

| + | |||

| + | ===1971=== | ||

| + | The 4004 was first introduced in Japan, as the microprocessor for the Busicom 141-PF calculator, in March 1971.<ref name="shima"/><ref name=tout1/> In North America, the first public mention of the 4004 was an advertisement in the November 15, 1971 edition of ''Electronic News'',<ref name = "Gilder 1990">George Gilder (1990), [https://books.google.com/books?id=xUxthKiLOvsC&pg=PA107 ''Microcosm: the quantum revolution in economics and technology''], Simon and Schuster, ISBN 978-0-671-70592-3, p. 107: "Intel's first advertisement for the 4004 appeared in the November 15, 1971 issue of ''Electronic News''"</ref> though unconfirmed reports put the date of first delivery as early as March 1971. Packaged in a 16-pin ceramic dual in-line package, the 4004 was the first commercially available computer processor designed and manufactured by [[integrated circuit|chip]] maker [[Intel]], which had previously made [[semiconductor]] memory chips. The 4004 was followed the next year by the first ever [[8-bit]] microprocessor, the 3,500 transistor [[Intel 8008|8008]] (and the [[Intel 4040|4040]], a revised and improved 4004). It was not until the development of the 40-pin [[Intel 8080|8080]] in 1974 that the address and data buses would be separated, giving faster and simpler access to memory. | ||

== References == | == References == | ||

{{reflist}} | {{reflist}} | ||

Revision as of 09:26, 3 July 2019

| Edit Values | |

| 4004 | |

| |

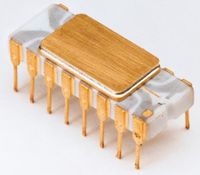

| 4004 in CerDIP | |

| General Info | |

| Designer | Intel |

| Manufacturer | Intel |

| Model Number | 4004 |

| Part Number | C4004, D4004, P4004 |

| Market | Commercial, Industrial |

| Introduction | November 15, 1971 (announced) December, 1971 (launched) |

| End-of-life | 1982 (last order) |

| Shop | Amazon |

| General Specs | |

| Family | MCS-4 |

| Series | MCS |

| Frequency | 500 kHz, 740 kHz |

| Microarchitecture | |

| ISA | 4004 (4004) |

| Microarchitecture | 4004 |

| Chipset | 4001, 4002, 4003 |

| Process | 10 µm |

| Transistors | 2,250 |

| Technology | pMOS |

| Die | 12 mm² 4 mm × 3 mm |

| Word Size | 4 bit |

| Cores | 1 |

| Threads | 1 |

| Max Address Mem | 4 kB |

| Electrical | |

| Power dissipation | 1 W |

| Vcore | 15 V ± 5% |

| Tstorage | -55 °C – 125 °C |

| Tambient | 0 °C – 70 °C |

The Intel 4004 was released by Intel Corporation in 1971 and was the first commercially available microprocessor. The 4004 was a 4-bit CPU, designed for use in the Busicom 141-PF printing calculator.[1] The chip, which is clocked at 740 KHz, employs a 10µm[2] process silicon-gate, capable of executing 92,000 instructions per second. The chip was capable of accessing 4KB of program memory and 640 bytes of RAM. The 4004 was part of the Intel MCS-4 system.

The microprocessor had a limited architecture, such as: only a 3-levels deep stack, a complex memory access scheme, and no interrupt support. In 1974 Intel released an enhanced version of the chip called the 4040.

It began as the "Busicom Project", a joint development by America's Intel and Japan's Busicom,[3][4] with initial design concepts by Busicom's Masatoshi Shima and Sharp's Tadashi Sasaki in 1968,[5][6][3] before being designed by Intel's Marcian Hoff and Federico Faggin and Busicom's Shima from 1969 to April 1970;[3][4][7] it was completed under Faggin's leadership, with Shima's assistance, in January 1971. The first commercial sale of the fully operational 4004 occurred in March 1971 to Busicom, for the Busicom 141-PF calculator, for which it was originally designed and built as a custom chip.[7]

Contents

Variations

Three primary source variations were produced by Intel: C4004, D4004 and the P4004. The Intel C4004 was the first chip to be manufactured; it had the gray traces visible on the white ceramic package itself. The C4004 was produced up until mid 1976, when production for the Intel D4004 began. The D4004 had a plastic, black ceramic package. The Intel P4004 is the plastic packaging version.

A couple secondary sources exists, which has been developed by National Semiconductor and Hitachi since mid-1975. National Semiconductor produced two versions: INS4004J and INS4004D. The INS4004J is a 16-pin black, ceramic DIP, while the INS4004D version is a 16-pin side-brazed, ceramic DIP. The other source was the HD35404 made by Hitachi. A third source was Microsystems International which actually manufactured an enhanced version of the chip since mid 1970 (also introduced in 1971).

| Manufacturer | Model | Package |

|---|---|---|

| Intel | C4004 | 16-pin Ceramic DIP |

| Intel | D4004 | 16-pin Ceramic DIP |

| Intel | P4004 | 16-pin Plastic DIP |

| National Semiconductor | INS4004D | 16-pin Ceramic DIP |

| National Semiconductor | INS4004J | 16-pin side-brazed Ceramic DIP |

| Hitachi | HD35404 | 16-pin DIP |

| Microsystems International | MF7114 | ? |

Pinout

The 4004 has 16 pins that are used for i/o, memory controller, clock phases, power and reset.

| Pin # | Pin Name | Purpose | Explanation |

|---|---|---|---|

| 1 | D0 | Bidirectional data bus pins | Address and data communication to the ROM and RAM occurs on D0-D3. |

| 2 | D1 | ||

| 3 | D2 | ||

| 4 | D3 | ||

| 5 | Vss | Main Supply | |

| 6 | Clock Phase 1 | Clock inputs | |

| 7 | Clock Phase 2 | ||

| 8 | Sync | ROM & RAM Sync | Synchronizes the ROM and RAM by signaling the clock is on the raising edge. |

| 9 | Reset | Reset flag | A logic 1 clears all processor status registers and forces the program counter to jump to address 0x0. The RESET signal must be on for at least 64 clock cycles in order to take effect. |

| 10 | Test | Test logic state | Signal can be tested via the JCN instruction.

|

| 11 | CM-ROM | CM-ROM output | ROM selection signal used to retrieve data from memory. |

| 12 | VDD | VSS -15±5% | |

| 13 | CM-RAM3 | CM-ROM outputs | Bank selection signal for the 4002 RAM chips in the system. |

| 14 | CM-RAM2 | ||

| 15 | CM-RAM1 | ||

| 16 | CM-RAM0 |

Designers

Lead designers for the 4004:

- Masatoshi Shima

- Tadashi Sasaki

- Ted Hoff

- Federico Faggin

- Stan Mazor

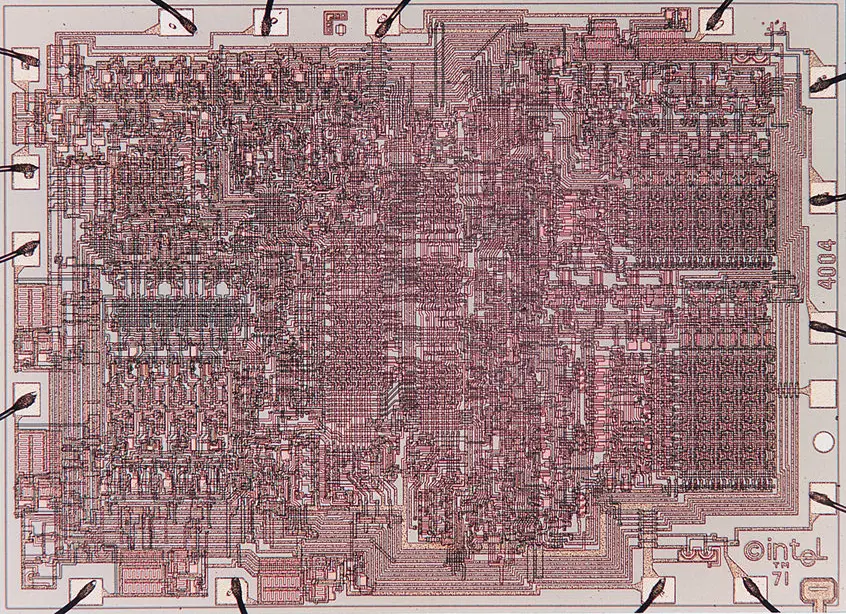

Die Shot

- 10 µm process

- pMOS transistors

- 2,250 transistors

- 12 mm² die

History and production

1968

The origins of the 4004 date back to the the "Busicom Project",[4] which began at Japanese calculator company Busicom in April 1968, when engineer Masatoshi Shima was tasked with designing a special-purpose LSI chipset, along with his supervisor Tadashi Tanba, for use in the Busicom 141-PF desktop calculator with integrated printer.[5][3] His initial design consisted of seven LSI chips, including a three-chip CPU.[4] His design included arithmetic units (adders), multiplier units, registers, read-only memory (ROM), and a macro-instruction set to control a decimal computer system.[5] Busicom then wanted a general-purpose LSI chipset, for not only desktop calculators, but also other equipment such as an automated teller machine (ATM), cash register and billing machine. Shima thus began work on a general-purpose LSI chipset in late 1968.[3]

Sharp engineer Tadashi Sasaki was also involved with its development, and conceived of a single-chip CPU in 1968, when he discussed the concept at a brainstorming meeting that was held in Japan. Sasaki attributes the basic invention to break the calculator chipset into four parts with ROM (4001), RAM (4002), shift registers (4003) and CPU (4004) to an unnamed woman, a software engineering researcher from Nara Women's College, who was present at the meeting. Sasaki then had his first meeting with Robert Noyce from Intel in 1968, and presented the woman's four-division chipset concept to Intel and Busicom.[6]

1969

Busicom approached the American company Intel for manufacturing help in 1969. Intel, which was more of a memory company back then, had facilities to manufacture the high density silicon gate MOS chip Busicom required.[3]

Shima went to Intel in June 1969 to present his design proposal. Due to Intel lacking logic engineers to understand the logic schematics or circuit engineers to convert them, Intel asked Shima to simplify the logic.[3] Intel wanted a single-chip CPU design,[3] influenced by Sharp's Tadashi Sasaki who presented the concept to Busicom and Intel in 1968.[6] The single-chip microprocessor design was then formulated by Intel's Marcian "Ted" Hoff in 1969,[4] simplifying Shima's initial design down to four chips, including a single-chip CPU.[4] Hoff, head of Intel's Application Research Department, contributed to the architectural proposal for Busicom. When asked where he got his ideas for the architecture, Hoff related that Plessey, "a British tractor company",[9] had donated a minicomputer to Stanford, and he had "played with it some" while he was there.

Due to Hoff's formulation lacking key details, Shima came up with his own ideas to find solutions for its implementation. Shima was responsible for adding a 10-bit static shift register to make it useful as a printer's buffer and keyboard interface, many improvements in the instruction set, making the RAM organization suitable for a calculator, the memory address information transfer, the key program in an area of performance and program capacity, the functional specification, decimal computer idea, software, desktop calculator logic, real-time I/O control, and data exchange instruction between the accumulator and general purpose register. Hoff and Shima eventually realized the 4-bit microprocessor concept together, with the help of Intel's Stanley Mazor to interpret the ideas of Shima and Hoff.[3] The specifications of the four chips were developed over a period of a few months in 1969, between an Intel team led by Hoff and a Busicom team led by Shima.[4]

Intel made further modifications to the design. Serial memories required more components, and would use 40 pins, a packaging standard different from Intel’s own 16-pin standard, and so it was proposed that an updated design produced with standard 16-pin DIP packaging and reduced instruction set be developed,[5] using a newly developed dynamic RAM (DRAM) memory chip. This resulted in the 4004 architecture, which is part of a family of chips, including ROM, DRAM, and serial-to-parallel shift register chips. The 4004 was subsequently designed using silicon gate technology and built of approximately 2,300 transistors.[10]

In late 1969, Shima returned to Japan.[3] After that, Intel had done no further work on the project until early 1970.[3][4]

1970

Shima returned to Intel in early 1970, and found that no further work had been done on the 4004 since he left, and that Hoff had moved on to other projects.[3] Only a week before Shima had returned to Intel,[3] Federico Faggin had joined Intel and become the project leader.[4] After Shima explained the project to Faggin, they worked together to design the 4004.[3]

Faggin, the sole chip designer among the engineers on the MCS-4 project, was the only one with experience in metal-oxide semiconductor (MOS) random logic and circuit design. He also had the crucial knowledge of the new silicon gate process technology with self-aligned gates, which he had created at Fairchild in 1968. At Fairchild in 1968, Faggin also designed and manufactured the first commercial IC using SGT, the Fairchild 3708.[11] As soon as he joined the Intel MOS Department, he created a new random logic design methodology based on silicon gate, and contributed many technology and circuit design inventions that enabled their single chip microprocessor to become a reality. His methodology set the design style for all the early Intel microprocessors and later for the Zilog Z80. He also led the MCS-4 project and was responsible for its successful outcome (1970–1971).[12] Shima designed the logic[3] and the Busicom calculator firmware, and assisted Faggin during the first six months of the implementation. The manager of Intel's MOS Design Department was Leslie L. Vadász.[12] At the time of the MCS-4 development, Vadasz's attention was completely focused on the mainstream business of semiconductor memories and he left the leadership and the management of the MCS-4 project to Faggin.

Thus, the chief designers of the chip were Faggin who created the design methodology and the silicon-based chip design, Hoff who formulated the architecture before moving on to other projects, and Shima who produced the initial Busicom design and then assisted in the development of the final Intel design.[5]

1971

The 4004 was first introduced in Japan, as the microprocessor for the Busicom 141-PF calculator, in March 1971.[3][5] In North America, the first public mention of the 4004 was an advertisement in the November 15, 1971 edition of Electronic News,[13] though unconfirmed reports put the date of first delivery as early as March 1971. Packaged in a 16-pin ceramic dual in-line package, the 4004 was the first commercially available computer processor designed and manufactured by chip maker Intel, which had previously made semiconductor memory chips. The 4004 was followed the next year by the first ever 8-bit microprocessor, the 3,500 transistor 8008 (and the 4040, a revised and improved 4004). It was not until the development of the 40-pin 8080 in 1974 that the address and data buses would be separated, giving faster and simpler access to memory.

References

- ↑ The Story of the Intel® 4004

- ↑ 4004 Datasheet

- ↑ 3.00 3.01 3.02 3.03 3.04 3.05 3.06 3.07 3.08 3.09 3.10 3.11 3.12 3.13 3.14 3.15 Masatoshi Shima, IEEE

- ↑ 4.0 4.1 4.2 4.3 4.4 4.5 4.6 4.7 4.8 Federico Faggin, The Making of the First Microprocessor, IEEE Solid-State Circuits Magazine, Winter 2009, IEEE Xplore

- ↑ 5.0 5.1 5.2 5.3 5.4 5.5 Nigel Tout, The Busicom 141-PF calculator and the Intel 4004 microprocessor, accessed November 15, 2009

- ↑ 6.0 6.1 6.2 William Aspray (1994-05-25), Oral-History: Tadashi Sasaki, Interview #211 for the Center for the History of Electrical Engineering, The Institute of Electrical and Electronics Engineers, Inc. Accessed 2013-01-02.

- ↑ 7.0 7.1 Faggin, F. (1992). "The Birth of the Microprocessor". Byte, pp. 145–150, March 1992.

- ↑ http://www.cpu-world.com/CPUs/4004/index.html Intel 4004 microprocessor family, retrieved 2011 Dec 14

- ↑ Possibly he had confused the Plessey name with that of Massey Ferguson, makers of agricultural machinery.

- ↑ Intel 4004 Fun Facts, Intel, accessed 2011-07-06

- ↑ Earliest Published Papers, retrieved 2012 Jan 16

- ↑ 12.0 12.1 The Intel4004, Intel4004.com, accessed 2008-03-15

- ↑ George Gilder (1990), Microcosm: the quantum revolution in economics and technology, Simon and Schuster, ISBN 978-0-671-70592-3, p. 107: "Intel's first advertisement for the 4004 appeared in the November 15, 1971 issue of Electronic News"

| base frequency | 0.5 MHz (5.0e-4 GHz, 500 kHz) + and 0.74 MHz (7.4e-4 GHz, 740 kHz) + |

| chipset | 4001 +, 4002 + and 4003 + |

| core count | 1 + |

| core voltage | 15 V (150 dV, 1,500 cV, 15,000 mV) + |

| core voltage tolerance | 5% + |

| designer | Intel +, Masatoshi Shima +, Tadashi Sasaki +, Ted Hoff +, Federico Faggin + and Stan Mazor + |

| die area | 12 mm² (0.0186 in², 0.12 cm², 12,000,000 µm²) + |

| die length | 4 mm (0.4 cm, 0.157 in, 4,000 µm) + |

| die width | 3 mm (0.3 cm, 0.118 in, 3,000 µm) + |

| family | MCS-4 + |

| first announced | November 15, 1971 + |

| first launched | December 1971 + |

| full page name | intel/mcs-4/4004 + |

| instance of | microprocessor + |

| isa | 4004 + |

| isa family | 4004 + |

| last order | 1982 + |

| ldate | December 1971 + |

| main image |  + + |

| main image caption | 4004 in CerDIP + |

| manufacturer | Intel + |

| market segment | Commercial + and Industrial + |

| max ambient temperature | 343.15 K (70 °C, 158 °F, 617.67 °R) + |

| max memory address | 4 kB + |

| max storage temperature | 398.15 K (125 °C, 257 °F, 716.67 °R) + |

| microarchitecture | 4004 + |

| min ambient temperature | 273.15 K (0 °C, 32 °F, 491.67 °R) + |

| min storage temperature | 218.15 K (-55 °C, -67 °F, 392.67 °R) + |

| model number | 4004 + |

| name | 4004 + |

| part number | C4004 +, D4004 + and P4004 + |

| power dissipation | 1 W (1,000 mW, 0.00134 hp, 0.001 kW) + |

| process | 10,000 nm (10 μm, 0.01 mm) + |

| series | MCS + |

| technology | pMOS + |

| thread count | 1 + |

| transistor count | 2,250 + |

| word size | 4 bit (0.5 octets, 1 nibbles) + |