(→Memory Hierarchy) |

|||

| Line 1: | Line 1: | ||

{{amd title|Zen|arch}} | {{amd title|Zen|arch}} | ||

{{microarchitecture | {{microarchitecture | ||

| + | | atype = CPU | ||

| name = Zen | | name = Zen | ||

| designer = AMD | | designer = AMD | ||

| Line 84: | Line 85: | ||

| successor link = amd/microarchitectures/zen+ | | successor link = amd/microarchitectures/zen+ | ||

}} | }} | ||

| − | '''Zen''' is the [[microarchitecture]] developed by [[AMD]] as a successor to both {{\\|Excavator}} and {{\\|Puma}}. Zen is an entirely new design, built from the ground up for optimal balance of performance and power capable of covering the entire computing spectrum from fanless notebooks to high-performance desktop computers. Zen is set to be released in early-2017. Zen is set to be eventually replaced by {{\\|Zen+}}. | + | '''Zen''' ('''family 17h''') is the [[microarchitecture]] developed by [[AMD]] as a successor to both {{\\|Excavator}} and {{\\|Puma}}. Zen is an entirely new design, built from the ground up for optimal balance of performance and power capable of covering the entire computing spectrum from fanless notebooks to high-performance desktop computers. Zen is set to be released in early-2017. Zen is set to be eventually replaced by {{\\|Zen+}}. |

== Etymology == | == Etymology == | ||

| Line 95: | Line 96: | ||

{| class="wikitable" | {| class="wikitable" | ||

|- | |- | ||

| − | ! Core !! C/T | + | ! Core !! C/T !! Target |

|- | |- | ||

| − | | {{amd|Naples|l=core}} || 32/64 | + | | {{amd|Naples|l=core}} || 32/64 || High-end server multiprocessors |

|- | |- | ||

| − | | {{amd|Snowy Owl|l=core}} || 16/32 | + | | {{amd|Snowy Owl|l=core}} || 16/32 || Mid-range server processors |

|- | |- | ||

| − | | {{amd|Summit Ridge|l=core}} || 8/16 | + | | {{amd|Summit Ridge|l=core}} || 8/16 || High-end desktops & enthusiasts market |

|- | |- | ||

| − | | {{amd|Raven Ridge|l=core}} || 4/8 | + | | {{amd|Raven Ridge|l=core}} || 4/8 || Mainstream desktop & mobile processors with GPU |

|} | |} | ||

| + | |||

| + | == Brands == | ||

| + | {{empty section}} | ||

| + | |||

| + | == Release Dates == | ||

| + | The first set of processors, as part of the {{amd|Ryzen}} family is expected to be officially launched before the end of Q1 - likely mid-February 2017 before the Game Developer Conference (GDC). The second batch is expected to be release toward the end of the year. | ||

== Process Technology == | == Process Technology == | ||

Zen is planned to be manufactured on [[Global Foundries]]' [[14 nm process]]. AMD's previous microarchitectures were based on [[32 nm|32]] and [[28 nm|28]] nanometer processes. The jump to 14 nm is part of AMD attempt to remain competitive against Intel (Both {{intel|SkyLake}} and {{intel|Kaby Lake}} are also manufactured on 14 nm although by 2017 Intel plans on moving on to {{intel|Cannonlake}} and [[10 nm process]]). The move to 14 nm will bring along related benefits of a smaller node such as reduced heat and power consumption for identical designs. | Zen is planned to be manufactured on [[Global Foundries]]' [[14 nm process]]. AMD's previous microarchitectures were based on [[32 nm|32]] and [[28 nm|28]] nanometer processes. The jump to 14 nm is part of AMD attempt to remain competitive against Intel (Both {{intel|SkyLake}} and {{intel|Kaby Lake}} are also manufactured on 14 nm although by 2017 Intel plans on moving on to {{intel|Cannonlake}} and [[10 nm process]]). The move to 14 nm will bring along related benefits of a smaller node such as reduced heat and power consumption for identical designs. | ||

| − | == | + | == Compatibility == |

| − | + | Microsoft announced that only [[Windows 10]] will have support for Zen. [[Linux]] added initial support for Zen starting with Linux Kernel 4.1. | |

| + | |||

| + | {| class="wikitable" | ||

| + | ! Vendor !! OS !! Version !! Notes | ||

| + | |- | ||

| + | | rowspan="3" | Microsoft || rowspan="3" | Windows || style="background-color: #ffdad6;" | Windows 7 || No Support | ||

| + | |- | ||

| + | | style="background-color: #ffdad6;" | Windows 8 || No Support | ||

| + | |- | ||

| + | | style="background-color: #d6ffd8;" | Windows 10 || Support | ||

| + | |- | ||

| + | | Linux || Linux || style="background-color: #d6ffd8;" | Kernel 4.1 || Initial Support | ||

| + | |} | ||

| + | |||

| + | == Compiler support == | ||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | ! Compiler !! Arch-Specific || Arch-Favorable | ||

| + | |- | ||

| + | | [[GCC]] || <code>-march=znver1</code> || <code>-mtune=znver1</code> | ||

| + | |- | ||

| + | | [[LLVM]] || <code>-march=znver1</code> || <code>-mtune=znver1</code> | ||

| + | |- | ||

| + | | [[Visual Studio]] || <code>/arch:AVX2</code> || ? | ||

| + | |} | ||

== Architecture == | == Architecture == | ||

Revision as of 01:41, 29 January 2017

| Edit Values | |

| Zen µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | AMD |

| Manufacturer | GlobalFoundries |

| Introduction | 2017 |

| Process | 14 nm |

| Core Configs | 2, 4, 8, 16, 32 |

| Pipeline | |

| Type | Superscalar |

| Speculative | Yes |

| Reg Renaming | Yes |

| Instructions | |

| ISA | x86-16, x86-32, x86-64 |

| Extensions | MOVBE, MMX, SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4.2, POPCNT, AVX, AVX2, AES, PCLMUL, RDRND, F16C, BMI, BMI2, RDSEED, ADCX, PREFETCHW, CLFLUSHOPT, XSAVE, SHA, CLZERO |

| Cache | |

| L1I Cache | 64 KiB/core 4-way set associative |

| L1D Cache | 32 KiB/core 8-way set associative |

| L2 Cache | 512 KiB/core 8-way set associative |

| L3 Cache | 2 MiB/core Up to 16-way set associative |

| Cores | |

| Core Names | Raven Ridge, Summit Ridge, Snowy Owl, Naples |

| Succession | |

Zen (family 17h) is the microarchitecture developed by AMD as a successor to both Excavator and Puma. Zen is an entirely new design, built from the ground up for optimal balance of performance and power capable of covering the entire computing spectrum from fanless notebooks to high-performance desktop computers. Zen is set to be released in early-2017. Zen is set to be eventually replaced by Zen+.

Contents

Etymology

Zen was picked by Michael Clark, AMD's senior fellow and lead architect. Zen was picked to represent the balance needed between the various competing aspects of a microprocessor - transistor allocation/die size, clock/frequency restriction, power limitations, and new instructions to implement.

Codenames

| Core | C/T | Target |

|---|---|---|

| Naples | 32/64 | High-end server multiprocessors |

| Snowy Owl | 16/32 | Mid-range server processors |

| Summit Ridge | 8/16 | High-end desktops & enthusiasts market |

| Raven Ridge | 4/8 | Mainstream desktop & mobile processors with GPU |

Brands

| This section is empty; you can help add the missing info by editing this page. |

Release Dates

The first set of processors, as part of the Ryzen family is expected to be officially launched before the end of Q1 - likely mid-February 2017 before the Game Developer Conference (GDC). The second batch is expected to be release toward the end of the year.

Process Technology

Zen is planned to be manufactured on Global Foundries' 14 nm process. AMD's previous microarchitectures were based on 32 and 28 nanometer processes. The jump to 14 nm is part of AMD attempt to remain competitive against Intel (Both SkyLake and Kaby Lake are also manufactured on 14 nm although by 2017 Intel plans on moving on to Cannonlake and 10 nm process). The move to 14 nm will bring along related benefits of a smaller node such as reduced heat and power consumption for identical designs.

Compatibility

Microsoft announced that only Windows 10 will have support for Zen. Linux added initial support for Zen starting with Linux Kernel 4.1.

| Vendor | OS | Version | Notes |

|---|---|---|---|

| Microsoft | Windows | Windows 7 | No Support |

| Windows 8 | No Support | ||

| Windows 10 | Support | ||

| Linux | Linux | Kernel 4.1 | Initial Support |

Compiler support

| Compiler | Arch-Specific | Arch-Favorable |

|---|---|---|

| GCC | -march=znver1 |

-mtune=znver1

|

| LLVM | -march=znver1 |

-mtune=znver1

|

| Visual Studio | /arch:AVX2 |

? |

Architecture

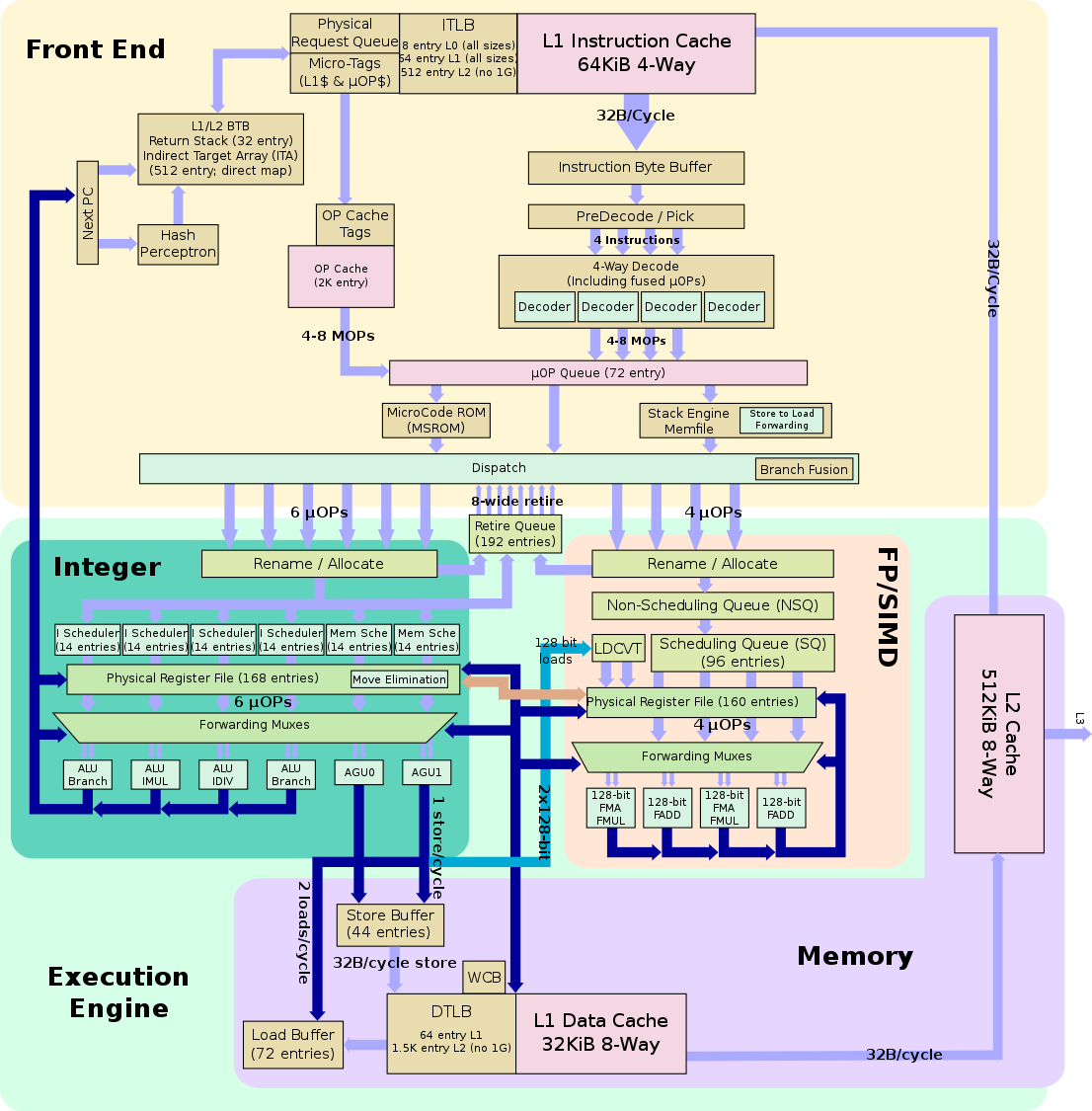

AMD Zen is an entirely new design from the ground up which introduces considerable amount of improvements and design changes over Excavator. Zen-based microprocessors will utilize AMD's Socket AM4 unified platform.

Key changes from Excavator

- Zen was designed to succeed BOTH Excavator (High-performance) and Puma (Low-power) covering the entire range in one architecture

- Cover the entire spectrum from fanless notebooks to high-performance desktops

- More aggressive clock gating with multi-level regions

- Power focus from design, employs low-power design methodologies

- Utilizes 14 nm process (from 28 nm)

- 40% improvement in IPC per core per single-thread (From Excavator)

- Core engine

- SMT support, 2 threads/core

- Improved branch mispredictions

- Better branch predicitons with 2 branches per BTB entry

- Lower miss latency penalty

- Large Op cache

- Wider μop dispatch (6, up from 4)

- Larger instruction scheduler

- Larger integer physical RF (84, up form 48)

- Larger FP physical RF (96, up form 60)

- Larger retire throughput (8, up from 4)

- Larger Retire Queue (192, up from 128)

- Larger Load Queue (72, up from 44)

- Larger Store Queue (44, up from 32)

- Quad-issue FPU

- Cache system

- Write-back L1 cache eviction policy (From write-through)

- Faster L2 cache

- Faster L3 cache

- Large Op cache

- Faster Load to FPU (down to 7, from 9 cycles)

- Better L1$ and L2$ data prefetcher

- 2x the L1 and L2 bandwidth

- 5x L3 bandwidth

- Move elimination block added

Block Diagram

Individual Core

Memory Hierarchy

- Cache

- L1I Cache:

- 64 KiB 4-way set associative

- 32 B line size

- shared by the two threads, per core

- 64 KiB 4-way set associative

- L1D Cache:

- 32 KiB 8-way set associative

- 32 B line size

- write-back policy

- 32 KiB 8-way set associative

- L2 Cache:

- 512 KiB 8-way set associative

- 32 B line

- write-back policy

- L3 Cache:

- 2 MiB/core, shared across all cores.

- Up to 16-way set associative

- Write-back policy

- System DRAM:

- 2 Channels

- L1I Cache:

Zen TLB consists of dedicated level one TLB for instruction cache and another one for data cache. Additionally there is a unified second level TLB.

- TLBs

- BP TLB

- 8 entry L0 TLB, all page sizes

- 64 entry L1 TLB, all page sizes

- 512 entry L2 TLB, no 1G pages

- DTLB

- 64 entry, all page sizes

- STLB

- 1.5K entry, no 1G pages

- BP TLB

Die Shot

| This section is empty; you can help add the missing info by editing this page. |

All Zen Chips

| Zen Chips | ||||||

|---|---|---|---|---|---|---|

| Model | Family | Core | Launched | Power Dissipation | Freq | Max Mem |

| 200GE | Athlon | Raven Ridge | 6 September 2018 | 3,200 MHz 3.2 GHz 3,200,000 kHz | 65,536 MiB 67,108,864 KiB 68,719,476,736 B 64 GiB 0.0625 TiB | |

| 220GE | Athlon | Raven Ridge | 21 December 2018 | 3,400 MHz 3.4 GHz 3,400,000 kHz | 65,536 MiB 67,108,864 KiB 68,719,476,736 B 64 GiB 0.0625 TiB | |

| 240GE | Athlon | Raven Ridge | 21 December 2018 | 3,500 MHz 3.5 GHz 3,500,000 kHz | 65,536 MiB 67,108,864 KiB 68,719,476,736 B 64 GiB 0.0625 TiB | |

| 3000G | Athlon | Dali Raven Ridge | 20 November 2019 | 3,500 MHz 3.5 GHz 3,500,000 kHz | 65,536 MiB 67,108,864 KiB 68,719,476,736 B 64 GiB 0.0625 TiB | |

| 300U | Athlon | Picasso | 6 January 2019 | 2,400 MHz 2.4 GHz 2,400,000 kHz | 65,536 MiB 67,108,864 KiB 68,719,476,736 B 64 GiB 0.0625 TiB | |

| 3150U | Athlon Gold | Dali | 6 January 2020 | 2,400 MHz 2.4 GHz 2,400,000 kHz | 32,768 MiB 33,554,432 KiB 34,359,738,368 B 32 GiB 0.0313 TiB | |

| PRO 200GE | Athlon | Raven Ridge | 6 September 2018 | 3,200 MHz 3.2 GHz 3,200,000 kHz | 65,536 MiB 67,108,864 KiB 68,719,476,736 B 64 GiB 0.0625 TiB | |

| 3050U | Athlon Silver | Dali | 6 January 2020 | 2,300 MHz 2.3 GHz 2,300,000 kHz | 32,768 MiB 33,554,432 KiB 34,359,738,368 B 32 GiB 0.0313 TiB | |

| 7251 | EPYC | Naples | 20 June 2017 | 2,100 MHz 2.1 GHz 2,100,000 kHz | 2,097,152 MiB 2,147,483,648 KiB 2,199,023,255,552 B 2,048 GiB 2 TiB | |

| 7261 | EPYC | Naples | 14 June 2018 | 2,500 MHz 2.5 GHz 2,500,000 kHz | 2,097,152 MiB 2,147,483,648 KiB 2,199,023,255,552 B 2,048 GiB 2 TiB | |

| 7281 | EPYC | Naples | 20 June 2017 | 2,100 MHz 2.1 GHz 2,100,000 kHz | 2,097,152 MiB 2,147,483,648 KiB 2,199,023,255,552 B 2,048 GiB 2 TiB | |

| 7301 | EPYC | Naples | 20 June 2017 | 2,200 MHz 2.2 GHz 2,200,000 kHz | 2,097,152 MiB 2,147,483,648 KiB 2,199,023,255,552 B 2,048 GiB 2 TiB | |

| 7351 | EPYC | Naples | 20 June 2017 | 2,400 MHz 2.4 GHz 2,400,000 kHz | 2,097,152 MiB 2,147,483,648 KiB 2,199,023,255,552 B 2,048 GiB 2 TiB | |

| 7351P | EPYC | Naples | 20 June 2017 | 2,400 MHz 2.4 GHz 2,400,000 kHz | 2,097,152 MiB 2,147,483,648 KiB 2,199,023,255,552 B 2,048 GiB 2 TiB | |

| 7371 | EPYC | Naples | 2019 | 3,100 MHz 3.1 GHz 3,100,000 kHz | 2,097,152 MiB 2,147,483,648 KiB 2,199,023,255,552 B 2,048 GiB 2 TiB | |

| 7401 | EPYC | Naples | 20 June 2017 | 2,000 MHz 2 GHz 2,000,000 kHz | 2,097,152 MiB 2,147,483,648 KiB 2,199,023,255,552 B 2,048 GiB 2 TiB | |

| 7401P | EPYC | Naples | 20 June 2017 | 2,000 MHz 2 GHz 2,000,000 kHz | 2,097,152 MiB 2,147,483,648 KiB 2,199,023,255,552 B 2,048 GiB 2 TiB | |

| 7451 | EPYC | Naples | 20 June 2017 | 2,300 MHz 2.3 GHz 2,300,000 kHz | 2,097,152 MiB 2,147,483,648 KiB 2,199,023,255,552 B 2,048 GiB 2 TiB | |

| 7501 | EPYC | Naples | 20 June 2017 | 2,000 MHz 2 GHz 2,000,000 kHz | 2,097,152 MiB 2,147,483,648 KiB 2,199,023,255,552 B 2,048 GiB 2 TiB | |

| 7551 | EPYC | Naples | 20 June 2017 | 2,000 MHz 2 GHz 2,000,000 kHz | 2,097,152 MiB 2,147,483,648 KiB 2,199,023,255,552 B 2,048 GiB 2 TiB | |

| 7551P | EPYC | Naples | 20 June 2017 | 2,000 MHz 2 GHz 2,000,000 kHz | 2,097,152 MiB 2,147,483,648 KiB 2,199,023,255,552 B 2,048 GiB 2 TiB | |

| 7601 | EPYC | Naples | 20 June 2017 | 2,200 MHz 2.2 GHz 2,200,000 kHz | 2,097,152 MiB 2,147,483,648 KiB 2,199,023,255,552 B 2,048 GiB 2 TiB | |

| 3101 | EPYC Embedded | Snowy Owl | 21 February 2018 | 2,100 MHz 2.1 GHz 2,100,000 kHz | 524,288 MiB 536,870,912 KiB 549,755,813,888 B 512 GiB 0.5 TiB | |

| 3151 | EPYC Embedded | Snowy Owl | 21 February 2018 | 2,700 MHz 2.7 GHz 2,700,000 kHz | 524,288 MiB 536,870,912 KiB 549,755,813,888 B 512 GiB 0.5 TiB | |

| 3201 | EPYC Embedded | Snowy Owl | 21 February 2018 | 1,500 MHz 1.5 GHz 1,500,000 kHz | 524,288 MiB 536,870,912 KiB 549,755,813,888 B 512 GiB 0.5 TiB | |

| 3251 | EPYC Embedded | Snowy Owl | 21 February 2018 | 2,500 MHz 2.5 GHz 2,500,000 kHz | 524,288 MiB 536,870,912 KiB 549,755,813,888 B 512 GiB 0.5 TiB | |

| 3255 | EPYC Embedded | Snowy Owl | 2,500 MHz 2.5 GHz 2,500,000 kHz | 524,288 MiB 536,870,912 KiB 549,755,813,888 B 512 GiB 0.5 TiB | ||

| 3301 | EPYC Embedded | Snowy Owl | 21 February 2018 | 2,000 MHz 2 GHz 2,000,000 kHz | 1,048,576 MiB 1,073,741,824 KiB 1,099,511,627,776 B 1,024 GiB 1 TiB | |

| 3351 | EPYC Embedded | Snowy Owl | 21 February 2018 | 1,900 MHz 1.9 GHz 1,900,000 kHz | 1,048,576 MiB 1,073,741,824 KiB 1,099,511,627,776 B 1,024 GiB 1 TiB | |

| 3401 | EPYC Embedded | Snowy Owl | 21 February 2018 | 1,850 MHz 1.85 GHz 1,850,000 kHz | 1,048,576 MiB 1,073,741,824 KiB 1,099,511,627,776 B 1,024 GiB 1 TiB | |

| 3451 | EPYC Embedded | Snowy Owl | 21 February 2018 | 2,150 MHz 2.15 GHz 2,150,000 kHz | 1,048,576 MiB 1,073,741,824 KiB 1,099,511,627,776 B 1,024 GiB 1 TiB | |

| FireFlight | 3 August 2018 | 3,000 MHz 3 GHz 3,000,000 kHz | 8,192 MiB 8,388,608 KiB 8,589,934,592 B 8 GiB 0.00781 TiB | |||

| 1200 | Ryzen 3 | Summit Ridge | 27 July 2017 | 3,100 MHz 3.1 GHz 3,100,000 kHz | 65,536 MiB 67,108,864 KiB 68,719,476,736 B 64 GiB 0.0625 TiB | |

| 1300X | Ryzen 3 | Summit Ridge | 27 July 2017 | 3,500 MHz 3.5 GHz 3,500,000 kHz | 65,536 MiB 67,108,864 KiB 68,719,476,736 B 64 GiB 0.0625 TiB | |

| 2200G | Ryzen 3 | Raven Ridge | 12 February 2018 | 3,500 MHz 3.5 GHz 3,500,000 kHz | 65,536 MiB 67,108,864 KiB 68,719,476,736 B 64 GiB 0.0625 TiB | |

| 2200GE | Ryzen 3 | Raven Ridge | 19 April 2018 | 3,200 MHz 3.2 GHz 3,200,000 kHz | 65,536 MiB 67,108,864 KiB 68,719,476,736 B 64 GiB 0.0625 TiB | |

| 2200U | Ryzen 3 | Raven Ridge | 8 January 2018 | 2,500 MHz 2.5 GHz 2,500,000 kHz | 32,768 MiB 33,554,432 KiB 34,359,738,368 B 32 GiB 0.0313 TiB | |

| 2300U | Ryzen 3 | Raven Ridge | 8 January 2018 | 2,000 MHz 2 GHz 2,000,000 kHz | 32,768 MiB 33,554,432 KiB 34,359,738,368 B 32 GiB 0.0313 TiB | |

| 3250U | Ryzen 3 | Dali | 6 January 2020 | 2,600 MHz 2.6 GHz 2,600,000 kHz | 32,768 MiB 33,554,432 KiB 34,359,738,368 B 32 GiB 0.0313 TiB | |

| PRO 1200 | Ryzen 3 | Summit Ridge | 3,100 MHz 3.1 GHz 3,100,000 kHz | 65,536 MiB 67,108,864 KiB 68,719,476,736 B 64 GiB 0.0625 TiB | ||

| PRO 1300 | Ryzen 3 | Summit Ridge | 3,500 MHz 3.5 GHz 3,500,000 kHz | 65,536 MiB 67,108,864 KiB 68,719,476,736 B 64 GiB 0.0625 TiB | ||

| PRO 2200G | Ryzen 3 | Raven Ridge | 10 May 2018 | 3,500 MHz 3.5 GHz 3,500,000 kHz | 65,536 MiB 67,108,864 KiB 68,719,476,736 B 64 GiB 0.0625 TiB | |

| PRO 2200GE | Ryzen 3 | Raven Ridge | 10 May 2018 | 3,200 MHz 3.2 GHz 3,200,000 kHz | 65,536 MiB 67,108,864 KiB 68,719,476,736 B 64 GiB 0.0625 TiB | |

| PRO 2300U | Ryzen 3 | Raven Ridge | 8 January 2018 | 2,000 MHz 2 GHz 2,000,000 kHz | 32,768 MiB 33,554,432 KiB 34,359,738,368 B 32 GiB 0.0313 TiB | |

| 1400 | Ryzen 5 | Summit Ridge | 11 April 2017 | 3,200 MHz 3.2 GHz 3,200,000 kHz | 65,536 MiB 67,108,864 KiB 68,719,476,736 B 64 GiB 0.0625 TiB | |

| 1500X | Ryzen 5 | Summit Ridge | 11 April 2017 | 3,500 MHz 3.5 GHz 3,500,000 kHz | 65,536 MiB 67,108,864 KiB 68,719,476,736 B 64 GiB 0.0625 TiB | |

| 1600 | Ryzen 5 | Summit Ridge | 11 April 2017 | 3,200 MHz 3.2 GHz 3,200,000 kHz | 65,536 MiB 67,108,864 KiB 68,719,476,736 B 64 GiB 0.0625 TiB | |

| 1600X | Ryzen 5 | Summit Ridge | 11 April 2017 | 3,600 MHz 3.6 GHz 3,600,000 kHz | 65,536 MiB 67,108,864 KiB 68,719,476,736 B 64 GiB 0.0625 TiB | |

| 2400G | Ryzen 5 | Raven Ridge | 12 February 2018 | 3,600 MHz 3.6 GHz 3,600,000 kHz | 65,536 MiB 67,108,864 KiB 68,719,476,736 B 64 GiB 0.0625 TiB | |

| 2400GE | Ryzen 5 | Raven Ridge | 19 April 2018 | 3,200 MHz 3.2 GHz 3,200,000 kHz | 65,536 MiB 67,108,864 KiB 68,719,476,736 B 64 GiB 0.0625 TiB | |

| Count: 79 | ||||||

See also

| codename | Zen + |

| core count | 2 +, 4 +, 8 +, 16 + and 32 + |

| designer | AMD + |

| first launched | 2017 + |

| full page name | amd/microarchitectures/zen + |

| instance of | microarchitecture + |

| instruction set architecture | x86-16 +, x86-32 + and x86-64 + |

| manufacturer | GlobalFoundries + |

| microarchitecture type | CPU + |

| name | Zen + |

| process | 14 nm (0.014 μm, 1.4e-5 mm) + |