From WikiChip

Difference between revisions of "intel/microarchitectures/ice lake (client)"

(→New instructions) |

(→New instructions) |

||

| Line 85: | Line 85: | ||

* {{x86|CLWB|<code>CLWB</code>}} - Force cache line write-back without flush | * {{x86|CLWB|<code>CLWB</code>}} - Force cache line write-back without flush | ||

* {{x86|RDPID|<code>RDPID</code>}} - Read Processor ID | * {{x86|RDPID|<code>RDPID</code>}} - Read Processor ID | ||

| + | * {{x86|AVX512VPOPCNTDQ|<code>AVX512VPOPCNTDQ</code>}} - AVX-512 Vector Population Count Doubleword and Quadword | ||

== All Ice Lake Chips == | == All Ice Lake Chips == | ||

Revision as of 17:19, 9 March 2018

| Edit Values | |

| Ice Lake µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | Intel |

| Manufacturer | Intel |

| Introduction | 2018 |

| Process | 10 nm |

| Instructions | |

| ISA | x86-64 |

| Cores | |

| Core Names | Ice Lake S |

| Succession | |

Ice Lake (ICL) Client Configuration is Intel's successor to Cannon Lake, a 10 nm microarchitecture for mainstream workstations, desktops, and mobile devices.

Contents

Codenames

| Core | Abbrev | Description | Graphics | Target |

|---|---|---|---|---|

| Ice Lake Y | ICL-Y | Extremely low power | 2-in-1s detachable, tablets, and computer sticks | |

| Ice Lake U | ICL-U | Ultra-low Power | Light notebooks, portable All-in-Ones (AiOs), Minis, and conference room | |

| Ice Lake H | ICL-H | High-performance Graphics | Ultimate mobile performance, mobile workstations | |

| Ice Lake S | ICL-S | Performance-optimized lifestyle | Desktop performance to value, AiOs, and minis | |

| Ice Lake X | ICL-X | Extreme Performance | High-end desktops & enthusiasts market | |

| Ice Lake DT | ICL-DT | Workstation | Workstations & entry-level servers |

Process Technology

- See also: Cannon Lake § Process Technology

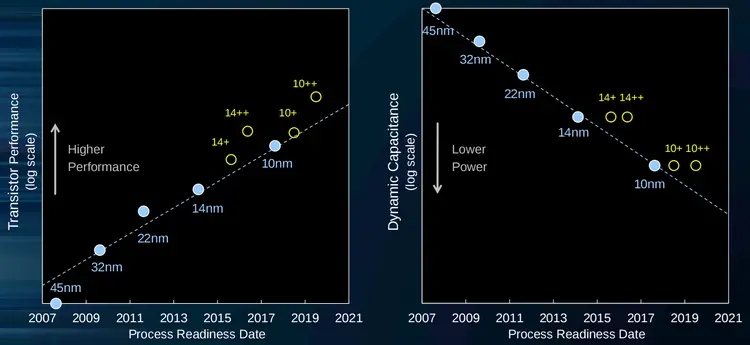

Ice Lake will use a second-generation enhanced 10 nm process called "10 nm+". Versus the first generation 10nm which was used for Cannon Lake, 10nm+ will feature higher performance through higher drive current for the same power envelope.

Compiler support

Support for Ice Lake was added in LLVM Clang 6.0 and GCC 8.0.

| Compiler | Arch-Specific | Arch-Favorable |

|---|---|---|

| ICC | -march=icelake |

-mtune=icelake

|

| GCC | -march=icelake |

-mtune=icelake

|

| LLVM | -march=icelake |

-mtune=icelake

|

| Visual Studio | /? |

/tune:?

|

CPUID

| Core | Extended Family |

Family | Extended Model |

Model |

|---|---|---|---|---|

| ? | 0 | 0x6 | 0x? | ? |

| Family 6 Model ? | ||||

| ? | 0 | 0x6 | ? | ? |

| Family 6 Model ? | ||||

Architecture

Not much is known about Ice Lake's architecture.

Key changes from Cannon Lake

New instructions

Ice Lake introduced a number of new instructions:

-

CLWB- Force cache line write-back without flush -

RDPID- Read Processor ID -

AVX512VPOPCNTDQ- AVX-512 Vector Population Count Doubleword and Quadword

All Ice Lake Chips

| List of Ice Lake-based Processors | ||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Main processor | Turbo Boost | Memory | GPU | Features | ||||||||||||||||

| Model | Launched | Price | Family | Platform | Core | Cores | Threads | L3$ | TDP | Base | 1 Core | 2 Cores | 4 Cores | 6 Cores | Max Memory | Name | Base | Burst | TBT | HT |

| Count: 0 | ||||||||||||||||||||

Facts about "Ice Lake (client) - Microarchitectures - Intel"

| codename | Ice Lake + |

| designer | Intel + |

| first launched | 2018 + |

| full page name | intel/microarchitectures/ice lake (client) + |

| instance of | microarchitecture + |

| instruction set architecture | x86-64 + |

| manufacturer | Intel + |

| microarchitecture type | CPU + |

| name | Ice Lake + |

| process | 10 nm (0.01 μm, 1.0e-5 mm) + |