From WikiChip

Difference between revisions of "intel/microarchitectures/ice lake (client)"

(https://software.intel.com/sites/default/files/managed/c5/15/architecture-instruction-set-extensions-programming-reference.pdf Page 13 lists new instructions supported by Ice Lake) |

|||

| Line 51: | Line 51: | ||

* Enhanced "10nm+" (from "10nm", 2nd gen) | * Enhanced "10nm+" (from "10nm", 2nd gen) | ||

* {{intel|Gen10|l=arch}} → {{intel|Gen11|l=arch}} graphics | * {{intel|Gen10|l=arch}} → {{intel|Gen11|l=arch}} graphics | ||

| + | |||

| + | ====New instructions ==== | ||

| + | Ice Lake introduced a number of {{x86|extensions|new instructions}}: | ||

| + | |||

| + | * RDPID | ||

| + | * Fast Short REP MOV | ||

| + | * AVX512_VPOPCNTDQ | ||

| + | * AVX512_VNNI, AVX512_VBMI2, AVX512_BITALG, AVX512+VAES, AVX512+GFNI, AVX512+VPCLMULQDQ | ||

== All Ice Lake Chips == | == All Ice Lake Chips == | ||

Revision as of 05:20, 2 December 2017

| Edit Values | |

| Ice Lake µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | Intel |

| Manufacturer | Intel |

| Introduction | 2018 |

| Process | 10 nm |

| Instructions | |

| ISA | x86-64 |

| Cores | |

| Core Names | Ice Lake S |

| Succession | |

Ice Lake (ICL) is a microarchitecture designed by Intel as a successor to Coffee Lake. Ice Lake is the "Architecture" microarchitecture as part of Intel's PAO model and is manufactured on Intel's 2nd generation 10 nm process.

Contents

Codenames

| Core | Abbrev | Description | Graphics | Target |

|---|---|---|---|---|

| Ice Lake Y | ICL-Y | Extremely low power | 2-in-1s detachable, tablets, and computer sticks | |

| Ice Lake U | ICL-U | Ultra-low Power | Light notebooks, portable All-in-Ones (AiOs), Minis, and conference room | |

| Ice Lake H | ICL-H | High-performance Graphics | Ultimate mobile performance, mobile workstations | |

| Ice Lake S | ICL-S | Performance-optimized lifestyle | Desktop performance to value, AiOs, and minis | |

| Ice Lake X | ICL-X | Extreme Performance | High-end desktops & enthusiasts market | |

| Ice Lake DT | ICL-DT | Workstation | Workstations & entry-level servers |

Process Technology

- See also: Cannonlake § Process Technology

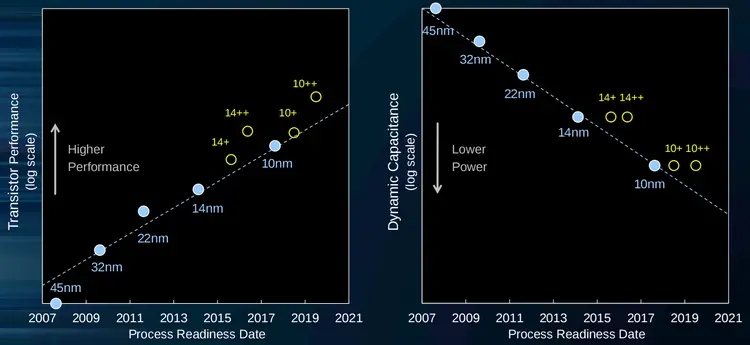

Ice Lake will use a second-generation enhanced 10 nm process called "10 nm+". Versus the first generation 10nm which was used for Cannonlake, 10nm+ will feature higher performance through higher drive current for the same power envelope.

Architecture

Not much is known about Ice Lake's architecture.

Key changes from Cannonlake

New instructions

Ice Lake introduced a number of new instructions:

- RDPID

- Fast Short REP MOV

- AVX512_VPOPCNTDQ

- AVX512_VNNI, AVX512_VBMI2, AVX512_BITALG, AVX512+VAES, AVX512+GFNI, AVX512+VPCLMULQDQ

All Ice Lake Chips

| List of Ice Lake-based Processors | ||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Main processor | Turbo Boost | Memory | GPU | Features | ||||||||||||||||

| Model | Launched | Price | Family | Platform | Core | Cores | Threads | L3$ | TDP | Base | 1 Core | 2 Cores | 4 Cores | 6 Cores | Max Memory | Name | Base | Burst | TBT | HT |

| Count: 0 | ||||||||||||||||||||

Facts about "Ice Lake (client) - Microarchitectures - Intel"

| codename | Ice Lake + |

| designer | Intel + |

| first launched | 2018 + |

| full page name | intel/microarchitectures/ice lake (client) + |

| instance of | microarchitecture + |

| instruction set architecture | x86-64 + |

| manufacturer | Intel + |

| microarchitecture type | CPU + |

| name | Ice Lake + |

| process | 10 nm (0.01 μm, 1.0e-5 mm) + |