From WikiChip

Difference between revisions of "intel/microarchitectures/ice lake (client)"

| Line 1: | Line 1: | ||

{{intel title|Ice Lake|arch}} | {{intel title|Ice Lake|arch}} | ||

{{microarchitecture | {{microarchitecture | ||

| − | | atype | + | |atype=CPU |

| − | | name | + | |name=Ice Lake |

| − | | designer | + | |designer=Intel |

| − | | manufacturer | + | |manufacturer=Intel |

| − | | introduction | + | |introduction=2018 |

| − | + | |process=10 nm | |

| − | | process | + | |core name=Ice Lake S |

| − | + | |predecessor=Cannonlake | |

| − | | | + | |predecessor link=intel/microarchitectures/cannonlake |

| − | | predecessor | + | |successor=Tigerlake |

| − | | predecessor link = intel/microarchitectures/cannonlake | + | |successor link=intel/microarchitectures/tigerlake |

| − | | successor | + | |succession=Yes |

| − | | successor link | ||

}} | }} | ||

'''Ice Lake''' ('''ICL''') is a [[microarchitecture]] designed by [[Intel]] as a successor to {{\\|Coffee Lake}}. Fabricated on a [[10 nm process]], Ice Lake is the "Architecture" microarchitecture as part of Intel's {{intel|PAO}} model. | '''Ice Lake''' ('''ICL''') is a [[microarchitecture]] designed by [[Intel]] as a successor to {{\\|Coffee Lake}}. Fabricated on a [[10 nm process]], Ice Lake is the "Architecture" microarchitecture as part of Intel's {{intel|PAO}} model. | ||

Revision as of 15:36, 24 November 2017

| Edit Values | |

| Ice Lake µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | Intel |

| Manufacturer | Intel |

| Introduction | 2018 |

| Process | 10 nm |

| Cores | |

| Core Names | Ice Lake S |

| Succession | |

Ice Lake (ICL) is a microarchitecture designed by Intel as a successor to Coffee Lake. Fabricated on a 10 nm process, Ice Lake is the "Architecture" microarchitecture as part of Intel's PAO model.

Process Technology

- See also: Cannonlake § Process Technology

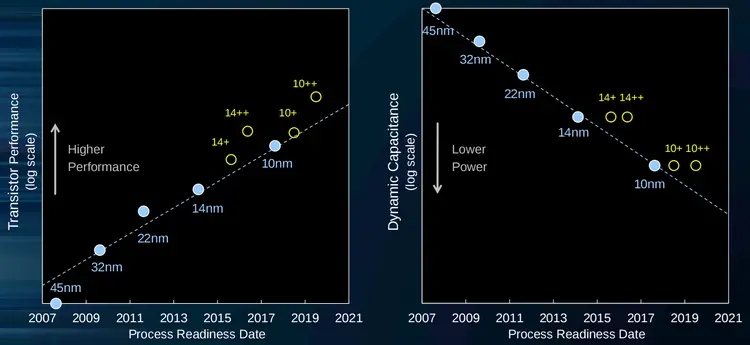

Ice Lake will use a second-generation enhanced 10 nm process called "10 nm+". Versus the first generation 10nm which was used for Cannonlake, 10nm+ will feature higher performance through higher drive current for the same power envelope.

Architecture

Not much is known about Ice Lake's architecture.

Key changes from Cannonlake

Facts about "Ice Lake (client) - Microarchitectures - Intel"

| codename | Ice Lake + |

| designer | Intel + |

| first launched | 2018 + |

| full page name | intel/microarchitectures/ice lake (client) + |

| instance of | microarchitecture + |

| manufacturer | Intel + |

| microarchitecture type | CPU + |

| name | Ice Lake + |

| process | 10 nm (0.01 μm, 1.0e-5 mm) + |