| Edit Values | |

| Semiconductor Devices | |

| Concepts | |

| Devices | |

|

CMOS (complementary metal–oxide–semiconductor) is a technique for constructing analog and digital logic circuits from two complementary MOS transistors - pMOS and nMOS. CMOS is the dominant technology used for VLSI and ULSI circuit chips used for anywhere from SRAM to microcontrollers and microprocessors.

CMOS, also known as complementary-symmetry metal–oxide–semiconductor (COS-MOS), is a type of metal–oxide–semiconductor field-effect transistor (MOSFET) fabrication process that uses complementary and symmetrical pairs of p-type and n-type MOSFETs for logic functions.[1] CMOS technology is used for constructing integrated circuit (IC) chips, including microprocessors, microcontrollers, memory chips (including CMOS BIOS), and other digital logic circuits. CMOS technology is also used for analog circuits such as image sensors (CMOS sensors), data converters, RF circuits (RF CMOS), and highly integrated transceivers for many types of communication.

Mohamed M. Atalla and Dawon Kahng invented the MOSFET at Bell Labs in 1959, and then demonstrated the PMOS (p-type MOS) and NMOS (n-type MOS) fabrication processes in 1960. These processes were later combined and adapted into the complementary MOS (CMOS) process by Chih-Tang Sah and Frank Wanlass at Fairchild Semiconductor in 1963. RCA commercialized the technology with the trademark "COS-MOS" in the late 1960s, forcing other manufacturers to find another name, leading to "CMOS" becoming the standard name for the technology by the early 1970s. CMOS eventually overtook NMOS as the dominant MOSFET fabrication process for very large-scale integration (VLSI) chips in the 1980s, while also replacing earlier transistor–transistor logic (TTL) technology. CMOS has since remained the standard fabrication process for MOSFET semiconductor devices in VLSI chips. As of 2011, 99% of IC chips, including most digital, analog and mixed-signal ICs, are fabricated using CMOS technology.[2]

Contents

Overview[edit]

- Main article: CMOS Complementary Topology

CMOS primarily makes use of what would otherwise be two separate circuit technologies - pMOS and nMOS. To better understand this, consider an nMOS transistor. Because it can pull no higher than VDD - Vt we get a degraded 1 output. Likewise with pMOS, we can pull no lower than Vt - a degraded 0 output. By combining both types, we can borrow the desired characteristics from both transistors such as a strong 0 and a strong 1.

CMOS circuits are designed with that concept in mind - always consisting of two separate sub-circuits called a PUN (pull-up network) and a PDN (pull-down network). CMOS logic must therefore by in one of two defined stages:

- PUN is open; PDN is conducting

- PUN is conducting; PDN is open

Conceptually they can be thought of as two switches, one controlling the connection between the output and VDD and one controlling the connection between the output and GND. Therefore it's important to note that if both switches are closed or both switches are open, the output will be ambiguous. The concept of a complementary topology ensures this does not happen. It should be noted that as the voltage on the transistor's gate changes, for a very brief moment both switches will be closed thereby creating a momentary spike in power consumption. This does become a problem with high frequency CMOS.

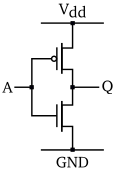

Inverter Example[edit]

- Main article: inverter

The simplest gate that can be implemented is the NOT gate which simply inverts the input. We can implement an inverter using a single nMOS and pMOS transistors. The pMOS transistor is connected to VDD while the nMOS transistor is connected to GND. When A is 0, the nMOS transistor turns OFF and the pMOS transistor turns ON. This results in Q being pulled up to 1 since the pMOS transistor will conduct VDD. Conversely, when A is 1, the nMOS transistor turns ON and the pMOS transistor turns OFF, thereby pulling Q down to GND.

Logic Families/Types[edit]

The use of static CMOS circuits with the standard PUN and PDN networks are used in the vast majority of combinational logic in integrated circuits. They are fast, low power, and have good noise margins. Perhaps the primary reason the majority of circuits are designed using static CMOS is simply due to the fact that its universally supported by CAD tools and in most standard cell libraries. Sometimes, however, specialized applications might have constraints that exceed what static CMOS can provide, for example power or area restrictions. For those occasions, various other CMOS logic families have been devised, each with their own advantages and disadvantages. Some of the common ones are listed below.

Static CMOS[edit]

- Main article: Static CMOS

Also called Full CMOS logic, static CMOS is the most commonly used logic style. Static logic provides high noise immunity, low static power consumption, and has relatively high test coverage. It does pose a number of weaknesses such as high fan-out load, and somewhat high noise generation.

Pseudo-NMOS Logic[edit]

- Main article: Pseudo-NMOS Logic

Pseudo-NMOS Logic circuit simply uses a pMOS transistor to satisfy CMOS's complementary topology. This type of logic allow high speed and low transistor count. However because of this very design, the output will experience reduced voltage swings and is thus susceptible to noise. When used sparingly, this circuit can provide substantial performance benefits at a cost of a small increase in static-power consumption. Additionally, when not used, the pMOS transistor can be used turned off shutting down the circuit at no additional cost.

Dynamic CMOS[edit]

- Main article: Dynamic CMOS

Dynamic CMOS uses a clocked pMOS PUN. This type of circuit has two phases: precharge and evaluation. When the clock is LOW, the output node is precharged to VDD (note that no current flows because the nMOS transistor is off). Once the clock goes back to HIGH the evaluation phase kicks in and the output will depend on the evaluation of the logic function implemented. Because inputs are hooked up to the nMOS transistors, the load capacitance is also smaller. This also makes it faster than static CMOS. Despite having almost half the number of transistors, this type of circuit still consumes more power than static CMOS due to the constant need to precharge and discharge of the output even if the input does not change. A side effect of this is that dynamic gates that are connected to the same clock signal cannot be directly cascaded since the monotonically falling output is not a suitable input to a second dynamic gate expecting monotonically rising signals.

Domino Logic[edit]

- Main articles: Domino Logic and Multiple-Output Domino Logic (MODL)

Domino logic solves the monotonicity problem in dynamic gates by placing an inverting static CMOS gate (usually an inverter, but could be a NAND or something) between cascading dynamic gates. The use of the inverter converts the monotonically falling output node into a rising one which is suitable for the next gate. The name domino gate is given to this dynamic-static CMOS pair because of its resemblance the behavior of domino tiles - all the gates are precharged simultaneously whereas the evaluation phase occurs sequentially.

Dual-rail Domino Logic[edit]

- Main article: Dual-rail Domino Logic

| This section is empty; you can help add the missing info by editing this page. |

NP Domino (Zipper)[edit]

- Main article: NP Domino

| This section is empty; you can help add the missing info by editing this page. |

Pass-Transistor Logic[edit]

- Main article: Pass-Transistor Logic

In Pass-Transistor Logic (PTL), inputs drive both gate terminals and source/drain terminals. In specialized circumstances, PTL can be significantly improve the speed, power, and area of the logic. In general, PTL usually yields equivalent logic to static CMOS - especially those making heavy use of transmission gates. PTL is not regenerative degrading the output as you chain them.

Complementary Pass-Transistor Logic[edit]

- Main article: Complementary Pass-Transistor Logic

Complementary Pass-Transistor Logic (CPTL) is a more specialized version of Pass-Transistor Logic which makes use of both the inputs and their complements. Likewise both the output and its complement gets generated.

Lean Integration with Pass Transistors[edit]

- Main article: Lean Integration with Pass Transistors

| This section is empty; you can help add the missing info by editing this page. |

Cascade Voltage Switch Logic[edit]

- Main article: Cascade Voltage Switch Logic (CVSL)

| This section is empty; you can help add the missing info by editing this page. |

History[edit]

- Further information: MOSFET and Transistor density

The MOSFET (metal-oxide-semiconductor field-effect transistor, or MOS transistor) was invented by Mohamed M. Atalla and Dawon Kahng at Bell Labs in 1959. There were originally two types of MOSFET fabrication processes, PMOS (p-type MOS) and NMOS (n-type MOS).[3] Both types were developed by Atalla and Kahng when they originally invented the MOSFET, fabricating both PMOS and NMOS devices with 20 µm and then 10 µm gate lengths in 1960.[4][5] While the MOSFET was initially overlooked and ignored by Bell Labs in favour of bipolar transistors,[4] the MOSFET invention generated significant interest at Fairchild Semiconductor.[3] Based on Atalla's work,[6] Chih-Tang Sah introduced MOS technology to Fairchild with his MOS-controlled tetrode fabricated in late 1960.[3]

A new type of MOSFET logic combining both the PMOS and NMOS processes was developed, called complementary MOS (CMOS), by Chih-Tang Sah and Frank Wanlass at Fairchild. In February 1963, they published the invention in a research paper.[7][8] Wanlass later filed US patent 3,356,858 for CMOS circuitry in June 1963, and it was granted in 1967. In both the research paper and the patent, the fabrication of CMOS devices was outlined, on the basis of thermal oxidation of a silicon substrate to yield a layer of silicon dioxide located between the drain contact and the source contact.[9][8]

CMOS was commercialised by RCA in the late 1960s. RCA adopted CMOS for the design of integrated circuits (ICs), developing CMOS circuits for an Air Force computer in 1965 and then a 288-bit CMOS SRAM memory chip in 1968.[7] RCA also used CMOS for its 4000-series integrated circuits in 1968, starting with a 20$nbsp;μm semiconductor manufacturing process before gradually scaling to a 10 μm process over the next several years.[10]

CMOS technology was initially overlooked by the American semiconductor industry in favour of NMOS, which was more powerful at the time. However, CMOS was quickly adopted and further advanced by Japanese semiconductor manufacturers due to its low power consumption, leading to the rise of the Japanese semiconductor industry.[11] Toshiba developed C²MOS (Clocked CMOS), a circuit technology with lower power consumption and faster operating speed than ordinary CMOS, in 1969. Toshiba used its C²MOS technology to develop a large-scale integration (LSI) chip for Sharp's Elsi Mini LED pocket calculator, developed in 1971 and released in 1972.[12] Suwa Seikosha (now Seiko Epson) began developing a CMOS IC chip for a Seiko quartz watch in 1969, and began mass-production with the launch of the Seiko Analog Quartz 38SQW watch in 1971.[13] The first mass-produced CMOS consumer electronic product was the Hamilton Pulsar "Wrist Computer" digital watch, released in 1970.[14] Due to low power consumption, CMOS logic has been widely used for calculators and watches since the 1970s.[15]

The earliest microprocessors in the early 1970s were PMOS processors, which initially dominated the early microprocessor industry. By the late 1970s, NMOS microprocessors had overtaken PMOS processors.[16] CMOS microprocessors were introduced in 1975, with the Intersil 6100,[16] and RCA CDP 1801.[17] However, CMOS processors did not become dominant until the 1980s.[16]

CMOS was initially slower than NMOS logic, thus NMOS was more widely used for computers in the 1970s.[15] The Intel 5101 (1$nbsp;kb SRAM) CMOS memory chip (1974) had an access time of 800$nbsp;ns,[18][19] whereas the fastest NMOS chip at the time, the Intel 2147 (4$nbsp;kb SRAM) HMOS memory chip (1976), had an access time of 55/70$nbsp;ns.[15][19] In 1978, a Hitachi research team led by Toshiaki Masuhara introduced the twin-well Hi-CMOS process, with its HM6147 (4$nbsp;kb SRAM) memory chip, manufactured with a 3 μm process.[15][20][21] The Hitachi HM6147 chip was able to match the performance (55/70$nbsp;ns access) of the Intel 2147 HMOS chip, while the HM6147 also consumed significantly less power (15$nbsp;mA) than the 2147 (110$nbsp;mA). With comparable performance and much less power consumption, the twin-well CMOS process eventually overtook NMOS as the most common semiconductor manufacturing process for computers in the 1980s.[15]

In the 1980s, CMOS microprocessors overtook NMOS microprocessors.[16] NASA's Galileo spacecraft, sent to orbit Jupiter in 1989, used the RCA 1802 CMOS microprocessor due to low power consumption.[14]

Intel introduced a 1.5 μm process for CMOS semiconductor device fabrication in 1983.[22] In the mid-1980s, Bijan Davari of IBM developed high-performance, low-voltage, deep sub-micron CMOS technology, which enabled the development of faster computers as well as portable computers and battery-powered handheld electronics.[23] In 1988, Davari led an IBM team that demonstrated a high-performance 250 nanometer CMOS process.[24]

Fujitsu commercialized a 700$nbsp;nm CMOS process in 1987,[22] and then Hitachi, Mitsubishi Electric, NEC and Toshiba commercialized 500$nbsp;nm CMOS in 1989.[25] In 1993, Sony commercialized a 350$nbsp;nm CMOS process, while Hitachi and NEC commercialized 250$nbsp;nm CMOS. Hitachi introduced a 160$nbsp;nm CMOS process in 1995, then Mitsubishi introduced 150$nbsp;nm CMOS in 1996, and then Samsung Electronics introduced 140$nbsp;nm in 1999.[25]

In 2000, Gurtej Singh Sandhu and Trung T. Doan at Micron Technology invented atomic layer deposition High-κ dielectric films, leading to the development of a cost-effective 90 nm CMOS process.[23][26] Toshiba and Sony developed a 65 nm CMOS process in 2002,[27] and then TSMC initiated the development of 45 nm CMOS logic in 2004.[28] The development of pitch double patterning by Gurtej Singh Sandhu at Micron Technology led to the development of 30$nbsp;nm class CMOS in the 2000s.[23]

CMOS is used in most modern LSI and VLSI devices.[15] As of 2010, CPUs with the best performance per watt each year have been CMOS static logic since 1976. As of 2019, planar CMOS technology is still the most common form of semiconductor device fabrication, but is gradually being replaced by non-planar FinFET technology, which is capable of manufacturing semiconductor nodes smaller than 20$nbsp;nm.[29]

Timeline[edit]

| Date | Channel length | Oxide thickness[30] | Researcher(s) | Organization | Ref |

|---|---|---|---|---|---|

| 1963-02 | ? | ? | Chih-Tang Sah, Frank Wanlass | Fairchild Semiconductor | [31][32] |

| 1968 | 20,000 nm | 100 nm | ? | RCA Laboratories | [33] |

| 1970 | 10,000 nm | 100 nm | ? | RCA Laboratories | [33] |

| 1976-12 | 2,000 nm | ? | A. Aitken, R.G. Poulsen, A.T.P. MacArthur, J.J. White | Mitel Semiconductor | [34] |

| 1978-02 | 3,000 nm | ? | Toshiaki Masuhara, Osamu Minato, Toshio Sasaki, Yoshio Sakai | Hitachi Central Research Laboratory | [35][36][37] |

| 1983-02 | 1,200 nm | 25 nm | R.J.C. Chwang, M. Choi, D. Creek, S. Stern, P.H. Pelley | Intel | [38][39] |

| 900 nm | 15 nm | Tsuneo Mano, J. Yamada, Junichi Inoue, S. Nakajima | Nippon Telegraph and Telephone (NTT) | [38][40] | |

| 1983-12 | 1,000 nm | 22.5 nm | G.J. Hu, Yuan Taur, Robert H. Dennard, Chung-Yu Ting | IBM T.J. Watson Research Center | [41] |

| 1987-02 | 800 nm | 17 nm | T. Sumi, Tsuneo Taniguchi, Mikio Kishimoto, Hiroshige Hirano | Matsushita | [38][42] |

| 700 nm | 12 nm | Tsuneo Mano, J. Yamada, Junichi Inoue, S. Nakajima | Nippon Telegraph and Telephone (NTT) | [38][43] | |

| 1987-09 | 500 nm | 12.5 nm | Hussein I. Hanafi, Robert H. Dennard, Yuan Taur, Nadim F. Haddad | IBM T.J. Watson Research Center | [44] |

| 1987-12 | 250 nm | ? | Naoki Kasai, Nobuhiro Endo, Hiroshi Kitajima | NEC | [45] |

| 1988-02 | 400 nm | 10 nm | M. Inoue, H. Kotani, T. Yamada, Hiroyuki Yamauchi | Matsushita | [38][46] |

| 1990-12 | 100 nm | ? | Ghavam G. Shahidi, Bijan Davari, Yuan Taur, James D. Warnock | IBM T.J. Watson Research Center | [47] |

| 1993 | 350 nm | ? | ? | Sony | [48] |

| 1996 | 150 nm | ? | ? | Mitsubishi Electric | |

| 1998 | 180 nm | ? | ? | TSMC | [49] |

| 2003-12 | 5 nm | ? | Hitoshi Wakabayashi, Shigeharu Yamagami, Nobuyuki Ikezawa | NEC | [50][51] |

See also[edit]

- Active pixel sensor (CMOS sensor)

- Beyond CMOS

- CMOS amplifier

- Electric (software) – used to lay out CMOS circuits

- FEOL (front-end-of-line) – the first part of IC fabrication process

- Gate equivalent – a technology-independent measure of circuit complexity

- HCMOS – high-speed CMOS 1982

- LVCMOS

- Magic (software) – used to lay out CMOS circuits

- List of MOSFET applications

- sCMOS

- Thermal oxidation

References[edit]

- ↑ What is CMOS Memory?

- ↑ (2013) High-Frequency Integrated Circuits. Cambridge University Press, 164. ISBN 9780521873024.

- ↑ 3.0 3.1 3.2 1960: Metal Oxide Semiconductor (MOS) Transistor Demonstrated. The Silicon Engine: A Timeline of Semiconductors in Computers. {{{issue}}}

- ↑ 4.0 4.1 (2007) History of Semiconductor Engineering. Springer Science & Business Media, 321–3. ISBN 9783540342588.

- ↑ (2013) High-Frequency Integrated Circuits. Cambridge University Press, 164. ISBN 978-0521873024.

- ↑ Evolution of the MOS transistor-from conception to VLSI. Proceedings of the IEEE. 76 (10): 1280–1326 (1290). doi:10.1109/5.16328

- ↑ 7.0 7.1 1963: Complementary MOS Circuit Configuration is Invented

- ↑ 8.0 8.1 Nanowatt logic using field-effect metal-oxide semiconductor triodes. 1963 IEEE International Solid-State Circuits Conference. Digest of Technical Papers. VI ({{{issue}}}): 32–33. doi:10.1109/ISSCC.1963.1157450

- ↑ Low stand-by power complementary field effect circuitry

- ↑ (2007) History of Semiconductor Engineering. Springer Science & Business Media, 330. ISBN 9783540342588.

- ↑ (1990) Microcosm: The Quantum Revolution In Economics And Technology. Simon and Schuster, 144–5. ISBN 9780671705923.

- ↑ 1972 to 1973: CMOS LSI circuits for calculators (Sharp and Toshiba)

- ↑ Early 1970s: Evolution of CMOS LSI circuits for watches

- ↑ 14.0 14.1 Tortoise of Transistors Wins the Race - CHM Revolution

- ↑ 15.0 15.1 15.2 15.3 15.4 15.5 1978: Double-well fast CMOS SRAM (Hitachi)

- ↑ 16.0 16.1 16.2 16.3 (2018) "CMOS and Beyond CMOS: Scaling Challenges", High Mobility Materials for CMOS Applications. Woodhead Publishing, 1. ISBN 9780081020623.

- ↑ CDP 1800 μP Commercially available. Microcomputer Digest. 2 (4): 1–3

- ↑ Silicon Gate MOS 2102A

- ↑ 19.0 19.1 A chronological list of Intel products. The products are sorted by date.

- ↑ A high-speed, low-power Hi-CMOS 4K static RAM. 1978 IEEE International Solid-State Circuits Conference. Digest of Technical Papers. XXI ({{{issue}}}): 110–111. doi:10.1109/ISSCC.1978.1155749

- ↑ Short Channel Hi-CMOS Device and Circuits. ESSCIRC 78: 4th European Solid State Circuits Conference - Digest of Technical Papers. {{{issue}}}: 131–132

- ↑ 22.0 22.1 Impact of Processing Technology on DRAM Sense Amplifier Design

- ↑ 23.0 23.1 23.2 IEEE Andrew S. Grove Award Recipients

- ↑ A high-performance 0.25 micrometer CMOS technology. International Electron Devices Meeting. {{{issue}}}. doi:10.1109/IEDM.1988.32749

- ↑ 25.0 25.1 Memory

- ↑ Atomic layer doping apparatus and method

- ↑ Toshiba and Sony Make Major Advances in Semiconductor Process Technologies

- ↑ A Banner Year: TSMC Annual Report 2004

- ↑ Global FinFET Technology Market 2024 Growth Analysis by Manufacturers, Regions, Type and Application, Forecast Analysis

- ↑ Angstrom

- ↑ 1963: Complementary MOS Circuit Configuration is Invented

- ↑ Nanowatt logic using field-effect metal–oxide semiconductor triodes. 1963 IEEE International Solid-State Circuits Conference. Digest of Technical Papers. p. 32–33. doi:10.1109/ISSCC.1963.1157450

- ↑ 33.0 33.1 (2007) History of Semiconductor Engineering. Springer Science & Business Media, 330. ISBN 9783540342588.

- ↑ 1976 International Electron Devices Meeting. 1976 International Electron Devices Meeting. p. 209–213. doi:10.1109/IEDM.1976.189021

- ↑ 1978: Double-well fast CMOS SRAM (Hitachi)

- ↑ 1978 IEEE International Solid-State Circuits Conference. Digest of Technical Papers. 1978 IEEE International Solid-State Circuits Conference. Digest of Technical Papers. p. 110–111. doi:10.1109/ISSCC.1978.1155749

- ↑ Short Channel Hi-CMOS Device and Circuits. ESSCIRC 78: 4th European Solid State Circuits Conference – Digest of Technical Papers. {{{issue}}}: 131–132

- ↑ 38.0 38.1 38.2 38.3 38.4 Impact of Processing Technology on DRAM Sense Amplifier Design

- ↑ (February 1983) "A 70ns high density CMOS DRAM", 1983 IEEE International Solid-State Circuits Conference. Digest of Technical Papers XXVI, 56–57. doi:10.1109/ISSCC.1983.1156456.

- ↑ (February 1983) "Submicron VLSI memory circuits", 1983 IEEE International Solid-State Circuits Conference. Digest of Technical Papers XXVI, 234–235. doi:10.1109/ISSCC.1983.1156549.

- ↑ (December 1983) "A self-aligned 1-μm CMOS technology for VLSI", 1983 International Electron Devices Meeting, 739–741. doi:10.1109/IEDM.1983.190615.

- ↑ (1987) "A 60ns 4Mb DRAM in a 300mil DIP", 1987 IEEE International Solid-State Circuits Conference. Digest of Technical Papers XXX, 282–283. doi:10.1109/ISSCC.1987.1157106.

- ↑ (1987) "Circuit technologies for 16Mb DRAMs", 1987 IEEE International Solid-State Circuits Conference. Digest of Technical Papers XXX, 22–23. doi:10.1109/ISSCC.1987.1157158.

- ↑ 0.5 μm CMOS Device Design and Characterization. ESSDERC '87: 17th European Solid State Device Research Conference. {{{issue}}}: 91–94

- ↑ (December 1987) "0.25 μm CMOS technology using P+polysilicon gate PMOSFET", 1987 International Electron Devices Meeting, 367–370. doi:10.1109/IEDM.1987.191433.

- ↑ (1988) "A 16mb Dram with an Open Bit-Line Architecture", 1988 IEEE International Solid-State Circuits Conference, 1988 ISSCC. Digest of Technical Papers, 246–. doi:10.1109/ISSCC.1988.663712.

- ↑ Fabrication of CMOS on ultrathin SOI obtained by epitaxial lateral overgrowth and chemical-mechanical polishing. International Technical Digest on Electron Devices. {{{issue}}}: 587–590. doi:10.1109/IEDM.1990.237130

- ↑ Memory

- ↑ 0.18-micron Technology

- ↑ (December 2003) "Sub-10-nm planar-bulk-CMOS devices using lateral junction control", IEEE International Electron Devices Meeting 2003, 20.7.1–20.7.3. doi:10.1109/IEDM.2003.1269446. ISBN 0-7803-7872-5.

- ↑ NEC test-produces world's smallest transistor

Further reading[edit]

- Baker, R. Jacob (2010). CMOS: Circuit Design, Layout, and Simulation, Third Edition. Wiley-IEEE, 1174. ISBN 978-0-470-88132-3.

- (2010) CMOS VLSI Design: A Circuits and Systems Perspective, Fourth Edition. Boston: Pearson/Addison-Wesley, 840. ISBN 978-0-321-54774-3.

- Veendrick, H. J. M. (2017). Nanometer CMOS ICs: From Basics to ASICs. Springer, 770. doi:10.1007/978-3-319-47597-4. ISBN 978-3-319-47595-0.

- Mead, Carver A. and Conway, Lynn (1980). Introduction to VLSI systems. Boston: Addison-Wesley. ISBN 0-201-04358-0.

External links[edit]

- CMOS gate description and interactive illustrations

- LASI is a "general purpose" IC layout CAD tool. It is a free download and can be used as a layout tool for CMOS circuits.