From WikiChip

Zen 4 - Microarchitectures - AMD

| Edit Values | |

| Zen 4 µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | AMD |

| Manufacturer | TSMC |

| Process | 5nm, 6nm |

| Succession | |

Zen 4 is a microarchitecture developed by AMD as a successor to Zen 3. See press release for details: AMD Launches Ryzen 7000 Series Desktop Processors

Contents

History

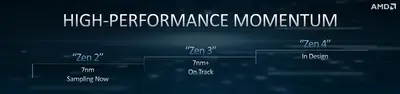

Zen 4 was first mentioned by Forrest Norrod during AMD's EPYC One Year Anniversary webinar. During the next horizon event which was held on November 6, 2018, AMD stated that Zen 4 was at the design completion phase.

Codenames

Product Codenames:

| Core | C/T | Target |

|---|---|---|

| Bergamo | Up to 128/256 | High-performance CSP server multiprocessors |

| Genoa | Up to 96/192 | High-end server multiprocessors |

| Storm Peak | Up to 64/128 | Workstation & enthusiasts market processors |

| Raphael | Up to 16/32 | Mainstream to high-end desktops & enthusiasts market processors |

| Dragon Range | Up to 16/32 | High-end mobile processors with GPU |

| Phoenix Point | Up to 8/16 | Mainstream desktop & mobile processors with GPU |

Architectural Codenames:

| Arch | Codename |

|---|---|

| Core | Persephone |

| CCD | Durango |

Products

| Processor Series | Cores/Threads | Market |

|---|---|---|

| EPYC 9004 "Genoa" | Up to 96/192 | High-end server multiprocessors |

| Ryzen Threadripper 7000 "Storm Peak" | Up to 96/192 | Workstation & enthusiasts market processors |

| Ryzen 7000 "Raphael" | Up to 16/32 | Mainstream to high-end desktops & enthusiasts market processors |

| Ryzen 7000 APU "Dragon Range" | Up to 16/32 | High-end mobile processors with GPU |

| Ryzen 7000 APU "Phoenix Point" | Up to 8/16 | Mainstream desktop & mobile processors with GPU |

Cores using variant Zen 4 uarch:

| Processor Series | Cores/Threads | Market |

|---|---|---|

| EPYC 9004 Bergamo | Up to 128/256 | Cloud multiprocessors (smaller, almost half-size Zen 4c [referred to as “Zen 4D” in leaks] core sacrificing half of the L3 cache.) |

Process Technology

Zen 4 is fabricated using both the 5nm node for the Core Compute Die (CCD) and the 6nm node for the Input/Output Die (IOD) by TSMC.

Architecture

Key changes from Zen 3

- Core

- AVX-512 instructions support (256-bit datapaths[1])

- L1 and L2 DTLB size increased from 64 to 72 and 2,048 to 3,072 entries

- L2 cache doubled from 512 KiB to 1 MiB per core

- Max. physical and linear address size raised from 48 to 52 and 57 bits respectively

- Improved cache load, write and prefetch from/to register (less latency)

- Higher Transistor Density, due to 5nm process

- Capable of higher all-core clockspeeds (shown by AMD to reach 5GHz+ on all cores)

- Larger integer register file (from 192 to 224), floating-point register file (from 160 to 192) and reorder buffer (from 256 to 320 entries)

- Package

- Raised maximum core/thread count from 64/128 to at least 96/192 (EPYC 9004) (Bergamo supports 128 cores but preliminary data shows a slightly altered architecture featuring cores that take up less space)

- Support for DDR5 memory and PCIe Gen 5

- New sockets AM5 (client), SP5 (server), SP6 (server), FP7/FP7r2 (mobile)

- RDNA2-based iGPU with 2 compute units (128 stream processors)

New Instructions

Zen 4 introduced the following ISA enhancements:

- AVX-512 - 512-bit Vector Instructions

- AVX512F - Foundation (first introduced with Intel Skylake)

- AVX512CD - Conflict Detection Instructions (Skylake X)

- AVX512VL - Vector Length Extensions (Skylake X)

- AVX512DQ - Doubleword and Quadword Instructions (Skylake X)

- AVX512BW - Byte and Word Instructions (Skylake X)

- AVX512 IFMA - Integer Fused Multiply-Add (Cannon Lake)

- AVX512 VBMI - Vector Bit Manipulation Instructions (Cannon Lake)

- AVX512 VPOPCNTDQ - Vector Population Count Instruction (Ice Lake)

- AVX512 BITALG - Bit Algorithms (Ice Lake)

- AVX512 VBMI2 - Vector Bit Manipulation Instructions 2 (Ice Lake)

- AVX512 VNNI - Vector Neural Network Instructions (Ice Lake)

- AVX512 BF16 - BFloat16 Instructions (Cooper Lake)

- Not supported: AVX512ER, AVX512PF (Knights Landing); AVX512 4VNNIW, 4FMAPS (Knights Mill); VP2INTERSECT (Tiger Lake)

- GFNI - Galois Field New Instructions (first introduced with Intel Ice Lake)

-

VGF2P8AFFINEQB- Galois field affine transformation -

VGF2P8AFFINEINVQB- Galois field affine transformation inverse -

VGF2P8MULB- Galois field multiply bytes

-

Memory Hierarchy

Data and Instruction Caches

- L0 Op Cache:

- 6.75K[1] Ops per core, 8-way(?) set associative

- 9 Op line size(?)

- Parity protected

- L1I Cache:

- 32 KiB per core, 8-way set associative

- 64 B line size

- Parity protected

- L1D Cache:

- 32 KiB per core, 8-way set associative

- 64 B line size

- Write-back policy

- ? cycles latency for Int

- ? cycles latency for FP

- ECC

- L2 Cache:

- 1 MiB per core, 8-way set associative

- 64 B line size

- Write-back policy

- Inclusive of L1(?)

- 14 cycles latency

- DEC-TED ECC, tag & state arrays SEC-DED

- L3 Cache:

- Shared by all cores in the CCX, configurable

- 16-way set associative

- 64 B line size

- L2 victim cache(?)

- Write-back policy

- 50 cycles average load-to-use latency

- DEC-TED ECC, tag array & shadow tags SEC-DED

- QoS Monitoring and Enforcement

Translation Lookaside Buffers

- ITLB

- 64 entry L1 TLB, fully associative, all page sizes

- 512 entry L2 TLB, ?-way set associative

- 4-Kbyte, 2-Mbyte, and 4-Mbyte pages

- Parity protected

- DTLB

- 72 entry L1 TLB, fully associative, all page sizes

- 3,072 entry L2 TLB, 12-way set associative

- 4-Kbyte, 2-Mbyte, and 4-Mbyte pages, PDEs to speed up table walks(?)

- Parity protected

4-Mbyte pages require two 2-Mbyte entries in all TLBs.

System DRAM

Sources: [2]

All Zen 4 Processors

| List of all Zen 4-based Processors | ||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Model | Family | Codename | C | T | L2 | L3 | Base | Turbo | Memory | TDP | Launched | Price | OPN | |

| Uniprocessors | ||||||||||||||

| 7600X | Ryzen 5 | Raphael | 6 | 12 | 6 MiB 6,144 KiB 6,291,456 B 0.00586 GiB | 32 MiB 32,768 KiB 33,554,432 B 0.0313 GiB | 4.7 GHz 4,700 MHz 4,700,000 kHz | 5.3 GHz 5,300 MHz 5,300,000 kHz | 105 W 105,000 mW 0.141 hp 0.105 kW | |||||

| 7700 | Ryzen 7 | Raphael | 8 | 16 | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 32 MiB 32,768 KiB 33,554,432 B 0.0313 GiB | 3.8 GHz 3,800 MHz 3,800,000 kHz | 5.3 GHz 5,300 MHz 5,300,000 kHz | 65 W 65,000 mW 0.0872 hp 0.065 kW | 10 January 2023 | $ 339.00 € 305.10 £ 274.59 ¥ 35,028.87 | 100-000000592, 100-100000592BOX | ||

| 7700X | Ryzen 7 | Raphael | 8 | 16 | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 32 MiB 32,768 KiB 33,554,432 B 0.0313 GiB | 4.5 GHz 4,500 MHz 4,500,000 kHz | 5.4 GHz 5,400 MHz 5,400,000 kHz | 105 W 105,000 mW 0.141 hp 0.105 kW | 27 September 2022 | $ 399.00 € 359.10 £ 323.19 ¥ 41,228.67 | 100-000000591, 100-100000591WOF | ||

| 7800X3D | Ryzen 7 | Raphael | 8 | 16 | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 96 MiB 98,304 KiB 100,663,296 B 0.0938 GiB | 4.2 GHz 4,200 MHz 4,200,000 kHz | 5 GHz 5,000 MHz 5,000,000 kHz | 120 W 120,000 mW 0.161 hp 0.12 kW | |||||

| 7900X3D | Ryzen 9 | Raphael | 12 | 24 | 12 MiB 12,288 KiB 12,582,912 B 0.0117 GiB | 128 MiB 131,072 KiB 134,217,728 B 0.125 GiB | 4.4 GHz 4,400 MHz 4,400,000 kHz | 5.6 GHz 5,600 MHz 5,600,000 kHz | 120 W 120,000 mW 0.161 hp 0.12 kW | |||||

| 7950X3D | Ryzen 9 | Raphael | 16 | 32 | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 128 MiB 131,072 KiB 134,217,728 B 0.125 GiB | 4.2 GHz 4,200 MHz 4,200,000 kHz | 5.7 GHz 5,700 MHz 5,700,000 kHz | 120 W 120,000 mW 0.161 hp 0.12 kW | 28 February 2023 | $ 699.00 € 629.10 £ 566.19 ¥ 72,227.67 | 100-000000908, 100-000000908WOF | ||

| 9354P | EPYC | Genoa | 32 | 64 | 32 MiB 32,768 KiB 33,554,432 B 0.0313 GiB | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 3.25 GHz 3,250 MHz 3,250,000 kHz | 3.75 GHz 3,750 MHz 3,750,000 kHz | DDR5-4800 | 280 W 280,000 mW 0.375 hp 0.28 kW | 10 November 2022 | $ 2,730.00 € 2,457.00 £ 2,211.30 ¥ 282,090.90 | 100-100000805, 100-100000805WOF | |

| 9454P | EPYC | Genoa | 48 | 96 | 48 MiB 49,152 KiB 50,331,648 B 0.0469 GiB | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 2.75 GHz 2,750 MHz 2,750,000 kHz | 3.65 GHz 3,650 MHz 3,650,000 kHz | DDR5-4800 | 290 W 290,000 mW 0.389 hp 0.29 kW | 10 November 2022 | $ 4,598.00 € 4,138.20 £ 3,724.38 ¥ 475,111.34 | 100-100000873, 100-100000873WOF | |

| 9554P | EPYC | Genoa | 64 | 128 | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 3.1 GHz 3,100 MHz 3,100,000 kHz | 3.75 GHz 3,750 MHz 3,750,000 kHz | DDR5-4800 | 360 W 360,000 mW 0.483 hp 0.36 kW | 10 November 2022 | $ 7,104.00 € 6,393.60 £ 5,754.24 ¥ 734,056.32 | 100-100000804, 100-100000804WOF | |

| 9654P | EPYC | Genoa | 96 | 192 | 96 MiB 98,304 KiB 100,663,296 B 0.0938 GiB | 384 MiB 393,216 KiB 402,653,184 B 0.375 GiB | 2.4 GHz 2,400 MHz 2,400,000 kHz | 3.55 GHz 3,550 MHz 3,550,000 kHz | DDR5-4800 | 360 W 360,000 mW 0.483 hp 0.36 kW | 10 November 2022 | $ 10,625.00 € 9,562.50 £ 8,606.25 ¥ 1,097,881.25 | 100-100000803, 100-100000803WOF | |

| Multiprocessors (dual-socket) | ||||||||||||||

| 9124 | EPYC | Genoa | 16 | 32 | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 3 GHz 3,000 MHz 3,000,000 kHz | 3.6 GHz 3,600 MHz 3,600,000 kHz | DDR5-4800 | 200 W 200,000 mW 0.268 hp 0.2 kW | 10 November 2022 | $ 1,083.00 € 974.70 £ 877.23 ¥ 111,906.39 | 100-100000802, 100-100000802WOF | |

| 9174F | EPYC | Genoa | 16 | 32 | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 4.1 GHz 4,100 MHz 4,100,000 kHz | 4.15 GHz 4,150 MHz 4,150,000 kHz | DDR5-4800 | 320 W 320,000 mW 0.429 hp 0.32 kW | 10 November 2022 | $ 3,850.00 € 3,465.00 £ 3,118.50 ¥ 397,820.50 | 100-100000796, 100-100000796WOF | |

| 9224 | EPYC | Genoa | 24 | 48 | 24 MiB 24,576 KiB 25,165,824 B 0.0234 GiB | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 2.5 GHz 2,500 MHz 2,500,000 kHz | 3.65 GHz 3,650 MHz 3,650,000 kHz | DDR5-4800 | 200 W 200,000 mW 0.268 hp 0.2 kW | 10 November 2022 | $ 1,825.00 € 1,642.50 £ 1,478.25 ¥ 188,577.25 | 100-100000939, 100-100000939WOF | |

| 9254 | EPYC | Genoa | 24 | 48 | 24 MiB 24,576 KiB 25,165,824 B 0.0234 GiB | 128 MiB 131,072 KiB 134,217,728 B 0.125 GiB | 2.9 GHz 2,900 MHz 2,900,000 kHz | 3.9 GHz 3,900 MHz 3,900,000 kHz | DDR5-4800 | 200 W 200,000 mW 0.268 hp 0.2 kW | 10 November 2022 | $ 2,299.00 € 2,069.10 £ 1,862.19 ¥ 237,555.67 | 100-100000480, 100-100000480WOF | |

| 9274F | EPYC | Genoa | 24 | 48 | 24 MiB 24,576 KiB 25,165,824 B 0.0234 GiB | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 4.05 GHz 4,050 MHz 4,050,000 kHz | 4.1 GHz 4,100 MHz 4,100,000 kHz | DDR5-4800 | 320 W 320,000 mW 0.429 hp 0.32 kW | 10 November 2022 | $ 3,060.00 € 2,754.00 £ 2,478.60 ¥ 316,189.80 | 100-100000794, 100-100000794WOF | |

| 9334 | EPYC | Genoa | 32 | 64 | 32 MiB 32,768 KiB 33,554,432 B 0.0313 GiB | 128 MiB 131,072 KiB 134,217,728 B 0.125 GiB | 2.7 GHz 2,700 MHz 2,700,000 kHz | 3.85 GHz 3,850 MHz 3,850,000 kHz | DDR5-4800 | 210 W 210,000 mW 0.282 hp 0.21 kW | 10 November 2022 | $ 2,990.00 € 2,691.00 £ 2,421.90 ¥ 308,956.70 | 100-100000800, 100-100000800WOF | |

| 9354 | EPYC | Genoa | 32 | 64 | 32 MiB 32,768 KiB 33,554,432 B 0.0313 GiB | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 3.25 GHz 3,250 MHz 3,250,000 kHz | 3.75 GHz 3,750 MHz 3,750,000 kHz | DDR5-4800 | 280 W 280,000 mW 0.375 hp 0.28 kW | 10 November 2022 | $ 3,420.00 € 3,078.00 £ 2,770.20 ¥ 353,388.60 | 100-100000798, 100-100000798WOF | |

| 9374F | EPYC | Genoa | 32 | 64 | 32 MiB 32,768 KiB 33,554,432 B 0.0313 GiB | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 3.85 GHz 3,850 MHz 3,850,000 kHz | 4.1 GHz 4,100 MHz 4,100,000 kHz | DDR5-4800 | 320 W 320,000 mW 0.429 hp 0.32 kW | 10 November 2022 | $ 4,850.00 € 4,365.00 £ 3,928.50 ¥ 501,150.50 | 100-100000792, 100-100000792WOF | |

| 9454 | EPYC | Genoa | 48 | 96 | 48 MiB 49,152 KiB 50,331,648 B 0.0469 GiB | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 2.75 GHz 2,750 MHz 2,750,000 kHz | 3.65 GHz 3,650 MHz 3,650,000 kHz | DDR5-4800 | 290 W 290,000 mW 0.389 hp 0.29 kW | 10 November 2022 | $ 5,225.00 € 4,702.50 £ 4,232.25 ¥ 539,899.25 | 100-100000478, 100-100000478WOF | |

| 9474F | EPYC | Genoa | 48 | 96 | 48 MiB 49,152 KiB 50,331,648 B 0.0469 GiB | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 3.6 GHz 3,600 MHz 3,600,000 kHz | 3.95 GHz 3,950 MHz 3,950,000 kHz | DDR5-4800 | 360 W 360,000 mW 0.483 hp 0.36 kW | 10 November 2022 | $ 6,780.00 € 6,102.00 £ 5,491.80 ¥ 700,577.40 | 100-100000788, 100-100000788WOF | |

| 9534 | EPYC | Genoa | 64 | 128 | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 2.45 GHz 2,450 MHz 2,450,000 kHz | 3.55 GHz 3,550 MHz 3,550,000 kHz | DDR5-4800 | 280 W 280,000 mW 0.375 hp 0.28 kW | 10 November 2022 | $ 8,803.00 € 7,922.70 £ 7,130.43 ¥ 909,613.99 | 100-100000799, 100-100000799WOF | |

| 9554 | EPYC | Genoa | 64 | 128 | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 3.1 GHz 3,100 MHz 3,100,000 kHz | 3.75 GHz 3,750 MHz 3,750,000 kHz | DDR5-4800 | 360 W 360,000 mW 0.483 hp 0.36 kW | 10 November 2022 | $ 9,087.00 € 8,178.30 £ 7,360.47 ¥ 938,959.71 | 100-100000790, 100-100000790WOF | |

| 9634 | EPYC | Genoa | 84 | 168 | 84 MiB 86,016 KiB 88,080,384 B 0.082 GiB | 384 MiB 393,216 KiB 402,653,184 B 0.375 GiB | 2.25 GHz 2,250 MHz 2,250,000 kHz | 3.1 GHz 3,100 MHz 3,100,000 kHz | DDR5-4800 | 290 W 290,000 mW 0.389 hp 0.29 kW | 10 November 2022 | $ 10,304.00 € 9,273.60 £ 8,346.24 ¥ 1,064,712.32 | 100-100000797, 100-100000797WOF | |

| 9654 | EPYC | Genoa | 96 | 192 | 96 MiB 98,304 KiB 100,663,296 B 0.0938 GiB | 384 MiB 393,216 KiB 402,653,184 B 0.375 GiB | 2.4 GHz 2,400 MHz 2,400,000 kHz | 3.55 GHz 3,550 MHz 3,550,000 kHz | DDR5-4800 | 360 W 360,000 mW 0.483 hp 0.36 kW | 10 November 2022 | $ 11,805.00 € 10,624.50 £ 9,562.05 ¥ 1,219,810.65 | 100-100000789, 100-100000789WOF | |

| Count: 24 | ||||||||||||||

Designers

- Mike Clark(?), chief architect

Bibliography

References

- ↑ 1.0 1.1 "Ryzen 7000 Desktop Preview", Angstronomics, August 29, 2022

- ↑ "Processor Programming Reference (PPR) for AMD Family 19h Models 10h, Revision A0 Processors", AMD Publ. #55901, Rev. 0.97, May 30, 2021

See Also

- AMD Zen, Zen 2, Zen 3

- Intel Meteor Lake

Facts about "Zen 4 - Microarchitectures - AMD"

| codename | Zen 4 + |

| designer | AMD + |

| full page name | amd/microarchitectures/zen 4 + |

| instance of | microarchitecture + |

| manufacturer | TSMC + |

| microarchitecture type | CPU + |

| name | Zen 4 + |