| Edit Values | |

| Socket AM2+ | |

| General Info | |

| Designer | AMD |

| Introduction | November 19, 2007 (launched) |

| Market | Desktop |

| Microarchitecture | K10 |

| TDP | 140 W 140,000 mW 0.188 hp 0.14 kW |

| Package | |

| Name | OPGA-940 (AM2) |

| Type | Organic Micro Pin Grid Array |

| Contacts | 940 |

| Dimension | 40.0 mm 4 cm × 40.0 mm1.575 in 4 cm 1.575 in |

| Pitch | 1.27 mm 0.05 in |

| Socket | |

| Name | Socket AM2+ |

| Type | PGA |

Socket AM2+, also known as AM2r2, was the second socket for OPGA-940 and OPGA-938-packaged AMD microprocessors with an integrated DDR2 memory controller and the successor to Socket AM2. Socket AM2+ targets the desktop segment. Its contemporaries are Socket S1 for mobile processors and Socket F for the server and workstation market. For the small form factor desktop, mobile and embedded market AMD developed package ASB1. Socket AM2+ was superseded by Socket AM3.

The main improvements of Socket AM2+ over AM2 are support for HyperTransport generation 3.0 and separate core and northbridge power planes, a power saving feature. Socket AM2+ processors are compatible with the earlier Socket AM2, subject to the motherboard recognizing the CPU, limiting its HT link to generation 1.0 mode, and using a single power plane. The OPGA-940 package for Socket AM2+ has the same dimensions but is mechanically, due to keying, and electrically incompatible with Socket 939 for processors with a DDR memory controller, Socket 940 for first generation Opteron processors, and Socket AM3 and AM3+ for processors with a DDR3 memory controller.

Socket AM2 processors in the OPGA-940 package and Socket AM3 processors in the OPGA-938 package are compatible with Socket AM2+, subject to the motherboard recognizing the CPU and the limitations of Socket AM2+.

All processors for Socket AM2+ belong to AMD's Family 10h based on the K10 microarchitecture.

Contents

Features

- 940-pin lidded micro pin grid array package, 1.27 mm pitch, 31 × 31 pins, 40 × 40 mm, organic substrate

- 16 bit HyperTransport 3.0 interface up to 2.2 GHz, 4400 MT/s, 8.8 Gbyte/s in each direction

- 2 × 64/72 bit DDR2 SDRAM interface (ganged or unganged) up to 533 MHz, PC-8500 (DDR2-1066), 17.0 Gbyte/s

- Up to 4 UDIMMs (2 per channel), up to 4 Gbyte per UDIMM, SEC-DED ECC

- JEDEC SSTL_1.8

- P-States; ACPI C1, C1E, C2, C3, S1, S3, S5; dual power planes

- Thermal diode, overtemperature protection

Chipsets

- AMD 700 series

- Nvidia nForce 700 series, GeForce 8000 series

Processors using Socket AM2+

- AMD Phenom X4 "Agena", X3 "Toliman"

- AMD Athlon X2 "Kuma"

- AMD Athlon "Lima"

- AMD Sempron "Sparta"

| List of all Socket AM2+-based Processors | |||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Model | Price | Process | Launched | µarch | Family | Core | C | T | Freq | Turbo | TDP | ||||||||

| Count: 0 | |||||||||||||||||||

Package Diagram

No data available. Presumably same dimensions as the OPGA-940 package for Socket AM2.

Socket Outline

No data available. Presumably same dimensions as Socket AM2.

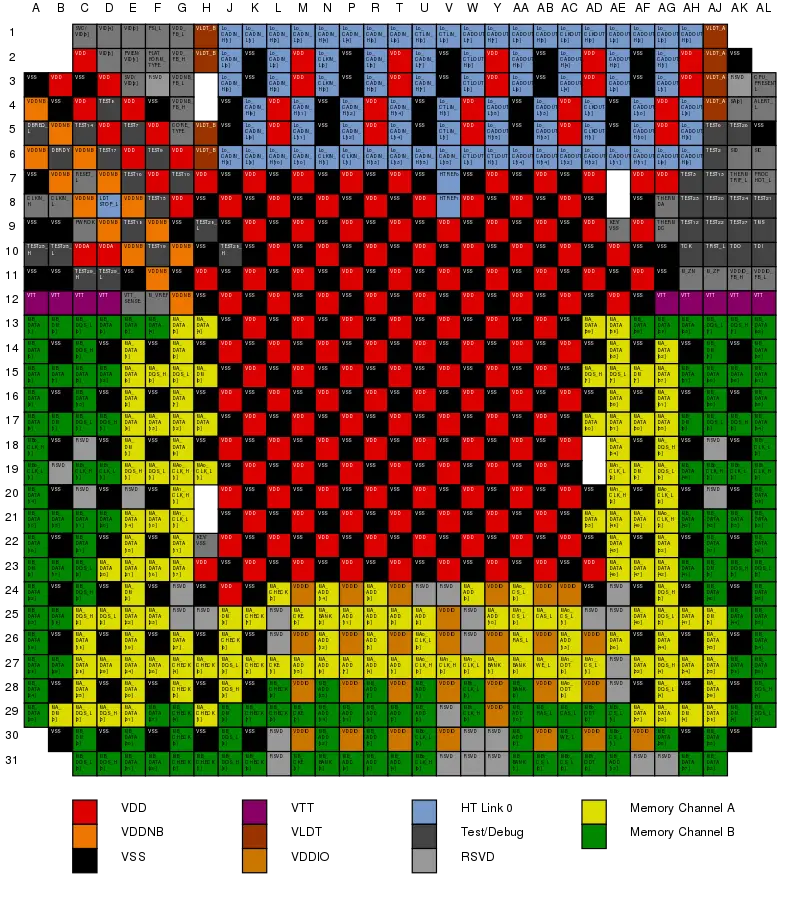

Pin Map

Socket AM2/AM2+ Differences

| Pin | Socket AM2 | Socket AM2+ |

|---|---|---|

| AL4 | RSVD | ALERT_L |

| G5 | RSVD | CORE_TYPE |

| AE9 | VSS | KEY/VSS |

| H22 | VSS | KEY/VSS |

| F2 | RSVD | PLATFORM_TYPE |

| AK4 | RSVD | SA[0] |

| E2 | VID[1] | PVIEN/VID[1] |

| E3 | VID[2] | SVD/VID[2] |

| C1 | VID[3] | SVC/VID[3] |

| A4 | VDD | VDDNB |

| A6 | VDD | VDDNB |

| B5 | VDD | VDDNB |

| B7 | VDD | VDDNB |

| C6 | VDD | VDDNB |

| C8 | VDD | VDDNB |

| D7 | VDD | VDDNB |

| D9 | VDD | VDDNB |

| E10 | VDD | VDDNB |

| E8 | VDD | VDDNB |

| F11 | VDD | VDDNB |

| F9 | VDD | VDDNB |

| G10 | VDD | VDDNB |

| G12 | VDD | VDDNB |

| G4 | RSVD | VDDNB_FB_H |

| G3 | RSVD | VDDNB_FB_L |

Pin Description

| Signal | Description |

|---|---|

| ALERT_L | Programmable pin that can indicate different events, including a SB-TSI interrupt |

| CLKIN_H/L | 200 MHz Differential PLL Reference Clock |

| CORE_TYPE | Indicates that the processor is capable of split core and northbridge voltage plane operation |

| CPU_PRESENT_L | Processor is present |

| DBREQ_L, DBRDY | Debug Request/Ready |

| HTREF0, HTREF1 | HyperTransport Compensation Resistor to VSS, VLDT |

| L0_CADIN/OUT_H/L[15:0] | HT Link 0 Differential Command/Address/Data Input/Output |

| L0_CLKIN/OUT_H/L[1:0] | HT Link 0 Differential Clock Input/Output |

| L0_CTLIN_H/L[1:0] | HT Link 0 Differential Control Input/Output |

| LDTSTOP_L | HT Stop Control Input for power management and link width and frequency change |

| MA0/MA1/MB0/MB1_CLK_H/L[2:0] | DRAM Differential Clock |

| MA0/MA1/MB0/MB1_CS_L[1:0] | DRAM Chip Select |

| MA0/MA1/MB0/MB1_ODT[0] | DRAM Enable Pin for On Die Termination |

| MA/MB_ADD[15:0] | DRAM Column/Row Address |

| MA/MB_BANK[2:0] | DRAM Bank Address |

| MA/MB_CAS_L | DRAM Column Address Strobe |

| MA/MB_CHECK[7:0] | DRAM ECC Bits |

| MA/MB_CKE[1:0] | DRAM Clock Enable |

| MA/MB_DATA[63:0] | DRAM Data Bus |

| MA/MB_DM[8:0] | DRAM Data Mask |

| MA/MB_DQS_H/L[8:0] | DRAM Differential Data Strobe |

| MA/MB_RAS_L | DRAM Row Address Strobe |

| MA/MB_WE_L | DRAM Write Enable |

| M_VREF | DRAM Interface Voltage Reference |

| M_ZP, M_ZN | Compensation Resistor to VSS, VDDIO |

| PLATFORM_TYPE | ? |

| PROCHOT_L | Processor in HTC-active state input/output |

| PSI_L | Power Status Indicator (low power state) for VDD regulator |

| PVIEN/VID[1] | Prior to PWROK assertion signals to the processor whether the platform supports PVI or SVI operation |

| PWROK | Voltages and CLKIN have reached specified operation |

| RESET_L | Processor Reset |

| RSVD | Reserved |

| SA[0] | Sideband interface (APML/SBI/SMBus) address selection |

| SIC, SID | Sideband Temperature Sensor Interface Clock, Data |

| SVD/VID[2] | Serial VID Interface Data |

| SVC/VID[3] | Serial VID Interface Clock |

| TCK, TDI, TDO, TMS, TRST_L | JTAG interface |

| TEST* | Test signal |

| THERMDA, THERMDC | Thermal Diode Anode, Cathode |

| THERMTRIP_L | Thermal Sensor Trip output |

| VDD | Core power supply |

| VDD_FB_H/L | Differential feedback to VDD regulator |

| VDDA | Filtered PLL supply voltage |

| VDDIO | DRAM I/O ring power supply |

| VDDIO_FB_H/L | Differential feedback to VDDIO regulator |

| VDDNB | Northbridge power supply |

| VDDNB_FB_H/L | Differential feedback to VDDNB regulator |

| VID[5:0] | Voltage ID (PVI) for VDD regulator |

| VLDT_A/B | HyperTransport I/O ring power supply |

| VSS | Ground |

| VTT | DRAM Termination voltage |

| VTT_SENSE | VTT monitor pin |

References

- "Socket AM2 Design Specification", AMD Publ. #31875, Rev. 3.00, May 2008

- "BIOS and Kernel Developer’s Guide (BKDG) For AMD Family 10h Processors", AMD Publ. #31116, Rev. 3.48, April 2010

- "Family 10h AMD Phenom™ Processor Product Data Sheet", AMD Publ. #44109, Rev. 3.00, November 2007

- "Revision Guide for AMD Family 10h Processors", AMD Publ. #41322, Rev. 3.92, March 2012

See also

| designer | AMD + |

| first launched | November 19, 2007 + |

| instance of | package + |

| market segment | Desktop + |

| microarchitecture | K10 + |

| name | Socket AM2+ + |

| package | OPGA-940 (AM2) + |

| package contacts | 940 + |

| package length | 40 mm (4 cm, 1.575 in) + |

| package pitch | 1.27 mm (0.05 in) + |

| package type | Organic Micro Pin Grid Array + |

| package width | 40 mm (4 cm, 1.575 in) + |

| socket | Socket AM2+ + |

| tdp | 140 W (140,000 mW, 0.188 hp, 0.14 kW) + |