| Edit Values | |

| Socket sWRX8 | |

| General Info | |

| Designer | AMD |

| Introduction | July 14, 2020 (launched) |

| Market | Workstation |

| Microarchitecture | Zen 2, Zen 3 |

| TDP | 280 W 280,000 mW 0.375 hp 0.28 kW |

| Package | |

| Name | sWRX8, FCLGA-4094 |

| Type | FC-OLGA |

| Contacts | 4094 |

| Dimension | 75.40 mm 7.54 cm × 58.50 mm2.969 in 5.85 cm × 6.26 mm2.303 in 0.246 in |

| Socket | |

| Name | sWRX8 |

| Type | SM-LGA |

| Succession | |

| Contemporary | |

| Socket sTRX4 Socket SP3 | |

Socket sWRX8 is a microprocessor socket designed by AMD for workstation versions of their third and fourth generation Ryzen Threadripper processors, the successor to Socket TR4. Contemporary mainstream desktop, HEDT, and server processors use Socket AM4, sTRX4, and SP3 respectively.

Socket sWRX8 is mechanically identical to Socket SP3 and the sockets TR4 and sTRX4 also derived from it. Electrically it differs minimally from Socket SP3 as well, in particular sWRX8 processors support UDIMMs in addition to RDIMMs, however this infrastructure is restricted to single socket systems with a maximum of one DIMM per memory channel. TR4 and sTRX4 processors support only UDIMMs on up to four memory channels, but up to two DIMMs per channel like Socket SP3, and omit four of eight PCIe interfaces present on Socket SP3 and sWRX8.

TR4 and sTRX4 processors are not supported on Socket sWRX8 or vice versa. If SP3 processors are compatible with sWRX8 platforms or vice versa, given suitable memory and firmware, is unclear.

Contents

Overview

Socket sWRX8 is a zero insertion force, screw actuated, surface-mount land grid array socket for use with a 4094-contact, 1.00 mm × 0.87 mm interstitial pitch, organic land grid array CPU package.

This single socket client infrastructure supports eight channels of 72-bit DDR4 memory with a maximum of one DIMM per channel, either UDIMMs or RDIMMs, eight 16-lane PCIe Gen 4 I/O links, four USB 3.2 Gen 2 ports, and up to 32 SATA Gen 3 ports. Due to the large number of high speed signals 12-layer motherboards are required, 14 layers recommended.

The following AMD processor families use Socket sWRX8:

| CPU Family | Microarch. | Process | Products | |

|---|---|---|---|---|

| Type 1 | Family 17h Models 30h–3Fh | Zen 2 | 7 nm & 12 nm | Ryzen Threadripper 3900 "Castle Peak" (Model 31h) |

| Type 2 | Family 19h Models 00h–0Fh | Zen 3 | 7 nm & 12 nm(?) | Ryzen Threadripper 5900 "Chagall" (Model 08h) |

Codenames of AMD sWRX8 reference platforms (CRBs) are "Cloudripper" and "Cloudripper DAP".

Package Description

The sWRX8 CPU package is lidded, has a 58.50 mm × 75.40 mm organic substrate with flip chip die attachment, and 4094 nickel and gold plated land pads. It ships with a carrier frame pre-installed. The carrier frame, made from an orange colored polycarbonate material, is a part of the package loading mechanism and remains on the package in the socket.

The package substrate has six keying notches along the short edges preventing it from being inserted 180 degrees rotated into the carrier frame or socket, or in an incompatible socket with mismatching keying features. Four additional positions are reserved for future models. However all sockets SP3, TR4, sTRX4, and sWRX8, and all processors for these sockets have the same keying. It is worth noting that these processors are also electrically keyed by pin SP3R1 and SP3R2. To boot the processor the motherboard must also provide compatible firmware. A triangular symbol on both sides of the substrate marks the location of pin A1, with corresponding markings on the socket. Decoupling capacitors are placed under the lid around the chiplets on the top side, and in two windows in the pad grid on the bottom side.

sWRX8 is a multi-chip package integrating one central I/O die and 4, 6, or 8 identical Core Complex Dies which contain eight CPU cores each. This silicon is "Starship" rev. SSP-B0 (CPU Family 17h) and "Genesis" GN-B1 (19h). AMD used the same chips for second and third generation EPYC server and embedded processors, and Ryzen Threadripper HEDT processors.

sWRX8 has the same memory and I/O interfaces, and the same on-package routing of signals as Socket SP3 Type-1/2 packages, with the differences noted above. The xGMI protocol and the WAFL interface, used to link processors on dual-socket platforms, are not supported on this socket. If sWRX8 processors are in fact EPYC 7002/7003 processors with different firmware and branding is unclear.

Socket Description

Socket sWRX8 is mechanically identical to Socket SP3.

Features

- Lidded land grid array package, 75.40 mm × 58.50 mm

- 4094 contacts in a 82 × 55 grid with 0.87 mm × 1.00 mm interstitial pitch

- Organic substrate, flip chip die attachment

- 8 × 64/72 bit DDR4 SDRAM interface

- Eight multi-function I/O interfaces P0-P3, G0-G3

Lane 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 PCIe x16 x8 x8 x4 x4 x4 x4 x2 x2 x2 x2 x2 x2 x2 x2 x1 x1 x1 x1 x1 x1 x1 x1 x1 x1 x1 x1 x1 x1 x1 x1 SATA 7 6 5 4 3 2 1 0 PHY 3 PHY 2 PHY 1 PHY 0

- PCIe Gen 1, 2, 3, 4 (16 GT/s) protocol supported on all interfaces

- 16 lanes, up to 8 ports per interface configurable x16, x8, x4, x2, x1 with power-of-two alignment (e.g. 1x4 + 4x1 + 1x8)

- Max. 7 PCIe ports in each 8-lane subset (e.g. 0x8 + 8x1 is not possible)

- Max. 7 PCIe ports per interface if any lane is configured as SATA port

- Different PCIe generations supported on the ports in the same interface

- Lane polarity inversion, per port lane reversal

- Up to 120 PCIe lanes total (one x8 link reserved for chipset attachment)

- PCIe Gen 1, 2, 3, 4 (16 GT/s) protocol supported on all interfaces

- SATA Gen 1, 2, 3 (6 Gb/s) protocol supported on the lower 8 lanes of P0, P1, G2, G3

- P0: SATA00-07, P1: SATA10-17, G2: SATA20-27, G3: SATA30-37

- Up to 32 SATA ports total

- SATA Gen 1, 2, 3 (6 Gb/s) protocol supported on the lower 8 lanes of P0, P1, G2, G3

- Four PHY groups on each interface

- Lanes sharing a PHY group must use the same protocol (PCIe, SATA)

- Four PHY groups on each interface

- 4 × USB 1.1, 2.0, 3.2 Gen 2×1 (10 Gb/s) ports

- Type-C connectors are supported with external components

- Low speed interfaces (some sharing pins):

Chipsets

sWRX8 processors are SoCs with an integrated controller hub so they do not require a chipset, but are paired with the AMD WRX80 chipset (AMD 500-Series) serving as I/O expander.

The chipset is attached with an x8 PCIe link and can provide the following additional interfaces:

- 16 lanes (+ 8-lane CPU link) PCIe Gen 1, 2, 3, 4 (16 GT/s)

- 8 × SATA Gen 1, 2, 3 (6 Gb/s) ports sharing pins with the PCIe interface

- 4 × SATA Gen 1, 2, 3 (6 Gb/s) ports, dedicated

- 8 × USB 1.1, 2.0, 3.2 Gen 2 (10 Gb/s) ports

- 5 × USB 1.1, 2.0 ports

An audio interface is not provided by Socket sWRX8 or the chipset, an audio controller is commonly attached as on-board USB device. The sWRX8/WRX80 platform does not support overclocking.

Processors using Socket sWRX8

| Model | Family | Microarch. | Cores | Threads | L2$ | L3$ | Base | Turbo | Memory | TDP | Launched | Price | OPN |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| PRO 3945WX | Ryzen Threadripper | Zen 2 | 12 | 24 | 6 MiB 6,144 KiB 6,291,456 B 0.00586 GiB | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 4 GHz 4,000 MHz 4,000,000 kHz | 4.3 GHz 4,300 MHz 4,300,000 kHz | DDR4-3200 | 280 W 280,000 mW 0.375 hp 0.28 kW | 14 July 2020 | 100-000000168 | |

| PRO 3955WX | Ryzen Threadripper | Zen 2 | 16 | 32 | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 3.9 GHz 3,900 MHz 3,900,000 kHz | 4.3 GHz 4,300 MHz 4,300,000 kHz | DDR4-3200 | 280 W 280,000 mW 0.375 hp 0.28 kW | 14 July 2020 | 100-000000167, 100-100000167WOF | |

| PRO 3975WX | Ryzen Threadripper | Zen 2 | 32 | 64 | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 128 MiB 131,072 KiB 134,217,728 B 0.125 GiB | 3.5 GHz 3,500 MHz 3,500,000 kHz | 4.2 GHz 4,200 MHz 4,200,000 kHz | DDR4-3200 | 280 W 280,000 mW 0.375 hp 0.28 kW | 14 July 2020 | 100-000000086, 100-100000086WOF | |

| PRO 3995WX | Ryzen Threadripper | Zen 2 | 64 | 128 | 32 MiB 32,768 KiB 33,554,432 B 0.0313 GiB | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 2.7 GHz 2,700 MHz 2,700,000 kHz | 4.2 GHz 4,200 MHz 4,200,000 kHz | DDR4-3200 | 280 W 280,000 mW 0.375 hp 0.28 kW | 14 July 2020 | 100-000000087, 100-100000087WOF | |

| PRO 5945WX | Ryzen Threadripper | Zen 3 | 12 | 24 | 6 MiB 6,144 KiB 6,291,456 B 0.00586 GiB | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 4.1 GHz 4,100 MHz 4,100,000 kHz | 4.5 GHz 4,500 MHz 4,500,000 kHz | DDR4-3200 | 280 W 280,000 mW 0.375 hp 0.28 kW | 8 March 2022 | 100-000000448 | |

| PRO 5955WX | Ryzen Threadripper | Zen 3 | 16 | 32 | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 4 GHz 4,000 MHz 4,000,000 kHz | 4.5 GHz 4,500 MHz 4,500,000 kHz | DDR4-3200 | 280 W 280,000 mW 0.375 hp 0.28 kW | 8 March 2022 | 100-000000447 | |

| PRO 5965WX | Ryzen Threadripper | Zen 3 | 24 | 48 | 12 MiB 12,288 KiB 12,582,912 B 0.0117 GiB | 128 MiB 131,072 KiB 134,217,728 B 0.125 GiB | 3.8 GHz 3,800 MHz 3,800,000 kHz | 4.5 GHz 4,500 MHz 4,500,000 kHz | DDR4-3200 | 280 W 280,000 mW 0.375 hp 0.28 kW | 8 March 2022 | 100-000000446 | |

| PRO 5975WX | Ryzen Threadripper | Zen 3 | 32 | 64 | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 128 MiB 131,072 KiB 134,217,728 B 0.125 GiB | 3.6 GHz 3,600 MHz 3,600,000 kHz | 4.5 GHz 4,500 MHz 4,500,000 kHz | DDR4-3200 | 280 W 280,000 mW 0.375 hp 0.28 kW | 8 March 2022 | 100-000000445 | |

| PRO 5995WX | Ryzen Threadripper | Zen 3 | 64 | 128 | 32 MiB 32,768 KiB 33,554,432 B 0.0313 GiB | 256 MiB 262,144 KiB 268,435,456 B 0.25 GiB | 2.7 GHz 2,700 MHz 2,700,000 kHz | 4.5 GHz 4,500 MHz 4,500,000 kHz | DDR4-3200 | 280 W 280,000 mW 0.375 hp 0.28 kW | 8 March 2022 | 100-000000444 | |

| Count: 9 |

Photos

| This section is empty; you can help add the missing info by editing this page. |

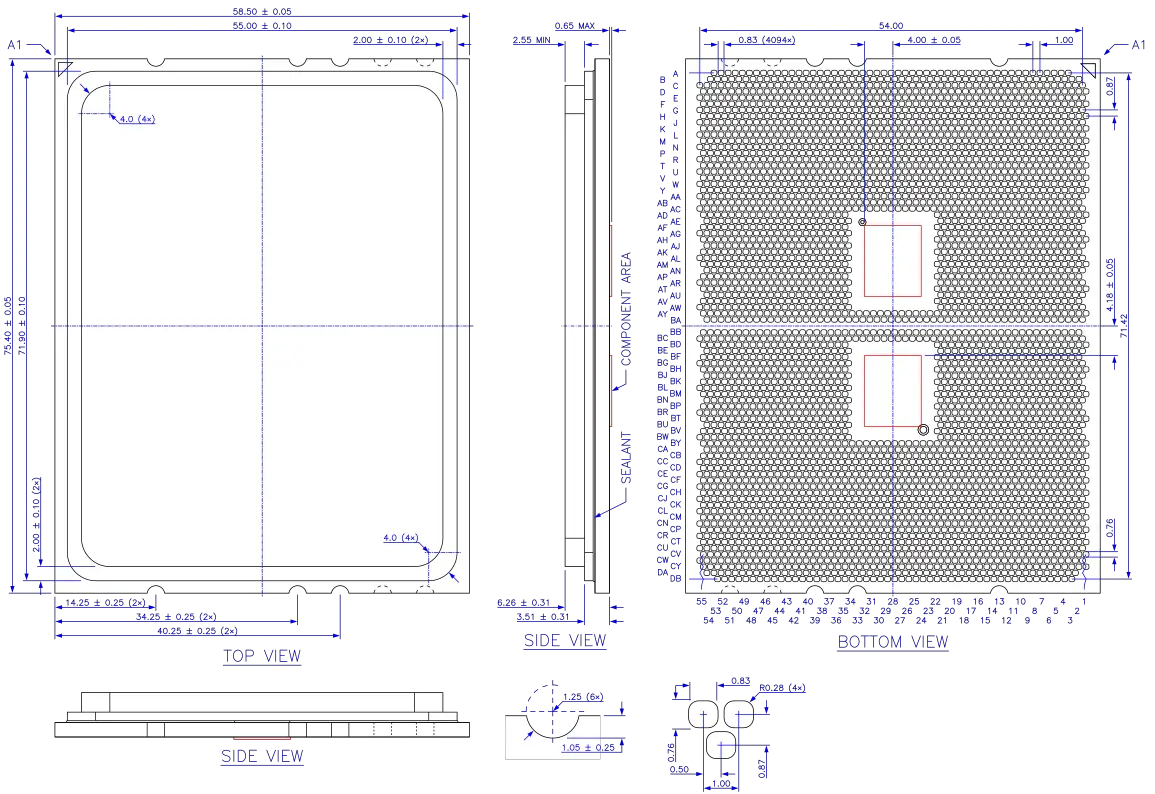

Package Diagram

sWRX8 package (same as Socket SP3 package). All dimensions in millimeters.

Socket Diagrams

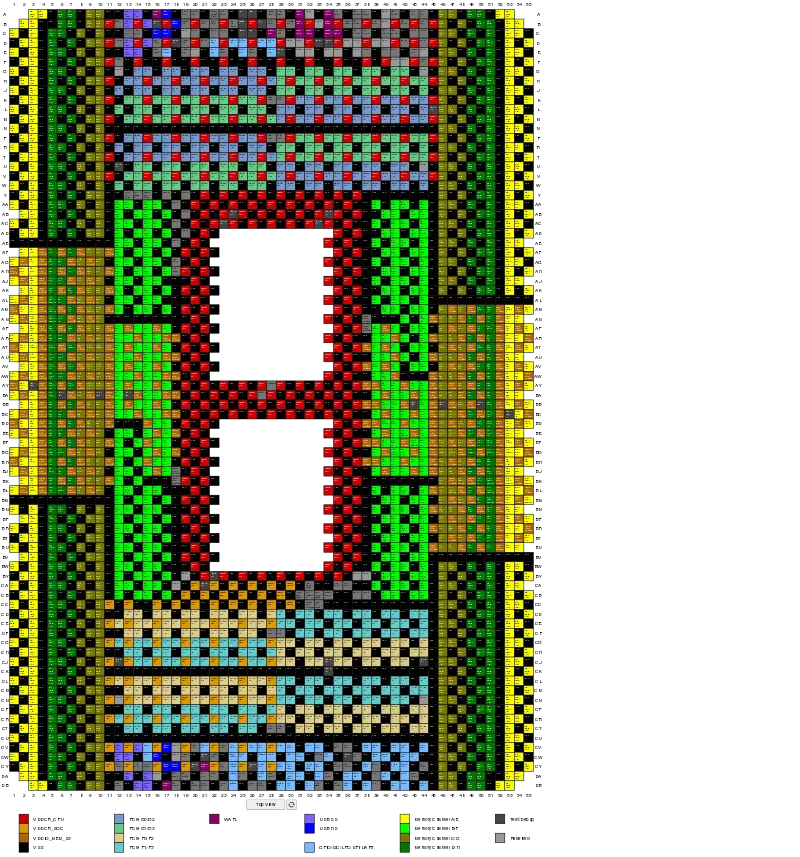

Pin Map

Socket sWRX8 pinout (same as Socket SP3, with some constraints), top view. This is a preview, click for a larger image and other views.

Pin Description

See Socket SP3.

Bibliography

- "Socket SP3 Design Specification", AMD Publ. #55260, Rev. 1.16, August 2020

- "Functional Data Sheet for sTRX4 and sWRX8 Processors", AMD Publ. #56515, Rev. 0.81, August 2019

- "Infrastructure Roadmap for sTRX4 and sWRX8 Processors", AMD Publ. #56443, Rev. 0.92, July 2021

See also

| designer | AMD + |

| first launched | July 14, 2020 + |

| instance of | package + |

| market segment | Workstation + |

| microarchitecture | Zen 2 + and Zen 3 + |

| name | Socket sWRX8 + |

| package | sWRX8 + and FCLGA-4094 + |

| package contacts | 4,094 + |

| package height | 6.26 mm (0.246 in) + |

| package length | 75.4 mm (7.54 cm, 2.969 in) + |

| package type | FC-OLGA + |

| package width | 58.5 mm (5.85 cm, 2.303 in) + |

| socket | sWRX8 + |

| tdp | 280 W (280,000 mW, 0.375 hp, 0.28 kW) + |