| Edit Values | |

| Vanilla-5 µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | University of Michigan, University of California, Cornell University, University of California |

| Manufacturer | TSMC |

| Process | 16 nm |

| Pipeline | |

| Type | Pipelined |

| OoOE | No |

| Speculative | No |

| Reg Renaming | No |

| Stages | 5 |

| Decode | 1 |

| Instructions | |

| ISA | RISC-V |

| Extensions | Integer, Multiply |

| Cache | |

| L1I Cache | 4 KiB/core |

| L1D Cache | 4 KiB/core |

Vanilla-5 is a custom RISC-V core microarchitecture designed specifically for the Celerity SoC. The work is a joint effort by the Bespoke Silicon Group at the University of Washington, Cornell University, University of Michigan, and UC San Diego.

Overview

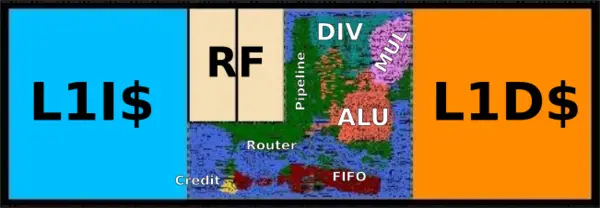

Vanilla-5 is a custom-designed RISC-V core designed by the Celerity SoC team for that chip. The core is a fully synthesized design that implements the RV32IM ISA (base as well as the integer and multiply extensions). Vanilla-5 was designed to take up very little silicon area. For that reason it uses an incredibly simple design - it's an in-order, single-issue, 5-stage design. Each core incorporates a 32-entry, 32b register file which is implemented using two 1R1W latch-based memory as well as a 4 KiB of private level 1 instruction cache and a private 4 KiB of private level 1 data cache.

The Vanilla-5 core is integrated into the Celerity SoC where it's used as part of a manycore array of 496 tiles. Each tile comprises a Vanilla-5 core and a router. The core is silicon-proven capable of up to 1.4 GHz.

Die

- TSMC 16 nm process

- 24,251 µm² (0.024 mm²) die area

Routing:

Breakdown

| Type | Area (µm²) | % |

|---|---|---|

| IMEM | 6691 | 27.59 |

| DMEM | 6691 | 27.59 |

| RF | 2008 | 8.28 |

| Core logic | 2473 | 10.20 |

| ALU | 485 | 2.00 |

| Div | 412 | 1.70 |

| Mult | 301 | 1.24 |

| Pipeline/other | 1275 | 5.26 |

| NoC | 1881 | 7.76 |

| Endpoint FIFO | 303 | 1.25 |

| Credit counter | 23 | 0.09 |

| Router | 1555 | 6.41 |

| Endcap/welltap | 281 | 1.16 |

| Filler | 1635 | 6.74 |

| Unutilized | 2591 | 10.68 |

| Total | 24251 | 100.00 |

Source core

The Vanilla-5 core is open source and can be found on https://bitbucket.org/taylor-bsg/bsg_manycore/src/master/v/vanilla_bean/

See also

Bibliography

- 2019 Symposia on VLSI Technology and Circuits (VLSI 2019).

- IEEE Hot Chips 29 Symposium (HCS) 2017.

| codename | Vanilla-5 + |

| designer | University of Michigan +, University of California + and Cornell University + |

| full page name | umich/microarchitectures/vanilla-5 + |

| instance of | microarchitecture + |

| instruction set architecture | RISC-V + |

| manufacturer | TSMC + |

| microarchitecture type | CPU + |

| name | Vanilla-5 + |

| pipeline stages | 5 + |

| process | 16 nm (0.016 μm, 1.6e-5 mm) + |