From WikiChip

Goldmont - Microarchitectures - Intel

| Edit Values | |

| Goldmont µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | Intel |

| Manufacturer | Intel |

| Introduction | August 30, 2016 |

| Process | 14 nm |

| Core Configs | 2, 4, 8, 12, 16 |

| Pipeline | |

| Type | Superscalar |

| Speculative | Yes |

| Reg Renaming | Yes |

| Stages | 12-14 |

| Instructions | |

| ISA | x86-64 |

| Extensions | MOVBE, MMX, SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4.2, POPCNT, AES, PCLMUL, RDRND, SHA |

| Cache | |

| L1I Cache | 32 KiB/Core 8-way set associative |

| L1D Cache | 24 KiB/Core 6-way set associative |

| L2 Cache | 1-2 MiB/2 Cores 16-way set associative |

| Cores | |

| Core Names | Apollo Lake, Denverton |

| Succession | |

Goldmont (GLM) is Intel's 14 nm microarchitecture of system on chips for the ultra-low power (ULP) devices. Goldmont-based processors and SoCs are part of the Atom, Pentium, and Celeron families. Goldmont superseded Airmont in August of 2016. With Goldmont, Intel stopped targeting smartphones altogether, cancelling the related cores and SKUs.

Contents

[hide]Codenames

| Platform | Core | Target |

|---|---|---|

| Apollo Lake | Entry-level PCs, Tablets | |

| Denverton | Ultra-low power servers, networking, storage, and IoT | |

| Willow Trail | Lightweight Tablets & high-end smartphone | |

| Morganfield | Broxton | Smartphone |

Process Technology

- Main article: Broadwell § Process Technology

Goldmont-based chips are manufactured on Intel's 14 nm process.

Architecture

Key changes from Airmont

- Pipeline

- Compared to Airmont, Goldmont is a 3-issue core.

- NOPs, MOVs and many ALU operations have 3 op/cycle throughput for 16, 32 and 64-bit registers. (8-bit ALU ops throughput is 2, 1.5 or 1 op per cycle).

- ADC, SBB have 0.5 op/cycle throughput, unchanged from Airmont.

- INC, DEC, BTx, shift ops are not faster than on Airmont, 8-bit shifts are slightly slower (0.66 op/cycle instead of 1).

- Rotate-through-carry (RCL, RCR) throughput continues to be slow and is slightly slower (used to be ~10 cycles per op, now ~12).

- 16- and 64-bit shift-double (SHLD, SHRD) throughput continues to be slow and is slightly slower (used to be ~10 cycles per op, now ~14) than on Airmont. (32-bit SHLD, SHRD are fast: 2-4 cycles).

- Variable shifts and rotates (SHL r32, CL etc) latency increased from 1 cycle to 2 cycles.

- Bit scan (BSF, BSR) throughput improved from 10 to 8 cycles per op.

- MUL throughput is better by 1 cycle (used to be 5/7 cycles for 32/64-bit mul, now 4/6).

- DIV is more than twice as fast as Airmont, 13 cycles for most divides, 128-bit/64-bit are ~42 cycles.

- PUSH to POP forwarding is improved.

- REP MOVS streaming copy is twice as fast: now ~26 bytes/cycle.

- REP STOS fill is not improved: ~9 bytes/cycle.

- Some vector instructions are faster, but like on Airmont, none have throughput >2 op/cycle. This includes often used ops like adds and multiplies:

- MULPS and MULPD have 4 cycle latency and 1 op/cycle throughput (used to have L5 and T0.5).

- ADDPD has 3 cycle latency and 1 op/cycle throughput (used to have L4 and T0.5).

- CRC32 instruction throughput improved from 6 cycles/op to 1 cycle/op, latency is halved from 6 to 3.

- Gen 9 GPUs

- HD Graphics 400 → HD Graphics 500 (12 Execution Units, no change)

- HD Graphics 405 → HD Graphics 505 (18 Execution Units, up from 16)

New instructions

Goldmont introduced a number of new instructions:

-

RDSEED- Generates 16, 32 or 64 bit random numbers seeds (NIST SP 800-90B & NIST SP 800-90C) -

SMAP- Supervisor Mode Access Prevention -

MPX-Memory Protection Extensions -

XSAVEC- Save processor extended states with compaction to memory -

XSAVES- Save processor supervisor-mode extended states to memory. -

CLFLUSHOPT- Flush & Invalidates memory operand and its associated cache line (All L1/L2/L3 etc..) -

SHA- Hardware acceleration for SHA hashing operations - FS/GS base access

Block Diagram

| This section is empty; you can help add the missing info by editing this page. |

Memory Hierarchy

- Cache

- Hardware prefetchers

- L1 Cache:

- 32 KiB 8-way set associative instruction, 64 B line size

- 24 KiB 6-way set associative data, 64 B line size

- Per core

- L2 Cache:

- 1 MiB 16-way set associative, 64 B line size

- Per 2 cores

- L3 Cache:

- No level 3 cache

- RAM

- Maximum of 1 GiB, 2 GiB, 4 GiB, 8 GiB

- dual 32-bit channels, 1 or 2 ranks per channel

Multithreading

Goldmont, like Airmont has no support for Intel Hyper-Threading Technology.

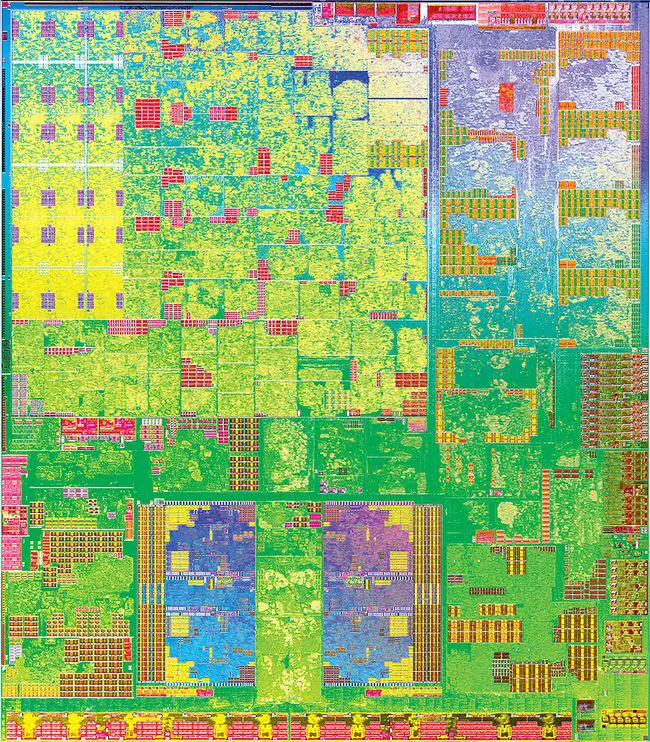

Die Shot

Intel Atom E3900 SoC series:

All Goldmont Chips

| Goldmont Chips | |||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| Main processor | IGP | ||||||||||

| Model | Family | Platform | Core | Launched | SDP | TDP | Freq | Max Mem | Name | Freq | Max Freq |

| C3308 | Atom | Denverton | 15 August 2017 | 9.5 W 9,500 mW 0.0127 hp 0.0095 kW | 1,600 MHz 1.6 GHz 1,600,000 kHz | 131,072 MiB 134,217,728 KiB 137,438,953,472 B 128 GiB 0.125 TiB | |||||

| C3338 | Atom | Denverton | 22 February 2017 | 9 W 9,000 mW 0.0121 hp 0.009 kW | 1,500 MHz 1.5 GHz 1,500,000 kHz | 131,072 MiB 134,217,728 KiB 137,438,953,472 B 128 GiB 0.125 TiB | |||||

| C3508 | Atom | Denverton | 15 August 2017 | 11.25 W 11,250 mW 0.0151 hp 0.0113 kW | 1,600 MHz 1.6 GHz 1,600,000 kHz | 262,144 MiB 268,435,456 KiB 274,877,906,944 B 256 GiB 0.25 TiB | |||||

| C3538 | Atom | Denverton | 15 August 2017 | 15 W 15,000 mW 0.0201 hp 0.015 kW | 2,100 MHz 2.1 GHz 2,100,000 kHz | 262,144 MiB 268,435,456 KiB 274,877,906,944 B 256 GiB 0.25 TiB | |||||

| C3558 | Atom | Denverton | 15 August 2017 | 16 W 16,000 mW 0.0215 hp 0.016 kW | 2,200 MHz 2.2 GHz 2,200,000 kHz | 262,144 MiB 268,435,456 KiB 274,877,906,944 B 256 GiB 0.25 TiB | |||||

| C3708 | Atom | Denverton | 15 August 2017 | 17 W 17,000 mW 0.0228 hp 0.017 kW | 1,700 MHz 1.7 GHz 1,700,000 kHz | 262,144 MiB 268,435,456 KiB 274,877,906,944 B 256 GiB 0.25 TiB | |||||

| C3750 | Atom | Denverton | 15 August 2017 | 21 W 21,000 mW 0.0282 hp 0.021 kW | 2,200 MHz 2.2 GHz 2,200,000 kHz | 262,144 MiB 268,435,456 KiB 274,877,906,944 B 256 GiB 0.25 TiB | |||||

| C3758 | Atom | Denverton | 15 August 2017 | 25 W 25,000 mW 0.0335 hp 0.025 kW | 2,200 MHz 2.2 GHz 2,200,000 kHz | 262,144 MiB 268,435,456 KiB 274,877,906,944 B 256 GiB 0.25 TiB | |||||

| C3808 | Atom | Denverton | 15 August 2017 | 25 W 25,000 mW 0.0335 hp 0.025 kW | 2,000 MHz 2 GHz 2,000,000 kHz | 262,144 MiB 268,435,456 KiB 274,877,906,944 B 256 GiB 0.25 TiB | |||||

| C3830 | Atom | Denverton | 15 August 2017 | 21 W 21,000 mW 0.0282 hp 0.021 kW | 1,900 MHz 1.9 GHz 1,900,000 kHz | 262,144 MiB 268,435,456 KiB 274,877,906,944 B 256 GiB 0.25 TiB | |||||

| C3850 | Atom | Denverton | 15 August 2017 | 25 W 25,000 mW 0.0335 hp 0.025 kW | 2,100 MHz 2.1 GHz 2,100,000 kHz | 262,144 MiB 268,435,456 KiB 274,877,906,944 B 256 GiB 0.25 TiB | |||||

| C3858 | Atom | Denverton | 15 August 2017 | 25 W 25,000 mW 0.0335 hp 0.025 kW | 2,000 MHz 2 GHz 2,000,000 kHz | 262,144 MiB 268,435,456 KiB 274,877,906,944 B 256 GiB 0.25 TiB | |||||

| C3950 | Atom | Denverton | 15 August 2017 | 24 W 24,000 mW 0.0322 hp 0.024 kW | 1,700 MHz 1.7 GHz 1,700,000 kHz | 262,144 MiB 268,435,456 KiB 274,877,906,944 B 256 GiB 0.25 TiB | |||||

| C3955 | Atom | Denverton | 15 August 2017 | 32 W 32,000 mW 0.0429 hp 0.032 kW | 2,100 MHz 2.1 GHz 2,100,000 kHz | 262,144 MiB 268,435,456 KiB 274,877,906,944 B 256 GiB 0.25 TiB | |||||

| C3958 | Atom | Denverton | 15 August 2017 | 31 W 31,000 mW 0.0416 hp 0.031 kW | 2,000 MHz 2 GHz 2,000,000 kHz | 262,144 MiB 268,435,456 KiB 274,877,906,944 B 256 GiB 0.25 TiB | |||||

| x5-E3930 | Atom x5 | Apollo Lake | Apollo Lake | 2017 | 6.5 W 6,500 mW 0.00872 hp 0.0065 kW | 1,300 MHz 1.3 GHz 1,300,000 kHz | 8,192 MiB 8,388,608 KiB 8,589,934,592 B 8 GiB 0.00781 TiB | HD Graphics 500 | 400 MHz 0.4 GHz 400,000 KHz | 550 MHz 0.55 GHz 550,000 KHz | |

| x5-E3940 | Atom x5 | Apollo Lake | Apollo Lake | 2017 | 9.5 W 9,500 mW 0.0127 hp 0.0095 kW | 1,600 MHz 1.6 GHz 1,600,000 kHz | 8,192 MiB 8,388,608 KiB 8,589,934,592 B 8 GiB 0.00781 TiB | HD Graphics 500 | 400 MHz 0.4 GHz 400,000 KHz | 600 MHz 0.6 GHz 600,000 KHz | |

| x7-E3950 | Atom x7 | Apollo Lake | Apollo Lake | 2017 | 12 W 12,000 mW 0.0161 hp 0.012 kW | 1,600 MHz 1.6 GHz 1,600,000 kHz | 8,192 MiB 8,388,608 KiB 8,589,934,592 B 8 GiB 0.00781 TiB | HD Graphics 505 | 500 MHz 0.5 GHz 500,000 KHz | 650 MHz 0.65 GHz 650,000 KHz | |

| J3355 | Celeron | Apollo Lake | 30 August 2016 | 10 W 10,000 mW 0.0134 hp 0.01 kW | 2,000 MHz 2 GHz 2,000,000 kHz | 8,192 MiB 8,388,608 KiB 8,589,934,592 B 8 GiB 0.00781 TiB | HD Graphics 500 | 250 MHz 0.25 GHz 250,000 KHz | 700 MHz 0.7 GHz 700,000 KHz | ||

| J3455 | Celeron | Apollo Lake | 30 August 2016 | 10 W 10,000 mW 0.0134 hp 0.01 kW | 1,500 MHz 1.5 GHz 1,500,000 kHz | 8,192 MiB 8,388,608 KiB 8,589,934,592 B 8 GiB 0.00781 TiB | HD Graphics 500 | 250 MHz 0.25 GHz 250,000 KHz | 750 MHz 0.75 GHz 750,000 KHz | ||

| N3350 | Celeron | Apollo Lake | 30 August 2016 | 4 W 4,000 mW 0.00536 hp 0.004 kW | 6 W 6,000 mW 0.00805 hp 0.006 kW | 1,100 MHz 1.1 GHz 1,100,000 kHz | 8,192 MiB 8,388,608 KiB 8,589,934,592 B 8 GiB 0.00781 TiB | HD Graphics 500 | 200 MHz 0.2 GHz 200,000 KHz | 650 MHz 0.65 GHz 650,000 KHz | |

| N3450 | Celeron | Apollo Lake | 30 August 2016 | 4 W 4,000 mW 0.00536 hp 0.004 kW | 6 W 6,000 mW 0.00805 hp 0.006 kW | 1,100 MHz 1.1 GHz 1,100,000 kHz | 8,192 MiB 8,388,608 KiB 8,589,934,592 B 8 GiB 0.00781 TiB | HD Graphics 500 | 200 MHz 0.2 GHz 200,000 KHz | 700 MHz 0.7 GHz 700,000 KHz | |

| J4205 | Pentium | Apollo Lake | 30 August 2016 | 10 W 10,000 mW 0.0134 hp 0.01 kW | 1,500 MHz 1.5 GHz 1,500,000 kHz | 8,192 MiB 8,388,608 KiB 8,589,934,592 B 8 GiB 0.00781 TiB | HD Graphics 505 | 250 MHz 0.25 GHz 250,000 KHz | 800 MHz 0.8 GHz 800,000 KHz | ||

| N4200 | Pentium | Apollo Lake | 30 August 2016 | 4 W 4,000 mW 0.00536 hp 0.004 kW | 6 W 6,000 mW 0.00805 hp 0.006 kW | 1,100 MHz 1.1 GHz 1,100,000 kHz | 8,192 MiB 8,388,608 KiB 8,589,934,592 B 8 GiB 0.00781 TiB | HD Graphics 505 | 200 MHz 0.2 GHz 200,000 KHz | 750 MHz 0.75 GHz 750,000 KHz | |

| Count: 24 | |||||||||||

Facts about "Goldmont - Microarchitectures - Intel"

| codename | Goldmont + |

| core count | 2 +, 4 +, 8 +, 12 + and 16 + |

| designer | Intel + |

| first launched | August 30, 2016 + |

| full page name | intel/microarchitectures/goldmont + |

| instance of | microarchitecture + |

| instruction set architecture | x86-64 + |

| manufacturer | Intel + |

| microarchitecture type | CPU + |

| name | Goldmont + |

| pipeline stages (max) | 14 + |

| pipeline stages (min) | 12 + |

| process | 14 nm (0.014 μm, 1.4e-5 mm) + |