From WikiChip

Difference between revisions of "intel/microarchitectures/willow cove"

(Blanked the page) |

m (Reverted edits by 188.165.24.181 (talk) to last revision by David) |

||

| Line 1: | Line 1: | ||

| + | {{intel title|Willow Cove|arch}} | ||

| + | {{microarchitecture | ||

| + | |atype=CPU | ||

| + | |name=Willow Cove | ||

| + | |designer=Intel | ||

| + | |manufacturer=Intel | ||

| + | |introduction=2020 | ||

| + | |process=10 nm | ||

| + | |isa=x86-64 | ||

| + | |predecessor=Sunny Cove | ||

| + | |predecessor link=intel/microarchitectures/sunny cove | ||

| + | |successor=Golden Cove | ||

| + | |successor link=intel/microarchitectures/golden cove | ||

| + | }} | ||

| + | '''Willow Cove''' is the successor to {{\\|Sunny Cove}}, a high-performance [[10 nm]] [[x86]] core microarchitecture designed by [[Intel]] for an array of server and client products, including {{\\|Tiger Lake}}. | ||

| + | == History == | ||

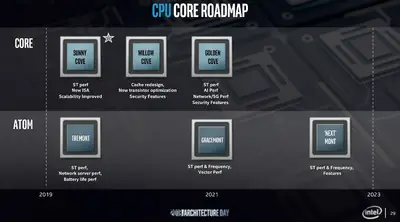

| + | [[File:sunny cove roadmap.png|thumb|right|400px|Intel Core roadmap]] | ||

| + | Willow Cove was originally unveiled by Intel at their 2018 architecture day. Willow Cove is intended to succeed Sunny Cove in the 2020 timeframe. | ||

| + | |||

| + | == Process Technology == | ||

| + | Willow Cove is designed to take advantage of Intel's [[10 nm process]]. | ||

| + | |||

| + | == Architecture == | ||

| + | === Key changes from {{\\|Sunny Cove}}=== | ||

| + | * New cache subsystem | ||

| + | * Security features | ||

| + | {{expand list}} | ||

| + | |||

| + | ==== New instructions ==== | ||

| + | Willow Cove introduced a number of {{x86|extensions|new instructions}}: | ||

| + | |||

| + | * Control-flow Enforcement Technology (CET) enhancements | ||

| + | * {{x86|MOVDIR|<code>MOVDIR</code>}} - Direct stores | ||

| + | * Additional {{x86|AVX-512}} extensions: | ||

| + | ** {{x86|AVX512_VP2INTERSECT|<code>AVX512_VP2INTERSECT</code>}} - AVX-512 Vector Intersection Instructions | ||

| + | |||

| + | ''Only on server parts ({{\\|Sapphire Rapids}}):'' | ||

| + | |||

| + | * {{x86|ENQCMD|<code>ENQCMD</code>}} - Enqueue Stores | ||

| + | |||

| + | == Bibliography == | ||

| + | * Intel Architecture Day 2018, December 11, 2018 | ||

Revision as of 22:05, 23 March 2020

| Edit Values | |

| Willow Cove µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | Intel |

| Manufacturer | Intel |

| Introduction | 2020 |

| Process | 10 nm |

| Instructions | |

| ISA | x86-64 |

| Succession | |

Willow Cove is the successor to Sunny Cove, a high-performance 10 nm x86 core microarchitecture designed by Intel for an array of server and client products, including Tiger Lake.

Contents

History

Willow Cove was originally unveiled by Intel at their 2018 architecture day. Willow Cove is intended to succeed Sunny Cove in the 2020 timeframe.

Process Technology

Willow Cove is designed to take advantage of Intel's 10 nm process.

Architecture

Key changes from Sunny Cove

- New cache subsystem

- Security features

This list is incomplete; you can help by expanding it.

New instructions

Willow Cove introduced a number of new instructions:

- Control-flow Enforcement Technology (CET) enhancements

-

MOVDIR- Direct stores - Additional AVX-512 extensions:

-

AVX512_VP2INTERSECT- AVX-512 Vector Intersection Instructions

-

Only on server parts (Sapphire Rapids):

-

ENQCMD- Enqueue Stores

Bibliography

- Intel Architecture Day 2018, December 11, 2018

Facts about "Willow Cove - Microarchitectures - Intel"

| codename | Willow Cove + |

| core count | 2 +, 4 +, 6 + and 8 + |

| designer | Intel + |

| first launched | 2020 + |

| full page name | intel/microarchitectures/willow cove + |

| instance of | microarchitecture + |

| instruction set architecture | x86-64 + |

| manufacturer | Intel + |

| microarchitecture type | CPU + |

| name | Willow Cove + |

| pipeline stages (max) | 19 + |

| pipeline stages (min) | 14 + |

| process | 10 nm (0.01 μm, 1.0e-5 mm) + |