From WikiChip

Difference between revisions of "zhaoxin/kaisheng"

| Line 8: | Line 8: | ||

| manufacturer = TSMC | | manufacturer = TSMC | ||

| type = Microprocessors | | type = Microprocessors | ||

| − | | first announced = | + | | first announced = 2017 |

| − | | first launched = | + | | first launched = 2018 |

| isa = x86 | | isa = x86 | ||

| microarch = WuDaoKou | | microarch = WuDaoKou | ||

Latest revision as of 10:42, 13 June 2018

| KaisHeng | |

| Developer | Zhaoxin |

| Manufacturer | TSMC |

| Type | Microprocessors |

| Introduction | 2017 (announced) 2018 (launch) |

| ISA | x86 |

| µarch | WuDaoKou, LuJiaZui |

| Word size | 64 bit 8 octets

16 nibbles |

| Process | 28 nm 0.028 μm

2.8e-5 mm |

| Technology | CMOS |

| Succession | |

| ← | |

| QuadCore | |

KaisHeng (KH) is a family of x86 microprocessors developed by Zhaoxin for the Chinese market. This family is primarily targeting server and networking devices.

Overview[edit]

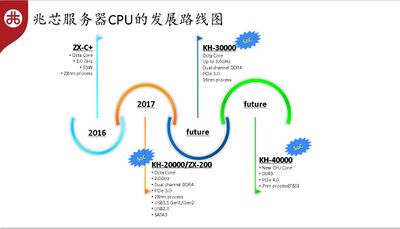

Announced in late 2017 and officially launched in early 2018, the KH series is primarily designed for general-purpose servers. Those chips are fully SoCs solutions that come with an optional I/O extension chipsets.

Models[edit]

KH-20000[edit]

- Main article: WuDaoKou microarchitecture

The KH-20000 (KH-20k) series is based on the WuDaoKou microarchitecture and is fabricated on HLMC's 28 nm process. Those parts all include the following common features:

- ISA: Everything up to AVX (SMM, FPU, NX, MMX, SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4.2, AES, SM3, SM4, and AVX)

- Tech: VT-x/EPT, TXT

- Mem: Up 64 GiB of dual-channel 2133 MT/s DDR4

KH-30000[edit]

- Main article: LuJiaZui microarchitecture

The KH-30000 is a planned series of processors based on LuJiaZui set to be fabricated on TSMC's 16 nm process.

KH-40000[edit]

The KH-40000 is a planned series of processors set to be fabricated on TSMC's 7 nm process.

Facts about "KaisHeng (KH) - Zhaoxin"

| designer | Zhaoxin + |

| first announced | 2017 + |

| first launched | 2018 + |

| full page name | zhaoxin/kaisheng + |

| instance of | microprocessor family + |

| instruction set architecture | x86 + |

| main designer | Zhaoxin + |

| manufacturer | TSMC + |

| microarchitecture | WuDaoKou + and LuJiaZui + |

| name | KaisHeng + |

| process | 28 nm (0.028 μm, 2.8e-5 mm) + |

| technology | CMOS + |

| word size | 64 bit (8 octets, 16 nibbles) + |