m |

(Added compiler support) |

||

| (4 intermediate revisions by 2 users not shown) | |||

| Line 43: | Line 43: | ||

| September, [[2018]] || {{ampere|Skylark|l=arch}} || [[14 nm]] || [[16 cores|16]]-[[32 cores|32]] | | September, [[2018]] || {{ampere|Skylark|l=arch}} || [[14 nm]] || [[16 cores|16]]-[[32 cores|32]] | ||

|- | |- | ||

| − | | September, [[2019]] || {{ampere|Quicksilver|l=arch}} || [[7 nm]] || | + | | September, [[2019]] || {{ampere|Quicksilver|l=arch}} || [[7 nm]] || 80 |

| + | |} | ||

| + | |||

| + | == Compiler Support == | ||

| + | {| class="wikitable" | ||

| + | |- | ||

| + | ! Compiler !! Arch-Specific || Arch-Favorable || Arch-Target | ||

| + | |- | ||

| + | | [[GCC]] || <code>-march=armv8-a</code> || <code>-mtune=emag</code> || <code>-mcpu=emag</code> | ||

| + | |- | ||

| + | | [[LLVM]] || <code>-march=armv8-a</code> || <code>-mtune=emag</code> || <code>-mcpu=emag</code> | ||

|} | |} | ||

| Line 52: | Line 62: | ||

* '''Mem:''' 8x DDR4 channels, up to 2666 MT/s with ECC; 1 TiB/socket | * '''Mem:''' 8x DDR4 channels, up to 2666 MT/s with ECC; 1 TiB/socket | ||

| − | * '''I/O:''' | + | * '''I/O:''' 42 PCIe Gen 3 lanes |

* '''TDP:''' Up to 125 W | * '''TDP:''' Up to 125 W | ||

| Line 97: | Line 107: | ||

* David Schor. (February 5, 2018). "''[https://fuse.wikichip.org/news/776/x-gene-3-gets-a-second-chance-at-ampere-with-a-new-32-core-16nm-arm-processor/ X-Gene 3 gets a second chance at Ampere with a new 32-core 16nm ARM processor]''". | * David Schor. (February 5, 2018). "''[https://fuse.wikichip.org/news/776/x-gene-3-gets-a-second-chance-at-ampere-with-a-new-32-core-16nm-arm-processor/ X-Gene 3 gets a second chance at Ampere with a new 32-core 16nm ARM processor]''". | ||

* David Schor. (September 19, 2018). "''[https://fuse.wikichip.org/news/1663/ampere-ships-first-gen-arm-server-processors/ Ampere Ships First Gen ARM Server Processors]''". | * David Schor. (September 19, 2018). "''[https://fuse.wikichip.org/news/1663/ampere-ships-first-gen-arm-server-processors/ Ampere Ships First Gen ARM Server Processors]''". | ||

| − | https://amperecomputing.com/ampere-announces-availability-of-emag-for-hyperscale-cloud-computing-and-unveils-aggressive-multi-generation-roadmap | + | * Ampere Computing. (September 18, 2018). "''[https://amperecomputing.com/ampere-announces-availability-of-emag-for-hyperscale-cloud-computing-and-unveils-aggressive-multi-generation-roadmap Ampere Announces Availability of eMAG™ for Hyperscale Cloud Computing and Unveils Aggressive, Multi-Generation Roadmap]''". |

| − | |||

Latest revision as of 11:59, 19 May 2021

| eMAG | |

| |

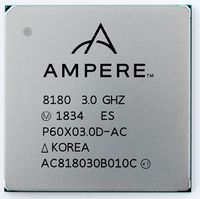

| eMAG 8180, front | |

| Developer | Ampere Computing, AppliedMicro |

| Manufacturer | TSMC |

| Type | Microprocessors |

| Introduction | February 5, 2018 (announced) September 8, 2018 (launch) |

| ISA | ARMv8 |

| µarch | Skylark, Quicksilver |

| Word size | 64 bit 8 octets

16 nibbles |

| Process | 16 nm 0.016 μm

1.6e-5 mm |

| Technology | CMOS |

| Succession | |

| ← | |

| X-Gene 2 | |

eMAG is a family of 64-bit high-performance ARM server microprocessors designed by Ampere Computing for the data center.

Contents

Overview[edit]

eMAG is a family of high-performance ARM server processors designed by Ampere Computing and introduced in 2018. Ampere's introduction of eMAG to the market concludes the design that started out by AppliedMicro. eMAG processors targets server workloads capable of taking advantage of a high core count with high throughput.

Codenames[edit]

| Introduction | Microarchitecture | Process | Cores |

|---|---|---|---|

| September, 2018 | Skylark | 14 nm | 16-32 |

| September, 2019 | Quicksilver | 7 nm | 80 |

Compiler Support[edit]

| Compiler | Arch-Specific | Arch-Favorable | Arch-Target |

|---|---|---|---|

| GCC | -march=armv8-a |

-mtune=emag |

-mcpu=emag

|

| LLVM | -march=armv8-a |

-mtune=emag |

-mcpu=emag

|

Models[edit]

1st Gen[edit]

- See also: Skylark µarch

First generation eMAG processors are based on the Skylark microarchitecture, a design that started out by AppliedMicro. Fabricated on TSMC's 16FF+ process, those processors feature up to 32 cores operating at up to 3.3 GHz.

- Mem: 8x DDR4 channels, up to 2666 MT/s with ECC; 1 TiB/socket

- I/O: 42 PCIe Gen 3 lanes

- TDP: Up to 125 W

| List of Skylark-based Processors | ||||||

|---|---|---|---|---|---|---|

| Model | Price | Launched | Cores | L3$ | Turbo | TDP |

| 8180 | $ 850.00 € 765.00 £ 688.50 ¥ 87,830.50 | 8 September 2018 | 32 | 32 MiB 32,768 KiB 33,554,432 B 0.0313 GiB | 3.3 GHz 3,300 MHz 3,300,000 kHz | 125 W 125,000 mW 0.168 hp 0.125 kW |

| Count: 1 | ||||||

2nd Gen[edit]

- See also: Quicksilver µarch

Second generation eMAG processors are planned for 2019. Those chips will be based on Ampere's Quicksilver microarchitecture and feature an array of new features and improvements.

See also[edit]

- Intel Xeon Scalable

- AMD EPYC

- Cavium ThunderX2

- Qualcomm Centriq

Bibliography[edit]

- David Schor. (February 5, 2018). "X-Gene 3 gets a second chance at Ampere with a new 32-core 16nm ARM processor".

- David Schor. (September 19, 2018). "Ampere Ships First Gen ARM Server Processors".

- Ampere Computing. (September 18, 2018). "Ampere Announces Availability of eMAG™ for Hyperscale Cloud Computing and Unveils Aggressive, Multi-Generation Roadmap".

| designer | Ampere Computing + and AppliedMicro + |

| first announced | February 5, 2018 + |

| first launched | September 8, 2018 + |

| full page name | ampere computing/emag + |

| instance of | microprocessor family + |

| instruction set architecture | ARMv8 + |

| main designer | Ampere Computing + |

| manufacturer | TSMC + |

| microarchitecture | Skylark + and Quicksilver + |

| name | eMAG + |

| process | 16 nm (0.016 μm, 1.6e-5 mm) + |

| technology | CMOS + |

| word size | 64 bit (8 octets, 16 nibbles) + |