| Edit Values | |

| Skylark µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | AppliedMicro, Ampere Computing |

| Manufacturer | TSMC |

| Introduction | 2018 |

| Process | 16 nm |

| Core Configs | 32 |

| Pipeline | |

| Type | Superscalar |

| OoOE | Yes |

| Speculative | Yes |

| Reg Renaming | Yes |

| Instructions | |

| ISA | ARMv8 |

| Succession | |

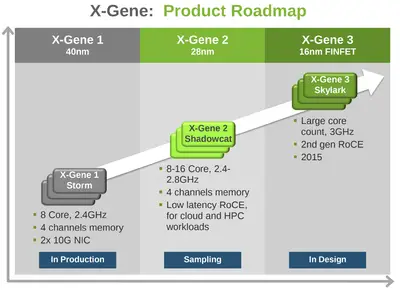

Skylark is AppliedMicro's successor to Shadowcat, a 16 nm ARM microarchitecture for servers. This microarcitecture was eventually acquired by Ampere Computing which has brought it to market under the eMAG brand.

Contents

Release Date[edit]

Skylark was first announced at Hot Chips 26 in 2014 with the goal of samples starting around the end of 2015. In November of 2016, AppliedMicro was acquired by MACOM. Samples for Skylark-based processors were finally announced in March 2017. Later the year the architecture designs, team, and other assets were acquired by Ampere Computing which has finally brought the product to market in early 2018 with mass production planned for mid-2018.

Technology[edit]

Skylark is manufactured on TSMC's 16FF+ process.

Architecture[edit]

Key changes from Shadowcat[edit]

- 16 nm (16FF+) process (from 28 nm)

- Faster frequency (3.3 GHz, up from 2.8 GHz)

- 4x core count (32 cores, up from 8)

- 4x processor modules (16 duplexes, up from 4)

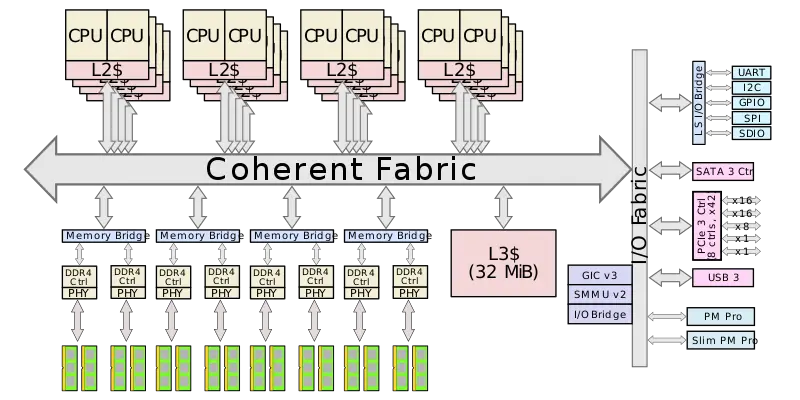

- Coherent network improved for large core count

- 4x L3 (32 MiB, up from 8 MiB)

- I/O

- Generic Interrupt Controller (GIC) v3.0 (up from v2.0)

- 5.25x more PCIe lanes(42 lanes, up from 8)

- 8 controllers (up from 1)

- Memory

- 2x memory channels (8 channels, up from 4)

- 2x DIMMs (16 DIMMs, up from 8)

- DDR4 (from DDR4)

- Faster DDR rates (2666 MT/s, up from 1866 MT/s)

- 2.86x Higher bandwidth (170.7 GB/s, up from 59.73 GB/s)

- 2x memory channels (8 channels, up from 4)

- Package

- 3211-pin (up from 1624)

This list is incomplete; you can help by expanding it.

Block Diagram[edit]

Entire SoC[edit]

Memory Hierarchy[edit]

- Cache

- L1I Cache

- 32 KiB

- L1D Cache

- 32 KiB

- L2

- 256 KiB

- Shared per processor module

- L3

- 32 MiB

- ECC protected

- Shared by entire chip

- L1I Cache

- System DRAM

- 8 channels

- 8 B/cycle/channel (@ memory clock)

- Up to DDR4 @ 2666 MT/s

- Up to 1 TiB

- ECC support,

Overview[edit]

| This section is empty; you can help add the missing info by editing this page. |

Bibliography[edit]

- AppliedMicro. (June, 2016). personal communication.

- Ampere Computing. (February 5, 2018). personal communication.

- Ampere Computing. (September 19, 2018). personal communication.

- David Schor. (September 19, 2018). "Ampere Ships First Gen ARM Server Processors".

| codename | Skylark + |

| core count | 32 + |

| designer | AppliedMicro + and Ampere Computing + |

| first launched | 2018 + |

| full page name | apm/microarchitectures/skylark + |

| instance of | microarchitecture + |

| instruction set architecture | ARMv8 + |

| manufacturer | TSMC + |

| microarchitecture type | CPU + |

| name | Skylark + |

| process | 16 nm (0.016 μm, 1.6e-5 mm) + |