| (3 intermediate revisions by 2 users not shown) | |||

| Line 27: | Line 27: | ||

|package module 1={{packages/greenwaves/aqfn-84}} | |package module 1={{packages/greenwaves/aqfn-84}} | ||

}} | }} | ||

| − | '''GAP8''' is a [[nona-core]] {{arch|32}} [[RISC-V]] ultra-low power microprocessor designed by [[GreenWaves]] and introduced in early [[2018]] for the edge computing and IoT market. This processor, which is fabricated on [[TSMC]]'s [[55nm process|55LP process]], is based on the {{ethz|PULP}} open core. The GAP8 incorporates [[9 cores|nine]] RISC-V cores along with a [[neural processor]] designed to accelerate [[convolutional neural network]]s (CNN). The GAP8 is said to offer a peak performance of up to 200 MOPS at 1 mW and up to 10 GOPS at a few tens of mW, making it well suitable for long autonomous battery-powered life. | + | '''GAP8''' is a [[nona-core]] {{arch|32}} [[RISC-V]] ultra-low power microprocessor designed by [[GreenWaves]] and introduced in early [[2018]] for the edge computing and IoT market. This processor, which is fabricated on [[TSMC]]'s [[55nm process|55LP process]], is based on the {{ethz|PULP}} open core. The GAP8 incorporates [[9 cores|nine]] RISC-V cores capable of running at up to 250 MHz along with a [[neural processor]] designed to accelerate [[convolutional neural network]]s (CNN). The GAP8 is said to offer a peak performance of up to 200 MOPS at 1 mW and up to 10 GOPS at a few tens of mW, making it well suitable for long autonomous battery-powered life. |

== Overview == | == Overview == | ||

| Line 50: | Line 50: | ||

GreenWaves claims the chip can do up to 200 MOPS at 1 mW and up to 10 GOPS at a few tens of mW, making it particularly useful for a long battery-powered life. | GreenWaves claims the chip can do up to 200 MOPS at 1 mW and up to 10 GOPS at a few tens of mW, making it particularly useful for a long battery-powered life. | ||

| − | == Block Diagram == | + | === Block Diagram === |

:[[File:gap8 block diagram.svg|700px]] | :[[File:gap8 block diagram.svg|700px]] | ||

| Line 81: | Line 81: | ||

== Features == | == Features == | ||

| + | [[File:gap8 next to a coin.png|right|300px]] | ||

* 4x PWM | * 4x PWM | ||

* 32 kHz external quartz | * 32 kHz external quartz | ||

| Line 87: | Line 88: | ||

* 2 programmable clocks | * 2 programmable clocks | ||

* Secured execution support with Memory Protection Unit (MPU) | * Secured execution support with Memory Protection Unit (MPU) | ||

| − | |||

== See also == | == See also == | ||

| − | * | + | * [https://fuse.wikichip.org/news/990/the-risc-v-momentum-continues-with-the-gap8-an-iot-ai-application-processor/ GAP8 on WikiChip Fuse] |

Latest revision as of 14:11, 28 February 2018

| Edit Values | ||||||

| GAP8 | ||||||

| ||||||

| GAP8, front package | ||||||

| General Info | ||||||

| Designer | GreenWaves | |||||

| Manufacturer | TSMC | |||||

| Model Number | GAP8 | |||||

| Market | Embedded | |||||

| Introduction | October, 2016 (announced) February 26, 2018 (launched) | |||||

| Release Price | $5 | |||||

| General Specs | ||||||

| Frequency | 250 MHz | |||||

| Microarchitecture | ||||||

| ISA | RV32IMC (RISC-V) | |||||

| Process | 55 nm | |||||

| Technology | CMOS | |||||

| Word Size | 32 bit | |||||

| Cores | 9 | |||||

| Threads | 9 | |||||

| Multiprocessing | ||||||

| Max SMP | 1-Way (Uniprocessor) | |||||

| Electrical | ||||||

| Power dissipation | 60 mW | |||||

| Vcore | 1 V-1.2 V | |||||

| VI/O | 1.8 V, 3.3 V | |||||

| Packaging | ||||||

| ||||||

GAP8 is a nona-core 32-bit RISC-V ultra-low power microprocessor designed by GreenWaves and introduced in early 2018 for the edge computing and IoT market. This processor, which is fabricated on TSMC's 55LP process, is based on the PULP open core. The GAP8 incorporates nine RISC-V cores capable of running at up to 250 MHz along with a neural processor designed to accelerate convolutional neural networks (CNN). The GAP8 is said to offer a peak performance of up to 200 MOPS at 1 mW and up to 10 GOPS at a few tens of mW, making it well suitable for long autonomous battery-powered life.

Contents

Overview[edit]

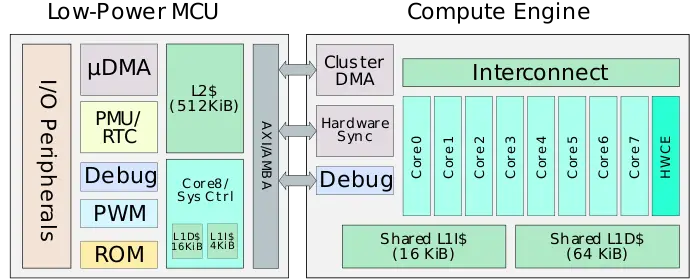

The GAP8 is a derivative of PULP, consisting of three major parts - autonomous peripherals, ultra-low power microcontroller, and the compute engine. The autonomous peripherals are a set of I/Os that can be used while the rest of the system is in deep idle state. The microcontroller and the compute engines sit on two entirely decoupled power domains, consuming power sparingly only when necessary.

The GAP8 has an L2 situated on the MCU side although it's shared by all the devices on the chip, including the cores from the compute engine. Therefore its possible to power gate the entire compute engine without affecting the L2. The L2 consists of four 128 KiB banks for a total of 512 KiB. The L2 can be configured as state retentive (presumably per bank @ 8 µA/bank) so backing up the L2 to flash storage, which consumes fairly significant power, is not needed.

MCU[edit]

The microcontroller block is a fairly standard MCU with many of the standard features. The MCU is situated on its own power domain with the peripherals power switchable and configurable along with the clock generator. It consists of a single system management core (also called a fabric controller by GreenWaves) for tasks such as peripherals and it can double as general purpose low-power core, meaning compute engine can remain power-gated unless absolutely necessary. This core has its own 16 KiB of data cache and 4 KiB of instruction cache.

The chip features nine cores (1 serving in the MCU + 8 in the compute engine), all are fully compliant 32-bit RISC-V cores with support for the integer multiplication and division instructions (M) and compressed instructions (C) standard extensions (i.e., RV32IMC). Inherited from PULP and further enhanced by GreenWaves is the use of the RISC-V standard ISA extension mechanism to enhance the cores and improve performance for DPS-centric operations, specifically operations frequently found in the algorithms executed by the compute engine. Specific instructions were added for operating on Convolutional Neural Networks (CNNs), Support Vector Machines (SVMs), Bayesian, Boosting, Visual Location, Fast Fourier Transforms (FFT), Cepstral Analysis and various others.

The MCU was designed to feel and behave like any other microcontroller on the market. It can be programmed using the familiar standard GCC/GDB toolchain derived from the one developed by the RISC-V foundation. Currently two real-time operating systems are supported, the PULP OS and Arm Mbed OS. GreenWaves has developed a full set of drivers for both of those operating systems in order to allow access to all the GAP8 peripherals.

The controller has a real-time clock (RTC) that can run at just 70nA low-power standby modes enabling the device to wake-up automatically.

Compute Engine[edit]

The compute engine consists of eight additional cores clustered together to form a low-power but powerful computational engine. The cluster share the same 64 KiB data and 16 KiB instruction caches. The engine sits on an entirely separate voltage and frequency domains which can be switched off when not operating or down-clocked to suit a particular workload more efficiently.

Supplementing the CPU cores is a seperate hardware convolution computation engine (HWCE) designed specifically to accelerates inference calculations for convolutional neural networks (CNNs). It does one cycle 5x5 convolution. HWCE shares the same memory with the rest of the cluster. GreenWaves has software libraries for Deep Learning (CNN based), Image Processing Library (e.g., People counting and Visual Monitoring), data analysis, and encryption optimized for the compute engine.

GreenWaves claims the chip can do up to 200 MOPS at 1 mW and up to 10 GOPS at a few tens of mW, making it particularly useful for a long battery-powered life.

Block Diagram[edit]

Cache[edit]

The GAP8 a private L1 cache for the MCU core which consists of a 16 KiB of data cache and 4 KiB of instruction cache. The compute engine has a shared level 1 cache of its own which consists of a 16 KiB instruction cache and a 64 KiB data cache. Additional, the entire chip shares a 512 KiB level 2 cache consisting of 4 128 KiB cache banks.

|

Cache Organization

Cache is a hardware component containing a relatively small and extremely fast memory designed to speed up the performance of a CPU by preparing ahead of time the data it needs to read from a relatively slower medium such as main memory. The organization and amount of cache can have a large impact on the performance, power consumption, die size, and consequently cost of the IC. Cache is specified by its size, number of sets, associativity, block size, sub-block size, and fetch and write-back policies. Note: All units are in kibibytes and mebibytes. |

|||||||||||||||||||||||||

|

|||||||||||||||||||||||||

Memory[edit]

The chip supports up to 16 MiB of SDRAM or additional RAM through the HyperBus interface.

Expansions[edit]

- 128 Mb/s LVDS IEEE compliant

- Serial I/Q

- UART

- Quad SPI Master + additional SPI Master

- SPI Slave

- I2S (2)

- I2C (2)

- Camera parallel interface (CPI)

- HyperBus (External Flash and RAM)

- 32 x GPIOs

Features[edit]

- 4x PWM

- 32 kHz external quartz

- Programmable Voltage Regulator

- Real Time Clock

- 2 programmable clocks

- Secured execution support with Memory Protection Unit (MPU)

See also[edit]

| Has subobject "Has subobject" is a predefined property representing a container construct and is provided by Semantic MediaWiki. | GAP8 - GreenWaves#package + |

| base frequency | 250 MHz (0.25 GHz, 250,000 kHz) + |

| core count | 9 + |

| core voltage (max) | 1.2 V (12 dV, 120 cV, 1,200 mV) + |

| core voltage (min) | 1 V (10 dV, 100 cV, 1,000 mV) + |

| designer | GreenWaves + |

| first announced | October 2016 + |

| first launched | February 26, 2018 + |

| full page name | greenwaves/gap8 + |

| instance of | microprocessor + |

| io voltage | 1.8 V (18 dV, 180 cV, 1,800 mV) + and 3.3 V (33 dV, 330 cV, 3,300 mV) + |

| isa | RV32IMC + |

| isa family | RISC-V + |

| l1$ size | 100 KiB (102,400 B, 0.0977 MiB) + |

| l1d$ size | 80 KiB (81,920 B, 0.0781 MiB) + |

| l1i$ size | 20 KiB (20,480 B, 0.0195 MiB) + |

| l2$ size | 0.5 MiB (512 KiB, 524,288 B, 4.882812e-4 GiB) + |

| ldate | February 26, 2018 + |

| main image |  + + |

| main image caption | GAP8, front package + |

| manufacturer | TSMC + |

| market segment | Embedded + |

| max cpu count | 1 + |

| model number | GAP8 + |

| name | GAP8 + |

| package | aQFN + |

| power dissipation | 0.06 W (60 mW, 8.046e-5 hp, 6.0e-5 kW) + |

| process | 55 nm (0.055 μm, 5.5e-5 mm) + |

| release price | $ 5.00 (€ 4.50, £ 4.05, ¥ 516.65) + |

| smp max ways | 1 + |

| technology | CMOS + |

| thread count | 9 + |

| word size | 32 bit (4 octets, 8 nibbles) + |