(→ARM) |

|||

| (6 intermediate revisions by one other user not shown) | |||

| Line 43: | Line 43: | ||

== Overview == | == Overview == | ||

Introduced in 2008 by [[Freescale]] as a successor to the {{freescale|PowerQUICC}} family, then one of industry's most popular communications processors. Like the PowerQUICC brand, QorIQ spanned the entire range of products from low-power and low-cost to large multi-core designs. Original designs were based on the [[POWER]] architecture. In 2012 Freescale announced the Layerscape series that adopts the [[ARM]] architecture which Freescale/NXP has been using since. | Introduced in 2008 by [[Freescale]] as a successor to the {{freescale|PowerQUICC}} family, then one of industry's most popular communications processors. Like the PowerQUICC brand, QorIQ spanned the entire range of products from low-power and low-cost to large multi-core designs. Original designs were based on the [[POWER]] architecture. In 2012 Freescale announced the Layerscape series that adopts the [[ARM]] architecture which Freescale/NXP has been using since. | ||

| + | |||

| + | == Power == | ||

| + | {{expand section}} | ||

=== Identification === | === Identification === | ||

| Line 67: | Line 70: | ||

| desc 6 = '''Iteration/Version''' | | desc 6 = '''Iteration/Version''' | ||

}} | }} | ||

| − | |||

| − | |||

| − | |||

=== P Series === | === P Series === | ||

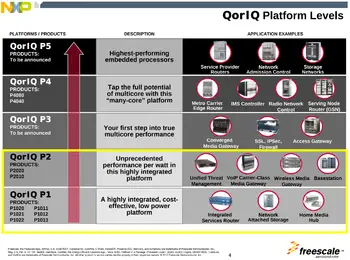

| − | [[File:QorIQ platform levels.png|right| | + | [[File:QorIQ platform levels.png|right|350px]] |

Announced in mid-2008, the QorIQ P-series are [[POWER]]-based microprocessors based on the {{freescale|e500|l=arch}} microarchitecture. Being the first Freescale multicore networking applications based on the [[45 nm process]], those parts offered a migration path for PowerQUICC II Pro and PowerQUICC III processor customers. All chips are fully software compatible with each other and existing PowerQUICC processors with multi-core parts supporting both symmetric and asymmetric multiprocessing. | Announced in mid-2008, the QorIQ P-series are [[POWER]]-based microprocessors based on the {{freescale|e500|l=arch}} microarchitecture. Being the first Freescale multicore networking applications based on the [[45 nm process]], those parts offered a migration path for PowerQUICC II Pro and PowerQUICC III processor customers. All chips are fully software compatible with each other and existing PowerQUICC processors with multi-core parts supporting both symmetric and asymmetric multiprocessing. | ||

==== P1 ==== | ==== P1 ==== | ||

| − | The P1 series are designed for low-power fan-less design designed to succeed previous models (e.g., PowerQUICC II Pro) with higher performance at the same power envelope. P1 parts are designed for the applications such as Ethernet switch controllers, gateways, wireless LAN access points, network printing/storage, and other networking devices with tight thermal constraints. | + | The P1 series are designed for low-power fan-less design designed to succeed previous models (e.g., PowerQUICC II Pro) with higher performance at the same power envelope. All models exhibit a peak power consumption of sub 5 W. P1 parts are designed for the applications such as Ethernet switch controllers, gateways, wireless LAN access points, network printing/storage, and other networking devices with tight thermal constraints. |

<!-- NOTE: | <!-- NOTE: | ||

| Line 87: | Line 87: | ||

{{comp table start}} | {{comp table start}} | ||

<table class="comptable sortable tc4"> | <table class="comptable sortable tc4"> | ||

| − | {{comp table header|main| | + | {{comp table header|main|7:List of QorIQ P1 Processors}} |

| − | {{comp table header|cols| | + | {{comp table header|cols|Announced|Cores|Core|%Frequency|L2$|Max Power|Package}} |

{{#ask: [[Category:microprocessor models by freescale]] [[family::QorIQ]] [[series::P1]] | {{#ask: [[Category:microprocessor models by freescale]] [[family::QorIQ]] [[series::P1]] | ||

|?full page name | |?full page name | ||

|?model number | |?model number | ||

| − | |?first | + | |?first announced |

|?core count | |?core count | ||

| + | |?core name | ||

|?base frequency#MHz | |?base frequency#MHz | ||

|?l2$ size#KiB | |?l2$ size#KiB | ||

| + | |?power dissipation#W | ||

| + | |?package | ||

|format=template | |format=template | ||

|template=proc table 3 | |template=proc table 3 | ||

| − | |userparam= | + | |userparam=9 |

|mainlabel=- | |mainlabel=- | ||

| + | |valuesep=, | ||

}} | }} | ||

{{comp table count|ask=[[Category:microprocessor models by freescale]] [[family::QorIQ]] [[series::P1]]}} | {{comp table count|ask=[[Category:microprocessor models by freescale]] [[family::QorIQ]] [[series::P1]]}} | ||

| Line 107: | Line 111: | ||

==== P2 ==== | ==== P2 ==== | ||

The P2 series are designed to succeed the PowerQUICC III parts. These parts feature a large cache that may be configured as stashing memory, four Ethernet controllers with QoS features and flow control, DDR2/DDR3 SDRAM Controller with ECC support, four general purpose SerDes lanes that may be configured as either two Serial RapidIO ports, three PCI Express ports and two SGMII ports. | The P2 series are designed to succeed the PowerQUICC III parts. These parts feature a large cache that may be configured as stashing memory, four Ethernet controllers with QoS features and flow control, DDR2/DDR3 SDRAM Controller with ECC support, four general purpose SerDes lanes that may be configured as either two Serial RapidIO ports, three PCI Express ports and two SGMII ports. | ||

| + | |||

| + | <!-- NOTE: | ||

| + | This table is generated automatically from the data in the actual articles. | ||

| + | If a microprocessor is missing from the list, an appropriate article for it needs to be | ||

| + | created and tagged accordingly. | ||

| + | |||

| + | Missing a chip? please dump its name here: https://en.wikichip.org/wiki/WikiChip:wanted_chips | ||

| + | --> | ||

| + | {{comp table start}} | ||

| + | <table class="comptable sortable tc4"> | ||

| + | {{comp table header|main|6:List of QorIQ P2 Processors}} | ||

| + | {{comp table header|cols|Launched|Cores|Core|%Frequency|L2$|Max Power}} | ||

| + | {{#ask: [[Category:microprocessor models by freescale]] [[family::QorIQ]] [[series::P2]] | ||

| + | |?full page name | ||

| + | |?model number | ||

| + | |?first launched | ||

| + | |?core count | ||

| + | |?core name | ||

| + | |?base frequency#MHz | ||

| + | |?l2$ size#KiB | ||

| + | |?power dissipation#W | ||

| + | |format=template | ||

| + | |template=proc table 3 | ||

| + | |userparam=8 | ||

| + | |mainlabel=- | ||

| + | }} | ||

| + | {{comp table count|ask=[[Category:microprocessor models by freescale]] [[family::QorIQ]] [[series::P2]]}} | ||

| + | </table> | ||

| + | {{comp table end}} | ||

| + | |||

| + | == ARM == | ||

| + | ===i.MX series=== | ||

| + | :;ARM920 based | ||

| + | * i.MX1 (MC9328MX1) | ||

| + | * i.MXL (MC9328MXL) | ||

| + | * i.MXS (MC9328MXS) | ||

| + | :;ARM926 based | ||

| + | *i.MX21 (MC9328MX21) | ||

| + | *i.MX23 (MCIMX23) | ||

| + | *i.MX25 (MCIMX25) | ||

| + | *i.MX27 (MCIMX27) | ||

| + | *i.MX28 (MCIMX28) | ||

| + | :;{{armh|ARM11|l=arch}} based | ||

| + | * i.MX31 (MCIMX31) | ||

| + | * i.MX35 (MCIMX355) | ||

| + | * i.MX37 (MCIMX37) | ||

| + | :;{{armh|Cortex-A8|l=arch}} based | ||

| + | * i.MX50 (MX508) | ||

| + | * i.MX51 (MCIMX515) | ||

| + | * i.MX53 (MCIMX535) | ||

| + | :;{{armh|Cortex-A9|l=arch}} based | ||

| + | * i.MX6 • MCIMX6 | ||

| + | * i.MX6 Solo • MCIMX6S (i.MX6S) | ||

| + | * i.MX6 SLL • MCIMX6V (i.MX6SLL) | ||

| + | * i.MX6 Solo Lite • MCIMX6L (i.MX6SL) | ||

| + | * i.MX6 Solo X • MCIMX6X (i.MX6SX) (Cortex-A9 + Cortex-M4) | ||

| + | * i.MX6 Dual • MCIMX6D (i.MX6D) | ||

| + | * i.MX6 Dual Lite • MCIMX6U (i.MX6DL) | ||

| + | * i.MX6 Dual Plus • MCIMX6DP (i.MX6DP) | ||

| + | * i.MX6 Quad • MCIMX6Q (i.MX6Q) | ||

| + | * i.MX6 QuadPlus • MCIMX6QP (i.MX6QP) | ||

| + | :;{{armh|Cortex-A7|l=arch}} based | ||

| + | * i.MX6 ULZ • MCIMX6Z (i.MX6ULZ) | ||

| + | * i.MX6 ULL • MCIMX6Y (i.MX6ULL) | ||

| + | * i.MX6 Ultra Lite • MCIMX6G (i.MX6UL) | ||

| + | * i.MX7 (Cortex-A7 + Cortex-M4) | ||

| + | * i.MX7 ULP (Ultra Low Power) | ||

| + | * i.MX7 Solo • 1x Cortex-A7 @800MHz | ||

| + | * i.MX7 Dual • 2x Cortex-A7 @1.2GHz | ||

| + | :;{{armh|Cortex-A72|l=arch}} based | ||

| + | * i.MX8 (8M/8X) Mini/Nano/Plus | ||

| + | :Cortex-A72, Cortex-A53, Cortex-A35 | ||

| + | :Cortex-M4F, Cortex-M7 | ||

| + | |||

| + | ===Layerscape family=== | ||

| + | :;{{armh|Cortex-A7|l=arch}} based | ||

| + | * LS1020A | ||

| + | * LS1021A | ||

| + | * LS1022A | ||

| + | :;{{armh|Cortex-A9|l=arch}} based | ||

| + | * LS1024A | ||

| + | :;{{armh|Cortex-A53|l=arch}} based | ||

| + | * LS1012A | ||

| + | * LS1023A/43A | ||

| + | * LS1088A | ||

| + | :;{{armh|Cortex-A72|l=arch}} based | ||

| + | * LS1017A/27A | ||

| + | * LS1018A/28A | ||

| + | * LS1026A/46A | ||

| + | * LS2044A/84A | ||

| + | * LS2048A/88A | ||

| + | * LS2160A/62A | ||

== See also == | == See also == | ||

* [[Cavium]] {{cavium|ThunderX}} | * [[Cavium]] {{cavium|ThunderX}} | ||

* [[Intel]] {{intel|Atom}} | * [[Intel]] {{intel|Atom}} | ||

Latest revision as of 04:47, 20 February 2025

| QorIQ | |

| Developer | Freescale, NXP |

| Manufacturer | IBM, TSMC |

| Type | System on Chips |

| Introduction | June 16, 2008 (announced) June 16, 2008 (launch) |

| Architecture | POWER & ARM Communication SoC |

| Word size | 32 bit 4 octets , 64 bit8 nibbles 8 octets

16 nibbles |

| Process | 45 nm 0.045 μm , 32 nm4.5e-5 mm 0.032 μm , 20 nm3.2e-5 mm 0.02 μm , 16 nm2.0e-5 mm 0.016 μm

1.6e-5 mm |

| Technology | CMOS |

| Clock | 533 MHz-2,000 MHz |

| Succession | |

| ← | |

| PowerQUICC | |

QorIQ (pronounced "Core IQ") is a family of ARM and POWER embedded and networking microprocessors designed and sold by NXP (formerly Freescale) since 2008 as a successor to the PowerQUICC family.

Contents

Overview[edit]

Introduced in 2008 by Freescale as a successor to the PowerQUICC family, then one of industry's most popular communications processors. Like the PowerQUICC brand, QorIQ spanned the entire range of products from low-power and low-cost to large multi-core designs. Original designs were based on the POWER architecture. In 2012 Freescale announced the Layerscape series that adopts the ARM architecture which Freescale/NXP has been using since.

Power[edit]

| This section requires expansion; you can help adding the missing info. |

Identification[edit]

Only applies to original QorIQ P & T series:

| Identification | ||||||||||||||

| QorIQ | P | 4 | 08 | 0 | ||||||||||

| QorIQ | P | 1 | 01 | 3 | ||||||||||

| Iteration/Version | ||||||||||||||

Core Count

| ||||||||||||||

| Platform Level | ||||||||||||||

Technology Node

| ||||||||||||||

Brand Name

| ||||||||||||||

P Series[edit]

Announced in mid-2008, the QorIQ P-series are POWER-based microprocessors based on the e500 microarchitecture. Being the first Freescale multicore networking applications based on the 45 nm process, those parts offered a migration path for PowerQUICC II Pro and PowerQUICC III processor customers. All chips are fully software compatible with each other and existing PowerQUICC processors with multi-core parts supporting both symmetric and asymmetric multiprocessing.

P1[edit]

The P1 series are designed for low-power fan-less design designed to succeed previous models (e.g., PowerQUICC II Pro) with higher performance at the same power envelope. All models exhibit a peak power consumption of sub 5 W. P1 parts are designed for the applications such as Ethernet switch controllers, gateways, wireless LAN access points, network printing/storage, and other networking devices with tight thermal constraints.

| List of QorIQ P1 Processors | |||||||

|---|---|---|---|---|---|---|---|

| Model | Announced | Cores | Core | Frequency | L2$ | Max Power | Package |

| P1010 | 16 June 2008 | 1 | e500 v2 | 667 MHz 0.667 GHz , 800 MHz667,000 kHz 0.8 GHz 800,000 kHz | 1.6 W 1,600 mW 0.00215 hp 0.0016 kW | TE-PBGA-II-689, TE-PBGA-425 | |

| P1011 | 16 June 2008 | 1 | e500 v2 | 800 MHz 0.8 GHz 800,000 kHz | 256 KiB 0.25 MiB 262,144 B 2.441406e-4 GiB | 1.56 W 1,560 mW 0.00209 hp 0.00156 kW | TE-PBGA-II-689 |

| P1012 | 7 December 2009 | 1 | e500 v2 | 533 MHz 0.533 GHz , 800 MHz533,000 kHz 0.8 GHz 800,000 kHz | 256 KiB 0.25 MiB 262,144 B 2.441406e-4 GiB | 1.6 W 1,600 mW 0.00215 hp 0.0016 kW | TE-PBGA-II-689 |

| P1013 | 9 September 2009 | 1 | e500 v2 | 1,067 MHz 1.067 GHz 1,067,000 kHz | 256 KiB 0.25 MiB 262,144 B 2.441406e-4 GiB | 3 W 3,000 mW 0.00402 hp 0.003 kW | TE-PBGA-II-689 |

| P1014 | 2010 | 1 | e500 v2 | 800 MHz 0.8 GHz 800,000 kHz | 256 KiB 0.25 MiB 262,144 B 2.441406e-4 GiB | 1.13 W 1,130 mW 0.00152 hp 0.00113 kW | TE-PBGA-II-689, TE-PBGA-425 |

| P1015 | October 2011 | 1 | e500 v2 | 400 MHz 0.4 GHz , 533 MHz400,000 kHz 0.533 GHz 533,000 kHz | 256 KiB 0.25 MiB 262,144 B 2.441406e-4 GiB | 1.4 W 1,400 mW 0.00188 hp 0.0014 kW | TE-PBGA-561 |

| P1016 | 1 | e500 v2 | 1.53 W 1,530 mW 0.00205 hp 0.00153 kW | TE-PBGA-561 | |||

| P1017 | 1 | e500 v2 | 2 W 2,000 mW 0.00268 hp 0.002 kW | TE-PBGA-457 | |||

| P1020 | 16 June 2008 | 2 | e500 v2 | 800 MHz 0.8 GHz 800,000 kHz | 256 KiB 0.25 MiB 262,144 B 2.441406e-4 GiB | 1.89 W 1,890 mW 0.00253 hp 0.00189 kW | TE-PBGA-II-689 |

| P1021 | 7 December 2009 | 2 | e500 v2 | 1,200 MHz 1.2 GHz 1,200,000 kHz | 256 KiB 0.25 MiB 262,144 B 2.441406e-4 GiB | 4.5 W 4,500 mW 0.00603 hp 0.0045 kW | TE-PBGA-II-689 |

| P1022 | 9 September 2009 | 2 | e500 v2 | 1,067 MHz 1.067 GHz 1,067,000 kHz | 256 KiB 0.25 MiB 262,144 B 2.441406e-4 GiB | 2.5 W 2,500 mW 0.00335 hp 0.0025 kW | TE-PBGA-II-689 |

| P1023 | 2 | e500 v2 | 2 W 2,000 mW 0.00268 hp 0.002 kW | TE-PBGA-457 | |||

| P1024 | October 2011 | 2 | e500 v2 | 533 MHz 0.533 GHz 533,000 kHz | 256 KiB 0.25 MiB 262,144 B 2.441406e-4 GiB | 1.6 W 1,600 mW 0.00215 hp 0.0016 kW | TE-PBGA-561 |

| P1025 | 2 | e500 v2 | 1.69 W 1,690 mW 0.00227 hp 0.00169 kW | TE-PBGA-561 | |||

| Count: 14 | |||||||

P2[edit]

The P2 series are designed to succeed the PowerQUICC III parts. These parts feature a large cache that may be configured as stashing memory, four Ethernet controllers with QoS features and flow control, DDR2/DDR3 SDRAM Controller with ECC support, four general purpose SerDes lanes that may be configured as either two Serial RapidIO ports, three PCI Express ports and two SGMII ports.

| List of QorIQ P2 Processors | ||||||

|---|---|---|---|---|---|---|

| Model | Launched | Cores | Core | Frequency | L2$ | Max Power |

| P2010 | 2009 | 1 | e500 v2 | 1,200 MHz 1.2 GHz 800 MHz1,200,000 kHz 0.8 GHz 1,000 MHz800,000 kHz 1 GHz 1,333 MHz1,000,000 kHz 1.333 GHz 1,333,000 kHz | 512 KiB 0.5 MiB 524,288 B 4.882812e-4 GiB | 6.7 W 6,700 mW 0.00898 hp 0.0067 kW |

| P2020 | 2009 | 2 | e500 v2 | 800 MHz 0.8 GHz 1,200 MHz800,000 kHz 1.2 GHz 1,333 MHz1,200,000 kHz 1.333 GHz 1,333,000 kHz | 512 KiB 0.5 MiB 524,288 B 4.882812e-4 GiB | 8 W 8,000 mW 0.0107 hp 0.008 kW |

| Count: 2 | ||||||

ARM[edit]

i.MX series[edit]

- ARM920 based

- i.MX1 (MC9328MX1)

- i.MXL (MC9328MXL)

- i.MXS (MC9328MXS)

- ARM926 based

- i.MX21 (MC9328MX21)

- i.MX23 (MCIMX23)

- i.MX25 (MCIMX25)

- i.MX27 (MCIMX27)

- i.MX28 (MCIMX28)

- ARM11 based

- i.MX31 (MCIMX31)

- i.MX35 (MCIMX355)

- i.MX37 (MCIMX37)

- Cortex-A8 based

- i.MX50 (MX508)

- i.MX51 (MCIMX515)

- i.MX53 (MCIMX535)

- Cortex-A9 based

- i.MX6 • MCIMX6

- i.MX6 Solo • MCIMX6S (i.MX6S)

- i.MX6 SLL • MCIMX6V (i.MX6SLL)

- i.MX6 Solo Lite • MCIMX6L (i.MX6SL)

- i.MX6 Solo X • MCIMX6X (i.MX6SX) (Cortex-A9 + Cortex-M4)

- i.MX6 Dual • MCIMX6D (i.MX6D)

- i.MX6 Dual Lite • MCIMX6U (i.MX6DL)

- i.MX6 Dual Plus • MCIMX6DP (i.MX6DP)

- i.MX6 Quad • MCIMX6Q (i.MX6Q)

- i.MX6 QuadPlus • MCIMX6QP (i.MX6QP)

- Cortex-A7 based

- i.MX6 ULZ • MCIMX6Z (i.MX6ULZ)

- i.MX6 ULL • MCIMX6Y (i.MX6ULL)

- i.MX6 Ultra Lite • MCIMX6G (i.MX6UL)

- i.MX7 (Cortex-A7 + Cortex-M4)

- i.MX7 ULP (Ultra Low Power)

- i.MX7 Solo • 1x Cortex-A7 @800MHz

- i.MX7 Dual • 2x Cortex-A7 @1.2GHz

- Cortex-A72 based

- i.MX8 (8M/8X) Mini/Nano/Plus

- Cortex-A72, Cortex-A53, Cortex-A35

- Cortex-M4F, Cortex-M7

Layerscape family[edit]

- Cortex-A7 based

- LS1020A

- LS1021A

- LS1022A

- Cortex-A9 based

- LS1024A

- Cortex-A53 based

- LS1012A

- LS1023A/43A

- LS1088A

- Cortex-A72 based

- LS1017A/27A

- LS1018A/28A

- LS1026A/46A

- LS2044A/84A

- LS2048A/88A

- LS2160A/62A

See also[edit]

| designer | Freescale + and NXP + |

| first announced | June 16, 2008 + |

| first launched | June 16, 2008 + |

| full page name | nxp/qoriq + |

| instance of | system on a chip family + |

| main designer | Freescale + |

| manufacturer | IBM + and TSMC + |

| name | QorIQ + |

| process | 45 nm (0.045 μm, 4.5e-5 mm) +, 32 nm (0.032 μm, 3.2e-5 mm) +, 20 nm (0.02 μm, 2.0e-5 mm) + and 16 nm (0.016 μm, 1.6e-5 mm) + |

| technology | CMOS + |

| word size | 32 bit (4 octets, 8 nibbles) + and 64 bit (8 octets, 16 nibbles) + |