From WikiChip

Difference between revisions of "hisilicon/microarchitectures/taishan v110"

(→Memory Hierarchy) |

(→Scalability) |

||

| Line 72: | Line 72: | ||

== Scalability == | == Scalability == | ||

| − | + | There are three cache coherent ports on each SoC. Every port supports 240 Gb/s (30 GB/s) of peak bandwidth for a total aggregated bandwidth of 720 Gb/s (90 GB/s) in a 2-way [[symmetric multiprocessing]] configuration. | |

| + | |||

| + | :[[File:Kunpeng 920 2smp.svg|600px]] | ||

| + | |||

| + | With all three links, there is also support for 4-way SMP. In this configuration, one link from each socket is connected to another socket for an all-for-all connection. | ||

| + | |||

| + | |||

| + | :[[File:Kunpeng 920 4smp.svg|600px]] | ||

== Die == | == Die == | ||

Revision as of 12:38, 2 May 2019

| Edit Values | |

| TaiShan µarch | |

| General Info | |

| Arch Type | CPU |

| Designer | HiSilicon |

| Manufacturer | TSMC |

| Introduction | 2019 |

| Process | 7 nm |

| Core Configs | 32, 48, 64 |

| Pipeline | |

| Type | Superscalar, Superpipeline |

| OoOE | Yes |

| Speculative | Yes |

| Reg Renaming | Yes |

| Decode | 4-way |

| Instructions | |

| ISA | ARMv8.2-A |

| Extensions | NEON |

| Cache | |

| L1I Cache | 64 KiB/core |

| L1D Cache | 64 KiB/core |

| L2 Cache | 512 KiB/core |

| L3 Cache | 1 MiB/core |

| Cores | |

| Core Names | TaiShan |

TaiShan is a high-performance ARM server microarchitecture designed by HiSilicon for Huawei's own TaiShan servers.

Contents

Brands

TaiShan-based CPUs are branded as the Kunpeng 920 series.

Release Dates

Kunpeng 920 CPUs were officially launched in early 2019.

Architecture

This list is incomplete; you can help by expanding it.

Block Diagram

Entire Chip

Memory Hierarchy

- Cache

- L1I Cache

- 64 KiB/core, private

- L1D Cache

- 64 KiB/core, private

- L2 Cache

- 512 KiB/core, private

- L3 Cache

- 1 MiB/core

- Shared by all cores

- System DRAM

- 1 TiB Max Memory / socket

- 8 Channels

- DDR4, up to 2933 MT/s

- 1 DPC and 2 DPC support

- 8 B/cycle/channel (@ memory clock)

- ECC, SDDC, DDDC

- L1I Cache

Overview

| This section is empty; you can help add the missing info by editing this page. |

Core

| This section is empty; you can help add the missing info by editing this page. |

Scalability

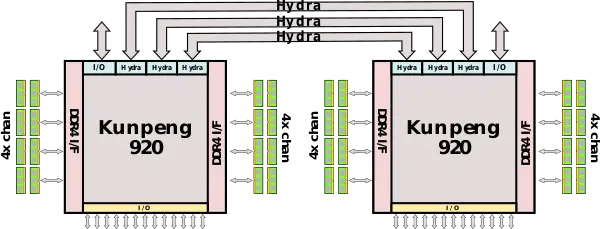

There are three cache coherent ports on each SoC. Every port supports 240 Gb/s (30 GB/s) of peak bandwidth for a total aggregated bandwidth of 720 Gb/s (90 GB/s) in a 2-way symmetric multiprocessing configuration.

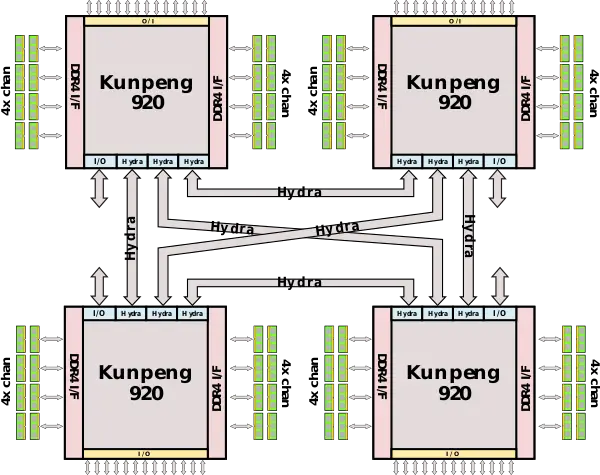

With all three links, there is also support for 4-way SMP. In this configuration, one link from each socket is connected to another socket for an all-for-all connection.

Die

- TSMC 7 nm HPC

- 20,000,000,000 transistors

All TaiShan Chips

| This section is empty; you can help add the missing info by editing this page. |

Bibliography

- Huawei. Personal Communication. 2019

- Huawei Connect 2018. October 2018

- HiSilicon Event. January 7, 2019

Facts about "TaiShan v110 - Microarchitectures - HiSilicon"

| codename | TaiShan + |

| core count | 32 +, 48 + and 64 + |

| designer | HiSilicon + |

| first launched | 2019 + |

| full page name | hisilicon/microarchitectures/taishan v110 + |

| instance of | microarchitecture + |

| instruction set architecture | ARMv8.2-A + |

| manufacturer | TSMC + |

| microarchitecture type | CPU + |

| name | TaiShan + |

| process | 7 nm (0.007 μm, 7.0e-6 mm) + |