(→Overview) |

|||

| (15 intermediate revisions by 3 users not shown) | |||

| Line 1: | Line 1: | ||

{{amd title|Naples|core}} | {{amd title|Naples|core}} | ||

{{core | {{core | ||

| − | | name | + | |name=Naples |

| − | | image | + | |image=amd naples (front).png |

| − | | | + | |caption=Package, front |

| − | | image | + | |back image=amd naples (back).png |

| − | + | |developer=AMD | |

| − | | developer | + | |manufacturer=GlobalFoundries |

| − | | manufacturer | + | |first announced=March 7, 2017 |

| − | | first announced | + | |first launched=June 20, 2017 |

| − | | first launched | + | |isa=x86-64 |

| − | | isa | + | |microarch=Zen |

| − | | microarch | + | |word=64 bit |

| − | | word | + | |proc=14 nm |

| − | | proc | + | |tech=CMOS |

| − | | tech | + | |clock min=2,000 MHz |

| − | | clock min | + | |clock max=2,400 MHz |

| − | | clock max | + | |package name 1=amd,socket_sp3 |

| − | | package | + | |successor=Rome |

| − | + | |successor link=amd/cores/rome | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | | successor | ||

| − | | successor link | ||

}} | }} | ||

| − | '''Naples''' is | + | '''Naples''' is codename for [[AMD]]'s highest-performance enterprise-level server [[multiprocessors]] based on the {{amd|Zen|l=arch}} microarchitecture. Naples processors support up [[32 cores]] and are fabricated on GlobalFoundries' [[14 nm process]]. Naples-based processors are branded as {{amd|EPYC}}. |

| − | |||

| − | Naples processors are | ||

== Overview == | == Overview == | ||

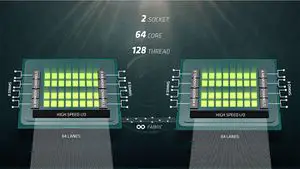

[[File:amd naples 2 sock.jpg|right|thumb]] | [[File:amd naples 2 sock.jpg|right|thumb]] | ||

| − | AMD Naples [[system on chips]] are a series of high-performance [[multiprocessors]] designed by [[AMD]] based on their {{amd|Zen|l=arch}} microarchitecture. Naples SoCs support both single and 2-way multiprocessing with up to a maximum of 32 cores (and 64 threads) per processor for a total of up to 64 cores (and 128 threads) for a 2-way MP system. Those SoCs sports 128 PCIe lanes each, however half of them are lost when in 2-way MP (leaving the system with the same overall lanes count as a single socket solution). Communication between the two chips is done via AMD's {{amd|Infinity Fabric}} protocol over the 64 | + | AMD Naples [[system on chips]] are a series of high-performance [[multiprocessors]] designed by [[AMD]] based on their {{amd|Zen|l=arch}} microarchitecture. Naples SoCs support both single and 2-way multiprocessing with up to a maximum of 32 cores (and 64 threads) per processor for a total of up to 64 cores (and 128 threads) for a 2-way MP system. Those SoCs sports 128 PCIe lanes each, however, half of them are lost when in 2-way MP (leaving the system with the same overall lanes count as a single socket solution). Communication between the two chips is done via AMD's {{amd|Infinity Fabric}} protocol over the 64 reserved lanes. Naples is platform/socket forward-compatible with both {{\\|Rome}} and {{\\|Milan}}. |

=== Common Features === | === Common Features === | ||

All Naples processors have the following: | All Naples processors have the following: | ||

| + | * 128 PCIe lanes (in both single-way and dual-way multiprocessing) | ||

* Octa-channel Memory | * Octa-channel Memory | ||

| − | ** Up to DDR4- | + | ** Up to DDR4-2666 ECC |

** Up to 2 [[TiB]] (4 TiB in 2MP) | ** Up to 2 [[TiB]] (4 TiB in 2MP) | ||

* Up to 32 cores / 64 threads | * Up to 32 cores / 64 threads | ||

* Everything up to {{x86||AVX2}} (i.e., {{x86|SMM}}, {{x86|FPU}}, {{x86|NX}}, {{x86|MMX}}, {{x86|SSE}}, {{x86|SSE2}}, {{x86|SSE3}}, {{x86|SSSE3}}, {{x86|SSE4.1}}, {{x86|SSE4.2}}, {{x86|AES}}, {{x86|AVX}}, {{x86|FMA3}}, and {{x86|AVX2}}), and {{x86|SHA}} | * Everything up to {{x86||AVX2}} (i.e., {{x86|SMM}}, {{x86|FPU}}, {{x86|NX}}, {{x86|MMX}}, {{x86|SSE}}, {{x86|SSE2}}, {{x86|SSE3}}, {{x86|SSSE3}}, {{x86|SSE4.1}}, {{x86|SSE4.2}}, {{x86|AES}}, {{x86|AVX}}, {{x86|FMA3}}, and {{x86|AVX2}}), and {{x86|SHA}} | ||

| − | |||

| − | |||

== Naples Processors == | == Naples Processors == | ||

| Line 50: | Line 41: | ||

created and tagged accordingly. | created and tagged accordingly. | ||

| − | Missing a chip? please dump its name here: | + | Missing a chip? please dump its name here: https://en.wikichip.org/wiki/WikiChip:wanted_chips |

--> | --> | ||

| − | |||

{{comp table start}} | {{comp table start}} | ||

| − | <table class="comptable sortable | + | <table class="comptable sortable tc5 tc6"> |

| − | + | {{comp table header|main|10:List of Naples Processors}} | |

| − | + | {{comp table header|cols|Family|Price|Launched|Cores|Threads|TDP|L2$|L3$|Base|Turbo}} | |

| − | {{comp table header | + | {{#ask: [[Category:microprocessor models by amd]] [[core name::Naples]] |

| − | {{#ask: [[Category:microprocessor models by amd | ||

|?full page name | |?full page name | ||

|?model number | |?model number | ||

|?microprocessor family | |?microprocessor family | ||

|?release price | |?release price | ||

| − | |||

|?first launched | |?first launched | ||

|?core count | |?core count | ||

|?thread count | |?thread count | ||

| + | |?tdp | ||

| + | |?l2$ size | ||

| + | |?l3$ size | ||

|?base frequency#GHz | |?base frequency#GHz | ||

|?turbo frequency (1 core)#GHz | |?turbo frequency (1 core)#GHz | ||

| − | |||

| − | |||

| − | |||

| − | |||

|format=template | |format=template | ||

|template=proc table 3 | |template=proc table 3 | ||

| − | |userparam= | + | |userparam=12 |

|mainlabel=- | |mainlabel=- | ||

| + | |valuesep=, | ||

}} | }} | ||

| − | + | {{comp table count|ask=[[Category:microprocessor models by amd]] [[core name::Naples]]}} | |

| − | {{comp table count|ask=[[Category:microprocessor models by amd | ||

</table> | </table> | ||

{{comp table end}} | {{comp table end}} | ||

== See also == | == See also == | ||

| − | + | {{amd zen core see also}} | |

| − | |||

* {{intel|Skylake|l=arch}} | * {{intel|Skylake|l=arch}} | ||

** {{intel|Skylake SP|l=core}} | ** {{intel|Skylake SP|l=core}} | ||

Latest revision as of 12:49, 18 November 2018

| Edit Values | |

| Naples | |

| |

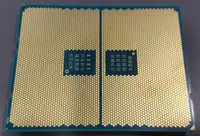

| Package, front | |

| General Info | |

| Designer | AMD |

| Manufacturer | GlobalFoundries |

| Introduction | March 7, 2017 (announced) June 20, 2017 (launched) |

| Microarchitecture | |

| ISA | x86-64 |

| Microarchitecture | Zen |

| Word Size | 8 octets 64 bit16 nibbles |

| Process | 14 nm 0.014 μm 1.4e-5 mm |

| Technology | CMOS |

| Clock | 2,000 MHz - 2,400 MHz |

| Packaging | |

| Package | SP3, FCLGA-4094 (FC-OLGA) |

| Dimension | 75.4 mm 7.54 cm × 58.5 mm2.969 in 5.85 cm × 6.26 mm2.303 in 0.246 in |

| Pitch | 0.87 mm 0.0343 in × 1 mm0.0394 in |

| Contacts | 4094 |

| Socket | SP3, LGA-4094 |

| |

| Succession | |

Naples is codename for AMD's highest-performance enterprise-level server multiprocessors based on the Zen microarchitecture. Naples processors support up 32 cores and are fabricated on GlobalFoundries' 14 nm process. Naples-based processors are branded as EPYC.

Overview[edit]

AMD Naples system on chips are a series of high-performance multiprocessors designed by AMD based on their Zen microarchitecture. Naples SoCs support both single and 2-way multiprocessing with up to a maximum of 32 cores (and 64 threads) per processor for a total of up to 64 cores (and 128 threads) for a 2-way MP system. Those SoCs sports 128 PCIe lanes each, however, half of them are lost when in 2-way MP (leaving the system with the same overall lanes count as a single socket solution). Communication between the two chips is done via AMD's Infinity Fabric protocol over the 64 reserved lanes. Naples is platform/socket forward-compatible with both Rome and Milan.

Common Features[edit]

All Naples processors have the following:

- 128 PCIe lanes (in both single-way and dual-way multiprocessing)

- Octa-channel Memory

- Up to DDR4-2666 ECC

- Up to 2 TiB (4 TiB in 2MP)

- Up to 32 cores / 64 threads

- Everything up to AVX2 (i.e., SMM, FPU, NX, MMX, SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4.2, AES, AVX, FMA3, and AVX2), and SHA

Naples Processors[edit]

| List of Naples Processors | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| Model | Family | Price | Launched | Cores | Threads | TDP | L2$ | L3$ | Base | Turbo |

| 7251 | EPYC | $ 574.00 € 516.60 £ 464.94 ¥ 59,311.42 | 20 June 2017 | 8 | 16 | 120 W 120,000 mW 0.161 hp 0.12 kW | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 32 MiB 32,768 KiB 33,554,432 B 0.0313 GiB | 2.1 GHz 2,100 MHz 2,100,000 kHz | 2.9 GHz 2,900 MHz 2,900,000 kHz |

| 7261 | EPYC | 14 June 2018 | 8 | 16 | 155 W 155,000 mW , 170 W0.208 hp 0.155 kW 170,000 mW 0.228 hp 0.17 kW | 4 MiB 4,096 KiB 4,194,304 B 0.00391 GiB | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 2.5 GHz 2,500 MHz 2,500,000 kHz | 2.9 GHz 2,900 MHz 2,900,000 kHz | |

| 7281 | EPYC | $ 650.00 € 585.00 £ 526.50 ¥ 67,164.50 | 20 June 2017 | 16 | 32 | 155 W 155,000 mW , 170 W0.208 hp 0.155 kW 170,000 mW 0.228 hp 0.17 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 32 MiB 32,768 KiB 33,554,432 B 0.0313 GiB | 2.1 GHz 2,100 MHz 2,100,000 kHz | 2.7 GHz 2,700 MHz 2,700,000 kHz |

| 7301 | EPYC | $ 825.00 € 742.50 £ 668.25 ¥ 85,247.25 | 20 June 2017 | 16 | 32 | 155 W 155,000 mW , 170 W0.208 hp 0.155 kW 170,000 mW 0.228 hp 0.17 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 2.2 GHz 2,200 MHz 2,200,000 kHz | 2.7 GHz 2,700 MHz 2,700,000 kHz |

| 7351 | EPYC | $ 1,100.00 € 990.00 £ 891.00 ¥ 113,663.00 | 20 June 2017 | 16 | 32 | 155 W 155,000 mW , 170 W0.208 hp 0.155 kW 170,000 mW 0.228 hp 0.17 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 2.4 GHz 2,400 MHz 2,400,000 kHz | 2.9 GHz 2,900 MHz 2,900,000 kHz |

| 7351P | EPYC | $ 750.00 € 675.00 £ 607.50 ¥ 77,497.50 | 20 June 2017 | 16 | 32 | 155 W 155,000 mW , 170 W0.208 hp 0.155 kW 170,000 mW 0.228 hp 0.17 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 2.4 GHz 2,400 MHz 2,400,000 kHz | 2.9 GHz 2,900 MHz 2,900,000 kHz |

| 7371 | EPYC | $ 1,550.00 € 1,395.00 £ 1,255.50 ¥ 160,161.50 | 2019 | 16 | 32 | 200 W 200,000 mW 0.268 hp 0.2 kW | 8 MiB 8,192 KiB 8,388,608 B 0.00781 GiB | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 3.1 GHz 3,100 MHz 3,100,000 kHz | 3.8 GHz 3,800 MHz 3,800,000 kHz |

| 7401 | EPYC | $ 1,850.00 € 1,665.00 £ 1,498.50 ¥ 191,160.50 | 20 June 2017 | 24 | 48 | 155 W 155,000 mW , 170 W0.208 hp 0.155 kW 170,000 mW 0.228 hp 0.17 kW | 12 MiB 12,288 KiB 12,582,912 B 0.0117 GiB | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 2 GHz 2,000 MHz 2,000,000 kHz | 3 GHz 3,000 MHz 3,000,000 kHz |

| 7401P | EPYC | $ 1,075.00 € 967.50 £ 870.75 ¥ 111,079.75 | 20 June 2017 | 24 | 48 | 155 W 155,000 mW , 170 W0.208 hp 0.155 kW 170,000 mW 0.228 hp 0.17 kW | 12 MiB 12,288 KiB 12,582,912 B 0.0117 GiB | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 2 GHz 2,000 MHz 2,000,000 kHz | 3 GHz 3,000 MHz 3,000,000 kHz |

| 7451 | EPYC | $ 2,400.00 € 2,160.00 £ 1,944.00 ¥ 247,992.00 | 20 June 2017 | 24 | 48 | 180 W 180,000 mW 0.241 hp 0.18 kW | 12 MiB 12,288 KiB 12,582,912 B 0.0117 GiB | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 2.3 GHz 2,300 MHz 2,300,000 kHz | 3.2 GHz 3,200 MHz 3,200,000 kHz |

| 7501 | EPYC | $ 3,400.00 € 3,060.00 £ 2,754.00 ¥ 351,322.00 | 20 June 2017 | 32 | 64 | 155 W 155,000 mW , 170 W0.208 hp 0.155 kW 170,000 mW 0.228 hp 0.17 kW | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 2 GHz 2,000 MHz 2,000,000 kHz | 3 GHz 3,000 MHz 3,000,000 kHz |

| 7551 | EPYC | $ 3,400.00 € 3,060.00 £ 2,754.00 ¥ 351,322.00 | 20 June 2017 | 32 | 64 | 180 W 180,000 mW 0.241 hp 0.18 kW | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 2 GHz 2,000 MHz 2,000,000 kHz | 3 GHz 3,000 MHz 3,000,000 kHz |

| 7551P | EPYC | $ 2,100.00 € 1,890.00 £ 1,701.00 ¥ 216,993.00 | 20 June 2017 | 32 | 64 | 180 W 180,000 mW 0.241 hp 0.18 kW | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 2 GHz 2,000 MHz 2,000,000 kHz | 3 GHz 3,000 MHz 3,000,000 kHz |

| 7601 | EPYC | $ 4,200.00 € 3,780.00 £ 3,402.00 ¥ 433,986.00 | 20 June 2017 | 32 | 64 | 180 W 180,000 mW 0.241 hp 0.18 kW | 16 MiB 16,384 KiB 16,777,216 B 0.0156 GiB | 64 MiB 65,536 KiB 67,108,864 B 0.0625 GiB | 2.2 GHz 2,200 MHz 2,200,000 kHz | 3.2 GHz 3,200 MHz 3,200,000 kHz |

| Count: 14 | ||||||||||

See also[edit]

| back image |  + + |

| designer | AMD + |

| first announced | March 7, 2017 + |

| first launched | June 20, 2017 + |

| instance of | core + |

| isa | x86-64 + |

| main image |  + + |

| main image caption | Package, front + |

| manufacturer | GlobalFoundries + |

| microarchitecture | Zen + |

| name | Naples + |

| package | SP3 + and FCLGA-4094 + |

| process | 14 nm (0.014 μm, 1.4e-5 mm) + |

| socket | SP3 + and LGA-4094 + |

| technology | CMOS + |

| word size | 64 bit (8 octets, 16 nibbles) + |